# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## 3.3V Phase-Lock Loop Clock Driver

### **General Description**

The ICSVF2510 is a high performance, low skew, low jitter clock driver. It uses a phase lock loop (PLL) technology to align, in both phase and frequency, the CLKIN signal with the CLKOUT signal. It is specifically designed for use with synchronous SDRAMs. The ICSVF2510 operates at 3.3V VCC and drives up to ten clock loads.

One bank of ten outputs provide low-skew, low-jitter copies of CLKIN. Output signal duty cycles are adjusted to 50 percent, independent of the duty cycle at CLKIN. Outputs can be enabled or disabled via control (OE) inputs. When the OE inputs are high, the outputs align in phase and frequency with CLKIN; when the OE inputs are low, the outputs are disabled to the logic low state.

The ICSVF2510 does not require external RC filter components. The loop filter for the PLL is included on-chip, minimizing component count, board space, and cost. The test mode shuts off the PLL and connects the input directly to the output buffer. This test mode, the ICSVF2510 can be use as low skew fanout clock buffer device. The ICSVF2510 comes in 24 pin 173mil Thin Shrink Small-Outline package (TSSOP) package.

#### **Features**

- Meets or exceeds PC133 registered DIMM specification1.1

- Spread Spectrum Clock Compatible

- Distributes one clock input to one bank of ten outputs

- Operating frequency 20MHz to 200MHz

- External feedback input (FBIN) terminal is used to synchrionize the outputs to the clock input

- No external RC network required

- Operates at 3.3V Vcc

- Plastic 24-pin 173mil TSSOP package

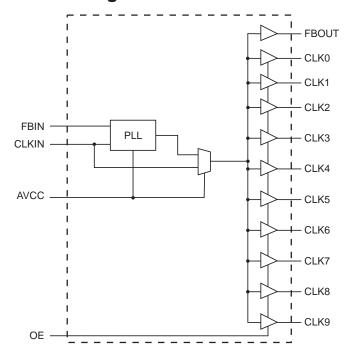

### **Block Diagram**

## **Pin Configuration**

| AGND  | 1  |          | 24 | CLKIN |

|-------|----|----------|----|-------|

| VCC   | 2  |          | 23 | AVCC  |

| CLK0  | 3  |          | 22 | VCC   |

| CLK1  | 4  | 0        | 21 | CLK9  |

| CLK2  | 5  | 51       | 20 | CLK8  |

| GND   | 6  | SVF251   | 19 | GND   |

| GND   | 7  | >>       | 18 | GND   |

| CLK3  | 8  | <u> </u> | 17 | CLK7  |

| CLK4  | 9  | _        | 16 | CLK6  |

| VCC   | 10 |          | 15 | CLK5  |

| OE    | 11 |          | 14 | VCC   |

| FBOUT | 12 |          | 13 | FBIN  |

|       |    |          |    |       |

24 Pin TSSOP

4.40 mm. Body, 0.65 mm. Pitch

# ICSVF2510

# **Pin Descriptions**

| PIN#         | PIN NAME        | TYPE | DESCRIPTION                                                                                                                   |

|--------------|-----------------|------|-------------------------------------------------------------------------------------------------------------------------------|

| 1            | AGND            | PWR  | Analog Ground                                                                                                                 |

| 2, 10, 14    | VCC             | PWR  | Power Supply (3.3V)                                                                                                           |

| 3            | CLK0            | OUT  | Buffered clock output.                                                                                                        |

| 4            | CLK1            | OUT  | Buffered clock output.                                                                                                        |

| 5            | CLK2            | OUT  | Buffered clock output.                                                                                                        |

| 6, 7, 18, 19 | GND             | PWR  | Ground                                                                                                                        |

| 8            | CLK3            | OUT  | Buffered clock output.                                                                                                        |

| 9            | CLK4            | OUT  | Buffered clock output.                                                                                                        |

| 11           | OE <sup>1</sup> | IN   | Output enable (has internal pull_up). When high, normal operation. When low, clock outputs are disabled to a logic low state. |

| 12           | FBOUT           | OUT  | Feedback output                                                                                                               |

| 13           | FBIN            | IN   | Feedback input                                                                                                                |

| 15           | CLK5            | OUT  | Buffered clock output.                                                                                                        |

| 16           | CLK6            | OUT  | Buffered clock output.                                                                                                        |

| 17           | CLK7            | OUT  | Buffered clock output.                                                                                                        |

| 20           | CLK8            | OUT  | Buffered clock output.                                                                                                        |

| 21           | CLK9            | OUT  | Buffered clock output.                                                                                                        |

| 22           | VCC             | PWR  | Power Supply (3.3V) digital supply.                                                                                           |

| 23           | AVCC            | IN   | Analog power supply (3.3V). When input is ground PLL is off and bypassed.                                                     |

| 24           | CLKIN           | IN   | Clock input                                                                                                                   |

#### Note:

1. Weak pull-ups on these inputs

# **Functionality**

| INF | PUTS        | (         | PLL    |        |          |  |

|-----|-------------|-----------|--------|--------|----------|--|

| OE  | AVCC        | CLK (9:0) | FBOUT  | Source | Shutdown |  |

| 0   | 3.33        | 0         | Driven | PLL    | N        |  |

| 1   | 3.33        | Driven    | Driven | PLL    | N        |  |

|     | Buffer Mode |           |        |        |          |  |

| 0   | 0           | 0         | Driven | CLKIN  | Υ        |  |

| 1   | 0           | Driven    | Driven | CLKIN  | Υ        |  |

Test mode:

When AVCC is 0, shuts off the PLL and connects the input directly to the output buffers

## **Absolute Maximum Ratings**

Supply Voltage (AVCC) . . . . . . . . . . . AVCC <  $(V_{cc} + 0.7 V)$

Supply Voltage (VCC) . . . . . . . . . . . . 4.3 V

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### **Electrical Characteristics - OUTPUT**

$T_A = 0 - 70$ °C;  $V_{DD} = V_{DDL} = 3.3 \text{ V +/-10\%}$ ;  $C_L = 30 \text{ pF}$ ;  $R_L = 500 \text{ Ohms (unless otherwise stated)}$

|                                    | 552                                 | , , , , , , , , , , , , , , , , , , , ,          |     |      | ,   |       |  |

|------------------------------------|-------------------------------------|--------------------------------------------------|-----|------|-----|-------|--|

| PARAMETER                          | SYMBOL                              | CONDITIONS                                       | MIN | TYP  | MAX | UNITS |  |

| Output High Voltage                | V <sub>OH</sub>                     | $I_{OH} = -8 \text{ mA}$                         | 2.4 | 2.9  |     | V     |  |

| Output Low Voltage                 | V <sub>OL</sub>                     | $I_{OL} = 8 \text{ mA}$                          |     | 0.25 | 0.4 | V     |  |

| Output High Current                | 1.                                  | $V_{OH} = 2.4 \text{ V}$                         |     | 27   |     | A     |  |

| Output High Current                | I <sub>OH</sub>                     | $V_{OH} = 2.0 \text{ V}$                         |     | 39   |     | mA    |  |

| Output Low Current                 | ı                                   | $V_{OL} = 0.8 \text{ V}$                         |     | 26   |     | mA    |  |

| Output Low Current                 | I <sub>OL</sub>                     | $V_{OL} = 0.55 \text{ V}$                        |     | 19   |     | IIIA  |  |

| Rise Time <sup>1</sup>             | T <sub>r</sub>                      | $V_{OL} = 0.8 \text{ V}, V_{OH} = 2.0 \text{ V}$ | 0.5 | 1.1  | 2.1 | ns    |  |

| Fall Time <sup>1</sup>             | T <sub>f</sub>                      | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.8 \text{ V}$ | 0.5 | 1.1  | 2.7 | ns    |  |

| Duty Cycle <sup>1</sup>            | D <sub>t</sub>                      | $V_T = 1.5 \text{ V;} C_L = 30 \text{ pF}$       | 48  | 50   | 52  | %     |  |

| Cycle to Cycle jitter <sup>1</sup> | T <sub>CYC</sub> - T <sub>CYC</sub> | at 66-100 MHz ; loaded outputs                   |     |      | 75  | ps    |  |

| Absolute Jitter <sup>1</sup>       | T <sub>JABS</sub>                   | 10000 cycles; C <sub>L</sub> = 30 pF             |     |      | 100 | ps    |  |

| Skew <sup>1</sup>                  | T <sub>sk</sub>                     | $V_T = 1.5 \text{ V (Window) Output to Output}$  |     |      | 100 | ps    |  |

| Phase error <sup>1</sup>           | T <sub>pe</sub>                     | $V_T = Vdd/2$ ; CLKIN-FBIN                       | -75 |      | 75  | ps    |  |

| Delay Input-Output <sup>1</sup>    | D <sub>R1</sub>                     | $V_T = 1.5 \text{ V}; \text{ PLL\_EN} = 0$       |     | 3.3  | 3.7 | ns    |  |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design, not 100% tested in production.

## ICSVF2510

## **Electrical Characteristics - Input & Supply**

$T_A = 0 - 70$ °C; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-}10\%$  (unless otherwise stated)

| PARAMETER          | SYMBOL                       | CONDITIONS                                     | MIN                   | TYP | MAX            | UNITS |

|--------------------|------------------------------|------------------------------------------------|-----------------------|-----|----------------|-------|

| Input High Voltage | $V_{IH}$                     |                                                | 2                     |     | $V_{DD} + 0.3$ | V     |

| Input Low Voltage  | $V_{IL}$                     |                                                | V <sub>SS</sub> - 0.3 |     | 0.8            | V     |

| Input High Current | I <sub>IH</sub>              | $V_{IN} = V_{DD}$                              |                       | 0.1 | 100            | uA    |

| Input Low Current  | I <sub>IL</sub>              | $V_{IN} = 0 V;$                                |                       | 19  | 50             | uA    |

| Operating current  | $I_{DD}^{1}$                 | C <sub>L</sub> = 0 pF; F <sub>IN</sub> @ 66MHz |                       |     | 170            | mA    |

| Input Capacitance  | C <sub>IN</sub> <sup>1</sup> | Logic Inputs                                   |                       | 4   |                | pF    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

# Timing requirements over recommended ranges of supply voltage and operating free-air temperature

| Cumbal           | Doromotor           | Took Conditions | N /1:00 | Mov  | l loit  |

|------------------|---------------------|-----------------|---------|------|---------|

| Symbol           | Parameter           | Test Conditions | Min.    | Max. | Unit    |

| $F_{OP}$         | Operating frequency |                 | 20      | 200  | MHz     |

| F <sub>CLK</sub> | Input clock         |                 | 25      | 200  | MHz     |

| ' CLK            | frequency           |                 | 20      | 200  | 1711 12 |

|                  | Input clock         |                 |         |      |         |

|                  | frequency duty      |                 | 40      | 60   | %       |

|                  | cycle               |                 |         |      |         |

|                  | Stabilization time  | After power up  |         | 15   | μs      |

Note: Time required for the PLL circuit to obtain phase lock of its feedback signal to its reference signal. In order for phase lock to be obtained, a fixed-frequency, fixed-phase reference signal must be present at CLK. Until phase lock is obtained, the specifications for parameters given in the switching characteristics table are not applicable.

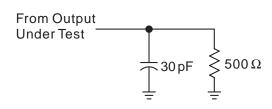

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Load Circuit for Outputs

#### Notes:

1. C<sub>L</sub> includes probe and jig capacitance.

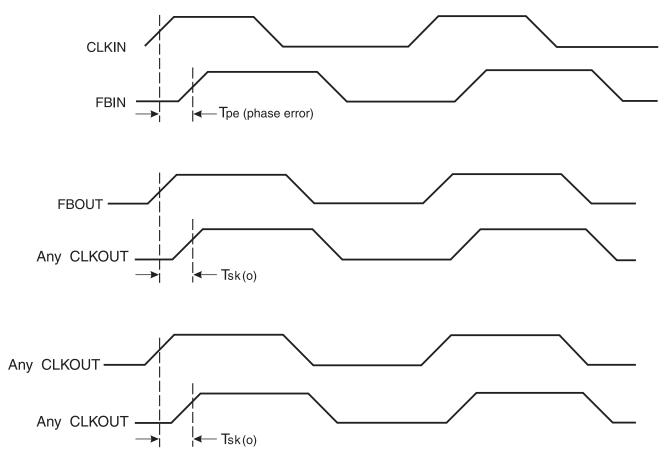

Figure 2. Voltage Waveforms

Propagation Delay Times

- 2. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  133MHz,  $Z_0 = 50 \Omega$ ,  $T_r \leq$  1.2ns,  $T_f \leq$  1.2ns.

- 3. The outputs are measured one at a time with one transition per measurement.

Figure 3. Phase Error and Skew Calculations

0722A—05/07/03

### ICSVF2510

#### **General Layout Precautions:**

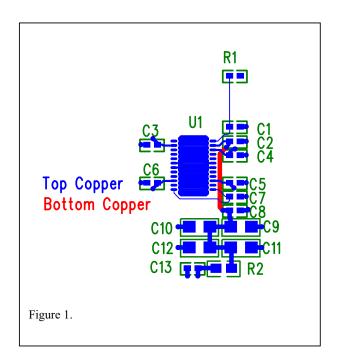

An ICS2509C is used as an example. It is similar to the ICSVF2510. The same rules and methods apply.

- 1) Use copper flooded ground on the top signal layer under the clock buffer The area under U1 in figure 1 on the right is an example. Every ground pin goes to a ground via. The vias are not visible in figure 1.

- Use power vias for power and ground. Vias 20 mil or larger in diameter have lower high frequency impedance. Vias for signals may be minimum drill size.

- Make all power and ground traces are as wide as the via pad for lower inductance.

- 4) VAA for pin 23 has a low pass RC filter to decouple the digital and analog supplies. C9-12 may be replaced with a single low ESR (0.8 ohm or less) device with the same total capacitance. R2 may be replaced with a ferrite bead. The bead should have a DC resistance of at least 0.5 ohms. 1 ohm is better. It should have an impedance of at least 300 ohms at 100MHz. 600 ohms at 100MHz is better.

- 5) Notice that ground vias are never shared.

- 6) All VCC pins have a decoupling capacitor. Power is always routed from the plane connection via to the capacitor pad to the VCC pin on the clock buffer.

- 7) Component R1 is located at the clock source.

- 8) Component C1, if used, has the effect of adding delay.

- 9) Component C7, if used, has the effect of subtracting delay. Delaying the FBIn clock will cause the output clocks to be earlier. A more effective method is to use the propagation time of a trace between FBOut and FBIn.

#### Component Values:

C1,C7= As necessary for delay adjust C[6:2]=.01uF C8,C13=0.1uF

C[12:9]=4.7Uf

R1=10 ohm. Locate at driver

R2=10 ohm.

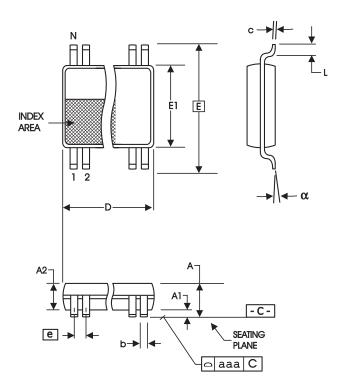

4.40 mm. Body, 0.65 mm. pitch TSSOP (173 mil) (0.0256 lnch)

|        | In Millimeters |                         | In Inches         |          |  |

|--------|----------------|-------------------------|-------------------|----------|--|

| SYMBOL | COMMON D       | IMENSIONS               | COMMON DIMENSIONS |          |  |

|        | MIN            | MAX                     | MIN               | MAX      |  |

| Α      |                | 1.20                    | -                 | .047     |  |

| A1     | 0.05           | 0.15                    | .002              | .006     |  |

| A2     | 0.80           | 1.05                    | .032              | .041     |  |

| b      | 0.19           | 0.30                    | .007              | .012     |  |

| С      | 0.09           | 0.20                    | .0035             | .008     |  |

| D      | SEE VARIATIONS |                         | SEE VARIATIONS    |          |  |

| E      | 6.40           | BASIC                   | 0.252 BASIC       |          |  |

| E1     | 4.30           | 4.50                    | .169              | .177     |  |

| е      | 0.65           | 0.65 BASIC 0.0256 BASIC |                   | BASIC    |  |

| L      | 0.45           | 0.75                    | .018              | .030     |  |

| N      | SEE VARIATIONS |                         | SEE VAF           | RIATIONS |  |

| α      | 0°             | 8°                      | 0°                | 8°       |  |

| aaa    |                | 0.10                    | -                 | .004     |  |

#### **VARIATIONS**

| N  | Dr   | nm.  | D (inch) |      |

|----|------|------|----------|------|

|    | MIN  | MAX  | MIN      | MAX  |

| 24 | 7.70 | 7.90 | .303     | .311 |

Reference Doc.: JEDEC Publication 95, MO-153

10-0035

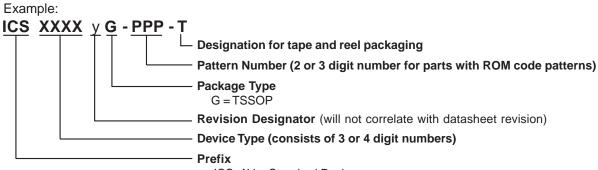

## **Ordering Information**

ICSVF2510yG-T

ICS, AV = Standard Device

0722A—05/07/03