# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

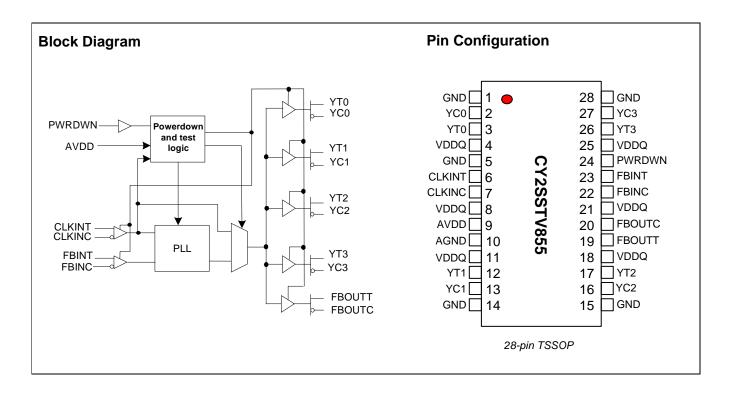

## Differential Clock Buffer/Driver

#### **Features**

- Phase-locked loop (PLL) clock distribution for Double Data Rate Synchronous DRAM applications

- 1:5 differential outputs

- External feedback pins (FBINT, FBINC) are used to synchronize the outputs to the clock input

- SSCG: Spread Aware<sup>™</sup> for electromagnetic interference (EMI) reduction

- 28-pin TSSOP package

- Conforms to JEDEC DDR specifications

## **Functional Description**

The CY2SSTV855 is a high-performance, very-low-skew, very-low-jitter zero-delay buffer that distributes a differential clock input pair (SSTL\_2) to four differential (SSTL\_2) pairs of clock outputs and one differential pair of feedback clock outputs. In support of low power requirements, when power-down is HIGH, the outputs switch in phase and frequency with the input clock. When power-down is LOW, all outputs are disabled to a high-impedance state and the PLL is shut down.

The device supports a low-frequency power-down mode. When the input is < 20 MHz, the PLL is disabled and the outputs are put in the Hi-Z state. When the input frequency is > 20 MHz, the PLL and outputs are enabled.

When AVDD is tied to ground, the PLL is turned off and bypassed with the input reference clock gated to the outputs. The Cypress CY2SSTV855 is Spread Aware and supports tracking of Spread Spectrum clock inputs to reduce EMI

#### Pin Definition<sup>[1, 2]</sup>

| Pin             | Name    | I/O | Description                                                                                                                                                                                         |  |

|-----------------|---------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6               | CLKINT  | ı   | True Clock Input. Low Voltage Differential True Clock Input.                                                                                                                                        |  |

| 7               | CLKINC  | ı   | Complementary Clock Input. Low Voltage Differential Complementary Clock Input.                                                                                                                      |  |

| 22              | FBINC   | I   | Feedback Complementary Clock Input. Differential Input Connect to FBOUTC for accessing the PLL.                                                                                                     |  |

| 23              | FBINT   | I   | Feedback True Clock Input. Differential Input Connect to FBOUTT for accessing the PLL.                                                                                                              |  |

| 3,12,17,26      | YT(0:3) | 0   | True Clock Outputs. Differential Outputs.                                                                                                                                                           |  |

| 2,13,16,27      | YC(0:3) | 0   | Complementary Clock Outputs. Differential Outputs.                                                                                                                                                  |  |

| 19              | FBOUTT  | 0   | eedback True Clock Output. Differential Outputs. Connect to FBINT for normal operation. A bypass delay capacitor at this output will control Input Reference/Output locks phase relationships.      |  |

| 20              | FBOUTC  | 0   | eedback Complementary Clock Output. Differential Outputs. Connect to FBINC formal operation. A bypass delay capacitor at this output will control Input eference/Output Clocks phase relationships. |  |

| 24              | PWRDWN  | I   | Control input to turn device in the power-down mode.                                                                                                                                                |  |

| 4,8,11,18,21,25 | VDDQ    |     | 2.5V Power Supply for Output Clock Buffers.2.5V Nominal.                                                                                                                                            |  |

| 9               | AVDD    |     | 2.5V Power Supply for PLL. 2.5V Nominal.                                                                                                                                                            |  |

| 1,5,14,15,28    | GND     |     | Ground                                                                                                                                                                                              |  |

| 10              | AGND    |     | Analog Ground. 2.5V Analog Ground.                                                                                                                                                                  |  |

## Zero-delay Buffer

When used as a zero-delay buffer the CY2SSTV855 will likely be in a nested clock tree application. For these applications the CY2SSTV855 offers a differential clock input pair as a PLL reference. The CY2SSTV855 then can lock onto the reference and translate with near zero delay to low-skew outputs. For normal operation, the external feedback differential input, FBINT/C, is connected to the feedback output, FBOUTT/C. By

connecting the feedback output to the feedback input the propagation delay through the device is eliminated. The PLL works to align the output edge with the input reference edge thus producing a near zero delay. The reference frequency affects the static phase offset of the PLL and thus the relative delay between the inputs and outputs.

When AVDD is strapped LOW, the PLL is turned off and bypassed for test purposes.

#### **Function Table**

| Inputs |        |          | Outputs  |         |         |        |        |              |

|--------|--------|----------|----------|---------|---------|--------|--------|--------------|

| AVDD   | PWRDWN | CLKINT   | CLKINC   | YT(0:3) | YC(0:3) | FBOUTT | FBOUTC | PLL          |

| GND    | Н      | L        | Н        | L       | Н       | L      | Н      | BYPASSED/OFF |

| GND    | Н      | Н        | L        | Н       | L       | Н      | L      | BYPASSED/OFF |

| 2.5V   | Н      | L        | Н        | L       | Н       | L      | Н      | On           |

| 2.5V   | Н      | Н        | L        | Н       | L       | Н      | L      | On           |

| 2.5V   | Х      | < 20 MHz | < 20 MHz | Hi-Z    | Hi-Z    | Hi-Z   | Hi-Z   | Off          |

#### Notes:

- PU = internal pull-up.

- A bypass capacitor (0.1μF) should be placed as close as possible to each positive power pin (< 0.2"). If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be cancelled by the lead inductance of the traces.</li>

...... Document #: 38-07459 Rev. \*F Page 2 of 6

## **Differential Parameter Measurement Information**

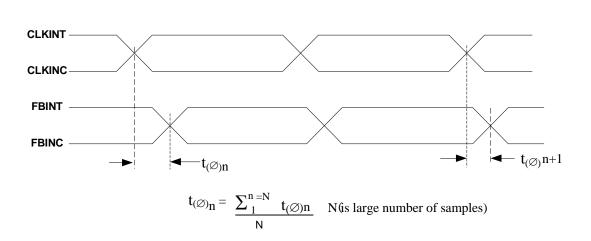

Figure 1. Static Phase Offset

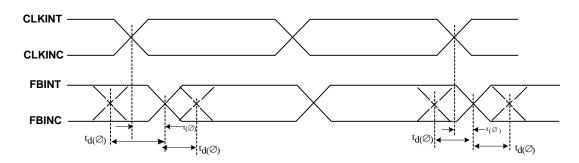

Figure 2. Dynamic Phase Offset

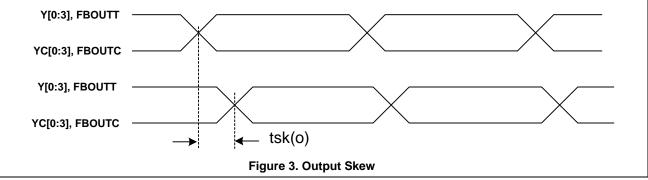

## **Differential Parameter Measurement Information** (continued)

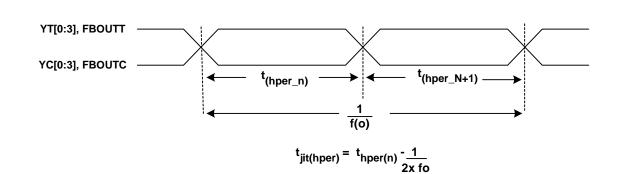

Figure 4. Half-period Jitter

$t_{jit(cc)} = t_{c(n)}^{-t}c_{(n+1)}$

Figure 5. Cycle-to-cycle Jitter

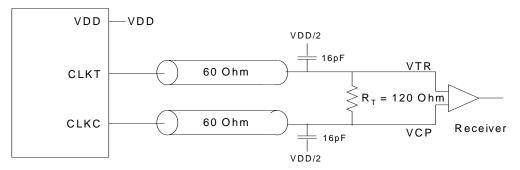

Figure 6. Differential Signal Using Direct Termination Resistor

## Absolute Maximum Conditions[3]

| Input Voltage Relative to V <sub>SS</sub> :               | V <sub>SS</sub> – 0.3V                    |

|-----------------------------------------------------------|-------------------------------------------|

| Input Voltage Relative to $V_{\mbox{\scriptsize DDQ}}$ or | AV <sub>DD</sub> : V <sub>DD</sub> + 0.3V |

| Storage Temperature:                                      | 65°C to + 150°C                           |

| Operating Temperature:                                    | 40°C to +85°C                             |

| Maximum Power Supply:                                     | 3.5V                                      |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation, V<sub>in</sub> and V<sub>out</sub> should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

## DC Electrical Specifications (AV<sub>DD</sub> = $V_{DDQ}$ = 2.5V ± 5%, $T_A$ = -40°C to +85°C)<sup>[4]</sup>

| Parameter        | Description                                        | Conditions                                             | Min.                           | Тур.                | Max.                        | Unit |

|------------------|----------------------------------------------------|--------------------------------------------------------|--------------------------------|---------------------|-----------------------------|------|

| $V_{\text{ID}}$  | Differential Input Voltage <sup>[5]</sup>          | CLKINT, FBINT                                          | 0.36                           |                     | V <sub>DDQ</sub> + 0.6      | V    |

| V <sub>IX</sub>  | Differential Input Crossing Voltage <sup>[6]</sup> | CLKTIN, FBINT                                          | (V <sub>DDQ</sub> /2) –<br>0.2 | V <sub>DDQ</sub> /2 | (V <sub>DDQ</sub> /2) + 0.2 | V    |

| I <sub>IN</sub>  | Input Current                                      | $V_{IN} = 0V$ or $V_{IN} = V_{DDQ}$ , CLKINT,<br>FBINT | -10                            | -                   | 10                          | μΑ   |

| I <sub>OL</sub>  | Output Low Current                                 | V <sub>DDQ</sub> = 2.375V, V <sub>OUT</sub> = 1.2V     | 26                             | 35                  | _                           | mA   |

| I <sub>OH</sub>  | Output High Current                                | V <sub>DDQ</sub> = 2.375V, V <sub>OUT</sub> = 1V       | -18                            | -32                 | _                           | mΑ   |

| V <sub>OL</sub>  | Output Low Voltage                                 | $V_{DDQ} = 2.375V, I_{OL} = 12 \text{ mA}$             |                                | -                   | 0.6                         | V    |

| V <sub>OH</sub>  | Output High Voltage                                | $V_{DDQ} = 2.375V$ , $I_{OH} = -12 \text{ mA}$         | 1.7                            | -                   | _                           | V    |

| V <sub>OUT</sub> | Output Voltage Swing <sup>[7]</sup>                |                                                        | 1.1                            | -                   | V <sub>DDQ</sub> – 0.4      | V    |

| V <sub>oc</sub>  | Output Crossing Voltage <sup>[8]</sup>             |                                                        | (V <sub>DDQ</sub> /2) –<br>0.2 | V <sub>DDQ</sub> /2 | (V <sub>DDQ</sub> /2) + 0.2 | V    |

| I <sub>OZ</sub>  | High-Impedance Output Current                      | $V_O = GND \text{ or } V_O = V_{DDQ}$                  | -10                            |                     | 10                          | μΑ   |

| I <sub>DDQ</sub> | Dynamic Supply Current <sup>[9]</sup>              | V <sub>DDQ</sub> = 170 MHz                             | _                              | 235                 | 300                         | mA   |

| I <sub>DD</sub>  | PLL Supply Current                                 | AV <sub>DD</sub> only                                  | _                              | 9                   | 12                          | mA   |

| Cin              | Input Pin Capacitance                              |                                                        | _                              | 4                   | _                           | pF   |

## AC Electrical Specifications (AV<sub>DD</sub> = $V_{DDQ}$ = 2.5V±5%, $T_A$ = -40°C to +85°C)<sup>[10, 11]</sup>

| Parameter                           | Description                                       | Conditions                | Min. | Тур. | Max. | Unit |

|-------------------------------------|---------------------------------------------------|---------------------------|------|------|------|------|

| f <sub>CLK</sub>                    | Operating Clock Frequency                         | $AV_{DD} = 2.5V \pm 0.2V$ | 60   |      | 170  | MHz  |

| t <sub>DC</sub>                     | Input Clock Duty Cycle <sup>[12]</sup>            |                           | 40   |      | 60   | %    |

| t <sub>LOCK</sub>                   | Maximum PLL lock Time                             |                           |      |      | 100  | μs   |

| t <sub>SL(O)</sub>                  | Output Clocks Slew Rate                           | 20% to 80% of VOD         | 1    |      | 2    | V/ns |

| t <sub>PZL</sub> , t <sub>PZH</sub> | Output Enable Time (all outputs) <sup>[13]</sup>  |                           |      | 30   |      | ns   |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | Output Disable Time (all outputs) <sup>[13]</sup> |                           |      | 10   |      | ns   |

| t <sub>CCJ</sub>                    | Cycle to Cycle Jitter                             | f > 66 MHz                | -100 |      | 100  | ps   |

| t <sub>JITT(H-PER)</sub>            | Half-period jitter                                | f > 66 MHz                | -100 |      | 100  | ps   |

#### Notes

- 3. Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

- 4. Unused inputs must be held HIGH or LOW to prevent them from floating.

- 5. Differential input signal voltage specifies the differential voltage |VTR VCP| required for switching, where VTR is the true input level and VCP is the complementary input level.

- 6. Differential cross-point input voltage is expected to track V<sub>DDQ</sub> and is the voltage at which the differential signals must be crossing.

- 7. For load conditions see Figure 6.

- 8. The value of  $V_{OC}$  is expected to be |VTR + VCP|/2. In case of each clock directly terminated by a  $120\Omega$  resistor. See Figure 6.

- 9. All outputs switching loaded with 16 pF in  $60\Omega$  environment. See Figure 6.

- 10. Parameters are guaranteed by design and characterization. Not 100% tested in production.

- 11. PLL is capable of meeting the specified parameters while supporting SSC synthesizers with modulation frequency between 30 kHz and 33.3 kHz with a downspread of -0.5%

- 12. While the pulse skew is almost constant over frequency, the duty cycle error increases at higher frequencies. This is due to the formula: duty cycle = t<sub>WH</sub>/t<sub>C</sub>, where the cycle time (t<sub>C</sub>) decreases as the frequency goes up.

- 13. Refers to transition of non-inverting output.

- 14. All differential input and output terminals are terminated with  $120\Omega/16~pF$  as shown in Figure 6.

# AC Electrical Specifications (AV<sub>DD</sub> = V<sub>DDQ</sub> = $2.5V\pm5\%$ , T<sub>A</sub> = -40°C to +85°C)<sup>[10, 11]</sup> (continued)

| Parameter          | Description                                         | Conditions | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------------------|------------|------|------|------|------|

| t <sub>PLH</sub>   | Low-to-High Propagation Delay,<br>CLKINT to YT[0:3] |            | 1.5  | 3.5  | 6    | ns   |

| t <sub>PHL</sub>   | High-to-Low Propagation Delay,<br>CLKINT to YT[0:3] |            | 1.5  | 3.5  | 6    | ns   |

| t <sub>SK(0)</sub> | Any Output to Any Output Skew <sup>[14]</sup>       |            | -    | _    | 100  | ps   |

| $t_{(\emptyset)}$  | Static Phase Offset <sup>[14]</sup>                 |            | -450 | _    | 450  | ps   |

| $t_{D(\emptyset)}$ | Dynamic Phase Offset                                | f > 66 MHz | -350 | _    | 350  | ps   |

## Ordering Information

| Part Number    | Package Type                 | Product Flow             |  |  |

|----------------|------------------------------|--------------------------|--|--|

| CY2SSTV855ZC   | 28-pin TSSOP                 | Commercial, 0° to 70°C   |  |  |

| CY2SSTV855ZCT  | 28-pin TSSOP – Tape and Reel | Commercial, 0° to 70°C   |  |  |

| CY2SSTV855ZI   | 28-pin TSSOP                 | Industrial, -40° to 85°C |  |  |

| CY2SSTV855ZIT  | 28-pin TSSOP – Tape and Reel | Industrial,-40° to 85°C  |  |  |

| Lead Free      |                              | ·                        |  |  |

| CY2SSTV855ZXC  | 28-pin TSSOP                 | Commercial, 0° to 70°C   |  |  |

| CY2SSTV855ZXCT | 28-pin TSSOP – Tape and Reel | Commercial, 0° to 70°C   |  |  |

| CY2SSTV855ZXI  | 28-pin TSSOP                 | Industrial, –40° to 85°C |  |  |

| CY2SSTV855ZXIT | 28-pin TSSOP – Tape and Reel | Industrial,-40° to 85°C  |  |  |

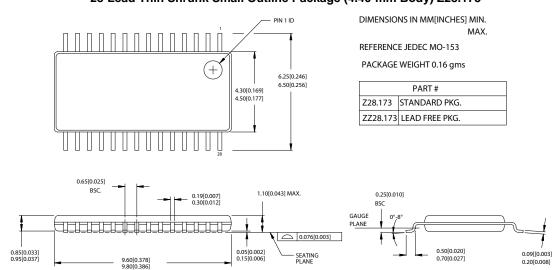

## **Package Drawing and Dimensions**

### 28-Lead Thin Shrunk Small Outline Package (4.40-mm Body) Z28.173

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

...... Document #: 38-07459 Rev. \*F Page 6 of 6