1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

## **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## **PI6C180**

## **Precision 1-18 Clock Buffer**

### Features

- High-speed, to 100 MHz

- Low-noise non-inverting 1-18 buffer

- Supports up to four SDRAM DIMMs

- Low skew (< 250ps) between any two output clocks

- I<sup>2</sup>C Serial Configuration interface

- Multiple V<sub>DD</sub>, V<sub>SS</sub> pins for noise reduction

- 3.3V power supply voltage

- Separate Hi-Z pin for testing

- Packaging:

- 48-pin SSOP (V)

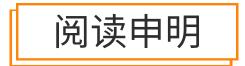

## **Block Diagram**

## Description

The PI6C180, a high-speed low-noise 1-18 non-inverting buffer designed for SDRAM clock buffer applications operates up to 100 MHz.

At power up all SDRAM output are enabled and active. The  $I^2C$  Serial control may be used to individually activate/deactivate any of the 18 output drivers.

The output enable (OE) pin may be pulled low to put all outputs in a Hi-Z state.

#### Note:

Purchase of  $I^2C$  components from Pericom conveys a license to use them in an  $I^2C$  system as defined by Philips.

## **Pin Configuration**

| -                  |             |                         |

|--------------------|-------------|-------------------------|

|                    |             |                         |

| NC                 | <b>d</b> 1  | 48 🛛 NC                 |

| NC                 | <b>C</b> 2  | 47 🛛 NC                 |

| $V_{DD0}$          | Цз          | 46 🛛 V <sub>DD9</sub>   |

| SDRAM0             | <b>4</b>    | 45 🛛 SDRAM15            |

| SDRAM1             | <b>[</b> 5  | 44 🛛 SDRAM14            |

| V <sub>SS0</sub>   | <b>4</b> 6  | 43 🛛 V <sub>SS9</sub>   |

| $V_{DD1}$          | <b>q</b> 7  | 42 🛛 V <sub>DD8</sub>   |

| SDRAM2             | <b>4</b> 8  | 41 🛛 SDRAM13            |

| SDRAM3             | <b>口</b> 9  | 40 🛛 SDRAM12            |

| V <sub>SS1</sub>   | <b>[</b> 10 | 39 🛛 V <sub>SS8</sub>   |

| BUF_IN             | <b>[</b> 11 | 38 🗖 OE                 |

| $V_{DD2}$          | <b>[</b> 12 | 37 🛛 V <sub>DD7</sub>   |

| SDRAM4             | <b>[</b> 13 | 36 🛛 SDRAM11            |

| SDRAM5             | <b>[</b> 14 | 35 🛛 SDRAM10            |

| $V_{SS2}$          | <b>[</b> 15 | 34 🛛 V <sub>SS7</sub>   |

| $V_{DD3}$          | <b>[</b> 16 | 33 📮 V <sub>DD6</sub>   |

| SDRAM6             | <b>[</b> 17 | 32 SDRAM9               |

| SDRAM7             | <b>[</b> 18 | 31 🛛 SDRAM8             |

| $V_{SS3}$          | <b>[</b> 19 | 30 🛛 V <sub>SS6</sub>   |

| $V_{DD4}$          | <b>[</b> 20 | 29 🛛 V <sub>DD5</sub>   |

| SDRAM16            | <b>[</b> 21 | 28 SDRAM17              |

| $V_{SS4}$          | <b>C</b> 22 | 27 🛛 V <sub>SS5</sub>   |

| V <sub>DDIIC</sub> | <b>C</b> 23 | 26 🛛 V <sub>SSIIC</sub> |

| SDATA              | <b>C</b> 24 | 25 🛛 SCLOCK             |

|                    | L           |                         |

# PERICOM®

## **Pin Description**

| Pin                                         | Symbol               | Туре     | Qty | Description                                                                              |

|---------------------------------------------|----------------------|----------|-----|------------------------------------------------------------------------------------------|

| 4, 5, 8, 9                                  | SDRAM[0-3]           | 0        | 4   | SDRAM Byte 0 clock output                                                                |

| 13, 14, 17, 18                              | SDRAM[4-7]           | 0        | 4   | SDRAM Byte 1 clock output                                                                |

| 31, 32, 35, 36                              | SDRAM[8-11]          | 0        | 4   | SDRAM Byte 2 clock output                                                                |

| 40, 41, 44, 45                              | SDRAM[12-15]         | 0        | 4   | SDRAM Byte 3 clock output                                                                |

| 21, 28                                      | SDRAM[16-17]         | 0        | 4   | SDRAM clock outputs usable for feedback                                                  |

| 11                                          | Buf_IN               | Ι        | 1   | Input for 1-18 buffer                                                                    |

| 38                                          | OE                   | Ι        | 1   | Hi-Z all outputs when held LOW. Has a $>100k\Omega$ internal pull-up resistor            |

| 24                                          | S <sub>DATA</sub>    | I/O      | 1   | Data pin for I <sup>2</sup> C circuitry. Has a >100k $\Omega$ internal pull-up resistor  |

| 25                                          | S <sub>CLOCK</sub>   | I/O      | 1   | Clock pin for I <sup>2</sup> C circuitry. Has a >100k $\Omega$ internal pull-ip resistor |

| 3, 7, 12, 16,<br>20, 29, 33, 37,<br>42, 46  | V <sub>DD[0-9]</sub> | Power    | 10  | 3.3V power supply for SDRAM buffers                                                      |

| 6, 10, 15, 19,<br>22, 27, 30, 34,<br>39, 43 | V <sub>SS[0-9]</sub> | Ground   | 10  | Ground for SDRAM buffers                                                                 |

| 23                                          | V <sub>DDIIC</sub>   | Power    | 1   | 3.3V power supply for I <sup>2</sup> C circuitry                                         |

| 26                                          | V <sub>SSIIC</sub>   | Ground   |     | Ground for I <sup>2</sup> C circuitry                                                    |

| 1, 2, 47, 48                                | NC                   | Reserved | 4   | Reserved for future modifications. No connects                                           |

## **OE** Functionality

| OE | SDRAM[0-17] | Notes |

|----|-------------|-------|

| 0  | Hi-Z        | 1     |

| 1  | BUF_IN      | 2     |

Notes:

1. Used for test purposes only

2. Buffers are non-inverting

## I<sup>2</sup>C Address Assignment

| A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W |

|----|----|----|----|----|----|----|-----|

| 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0   |

## **Serial Configuration Map**

## Byte0: SDRAM Active/Inactive Register

(1 = enable, 0 = disable)

| Bit | Pin | Description              |

|-----|-----|--------------------------|

| 7   | 18  | SDRAM7 (Active/Inactive) |

| 6   | 17  | SDRAM6 (Active/Inactive) |

| 5   | 14  | SDRAM5 (Active/Inactive) |

| 4   | 13  | SDRAM4 (Active/Inactive) |

| 3   | 9   | SDRAM3 (Active/Inactive) |

| 2   | 8   | SDRAM2 (Active/Inactive) |

| 1   | 5   | SDRAM1 (Active/Inactive) |

| 0   | 4   | SDRAM0 (Active/Inactive) |

Note:

1. Inactive means outputs are held LOW and are disabled from switching.

## 2-Wire I<sup>2</sup>C Control

The I<sup>2</sup>C interface permits individual enable/disable of each clock output and test mode enable.

The PI6C180 is a slave receiver device. It can not be read back. Sub addressing is not supported. All preceding bytes must be sent in order to change one of the control bytes.

Every bite put on the SDATA line must be 8-bits long (MSB first), followed by an acknowledge bit generated by the receiving device.

During normal data transfers SDATA changes only when SCLOCK is LOW. Exceptions: A HIGH to LOW transition on SDATA while SCLOCK is HIGH indicates a "start" condition. A LOW to HIGH transition on SDATAwhile SCLOCK is HIGH is a "stop" condition and indicates the end of a data transfer cycle.

Each data transfer is initiated with a start condition and ended with a stop condition. The first byte after a start condition is always a 7-bit address byte followed by a read/write bit. (HIGH = read from addressed device, LOW= write to addressed device). If the device's own address is detected, PI6C180 generates an acknowledge by pulling SDATA line LOW during ninth clock pulse, then accepts the following data bytes until another start or stop condition is detected.

Following acknowledgement of the address byte (D2), two more bytes must be sent:

- 1. "Command Code" byte, and

- 2. "Byte Count" byte.

Although the data bits on these two bytes are "don't care," they must be sent and acknowledged.

| yte1: SDF | RAM Activ  | ve/Inactive | Register |

|-----------|------------|-------------|----------|

| 1         | 0 - diante | (a)         |          |

(1 = enable, 0 = disable)

B

| Bit | Pin | Description               |

|-----|-----|---------------------------|

| 7   | 45  | SDRAM15 (Active/Inactive) |

| 6   | 44  | SDRAM14 (Active/Inactive) |

| 5   | 41  | SDRAM13 (Active/Inactive) |

| 4   | 40  | SDRAM12 (Active/Inactive) |

| 3   | 36  | SDRAM11 (Active/Inactive) |

| 2   | 35  | SDRAM10 (Active/Inactive) |

| 1   | 32  | SDRAM9 (Active/Inactive)  |

| 0   | 31  | SDRAM8 (Active/Inactive)  |

#### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature–65°C to +150°C                   |

|------------------------------------------------------|

| Ambient Temperature with Power Applied0°C to +70°C   |

| 3.3V Supply Voltage to Ground Potential0.5V to +4.6V |

| DC Input Voltage0.5V to +4.6V                        |

|                                                      |

#### Note:

Stresses greater than those listed under MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Supply Current ( $V_{DD} = +3.465V$ , $C_{LOAD} = Max$ .)

| Symbol          | Parameter      | Test Condidtion      | Min. | Тур. | Max. | Units |

|-----------------|----------------|----------------------|------|------|------|-------|

| I <sub>DD</sub> |                | BUF_IN = 0 MHz       |      |      | 2    |       |

| I <sub>DD</sub> | Supply Current | $BUF_IN = 66.66 MHz$ |      |      | 230  | mA    |

| I <sub>DD</sub> |                | BUF_IN = 100.00 MHz  |      |      | 360  |       |

#### **Byte2: Optional Register for Possible Future Requirements** (1 = enable, 0 = disable)

| Bit | Pin | Description               |

|-----|-----|---------------------------|

| 7   | 28  | SDRAM17 (Active/Inactive) |

| 6   | 21  | SDRAM16 (Active/Inactive) |

| 5   |     | (Reserved)                |

| 4   |     | (Reserved)                |

| 3   |     | (Reserved)                |

| 2   |     | (Reserved)                |

| 1   |     | (Reserved)                |

| 0   |     | (Reserved)                |

## **DC Operating Specifications** ( $V_{DD} = +3.3V \pm 5\%$ , $T_A = 0^{\circ}C - 70^{\circ}C$ )

| Symbol                    | Parameter                    | Test Conditions       | Min.                 | Тур. | Max.                 | Units |

|---------------------------|------------------------------|-----------------------|----------------------|------|----------------------|-------|

| Input Voltag              | e                            |                       |                      |      |                      |       |

| V <sub>IH</sub>           | Input High voltage           | V <sub>DD</sub>       | 2.0                  |      | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub>           | Input Low voltage            |                       | V <sub>SS</sub> -0.3 |      | 0.8                  |       |

| I <sub>IL</sub>           | Input leakage current        | $0 < V_{IN} < V_{DD}$ | -5                   |      | 5                    | mA    |

| V <sub>DD</sub> [0-9] = . | 3.3V ±5% Output High voltage | $I_{OH} = -1mA$       | 2.4                  |      |                      | V     |

| V <sub>OL</sub>           | Output Low voltage           | $I_{OL} = 1mA$        |                      |      | 0.4                  |       |

| C <sub>OUT</sub>          | Output pin capacitance       |                       |                      | 6    |                      | pF    |

| C <sub>IN</sub>           | Input pin capacitance        |                       |                      | 5    |                      |       |

| L <sub>PIN</sub>          | Pin Inductance               |                       |                      | 7    |                      | nH    |

| T <sub>A</sub>            | Ambient Temperature          | No Airflow            | 0                    |      | 70                   | °C    |

## **SDRAM Clock Buffer Operating Specification**

| Symbol                | Parameter                        | Test Conditions        | Min. | Тур. | Max. | Units |

|-----------------------|----------------------------------|------------------------|------|------|------|-------|

| I <sub>OHMIN</sub>    | Pull-up current                  | $V_{OUT} = 2.0 V$      | -54  |      |      |       |

| I <sub>OHMAX</sub>    | Pull-up current                  | $V_{OUT} = 3.135 V$    |      |      | -46  | A     |

| I <sub>OLMIN</sub>    | Pull-down current                | $V_{OUT} = 1.0V$       | 54   |      |      | mA    |

| I <sub>OLMAX</sub>    | Pull-down current                | $V_{OUT} = 0.4 V$      |      |      | 53   |       |

| t <sub>RH</sub> SDRAM | Output rise edge rate SDRAM only | 3.3V ±5% @ 0.4V - 2.4V | 1.5  |      | 4    | Mar   |

| t <sub>TH</sub> SDRAM | Output fall edge rate SDRAM only | 3.3V ±5% @ 2.4V - 0.4V | 1.5  |      | 4    | V/ns  |

## **AC Timing**

| Symbol                              | Parameter                                 | 66 ] | 66 MHz |      | 100 MHz |               |  |

|-------------------------------------|-------------------------------------------|------|--------|------|---------|---------------|--|

|                                     |                                           | Min. | Max.   | Min. | Max.    | Units         |  |

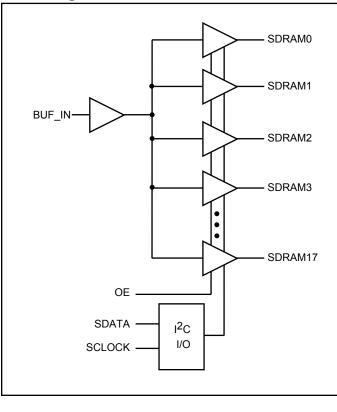

| t <sub>SDRISE</sub>                 | SDRAM CLK rise time                       | 1.5  | 4.0    | 1.5  | 4.0     | 4.0 V/ns      |  |

| t <sub>SDFALL</sub>                 | SDRAM CLK fall time                       | 1.5  | 4.0    | 1.5  | 4.0     | V/IIS         |  |

| t <sub>PLH</sub>                    | SDRAM Buffer LH prop delay                | 1.0  | 5.0    | 1.0  | 5.0     |               |  |

| t <sub>PHL</sub>                    | SDRAM Buffer HL prop delay                | 1.0  | 5.0    | 1.0  | 5.0     |               |  |

| t <sub>PZL</sub> , t <sub>PZH</sub> | SDRAM Buffer Enable delay <sup>(1)</sup>  | 1.0  | 8.0    | 1.0  | 8.0     | 8.0 ns<br>8.0 |  |

| t <sub>PLZ</sub> , t <sub>PHZ</sub> | SDRAM Buffer DIsable delay <sup>(1)</sup> | 1.0  | 8.0    | 1.0  | 8.0     |               |  |

| Duty Cycle                          | Measured at 1.5V                          | 45   | 55     | 45   | 55      | %             |  |

| t <sub>SDSKW</sub>                  | SDRAM Output-to-Output skew               |      | 250    |      | 250     | ps            |  |

Note:

1. This Parameter specified at 5MHz input frequency.

# PERICOM®

Figure 1. Clock Waveforms

#### Minimum & Maximum Expected Capacitive Loads

| Clock | Min.<br>Load | Max.<br>Load | Units | Notes                      |

|-------|--------------|--------------|-------|----------------------------|

| SDRAM | 20           | 30           | pF    | SDRAM DIMM<br>Specfication |

#### Notes:

- 1. Maximum rise/fall times are guaranteed at maximum specified load.

- 2. Minimum rise/fall times are guaranteed at minimum specified load.

- Rise/fall times are specified with pure capacitive load as shown.

Testing is done with an additional 500 akm register

Testing is done with an additional 500-ohm resistor in parallel.

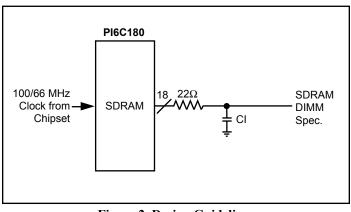

## **Design Guidelines to Reduce EMI**

- 1. Place series resistors and CI capacitors as close as possible to the respective clock pins. Typical value for CI is 10pF. Series resistor value can be increased to reduce EMI provided that the rise and fall time are still within the specified values.

- 2. Minimize the number of "vias" of the clock traces.

- 3. Route clock traces over a continuous ground plane or over a continuous power plane. Avoid routing clock traces from plane to plane (refer to rule #2).

- 4. Position clock signals away from signals that go to any cables or any external connectors.

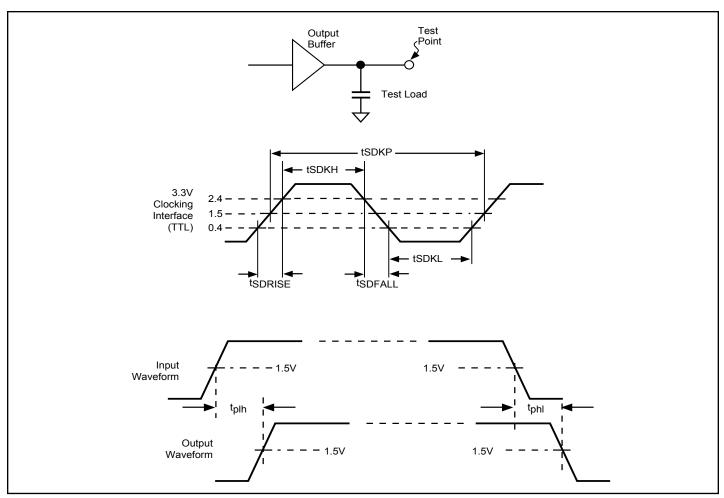

## **PCB Layout Suggestion**

#### Notes:

- 1. This is only a suggested layout. There may be alternate solutions depending on actual PCB design and layout.

- 2. As a general rule, C1-C11 should be placed as close as possible to their respective  $V_{DD}$ .

- 3. Recommended capacitor values:  $C1-C11 = 0.1 \mu F$ , ceramic  $C12 = 22 \mu F$

Figure 2. Design Guidelines

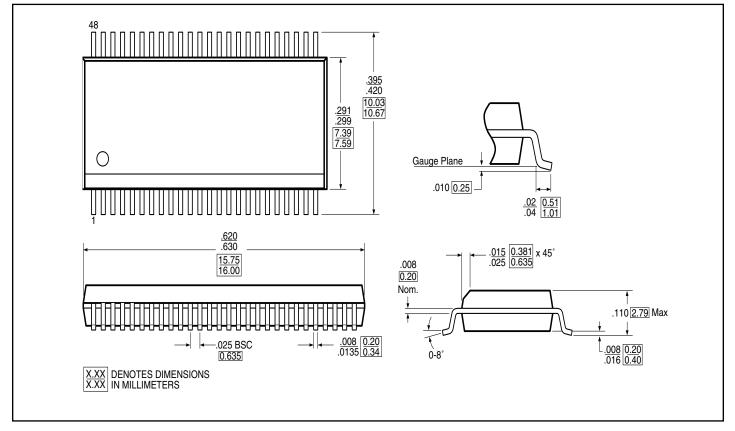

## Packaging Mechanical: 48-Pin SSOP (V)

## **Ordering Information**

| Ordering Code | Package Code | Package Type |

|---------------|--------------|--------------|

| PI6C180V      | V            | 48-pin SSOP  |

Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/