1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

2.5V or 3.3V, 200-MHz, 1:18 Clock Distribution Buffer

#### Features

- 200-MHz clock support

- LVPECL or LVCMOS/LVTTL clock input

- LVCMOS/LVTTL compatible inputs

- 18 clock outputs: drive up to 36 clock lines

- 60 ps typical output-to-output skew

- Dual or single supply operation:

- -3.3V core and 3.3V outputs

- -3.3V core and 2.5V outputs

- -2.5V core and 2.5V outputs

- Pin compatible with MPC940L, MPC9109

- Available in Commercial and Industrial temperature

- 32-pin LQFP package

### Description

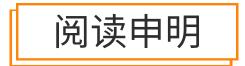

The CY29940 is a low-voltage 200-MHz clock distribution buffer with the capability to select either a differential LVPECL or a LVCMOS/LVTTL compatible input clock. The two clock sources can be used to provide for a test clock as well as the primary system clock. All other control inputs are LVC-MOS/LVTTL compatible. The eighteen outputs are 2.5V or 3.3V LVCMOS/LVTTL compatible and can drive  $50\Omega$  series or parallel terminated transmission lines. For series terminated transmission lines, each output can drive one or two traces giving the device an effective fanout of 1:36. Low output-to-output skews make the CY29940 an ideal clock distribution buffer for nested clock trees in the most demanding of synchronous systems.

### **Pin Description**<sup>[1]</sup>

| Pin                                                                            | Name      | PWR  | I/O   | Description                                                                          |

|--------------------------------------------------------------------------------|-----------|------|-------|--------------------------------------------------------------------------------------|

| 5                                                                              | PECL_CLK  |      | I, PU | PECL Input Clock                                                                     |

| 6                                                                              | PECL_CLK# |      | I, PD | PECL Input Clock                                                                     |

| 3                                                                              | TCLK      |      | I, PD | External Reference/Test Clock Input                                                  |

| 9, 10, 11, 13, 14,<br>15, 18, 19, 20, 22,<br>23, 24, 26, 27, 28,<br>30, 31, 32 | Q(17:0)   | VDDC | 0     | Clock Outputs                                                                        |

| 4                                                                              | TCLK_SEL  |      | I, PD | Clock Select Input. When LOW, PECL clock is selected and when HIGH TCLK is selected. |

| 8, 16, 29                                                                      | VDDC      |      |       | 3.3V or 2.5V Power Supply for Output Clock Buffers                                   |

| 7, 21                                                                          | VDD       |      |       | 3.3V or 2.5V Power Supply                                                            |

| 1, 2, 12, 17, 25                                                               | VSS       |      |       | Common Ground                                                                        |

Note:

1. PD = Internal Pull-Down, PU = Internal Pull-up

## Maximum Ratings<sup>[2]</sup>

| Maximum Input Voltage Relative to V_{SS}: V_{SS} - 0.3V      |

|--------------------------------------------------------------|

| Maximum Input Voltage Relative to $V_{DD}$ : $V_{DD}$ + 0.3V |

| Storage Temperature:65°C to + 150°C                          |

| Operating Temperature:40°C to +85°C                          |

| Maximum ESD Protection2 kV                                   |

| Maximum Power Supply:5.5V                                    |

| Maximum Input Current:+20 mA                                 |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation,  $V_{\text{in}}$  and  $V_{\text{out}}$  should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

| Parameter        | Description                               | Conditions                                              | Min.                  | Тур. | Max.                  | Unit. |

|------------------|-------------------------------------------|---------------------------------------------------------|-----------------------|------|-----------------------|-------|

| V <sub>IL</sub>  | Input Low Voltage                         |                                                         | V <sub>SS</sub>       | _    | 0.8                   | V     |

| V <sub>IH</sub>  | Input High Voltage                        |                                                         | 2.0                   | _    | V <sub>DD</sub>       | V     |

| ۱ <sub>IL</sub>  | Input Low Current <sup>[3]</sup>          |                                                         |                       | _    | -200                  | μA    |

| I <sub>IH</sub>  | Input High Current <sup>[3]</sup>         |                                                         |                       | _    | 200                   | μA    |

| V <sub>PP</sub>  | Peak-to-Peak Input<br>Voltage<br>PECL_CLK |                                                         | 500                   | -    | 1000                  | mV    |

| V <sub>CMR</sub> | Common Mode Range <sup>[4]</sup>          | V <sub>DD</sub> = 3.3V                                  | $V_{DD} - 1.4$        | _    | $V_{DD} - 0.6$        | V     |

|                  | PECL_CLK                                  | V <sub>DD</sub> = 2.5V                                  | V <sub>DD</sub> – 1.0 | -    | V <sub>DD</sub> - 0.6 | V     |

| V <sub>OL</sub>  | Output Low Voltage <sup>[5, 6, 7]</sup>   | I <sub>OL</sub> = 20 mA                                 | -                     | -    | 0.5                   | V     |

| V <sub>OH</sub>  | Output High Voltage <sup>[5, 6, 7]</sup>  | $I_{OH} = -20 \text{ mA}, V_{DDC} = 3.3 \text{V}$       | 2.4                   | -    | -                     | V     |

|                  |                                           | $I_{OH} = -20 \text{ mA}, V_{DDC} = 2.5 \text{V}$       | 1.8                   | _    | _                     | V     |

| I <sub>DDQ</sub> | Quiescent Supply<br>Current               |                                                         | -                     | 5    | 7                     | mA    |

| I <sub>DD</sub>  | Dynamic Supply<br>Current                 | $V_{DD}$ = 3.3V, Outputs @ 150 MHz, CL = 15 pF          | -                     | 285  | -                     | mA    |

|                  |                                           | V <sub>DD</sub> =3.3V, Outputs @ 200 MHz,<br>CL = 15 pF | -                     | 335  | -                     |       |

|                  |                                           | V <sub>DD</sub> =2.5V, Outputs @ 150 MHz,<br>CL = 15 pF | -                     | 200  | _                     |       |

|                  |                                           | $V_{DD}$ =2.5V, Outputs @ 200 MHz, CL = 15 pF           | -                     | 240  | _                     |       |

| Z <sub>out</sub> | Output Impedance                          | V <sub>DD</sub> = 3.3V                                  | 8                     | 12   | 16                    | Ω     |

|                  |                                           | V <sub>DD</sub> = 2.5V                                  | 10                    | 15   | 20                    |       |

| C <sub>in</sub>  | Input Capacitance                         |                                                         | -                     | 4    | -                     | pF    |

Notes:

2.

Multiple Supplies: The Voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required. Inputs have pull-up/pull-down resistors that effect input current. The VCMR is the difference from the most positive side of the differential input signal. Normal operation is obtained when the "High" input is within the VCMR range and the input lies within the VPP specification. Driving series or parallel terminated 50Ω (or 50Ω to VDD/2) transmission lines 3. 4. Outputs driving  $50\Omega$  transmission lines. 5.

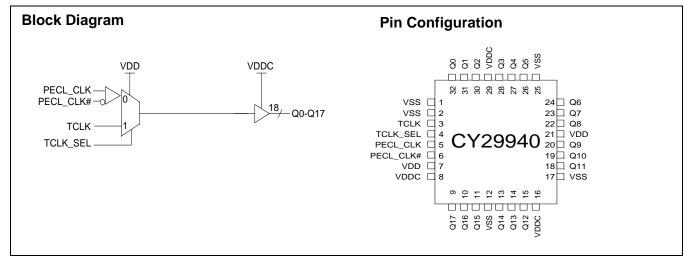

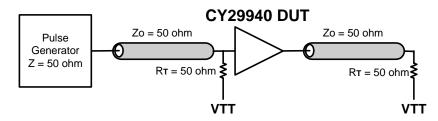

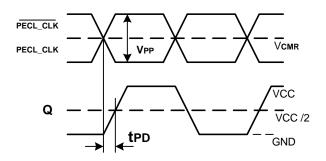

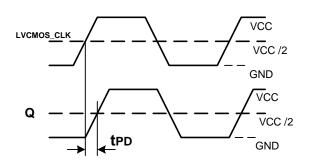

See Figure 1 &2.

50% input duty cycle.

| Parameter                      | Description Conditions                                                                                                                                                         |                                          |                  | Min. | Тур. | Max. | Unit. |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------|------|------|-------|--|

| F <sub>max</sub>               | Input Frequency                                                                                                                                                                |                                          | -                | -    | -    | 200  | MHz   |  |

| t <sub>PD</sub>                | PECL_CLK to Q Delay <sup>[5, 6, 11]</sup><br>=150 MHz</td <td>V<sub>DD</sub> = 3.3V</td> <td>t<sub>PHL</sub></td> <td>2.0</td> <td>_</td> <td>3.2</td> <td rowspan="2">ns</td> | V <sub>DD</sub> = 3.3V                   | t <sub>PHL</sub> | 2.0  | _    | 3.2  | ns    |  |

|                                |                                                                                                                                                                                | 85°C                                     | t <sub>PLH</sub> | 2.1  | -    | 3.4  |       |  |

|                                |                                                                                                                                                                                | V <sub>DD</sub> = 3.3V                   | t <sub>PHL</sub> | 1.9  | -    | 3.1  |       |  |

|                                |                                                                                                                                                                                | 70°C                                     | t <sub>PLH</sub> | 2.0  | -    | 3.2  |       |  |

|                                |                                                                                                                                                                                | $V_{DD} = 2.5V$                          | t <sub>PHL</sub> | 2.5  | -    | 5.2  |       |  |

|                                |                                                                                                                                                                                | 85°C                                     | t <sub>PLH</sub> | 2.6  | -    | 5    |       |  |

|                                |                                                                                                                                                                                | $V_{DD} = 2.5V$                          | t <sub>PHL</sub> | 2.5  | -    | 5    |       |  |

|                                |                                                                                                                                                                                | 70°C                                     | t <sub>PLH</sub> | 2.6  | -    | 5    |       |  |

| t <sub>PD</sub>                | LVCMOS to Q Delay <sup>[5, 6, 11]</sup>                                                                                                                                        | V <sub>DD</sub> = 3.3V                   | t <sub>PHL</sub> | 1.9  | -    | 3    | ns    |  |

|                                | =150 MHz</td <td>85°C</td> <td>t<sub>PLH</sub></td> <td>2.0</td> <td>_</td> <td>3.2</td>                                                                                       | 85°C                                     | t <sub>PLH</sub> | 2.0  | _    | 3.2  |       |  |

|                                |                                                                                                                                                                                | V <sub>DD</sub> = 3.3V<br>70°C           | t <sub>PHL</sub> | 1.8  | -    | 2.9  |       |  |

|                                |                                                                                                                                                                                |                                          | t <sub>PLH</sub> | 1.8  | -    | 3.1  |       |  |

|                                |                                                                                                                                                                                | V <sub>DD</sub> = 2.5V<br>85°C           | t <sub>PHL</sub> | 2.5  | _    | 4    |       |  |

|                                |                                                                                                                                                                                |                                          | t <sub>PLH</sub> | 2.5  | -    | 4    |       |  |

|                                |                                                                                                                                                                                | V <sub>DD</sub> = 2.5V<br>70°C           | t <sub>PHL</sub> | 2.3  | -    | 3.8  |       |  |

|                                |                                                                                                                                                                                |                                          | t <sub>PLH</sub> | 2.3  | _    | 3.8  |       |  |

| tj                             | Total Jitter                                                                                                                                                                   | V <sub>DD</sub> = 3.3V @ 150MHz          |                  | -    | -    | 10   | ps    |  |

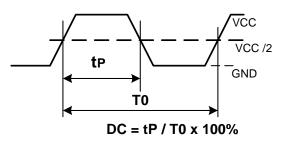

| FoutDC                         | Output Duty Cycle <sup>[5, 6, 7]</sup>                                                                                                                                         | FCLK < 134 MHz<br>FCLK > 134 MHz         |                  | -    | _    | 55   | %     |  |

|                                |                                                                                                                                                                                |                                          |                  | -    | -    | 60   |       |  |

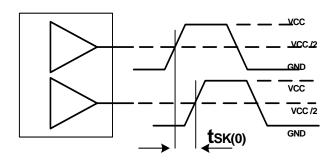

| T <sub>skew</sub>              | Output-to-Output Skew <sup>[5, 6]</sup>                                                                                                                                        | $V_{DD} = 3.3V$                          |                  | -    | 60   | 150  | ps    |  |

|                                |                                                                                                                                                                                | V <sub>DD</sub> = 2.5V                   |                  | -    |      | 200  |       |  |

| T <sub>skew</sub> (pp)         | Part-to-Part Skew <sup>[9]</sup>                                                                                                                                               | PECL, V <sub>DDC</sub> = 3.3V            |                  | -    | -    | 1.4  | ns    |  |

|                                |                                                                                                                                                                                | PECL, V <sub>DDC</sub> = 2.5V            |                  | -    | -    | 2.2  |       |  |

| T <sub>skew</sub> (pp)         | Part-to-Part Skew <sup>[9]</sup>                                                                                                                                               | TCLK, V <sub>DDC</sub> = 3.3V            |                  | -    | -    | 1.2  | ns    |  |

|                                |                                                                                                                                                                                | TCLK, V <sub>DDC</sub> = 2.5V            |                  | -    | -    | 1.7  |       |  |

| T <sub>skew</sub> (pp)         | Part to Part Skew <sup>[10]</sup>                                                                                                                                              | PECL_CLK                                 |                  | -    | -    | 850  | ps    |  |

|                                |                                                                                                                                                                                | TCLK                                     |                  | -    | -    | 750  |       |  |

| t <sub>R</sub> /t <sub>F</sub> | Output Clocks Rise/Fall Time <sup>[5, 6]</sup>                                                                                                                                 | 0.7V to 2.0V,<br>V <sub>DDC</sub> = 3.3V |                  | 0.3  | -    | 1.1  | ns    |  |

|                                |                                                                                                                                                                                | 0.5V to 1.8V,<br>V <sub>DDC</sub> = 2.5V |                  | 0.3  | -    | 1.2  | ]     |  |

## **AC Parameters**<sup>[8]</sup>: $V_{DD} = 3.3V \pm 5\%$ or 2.5V $\pm 5\%$ , $V_{DDC} = 3.3V \pm 5\%$ or 2.5V $\pm 5\%$ , $T_A = -40$ °C to +85°C

Notes:

Parameters are guaranteed by design and characterization. Not 100% tested in production. All parameters specified with loaded outputs.

Across temperature and voltage ranges, includes output skew.

For a specific temperature and voltage, includes output skew

Parameters tested @ 150 MHz.

Figure 1. LVCMOS\_CLK CY29940 Test Reference for V<sub>CC</sub> = 3.3V and V<sub>CC</sub> = 2.5V

Figure 2. PECL\_CLK CY29940 Test Reference for V\_{CC} = 3.3V and V\_{CC} = 2.5V

Figure 3. Propagation Delay (TPD) Test Reference

Figure 4. LVCMOS Propagation Delay (TPD) Test Reference

Figure 5. Output Duty Cycle (FoutDC)

Figure 6. Output-to-Output Skew tsk(0)

# **Ordering Information**

| Part Number | Package Type                | Production Flow            |  |  |  |

|-------------|-----------------------------|----------------------------|--|--|--|

| CY29940AI   | 32 Pin LQFP                 | Industrial, -40°C to +85°C |  |  |  |

| CY29940AIT  | 32 Pin LQFP – Tape and Reel | Industrial, -40°C to +85°C |  |  |  |

| CY29940AC   | 32 Pin LQFP                 | Commercial, 0°C to 70°C    |  |  |  |

| CY29940ACT  | 32 Pin LQFP – Tape and Reel | Commercial, 0°C to 70°C    |  |  |  |

| Lead-free   |                             |                            |  |  |  |

| CY29940AXI  | 32 Pin LQFP                 | Industrial, -40°C to +85°C |  |  |  |

| CY29940AXIT | 32 Pin LQFP – Tape and Reel | Industrial, -40°C to +85°C |  |  |  |

| CY29940AXC  | 32 Pin LQFP                 | Commercial, 0°C to 70°C    |  |  |  |

| CY29940AXCT | 32 Pin LQFP – Tape and Reel | Commercial, 0°C to 70°C    |  |  |  |

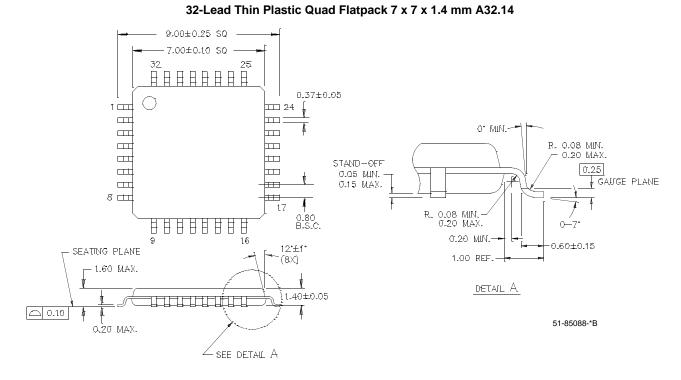

## **Package Drawing and Dimensions**

All product and company names mentioned in this document may be the trademarks of their respective owners.

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress all risk of such use and in doing so indemnifies Cypress against all charges.

# **Document History Page**

| Document Title: CY29940 2.5V or 3.3V, 200-MHz, 1:18 Clock Distribution Buffer<br>Document Number: 38-07283 |         |               |                    |                                                                                                                                                                                                                              |  |  |

|------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| REV.                                                                                                       | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                        |  |  |

| **                                                                                                         | 111094  | 02/01/02      | BRK                | New data sheet                                                                                                                                                                                                               |  |  |

| *A                                                                                                         | 116776  | 08/15/02      | HWT                | Incorporate results of final characterization using corporate methods, added<br>output impedance on page 3 and added output duty cycle on page 4.<br>Add commercial temperature range in the ordering information on page 6. |  |  |

| *В                                                                                                         | 122875  | 12/21/02      | RBI                | Add power up requirements to maximum rating information                                                                                                                                                                      |  |  |

| *C                                                                                                         | 448379  | See ECN       | RGL                | Add typical value for output-to-output skew<br>Add Lead-free devices                                                                                                                                                         |  |  |