1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

www.ti.com

SBES016-MARCH 2009

# CCD Analog Front-End with Timing Generator and Vertical Driver for Digital Cameras

Check for Samples: VSP01M01, VSP01M02

# FEATURES

- CCD Signal Processing:

- 36-MHz Correlated Double Sampling (CDS)

- 16-Bit Analog-to Digital Conversion:

- 36-MHz Conversion Rate

- No Missing Codes Ensured

- 80-dB Input-Referred SNR (at 12-dB Gain)

- Programmable Black Level Clamping

- Programmable Gain Amplifier (PGA):

- -9 dB to +44 dB

-3 dB to +18 dB by Analog Front Gain

-6 dB to +26 dB by Digital Gain

- Timing Generator:

- Fully Programmable V<sub>RATE</sub> Timing by Serial I/O

- Default Timing Supports Standard Operation

- Flexible V<sub>RATE</sub> Pin Assignment

- HD/VD Master or Slave Mode

- External Trigger, Strobe Function Support

- Flexible Draft or Pixel Summing Operation

- RG and HG Driver:

- Programmable Drivability Control

- Two Horizontal Transfer Independent Drivers

- One Reset Gate Driver

- CCD Horizontal High-Speed Clock Phase Control:

- Fine Step: 0.28 ns

- Wide Step: 1/3 Pixel Rate

- Vertical CCD Driver:

- 8-Channel V<sub>DRIVER</sub> with Sub-Driver

- Supports Three-Field CCD Driving

- Three Level Drivers (V<sub>TRANSFER</sub>) × 5

- Two Level Drivers ( $V_{\text{TRANSFER}}$ ) × 3

- Two Level Drivers (E<sub>SHUTTER</sub>) × 1

- 450 pF to 1890 pF with 60  $\Omega$  to 240  $\Omega$

- Flexible Voltage Operation:

- AFET + TG: 2.7 V to 3.6 V

- VL: -5.0 V to -9.0 V

- VM: GND

- VH: 11.5 V to 15.5 V

- Low Power: 139 mW at 3.0 V, 36 MHz

- Stand-By + Power-Save Mode: 36 mW

- Stand-By Mode (MCK Off): 10 mW

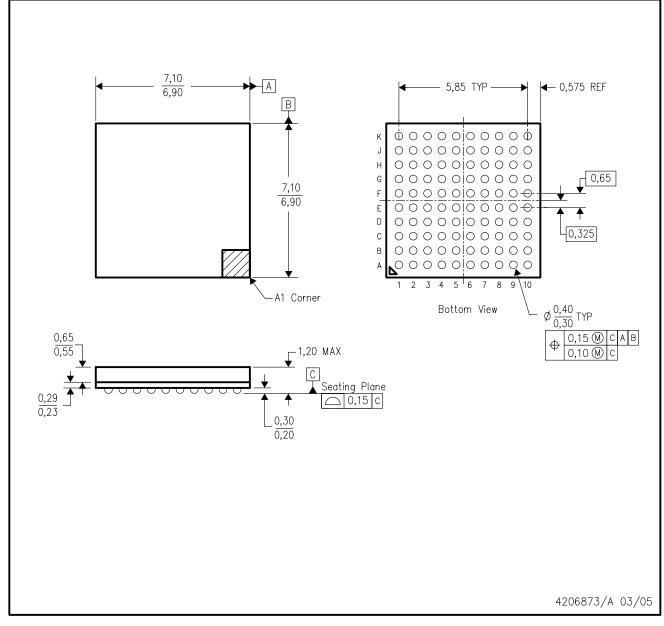

- BGA-100 Package

# DESCRIPTION

The VSP01M01 and VSP01M02 are complete mixedsignal ICs for charge-coupled device (CCD) signal processing with a built-in CCD timing generator, analog-to-digital converter (ADC), and CCD vertical driver. The AFE CCD channel has correlated double sampling to extract image information from the CCD output signal. Signal paths have gains ranging from -9 dB to +44 dB. The black level clamping circuit enables accurate black reference level and quick black level recovery after gain changes. An input signal clamp with CDS offset adjustment function is available. The system synchronizes the master clock, horizontal driver (HD), and vertical driver (VD). The VSP01M01 and VSP01M02 support all signal terminals required by CCD architecture. The RG driver, HG driver, and vertical driver synchronize the ADC clock phase in order to realize ideal performance.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

#### Not Recommended for New Designs

#### SBES016-MARCH 2009

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

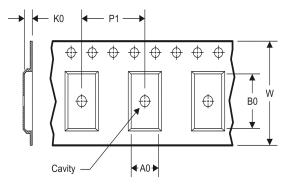

#### Table 1. PACKAGE/ORDERING INFORMATION<sup>(1)</sup>

| PRODUCT                    | PACKAGE-<br>LEAD                 | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|----------------------------|----------------------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| VSP01M01ZWD <sup>(2)</sup> | BCA 100                          | ZWD                   | –25°C to +85°C                    | VSP01M01           | VSP01M01ZWD        | Tray, 360                    |

| VSPUTIVIUTZVUD(=/          | P01M01ZWD <sup>(2)</sup> BGA-100 |                       | -25 °C 10 +65 °C                  | VSPUTMUT           | VSP01M01ZWDR       | Tape and Reel                |

| VSP01M01GWD                | BCA 100                          | CWD                   | –25°C to +85°C                    | VSP01M01           | VSP01M01GWD        | Tray, 360                    |

| VSPUTIVIUTGVUD             | 1GWD BGA-100 GWD                 |                       | -25 °C 10 +65 °C                  | VSPUTMUT           | VSP01M01GWDR       | Tape and Reel                |

| VSP01M02ZWD <sup>(2)</sup> |                                  |                       |                                   | VSP01M02ZWD        | Tray, 360          |                              |

| v 5PU 11VIU2ZVVD(=)        | BGA-100                          | ZWD                   | –25°C to +85°C                    | VSP01M02           | VSP01M02ZWDR       | Tape and Reel                |

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

(2) The package is Pb-free.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

| PARAMETER                                |             | VSP01M01, VSP01M02   | UNIT |

|------------------------------------------|-------------|----------------------|------|

|                                          | AVDD        | -0.3 to +4.0         | V    |

|                                          | DRVDD       | -0.3 to +4.0         | V    |

| Supply voltage                           | VDD5        | -0.3 to +6.0         | V    |

|                                          | VL          | GND to -10           | V    |

|                                          | VH          | VL + 26              | V    |

| Supply voltage differences               | AVDD, DRVDD | ±0.1                 | V    |

| Ground voltage differences               | VSS         | ±0.1                 | V    |

| Digital input voltage                    |             | -0.3 to (DVDD + 0.3) | V    |

| Analog input voltage                     |             | -0.3 to (AVDD + 0.3) | V    |

| Input current (any pins except supplies) |             | ±10                  | mA   |

| Ambient temperature under bias           |             | -25 to +85           | °C   |

| Storage temperature                      |             | -55 to +125          | °C   |

| Junction temperature                     |             | +150                 | °C   |

| Package temperature (IR reflow, peak)    |             | +250                 | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. Exposure to absolutemaximum-rated conditions for extended periods may affect device reliability. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.

# **RECOMMENDED OPERATING CONDITIONS**

Over operating free-air temperature range, unless otherwise noted.

| PARAMETER                                     |      | MIN  | TYP  | МАХ  | UNIT |

|-----------------------------------------------|------|------|------|------|------|

| Analog supply voltage                         | AVDD | 2.7  | 3.0  | 3.6  | V    |

|                                               | DVDD | 2.7  | 3.0  | 3.6  | V    |

| Digital supply voltage                        | VDD5 | 3.0  |      | 5.5  | V    |

|                                               | VL   | -9.0 |      | -5.0 | V    |

| Driver supply voltage                         | VH   | 11.5 |      | 15.5 | V    |

| Digital input logic family                    |      |      | CMOS |      |      |

|                                               | MCK  | 12   |      | 36   | MHz  |

| Digital input clock frequency                 | SCLK |      |      | 20   | MHz  |

| Digital output load capacitance               |      |      |      | 10   | pF   |

| Operating free-air temperature T <sub>A</sub> |      | -25  |      | +85  | °C   |

SBES016-MARCH 2009

www.ti.com

#### **ELECTRICAL CHARACTERISTICS**

All specifications at  $T_A = +25^{\circ}$ C, all power supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

|                                        |                                                | VSPC    | 01M01ZWD<br>01M01GWD<br>01M02ZWD | ,    |        |  |

|----------------------------------------|------------------------------------------------|---------|----------------------------------|------|--------|--|

| PARAMETER                              | TEST CONDITIONS                                | MIN TYP |                                  | MAX  | UNIT   |  |

| RESOLUTION                             |                                                |         |                                  |      |        |  |

| Desclution                             | VSP01M01 only                                  |         | 10                               |      | Bits   |  |

| Resolution                             | VSP01M02 only                                  |         | 12                               |      | Bits   |  |

| CONVERSION/CLOCK RATE                  |                                                |         |                                  |      |        |  |

| Conversion/clock rate                  |                                                |         |                                  | 36   | MHz    |  |

| ANALOG INPUT (CCDIN)                   |                                                |         |                                  |      |        |  |

| Input signal level for full-scale out  | CDS gain = 0 dB, DPGA gain = 0 dB              |         |                                  | 1000 | mV     |  |

| Maximum input range                    | CDS gain = $-3$ dB, DPGA gain = 0 dB           |         |                                  | 1300 | mV     |  |

| Input capacitance                      |                                                |         | 15                               |      | pF     |  |

| Input limit                            |                                                | -0.3    |                                  | 3.3  | V      |  |

| TRANSFER CHARACTERISTICS               |                                                |         |                                  |      |        |  |

| Differential nonlinearity D            | L CDS gain = 0 dB, DPGA gain = 0 dB            |         | ±0.25                            |      | LSB    |  |

| Integral nonlinearity I                | L CDS gain = 0 dB, DPGA gain = 0 dB            |         | ±0.5                             |      | LSB    |  |

| No missing codes                       |                                                |         | Ensured                          |      |        |  |

| Step response settling time            | Full-scale step input                          |         | 1                                |      | Pixel  |  |

| Overload recovery time                 | Step input from 1.8 V to 0 V                   |         | 2                                |      | Pixels |  |

| Data latency                           |                                                |         | 9                                |      | Clocks |  |

| Circulto aciac actic (1)               | Grounded input capacitor, PGA gain = 0 dB      |         | 76                               |      | dB     |  |

| Signal-to-noise ratio <sup>(1)</sup>   | Grounded input capacitor, analog gain = +12 dB |         | 68                               |      | dB     |  |

| CCD offset correction range            |                                                | -200    |                                  | 200  | mV     |  |

| INPUT CLAMP                            |                                                |         |                                  |      |        |  |

| Clamp on-resistance                    |                                                |         | 400                              |      | Ω      |  |

| Clamp level                            |                                                |         | 1.5                              |      | V      |  |

| PROGRAMMABLE ANALOG FRONT G            | AIN (CDS)                                      |         |                                  |      |        |  |

| Minimum gain                           | Gain code = 111b                               |         | -3                               |      | dB     |  |

| Default gain                           | Gain code = 000b                               |         | 0                                |      | dB     |  |

| Medium gain 1                          | Gain code = 001b                               |         | 6                                |      | dB     |  |

| Medium gain 2                          | Gain code = 010b                               |         | 12                               |      | dB     |  |

| Maximum gain                           | Gain code = 011b                               |         | 18                               |      | dB     |  |

| Gain control error                     |                                                |         | 0.5                              |      | dB     |  |

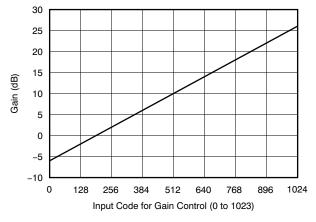

| PROGRAMMABLE DIGITAL GAIN (DPO         | A)                                             |         |                                  |      |        |  |

| Programmable gain range                |                                                | -6      |                                  | 26   | dB     |  |

| Gain step                              |                                                |         | 0.03125                          |      | dB     |  |

| OPTICAL BLACK CLAMP LOOP               |                                                |         |                                  |      |        |  |

| Control DAC resolution                 |                                                |         | 10                               |      | Bits   |  |

| Loop time constant                     |                                                |         | 40.7                             |      | μs     |  |

|                                        | Programmable range of clamp level              | 16      |                                  | 78   | LSB    |  |

| Optical black clamp level (VSP01M01 on |                                                |         | 32                               |      | LSB    |  |

| - · · ·                                | OB level program step                          |         | 2                                |      | LSB    |  |

|                                        | Programmable range of clamp level              | 64      |                                  | 312  | LSB    |  |

| Optical black clamp level (VSP01M02 on |                                                |         | 128                              |      | LSB    |  |

|                                        | OB level program step                          |         | 8                                |      | LSB    |  |

(1) SNR = 20 log (full-scale voltage/rms noise).

www.ti.com

#### SBES016-MARCH 2009

# **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = +25^{\circ}$ C, all power supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

|                                                     |                  |                                                                               | VSP0 <sup>2</sup> | 1M01ZWD<br>1M01GWD<br>1M02ZWD | ,        |      |

|-----------------------------------------------------|------------------|-------------------------------------------------------------------------------|-------------------|-------------------------------|----------|------|

| PARAMETER                                           |                  | TEST CONDITIONS                                                               | MIN TYP MAX       |                               | MAX      | UNIT |

| DIGITAL INPUTS                                      |                  | •                                                                             |                   |                               |          |      |

| Logic family                                        |                  |                                                                               |                   | CMOS                          |          |      |

|                                                     | V <sub>T+</sub>  | Low to high threshold voltage                                                 |                   | 1.7                           |          | V    |

| Input voltage                                       | V <sub>T</sub> - | High to low threshold voltage                                                 |                   | 1.0                           |          | V    |

|                                                     | I <sub>IH</sub>  | Logic high, V <sub>IN</sub> = +3 V                                            |                   |                               | ±20      | μA   |

| Input current                                       | ۱ <sub>۱۲</sub>  | Logic low, V <sub>IN</sub> = 0 V                                              |                   |                               | ±20      | μA   |

| Input capacitance                                   |                  | -                                                                             |                   | 5                             |          | pF   |

| Maximum input voltage                               |                  |                                                                               | -0.3              | DVE                           | DD + 0.3 | V    |

| DIGITAL OUTPUTS (DATA)                              | I                | I                                                                             |                   |                               |          |      |

| Logic family                                        |                  |                                                                               |                   | CMOS                          |          |      |

| Logic coding                                        |                  |                                                                               | Straight          | t Binary                      |          |      |

|                                                     | V <sub>OH</sub>  | Logic high                                                                    | 2.4               |                               |          | V    |

| Output voltage                                      | V <sub>OL</sub>  | Logic low                                                                     |                   |                               | 0.4      | V    |

|                                                     |                  | Output data delay code = 00b                                                  |                   | 0                             |          | ns   |

|                                                     | -                | Output data delay code = 01b                                                  |                   | 2                             |          | ns   |

| Additional output data delay                        | -                | Output data delay code = 10b                                                  |                   | 4                             |          | ns   |

|                                                     | -                | Output data delay code = 11b                                                  |                   | 6                             |          | ns   |

| H <sub>DRIVER</sub> OUTPUTS                         |                  |                                                                               |                   |                               |          |      |

|                                                     |                  | Logic high ( $V_{OH}$ ) $I_{OH}$ = 0 mA                                       | VDD5              | 5 – 0.05                      |          | V    |

| Output voltage                                      | RG, HL           | Logic high ( $V_{OH}$ ) $I_{OH} = -6.8 \text{ mA}$                            | VDD               | 05 – 0.6                      |          | V    |

|                                                     | -                | Logic low ( $V_{OL}$ ) $I_{OL} = 6.8 \text{ mA}$                              |                   |                               | 0.4      | V    |

|                                                     |                  | Logic high ( $V_{OH}$ ) $I_{OH} = 0 \text{ mA}$                               | VDD5              | 5 – 0.05                      |          | V    |

| Output voltage<br>(HG1A, HG1B, HG2A, HG2B)          |                  | Logic high (V <sub>OH</sub> ) $I_{OH}$ = -13.6 mA (max),<br>-6.8 mA (min)     | VDD               | 95 – 0.6                      |          | V    |

| (1017, 1010, 1027, 1020)                            | -                | Logic low (V <sub>OL</sub> ) I <sub>OL</sub> = 13.6 mA (max),<br>6.8 mA (min) |                   |                               | 0.4      | V    |

| TG OUTPUTS                                          |                  |                                                                               |                   |                               |          |      |

| Output voltage (V0N-V12N, P0-F                      |                  | Logic high (V <sub>OH</sub> ) $I_{OH} = -1.7 \text{ mA}$                      | DVD               | D – 0.6                       |          | V    |

| FIELD, STROBE, MSHUT, SUB<br>SUBSW2, ADCCK, HD, VD) | SW1,             | Logic low (V <sub>OL</sub> ) $I_{OL}$ = 1.7 mA                                |                   |                               | 0.4      | V    |

| TP output voltage (TPP, TPD)                        |                  | Logic high (V <sub>OH</sub> ) $I_{OH} = -1.7 \text{ mA}$                      | DVD               | D – 0.6                       |          | V    |

| in output voltage (in i , IFD)                      |                  | Logic low (V <sub>OL</sub> ) $I_{OL}$ = 1.7 mA                                |                   |                               | 0.4      | V    |

| V <sub>DRIVER</sub> OUTPUTS                         | · · · · ·        |                                                                               |                   |                               |          |      |

|                                                     | I <sub>OL</sub>  | V1, V2, V3A, V3B, V4, V5A, V5B, V6 = -8.1 V                                   | 10                |                               |          | mA   |

| Output current                                      | I <sub>OM1</sub> | V1, V2, V3A, V3B, V4, V5A, V5B, V6 = -0.2 V                                   |                   |                               | -5.0     | mA   |

| (V1, V2, V3A, V3B, V4, V5A,<br>V5B, V6)             | I <sub>OM2</sub> | V1, V3A, V3B, V5A, V5B = 0.2 V                                                | 5                 |                               |          | mA   |

| (VL = -9.0 V, VM = 0 V,                             | I <sub>OH</sub>  | V1, V3A, V3B, V5A, V5B = 14.55 V                                              |                   |                               | -7.2     | mA   |

| VH = 15.5 V)                                        | I <sub>OSL</sub> | SUB = -8.1 V                                                                  | 5.4               |                               |          | mA   |

|                                                     | I <sub>OSH</sub> | SUB = 14.55 V                                                                 |                   |                               | -4       | mA   |

#### www.ti.com

## **ELECTRICAL CHARACTERISTICS (continued)**

All specifications at  $T_A = +25^{\circ}$ C, all power supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

|                                   |                                |                                              | VSP01M01ZWD,<br>VSP01M01GWD,<br>VSP01M02ZWD |       |      |      |  |

|-----------------------------------|--------------------------------|----------------------------------------------|---------------------------------------------|-------|------|------|--|

| PARAMETER                         |                                | TEST CONDITIONS                              | MIN                                         | TYP   | MAX  | UNIT |  |

| POWER SUPPLY                      |                                |                                              |                                             |       | ·    |      |  |

|                                   | $AV_{DD}$                      |                                              | 2.7                                         | 3.0   | 3.6  | V    |  |

|                                   | $DV_DD$                        |                                              | 2.1                                         | 3.0   | 3.0  | v    |  |

| Supply voltage                    | VDD5                           | for HG1A, HG1B, HG2A, HG2B, HL, RG           | 3.0                                         |       | 5.5  | V    |  |

|                                   | VL                             | for V1, V2, V3A, V3B, V4, V5A, V5B, V6       | -9                                          |       | -5   | V    |  |

|                                   | VH                             | for V1, V2, V3A, V3B, V4, V5A, V5B, V6       | 11.5                                        |       | 15.5 | V    |  |

| Power dissipation                 | AFE                            |                                              |                                             | 85    |      | mW   |  |

| Power dissipation                 | TG + H,<br>R <sub>DRIVER</sub> | Normal operation mode: no CCD load           |                                             | 50    |      | mW   |  |

| Power dissipation                 | V <sub>DRIVER</sub>            | (at 3.0 V, 38 MHz)                           |                                             | 4     |      | mW   |  |

| Power dissipation (total) without | t CCD load                     |                                              |                                             | 139   |      | mW   |  |

| Demon disain ation (tatal)        |                                | Standby + power-save mode (at 3.0 V, 38 MHz) |                                             | 36    |      | mW   |  |

| Power dissipation (total)         |                                | Master clock off mode (at 3.0 V)             |                                             | 10    |      | mW   |  |

| TEMPERATURE RANGE                 |                                |                                              |                                             |       |      |      |  |

| Operating temperature             |                                |                                              | -25                                         |       | +85  | °C   |  |

| Thermal resistance                | $\theta_{JA}$                  | At 165 mW power dissipation with load        |                                             | 46.18 |      | °C/W |  |

# SWITCHING CHARACTERISTICS

All specifications at  $T_A = +25^{\circ}$ C, all power supply voltages = +3.0 V, and conversion rate = 36 MHz, unless otherwise noted.

| PARAMETER              |                  | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|------------------------|------------------|---------------------|-----|-----|-----|------|

|                        | t <sub>PLM</sub> |                     |     | 15  | 100 | ns   |

|                        | t <sub>PMH</sub> |                     |     | 20  | 100 | ns   |

| Propagation delay time | t <sub>PLH</sub> |                     |     | 20  | 100 | ns   |

| Fropagation delay time | t <sub>PML</sub> |                     |     | 15  | 50  | ns   |

|                        | t <sub>PHM</sub> |                     |     | 30  | 50  | ns   |

|                        | t <sub>PHL</sub> |                     |     | 30  | 50  | ns   |

|                        | t <sub>TLM</sub> | $VL\toVM$           |     |     | 300 | ns   |

| Rise time              | t <sub>TMH</sub> | $VM\toVH$           |     |     | 300 | ns   |

|                        | t <sub>TLH</sub> | $VL\toVH$           |     |     | 300 | ns   |

|                        | t <sub>TML</sub> | $VM \rightarrow VL$ |     |     | 300 | ns   |

| Fall time              | t <sub>THM</sub> | $VH \rightarrow VM$ |     |     | 300 | ns   |

|                        | t <sub>THL</sub> | $VH\toVL$           |     |     | 300 | ns   |

|                        | V <sub>CLH</sub> |                     |     |     | 2.0 | V    |

|                        | V <sub>CLL</sub> |                     |     |     | 2.0 | V    |

| Output noise voltage   | V <sub>CMH</sub> |                     |     |     | 2.0 | V    |

|                        | V <sub>CML</sub> |                     |     |     | 2.0 | V    |

|                        | $V_{CHL}$        |                     |     |     | 2.0 | V    |

TEXAS INSTRUMENTS

SBES016-MARCH 2009

www.ti.com

#### **PIN CONFIGURATION**

#### VSP01M01ZWD, VSP01M01GWD BGA PACKAGE (BOTTOM VIEW)

|   |       |        |                   |        | •      | ,      |       |      |      |       |

|---|-------|--------|-------------------|--------|--------|--------|-------|------|------|-------|

|   | 1     | 2      | 3                 | 4      | 5      | 6      | 7     | 8    | 9    | 10    |

| А | DAC1  | V12N   | CH2N              | V6N    | NC     | V1N    | VON   | NC   | NC   | CH0N  |

| В | DAC2  | V11N   | V10N              | V8N    | V7N    | CH1N   | NC    | CH3N | B8   | NC    |

| с | CCDIN | CCDGND | V9N               | V3N    | V4N    | V2N    | CH5N  | B9   | B6   | B7    |

| D | СОВ   | BYP    | BYP2              | AVDD   | DVSS   | DVSS   | DRVDD | CH4N | B4   | B5    |

| Е | СМ    | BYPM   | REFN              | AVDD   | AVSS   | AVSS   | DRVDD | B3   | B1   | B2    |

| F | REFP  | V5N    | NC                | AVDD   | AVSS   | AVSS   | DRVDD | V2   | B0   | SUB   |

| G | BYPD  | V3B    | TPD               | DVSS   | VL     | VH     | VDD5  | VSS5 | VSS5 | NC    |

| н | TPP   | SYSRST | R <sub>LOAD</sub> | V5A    | V3A    | STROBE | VDD5  | V6   | RG   | H1A   |

| J | SDATA | SCLK   | TRIG              | VD     | SUBSW1 | MSHUT  | SUBN  | HL   | V4   | ADCCK |

| к | MCK   | CS     | HD                | SUBSW2 | V1     | FIELD  | V5B   | H2A  | H1B  | H2B   |

## **PIN CONFIGURATION**

#### VSP01M02ZWD BGA PACKAGE (BOTTOM VIEW)

|   | 1     | 2      | 3                 | 4      | 5      | 6      | 7     | 8    | 9    | 10    |

|---|-------|--------|-------------------|--------|--------|--------|-------|------|------|-------|

| А | DAC1  | V12N   | CH2N              | V6N    | NC     | V1N    | VON   | NC   | NC   | CH0N  |

| В | DAC2  | V11N   | V10N              | V8N    | V7N    | CH1N   | NC    | CH3N | B10  | B1    |

| С | CCDIN | CCDGND | V9N               | V3N    | V4N    | V2N    | CH5N  | B11  | B8   | B9    |

| D | СОВ   | BYP    | BYP2              | AVDD   | DVSS   | DVSS   | DRVDD | CH4N | B6   | B7    |

| Е | СМ    | BYPM   | REFN              | AVDD   | AVSS   | AVSS   | DRVDD | B5   | B3   | B4    |

| F | REFP  | V5N    | NC                | AVDD   | AVSS   | AVSS   | DRVDD | V2   | B2   | SUB   |

| G | BYPD  | V3B    | TPD               | DVSS   | VL     | VH     | VDD5  | VSS5 | VSS5 | B0    |

| н | TPP   | SYSRST | R <sub>LOAD</sub> | V5A    | V3A    | STROBE | VDD5  | V6   | RG   | H1A   |

| J | SDATA | SCLK   | TRIG              | VD     | SUBSW1 | MSHUT  | SUBN  | HL   | V4   | ADCCK |

| к | MCK   | CS     | HD                | SUBSW2 | V1     | FIELD  | V5B   | H2A  | H1B  | H2B   |

EXAS STRUMENTS **VSP01M01** VSP01M02

SBES016-MARCH 2009

www.ti.com

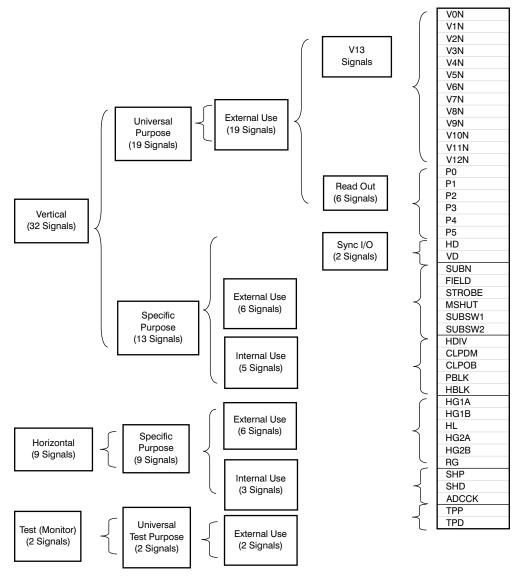

#### Table 2. TERMINAL FUNCTIONS

| TERMINAL |     |                     |                                             |  |  |

|----------|-----|---------------------|---------------------------------------------|--|--|

| NAME     | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                                 |  |  |

| DAC1     | A1  | DO                  | DAC1 output                                 |  |  |

| V12N     | A2  | DO                  | Vertical rate signal 12N                    |  |  |

| CH2N     | A3  | DO                  | Universal vertical rate signal 2N (for V3A) |  |  |

| V6N      | A4  | DO                  | Vertical rate signal 6N (for V6)            |  |  |

| NC       | A5  | —                   | No connection                               |  |  |

| V1N      | A6  | DO                  | Vertical rate signal 1N (for V1)            |  |  |

| VON      | A7  | DO                  | Vertical rate signal 0N                     |  |  |

| NC       | A8  | —                   | No connection                               |  |  |

| NC       | A9  | _                   | No connection                               |  |  |

| CH0N     | A10 | DO                  | Universal vertical rate signal 0N           |  |  |

| DAC2     | B1  | DO                  | DAC2 output                                 |  |  |

| V11N     | B2  | DO                  | Vertical rate signal 11N                    |  |  |

| V10N     | B3  | DO                  | Vertical rate signal 10N                    |  |  |

| V8N      | B4  | DO                  | Vertical rate signal 8N                     |  |  |

| V7N      | B5  | DO                  | Vertical rate signal 7N                     |  |  |

| CH1N     | B6  | DO                  | Universal vertical rate signal 1N (for V1)  |  |  |

| NC       | B7  | _                   | No connection                               |  |  |

| CH3N     | B8  | DO                  | Universal vertical rate signal 3N (for V5A) |  |  |

| B8       | B9  | DO                  | Data out bit 8 (VSP01M01 only)              |  |  |

| B10      | B9  | DO                  | Data out bit 10 (VSP01M02 only)             |  |  |

| NC       | B10 |                     | No connection (VSP01M01 only)               |  |  |

| B1       | B10 | DO                  | Data out bit 1 (VSP01M02 only)              |  |  |

| CCDIN    | C1  | AI                  | CCD signal input                            |  |  |

| CCDGND   | C2  | AI                  | CCD signal input ground                     |  |  |

| V9N      | C3  | DO                  | Vertical rate signal 9N                     |  |  |

| V3N      | C4  | DO                  | Vertical rate signal 3N (for V3A, V3B)      |  |  |

| V4N      | C5  | DO                  | Vertical rate signal 4N (for V4)            |  |  |

| V2N      | C6  | DO                  | Vertical rate signal 2N (for V2)            |  |  |

| CH5N     | C7  | DO                  | Universal vertical rate signal 5N (for V5B) |  |  |

| B9       | C8  | DO                  | Data out bit 9 (MSB) (VSP01M01 only)        |  |  |

| B11      | C8  | DO                  | Data out bit 11 (MSB) (VSP01M02 only)       |  |  |

| B6       | C9  | DO                  | Data out bit 6 (VSP01M01 only)              |  |  |

| B8       | C9  | DO                  | Data out bit 8 (VSP01M02 only)              |  |  |

| B7       | C10 | DO                  | Data out bit 7 (VSP01M01 only)              |  |  |

| B9       | C10 | DO                  | Data out bit 9 (VSP01M02 only)              |  |  |

| СОВ      | D1  | AO                  | OB loop feedback capacitor <sup>(2)</sup>   |  |  |

| BYP      | D2  | AO                  | Internal reference <sup>(3)</sup>           |  |  |

| BYP2     | D3  | AO                  | Internal reference <sup>(4)</sup>           |  |  |

| AVDD     | D4  | Р                   | Analog power supply                         |  |  |

| DVSS     | D5  | Р                   | Ground                                      |  |  |

| DVSS     | D6  | Р                   | Ground                                      |  |  |

(1) Designators by type: P: power-supply and ground, DI: digital input, DO: digital output, DI/O: digital input and output, AI: analog input, AO: analog output, and VDO:  $V_{DRIVER}$  digital output. Should be connected to ground with a bypass capacitor. The recommended value is 0.1 µF to 0.22 µF; however, actual value depends

(2) on the application environment. Refer to the OB Loop and OB Clamp Level section for more detail.

Should be connected to ground with a bypass capacitor (0.1 µF). Refer to the Voltage Reference section for more detail. (3)

Should be connected to ground with a bypass capacitor. The recommended value is 400 pF to 1000 pF; however, actual value depends (4) on the application environment. Refer to the Voltage Reference section for more detail.

Copyright © 2009, Texas Instruments Incorporated

www.ti.com

SBES016-MARCH 2009

#### Table 2. TERMINAL FUNCTIONS (continued)

| TERMINAL |     |                     |                                                  |

|----------|-----|---------------------|--------------------------------------------------|

| NAME     | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                                      |

| DRVDD    | D7  | Р                   | Digital output power supply                      |

| CH4N     | D8  | DO                  | Universal vertical rate signal 4N (for V3B)      |

| B4       | D9  | DO                  | Data out bit 4 (VSP01M01 only)                   |

| B6       | D9  | DO                  | Data out bit 6 (VSP01M02 only)                   |

| B5       | D10 | DO                  | Data out bit 5 (VSP01M01 only)                   |

| B7       | D10 | DO                  | Data out bit 7 (VSP01M02 only)                   |

| СМ       | E1  | AO                  | Internal reference <sup>(3)</sup>                |

| BYPM     | E2  | AO                  | Internal reference <sup>(4)</sup>                |

| REFN     | E3  | AO                  | Internal reference <sup>(3)</sup>                |

| AVDD     | E4  | Р                   | Analog power supply                              |

| AVSS     | E5  | Р                   | Ground                                           |

| AVSS     | E6  | Р                   | Ground                                           |

| DRVDD    | E7  | Р                   | Digital output power supply                      |

| B3       | E8  | DO                  | Data out bit 3 (VSP01M01 only)                   |

| B5       | E8  | DO                  | Data out bit 5 (VSP01M02 only)                   |

| B1       | E9  | DO                  | Data out bit 1 (VSP01M01 only)                   |

| B3       | E9  | DO                  | Data out bit 3 (VSP01M02 only)                   |

| B2       | E10 | DO                  | Data out bit 2 (VSP01M01 only)                   |

| B4       | E10 | DO                  | Data out bit 4 (VSP01M02 only)                   |

| REFP     | F1  | AO                  | Internal reference <sup>(5)</sup>                |

| V5N      | F2  | DO                  | Vertical rate signal 5N (for V5A, V5B)           |

| NC       | F3  | _                   | No connection                                    |

| AVDD     | F4  | Р                   | Analog power supply                              |

| AVSS     | F5  | Р                   | Ground                                           |

| AVSS     | F6  | Р                   | Ground                                           |

| DRVDD    | F7  | Р                   | Digital output power supply                      |

| V2       | F8  | VDO                 | V <sub>DRIVER</sub> out 2                        |

| B0       | F9  | DO                  | Data out bit 0 (LSB) (VSP01M01 only)             |

| B2       | F9  | DO                  | Data out bit 2 (VSP01M02 only)                   |

| SUB      | F10 | VDO                 | V <sub>DRIVER</sub> out for CCD electric shutter |

| BYPD     | G1  | AO                  | DLL bypass <sup>(6)</sup>                        |

| V3B      | G2  | VDO                 | V <sub>DRIVER</sub> out 3B                       |

| TPD      | G3  | DO                  | Test pin for SHD, CLPDM, HDIV                    |

| DVSS     | G4  | Р                   | Ground                                           |

| VL       | G5  | Р                   | V <sub>DRIVER</sub> power supply                 |

| VH       | G6  | Р                   | V <sub>DRIVER</sub> power supply                 |

| VDD5     | G7  | Р                   | Digital power supply                             |

| VSS5     | G8  | Р                   | Digital ground                                   |

| VSS5     | G9  | P                   | Digital ground                                   |

| NC       | G10 | _                   | No connection (VSP01M01 only)                    |

| B0       | G10 | DO                  | Data out bit 0 (LSB) (VSP01M02 only)             |

| TPP      | H1  | DO                  | Test pin for SHP, CLPOB, PBLK, HBLK              |

| SYSRST   | H2  | DI                  | Asynchronous reset                               |

|          |     |                     | -,                                               |

(5)

Should be connected to ground with a bypass capacitor (0.1  $\mu$ F). Refer to the *Voltage Reference* section for more detail. Should be connected to ground with a bypass capacitor. The recommended value is 1000 pF to 0.1  $\mu$ F; however, actual value depends (6) on the application environment.

www.ti.com

# Table 2. TERMINAL FUNCTIONS (continued)

| TERMINAL |     |                     |                                   |

|----------|-----|---------------------|-----------------------------------|

| NAME     | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                       |

| V5A      | H4  | VDO                 | V <sub>DRIVER</sub> out 5A        |

| V3A      | H5  | VDO                 | V <sub>DRIVER</sub> out 3A        |

| STROBE   | H6  | DO                  | Strobe signal                     |

| VDD5     | H7  | Р                   | Digital power supply              |

| V6       | H8  | VDO                 | V <sub>DRIVER</sub> out 6         |

| RG       | H9  | DO                  | CCD reset gate signal             |

| H1A      | H10 | DO                  | CCD horizontal transfer signal 1A |

| SDATA    | J1  | DI                  | Serial data                       |

| SCLK     | J2  | DI                  | Serial data clock                 |

| TRIG     | J3  | DI                  | External trigger                  |

| VD       | J4  | DI/O                | Vertical sync                     |

| SUBSW1   | J5  | DO                  | CCD substrate signal switch 1     |

| MSHUT    | J6  | DO                  | Mechanical shutter signal         |

| SUBN     | J7  | DO                  | CCD electric shutter (for SUB)    |

| HL       | J8  | DO                  | CCD horizontal transfer signal    |

| V4       | J9  | VDO                 | V <sub>DRIVER</sub> out 4         |

| ADCCK    | J10 | DO                  | Clock for digital output buffer   |

| MCK      | K1  | DI                  | Master clock                      |

| CS       | K2  | DI                  | Chip select                       |

| HD       | K3  | DI/O                | Horizontal sync                   |

| SUBSW2   | K4  | DO                  | CCD substrate signal switch 2     |

| V1       | K5  | VDO                 | V <sub>DRIVER</sub> out 1         |

| FIELD    | K6  | DO                  | Field index signal                |

| V5B      | K7  | VDO                 | V <sub>DRIVER</sub> out 5B        |

| H2A      | K8  | DO                  | CCD horizontal transfer signal 2A |

| H1B      | K9  | DO                  | CCD horizontal transfer signal 1B |

| H2B      | K10 | DO                  | CCD horizontal transfer signal 2B |

www.ti.com

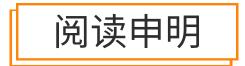

# FUNCTIONAL BLOCK DIAGRAM

www.ti.com

## TIMING CHARACTERISTICS

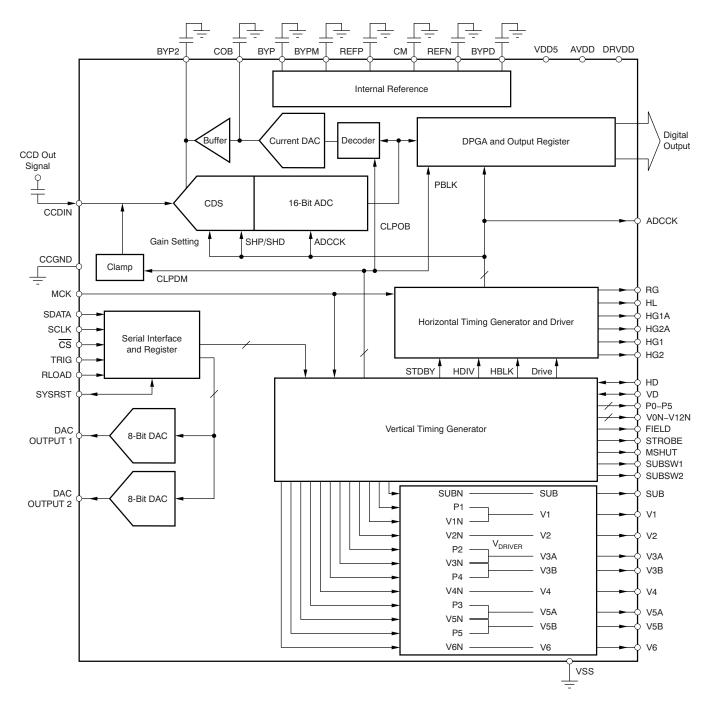

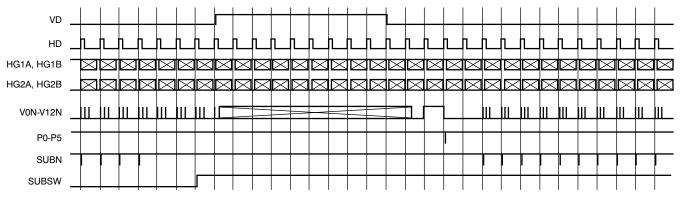

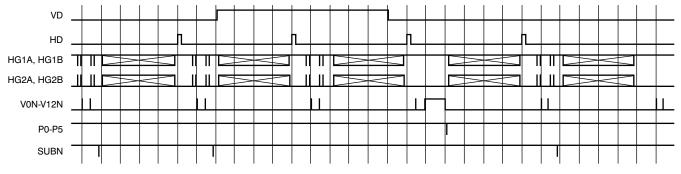

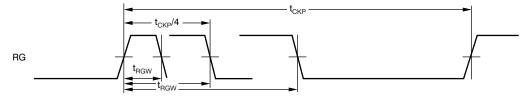

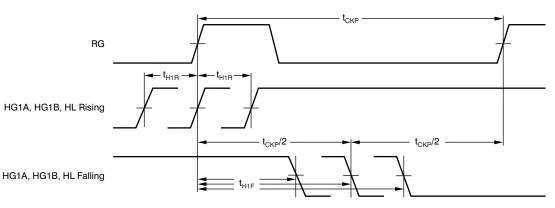

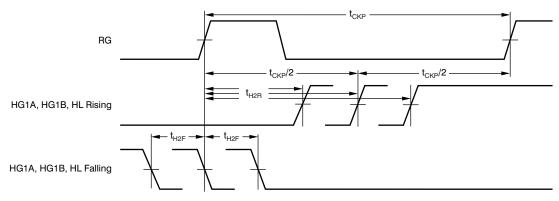

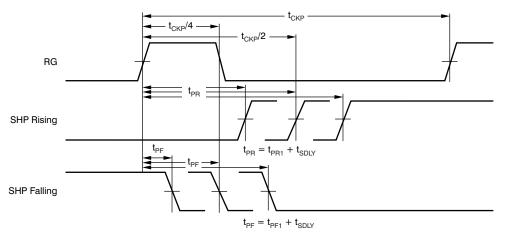

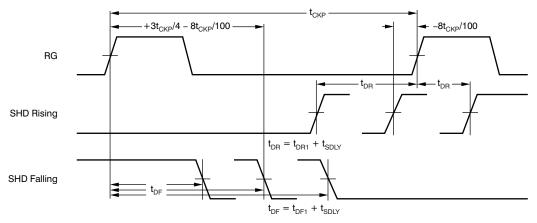

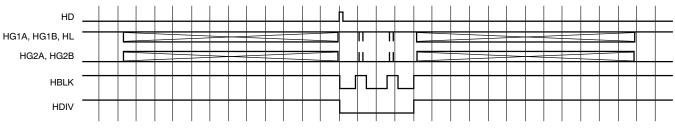

## TG HIGH-SPEED PULSE TIMING

NOTE: Dashed lines indicate programmable parameters.

Figure 1. TG High-Speed Pulse Timing

#### www.ti.com

|                      |                                                    | ng Characteristics for                        | or Figure 1                                      |                                                   |                        |

|----------------------|----------------------------------------------------|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------|------------------------|

|                      | PARAMETER                                          | MIN                                           | TYP                                              | MAX                                               | UNIT                   |

| t <sub>MCKP</sub>    | MCK clock period                                   | 27.7                                          |                                                  | 83.3                                              | ns                     |

| t <sub>MCKRG</sub>   | MCK rising edge to RG rising edge <sup>(1)</sup>   |                                               | 14                                               |                                                   | ns                     |

| t <sub>CKP</sub>     | Pixel rate                                         | 27.7                                          |                                                  | 83.3                                              | ns                     |

| t <sub>RGW</sub>     | RG rising edge to RG falling edge <sup>(2)</sup>   | t <sub>CKP</sub> /4 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /4                              | t <sub>CKP</sub> /4 + 15t <sub>CKP</sub> /100     | ns                     |

| t <sub>H1R</sub>     | RG rising edge to HG1 rising edge <sup>(2)</sup>   | -16t <sub>CKP</sub> /100                      | 0                                                | 15t <sub>CKP</sub> /100                           | ns                     |

| t <sub>H1F</sub>     | RG rising edge to HG1 falling edge <sup>(2)</sup>  | t <sub>CKP</sub> /2 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /2                              | t <sub>CKP</sub> /2 + 15t <sub>CKP</sub> /100     | ns                     |

| t <sub>H2R</sub>     | RG rising edge to HG2 rising edge <sup>(2)</sup>   | t <sub>CKP</sub> /2 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /2                              | t <sub>CKP</sub> /2 + 15t <sub>CKP</sub> /100     | ns                     |

| t <sub>H2F</sub>     | RG rising edge to HG2 falling edge <sup>(2)</sup>  | -16t <sub>CKP</sub> /100                      | 0                                                | +15t <sub>CKP</sub> /100                          | ns                     |

| t <sub>LHR</sub>     | RG rising edge to HL rising edge <sup>(2)</sup>    | -16t <sub>CKP</sub> /100                      | 0                                                | +15t <sub>CKP</sub> /100                          | ns                     |

| t <sub>LHF</sub>     | RG rising edge to HL falling edge <sup>(2)</sup>   | t <sub>CKP</sub> /2 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /2                              | t <sub>CKP</sub> /2 + 15t <sub>CKP</sub> /100     | ns                     |

| t <sub>PF</sub>      | RG rising edge to SHP falling edge <sup>(2)</sup>  | t <sub>CKP</sub> /4 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /4                              | t <sub>CKP</sub> /4 + 15t <sub>CKP</sub> /100 + 6 | ns                     |

| t <sub>PR</sub>      | RG rising edge to SHP rising edge <sup>(2)</sup>   | t <sub>CKP</sub> /2 - 16t <sub>CKP</sub> /100 | t <sub>CKP</sub> /2                              | $t_{CKP}/2 + 15t_{CKP}/100 + 6$                   | ns                     |

| t <sub>DF</sub>      | RG rising edge to SHD falling edge <sup>(2)</sup>  | $3t_{CKP}/4 - 24t_{CKP}/100$                  | 3t <sub>CKP</sub> /4 –<br>8t <sub>CKP</sub> /100 | $3t_{CKP}/4 + 7t_{CKP}/100 + 6$                   | ns                     |

| t <sub>DR</sub>      | RG rising edge to SHD rising edge <sup>(2)</sup>   | -24t <sub>CKP</sub> /100                      | -8t <sub>CKP</sub> /100                          | 7t <sub>CKP</sub> /100 + 6                        | ns                     |

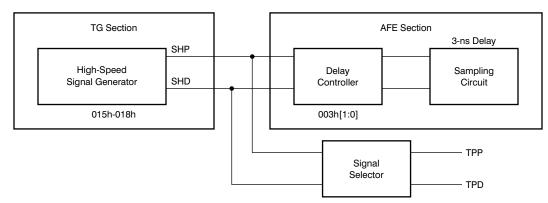

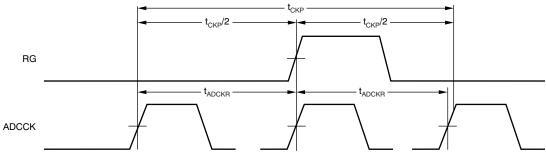

| t <sub>ADCKR</sub>   | RG rising edge to ADCCK rising edge <sup>(3)</sup> | -50t <sub>CKP</sub> /100                      | 0                                                | 49t <sub>CKP</sub> /100                           | ns                     |

| t <sub>S</sub>       | Sampling delay for SHP and SHD                     |                                               | 3                                                |                                                   | ns                     |

| t <sub>INHIBIT</sub> | Inhibited clock period                             | 4                                             | 7                                                | 10                                                | ns                     |

| t <sub>ADC</sub>     | ADCCK duty                                         |                                               | 50                                               |                                                   | %                      |

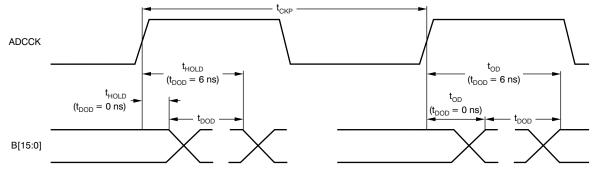

| t <sub>DOD</sub>     | Data out delay (register setting 002h)             | 0                                             | 0                                                | 6                                                 | ns                     |

| t <sub>HOLD</sub>    | Output hold time                                   | $2 + t_{DOD}$                                 |                                                  |                                                   | ns                     |

| t <sub>OD</sub>      | Output delay (no load)                             |                                               |                                                  | 27 + t <sub>DOD</sub>                             | ns                     |

| DL                   | Data latency                                       |                                               | 9 (fixed)                                        |                                                   | t <sub>CKP</sub> cycle |

Table 3. Timing Characteristics for Figure 1

(1) Pulse phase can be programmed through the serial interface.

(2) RG pulse width can be programmed through the serial interface. Refer to the *High-Speed Pulse Adjustment* section of the *TG (Timing Generator) Section* for details.

(3) ADCCK phase can also be programmed as a 90-degree step through the serial interface.

SBES016-MARCH 2009

#### www.ti.com

# SLAVE MODE: VD, HD SPECIFICATIONS

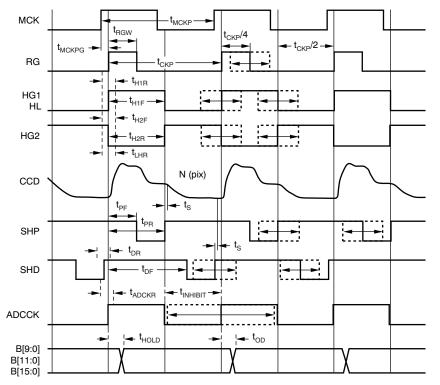

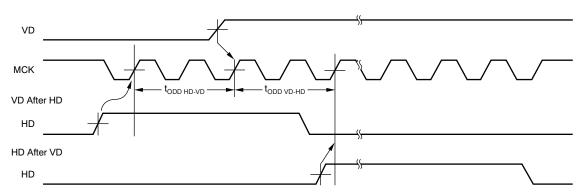

## VD, HD Detect

The odd field of the two-field CCD operation and the first field of the even field operation is detected by the VD and HD phase. The delay limit of the VD and HD phase is specified in Figure 2 and Figure 3.

Figure 2. VD, HD Falling Edge Detect

Figure 3. VD, HD Rising Edge Detect

|                        | MIN                                                                 | TYP | MAX | UNIT |                |

|------------------------|---------------------------------------------------------------------|-----|-----|------|----------------|

| t <sub>VD</sub>        | VD trail-to-trail                                                   | 10  |     |      | т (MCK cycles) |

| t <sub>HD</sub>        | HD trail-to-trail                                                   | 10  |     |      | т (MCK cycles) |

| todd hd-vd             | VD trail delay limit for ODD detect<br>(register setting 02Fh[2:0]) | 0   | 1   | 6    | т (MCK cycles) |

| t <sub>ODD HD-VD</sub> | HD trail delay limit for ODD detect<br>(register setting 02Fh[5:3]) | 0   | 1   | 6    | т (MCK cycles) |

| Table 4. Timing Characteristics for Figure 2 and Figure | 3 ( | 1) |

|---------------------------------------------------------|-----|----|

|---------------------------------------------------------|-----|----|

(1) The VD, HD edge is detected by the rising edge of MCK.

SBES016-MARCH 2009

www.ti.com

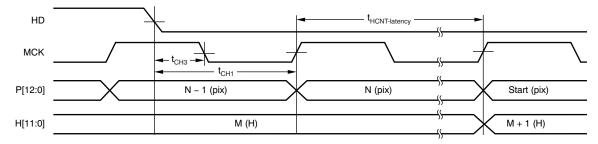

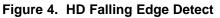

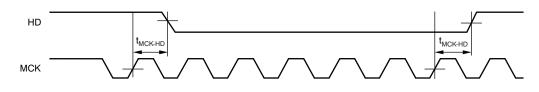

## **H**COUNTER Reset

$H_{COUNTER}$  is reset via HD detection. The timing is shown in Figure 4 and Figure 5.

| Table 5. Timing Characteristics for Figure 4 and | Figure 5 <sup>(1)</sup> |

|--------------------------------------------------|-------------------------|

|--------------------------------------------------|-------------------------|

|                               |                                                                    |                        | STER                |     |     |     |                |

|-------------------------------|--------------------------------------------------------------------|------------------------|---------------------|-----|-----|-----|----------------|

|                               | PARAMETER                                                          | VD, HD EDGE<br>020h[3] | MCK EDGE<br>020h[2] | MIN | ТҮР | МАХ | UNIT           |

| t <sub>CH1</sub>              | HD falling edge to MCK rising edge                                 | 0 (falling)            | 0 (rising)          | -6  |     | 1   | ns             |

| t <sub>CH2</sub>              | HD rising edge to MCK rising edge                                  | 1 (rising)             | 0 (rising)          | -6  |     | 1   | ns             |

| t <sub>CH3</sub>              | HD falling edge to MCK falling edge                                | 0 (falling)            | 1 (falling)         | -4  |     | 3   | ns             |

| t <sub>CH4</sub>              | HD rising edge to MCK falling edge                                 | 1 (rising)             | 1 (falling)         | -4  |     | 3   | ns             |

| t <sub>HCNT-</sub><br>LATENCY | H <sub>COUNTER</sub> reset latency<br>(register setting 034h[3:0]) | _                      | _                   |     | 6   |     | т (MCK cycles) |

(1)  $H_{COUNTER}$  reset timing is selected by MCK edge polarity.

www.ti.com

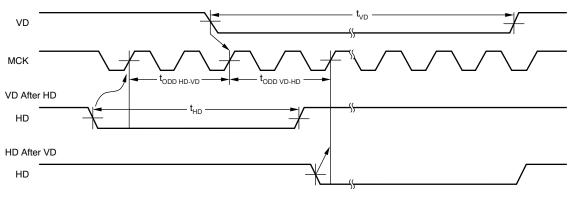

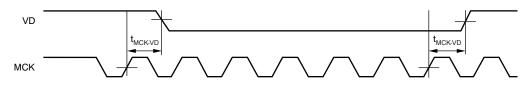

## MASTER MODE: HD, VD SPECIFICATIONS

The HD, VD MCK timing is shown in Figure 6 and Figure 7.

Figure 6. VD MCK Specification

Figure 7. HD MCK Specification

| Table 6. Timing Characteristics | for Figure 6 and Figure 7 |

|---------------------------------|---------------------------|

|---------------------------------|---------------------------|

|                     | PARAMETER                          |  | ТҮР | MAX | UNIT |

|---------------------|------------------------------------|--|-----|-----|------|

| t <sub>MCK-VD</sub> | MCK rising edge to VD falling edge |  | 10  |     | ns   |

| t <sub>MCK-HD</sub> | MCK rising edge to HD falling edge |  | 10  |     | ns   |

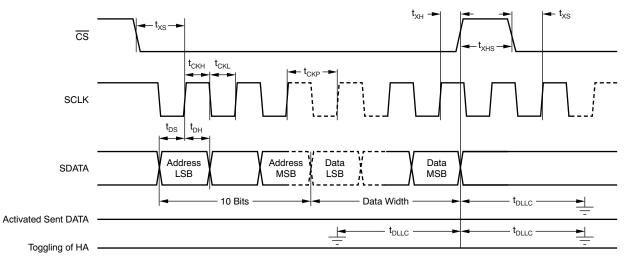

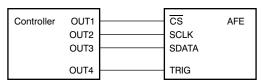

### SERIAL INTERFACE TIMING SPECIFICATION

The serial interface has two writing modes: standard and continuous write. These modes are shown in Figure 8 and Figure 9.

Figure 8. Standard Mode Timing

SBES016-MARCH 2009

#### Figure 9. Continuous Write Mode Timing

|                   | PARAMETER                            | MIN | ТҮР | MAX | UNIT    |

|-------------------|--------------------------------------|-----|-----|-----|---------|

| t <sub>CKP</sub>  | Clock period                         | 50  |     |     | ns      |

| t <sub>CKH</sub>  | Clock high pulse width               | 25  |     |     | ns      |

| t <sub>CKL</sub>  | Clock low pulse width                | 25  |     |     | ns      |

| t <sub>DS</sub>   | Data setup time                      | 15  |     |     | ns      |

| t <sub>DH</sub>   | Data hold time                       | 15  |     |     | ns      |

| t <sub>XS</sub>   | S <sub>LOAD</sub> to SCLK setup time | 20  |     |     | ns      |

| t <sub>XH</sub>   | SCLK to $\overline{CS}$ hold time    | 20  |     |     | ns      |

| t <sub>XHS</sub>  | CS width                             | 20  |     |     | ns      |

| t <sub>DLLC</sub> | Data load latency clock              |     |     | 10  | MCK CLK |

#### Table 7. Timing Characteristics for Figure 8 and Figure 9

Data shift operation should decode at the rising edges of SCLK while  $\overline{CS}$  is low.

Parallel latch timing for each mode is described in Table 8.

#### Table 8. Parallel Latch

| MODE             | PARALLEL LATCH TIMING |  |

|------------------|-----------------------|--|

| Standard write   | Rising edge of CS     |  |

| Continuous write | End of data (MSB)     |  |

In addition to the parallel latch, there are several registers dedicated to the specific features of the device; these registers are synchronized with MCK. It takes less than 10 clock cycles for the data in the parallel latch to be written to these registers. Therefore, to complete the data updates, it requires less than 10 clock cycles after parallel latching.

Toggling of HA is inhibited from parallel latch. Refer to the Serial interface (SPI) section of the Common Section for details.

www.ti.com

#### SBES016-MARCH 2009

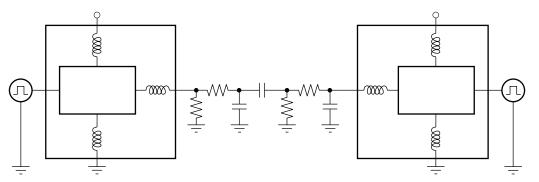

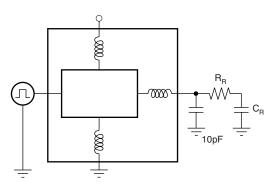

#### **EQUIVALENT CIRCUITS**

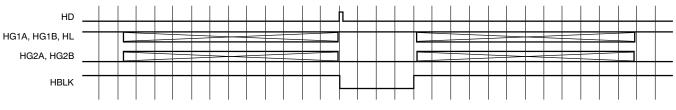

Figure 10 shows the HG1A, HG1B, HG2A, and HG2B high-speed driver and load model. The driver supports up to 150 pF. Figure 11 shows the RG and HL high-speed driver and load model. The driver supports up to 10 pF.

Figure 10. HG Driver and Load Model

Figure 11. RG Driver and Load Model

www.ti.com

#### **COMMON SECTION**

#### **REGISTER/MEMORY MAP**

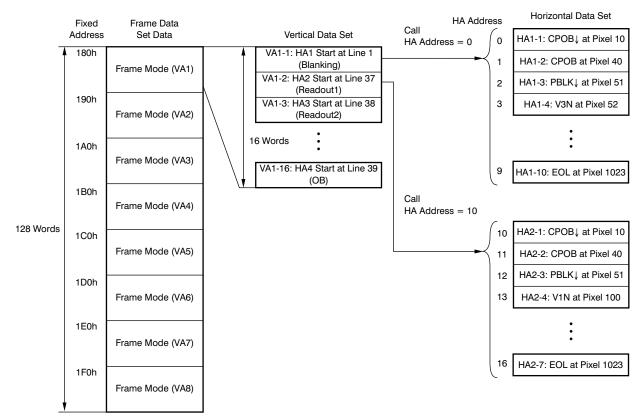

Figure 12 shows the TG register/memory map, which has 1024 words of 32-bit instruction (max). The 256-word register area enables active instruction, which requires dynamic operation. The 768-word memory area enables static instruction, which is almost fixed during a frame rate.

|      | Address                    | Data                          |                                                       |

|------|----------------------------|-------------------------------|-------------------------------------------------------|

|      | <b>◄</b> 10-Bit <b>─</b> ► | 22 Bits (maximum) ———         | <b>→</b>                                              |

| 000h | 00 0000 0000b              | <ul> <li>← 6-Bit →</li> </ul> | Register (active control)<br>192 Words (maximum)      |

| 0BFh | 00 1011 1111b              |                               |                                                       |

| 0C0h | 00 1100 0000b              |                               | Register (reserved)                                   |

| 0FFh | 00 1111 1111b              | ◄16-Bit►                      | 64 Words (maximum)                                    |

| 100h | 01 0000 0000b              | #1 (100h)                     | 4                                                     |

|      |                            | #2 (120h)                     | Memory [vertical high-speed transfer(HS) #1-4]        |

|      |                            | #3 (140h)                     | 128 Words (maximum)                                   |

| 17Fh | 01 0111 1111b              | #4 (160h)                     |                                                       |

| 180h | 01 1000 0000b              | VA1 (180h)                    | <b>^</b>                                              |

|      |                            | VA2 (190h)                    |                                                       |

|      |                            | VA3 (1A0h)                    | Memory (vertical timing: VA1-VA8)                     |

|      |                            | VA4 (1B0h)<br>VA5 (1C0h)      | 128 Words (maximum) <sup>(1)</sup>                    |

|      |                            | VA6 (100h)                    |                                                       |

|      |                            | VA7 (1E0h)                    |                                                       |

| 1FFh | 01 1111 1111b              | VA8 (1F0h)                    |                                                       |

| 200h | 10 0000 0000Ь              | HA Address<br>0               | Memory (horizontal timing: HA)<br>512 Words (maximum) |

| 3FFh | 11 1111 1111b              | 511                           |                                                       |

NOTE: Shaded cells indicate the area under discussion.

(1) Refer to the TG Instruction Hierarchy section of the TG (Timing Generator) Section for details.

Figure 12. VSP01M01/VSP01M02 TG Register/Memory Map

www.ti.com

#### SERIAL INTERFACE (SPI)

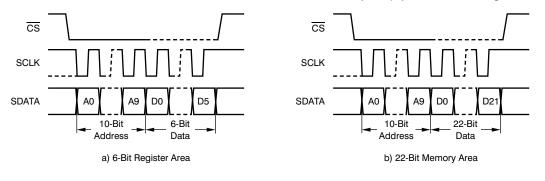

The SPI functions and timings are controlled through the serial interface, which is composed of three signals: SDATA, SCLK, and CS. SDATA data are sequentially stored to the shift register at the rising edge of SCLK. Before a write operation, CS must go low, and remain low during writing. Refer to *Serial Interface Timing Specification* for further details.

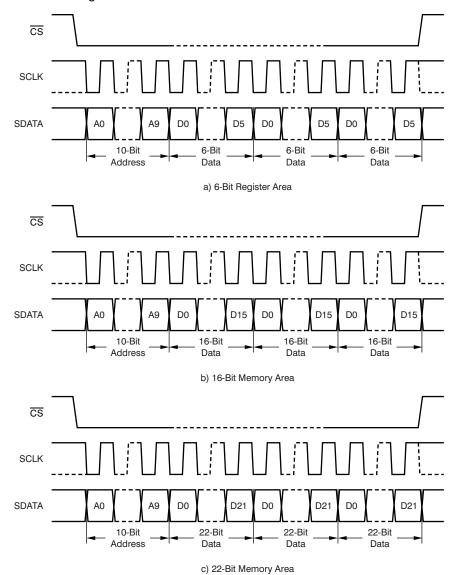

The serial interface command is composed of a 10-bit address and 6-bit, 16-bit, or 22-bit data. Table 9 shows the data width for each address area.

| ADDRESS (10-Bit) | DATA WIDTH (Bits) | USAGE            |

|------------------|-------------------|------------------|

| 000h-0BFh        | 6                 | Register         |

| 100h-17Fh        | 16                | HS memory        |

| 180h-3FFh        | 22                | HA and VA memory |

#### Table 9. Address Data Width<sup>(1)</sup>

(1) Refer to *Register/Memory Map* for details.

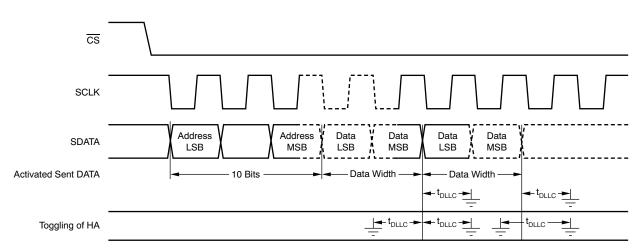

The SPI has two write modes: standard and continuous.

#### Standard Write Mode

The VSP01M01 and VSP01M02 support a standard write mode, as shown in Figure 13. Normally, a serial interface command is sent by one address and data combination. The 10-bit address should primarily be sent LSB first; the following 6-bit, 16-bit, or 22-bit data should also sent LSB first. 6-bit, 16-bit, or 22-bit data are stored in the respective register by the <u>10-bit</u> address at the rising edge of  $\overline{CS}$ . The stored serial command data change immediately at rising edge of  $\overline{CS}$  or are reserved by programmable control. If the data bit does not contain either 6-bits, 16-bits, or 22-bits at the end of the data stream, any empty data bits are ignored.

c) 16-Bit Memory Area

Figure 13. SPI Standard Write Mode

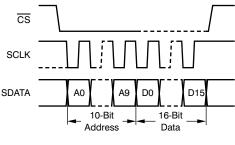

#### **Continuous Write Mode**

These devices also support a continuous write mode, as shown in Figure 14. When the input serial data are longer than one set of instructions, the following data stream is automatically recognized as the data of the next address. In this mode, 6-bit, 16-bit, or 22-bit serial command data are stored to the respective registers immediately when those data are fetched. Address and data should be sent LSB first, in the same way as standard write mode. If the data bit does not contain either 6-bits, 16-bits, or 22-bits at the end of the data stream, any empty data bits are ignored.

Figure 14. SPI Continuous Write Mode

# www.ti.com

#### Mode Confusion

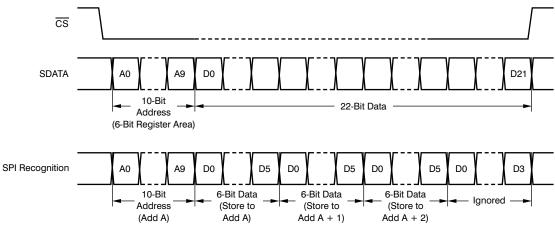

If 22 bits of data are sent to a 6-bit register area, the SPI recognizes *continuous write mode*, because usually only 6-bit data should be sent to 6-bit register area in *standard write mode*, as shown in Figure 15. The end-of-data point is recognized by the rising edge of CS.

Figure 15. Mode Confusion

SPI recognition is shown in Table 10.

#### Table 10. SPI Recognition

|                | DATA WIDTH                         |                                       |                                    |                         |

|----------------|------------------------------------|---------------------------------------|------------------------------------|-------------------------|

| ADDRESS AREA   | 6-BIT                              | 16-BIT                                | 22-BIT                             | 32-BIT                  |

| 6-bit register | Standard <sup>(1)</sup> (one word) | Continuous <sup>(2)</sup> (two words) | Continuous (three words)           | Continuous (five words) |

| 16-bit memory  | Ignored                            | Standard (one word)                   | Standard <sup>(3)</sup> (one word) | Continuous (two words)  |

| 22-bit memory  | Ignored                            | Ignored                               | Standard (one word)                | Standard (one word)     |

(1) Shaded cells indicate standard operation.

(2) Continuous = continuous write mode.

(3) Standard = standard write mode.

#### Read and Write Batting

Address 100h-3FFh is the memory area. HA, VA, and HS access this memory area to read programs. If the SPI writes to the memory area during a program read, the programmed operation is cancelled. SPI operation should be done with *TG disable*. If SPI operation must be done with *TG enable* (TG operating), the SPI must write for a no-read term (no toggling term). For the register area (000h-0FFh), this precaution is not necessary.

#### **REGISTER UPDATE**

The update timing of each register is specified in Table 11.

#### Table 11. Updated Timing

| REGISTER ADDRESS | UPDATE TIMING                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------|

| 000h             | Real time                                                                                           |

| 001h-01Fh        | Timing specified at bits 0-2 of 000h (AFE update)                                                   |

| 020h-035h        | Real time                                                                                           |

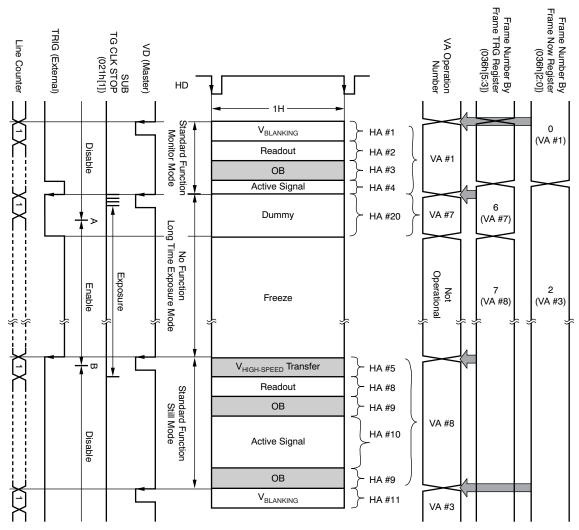

| 036h[2:0]        | VD; refer to the CCD Timing Composition section of the TG (Timing Generator) Section for details.   |

| 036h[5:3]        | TRIG; refer to the CCD Timing Composition section of the TG (Timing Generator) Section for details. |

| 037h-0FFh        | Timing specified at bit 3 of 000h (TG update)                                                       |

www.ti.com

The AFE register is updated in real time by the R<sub>LOAD</sub> pin or VD, as shown in Table 12.

#### Table 12. Update Select Register (AFE)

| PARAMETER  | REGISTER ADDRESS | DESCRIPTION                                                                                                                                                                        |

|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AFE UPDATE | 000h[0]          | 0 = Real-time update (default)<br>1 = Updated by R <sub>LOAD</sub> pin or VD                                                                                                       |

|            |                  | AFE register update signal and polarity                                                                                                                                            |

| AFE UP POL | 000h[2:1]        | $\begin{array}{ll} 00b = R_{LOAD} \text{ rising edge (default)} & 10b = VD \text{ rising edge} \\ 01b = R_{LOAD} \text{ falling edge} & 11b = VD \text{ falling edge} \end{array}$ |

The TG register can be updated at a specified line number through VA instruction. The update method selection is described in Table 13. In general, this function is used for SUBN control.

#### Table 13. Update Select Register (TG)

| PARAMETER | REGISTER ADDRESS | DESCRIPTION                                                                                                                                              |

|-----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| TG UPDATE | 000h[3]          | 0 = Real-time update (default)<br>1 = Updated by VA instruction line number<br>Refer to the <i>Vertical Sequence</i> section for VA instruction details. |

#### MCK STOP DETECT

The MCK stop detect function is supported, as shown in Table 14. If an MCK stop was detected, all register values are cleared. After an MCK stop detect, a SYSRST is required.

#### Table 14. MCK Stop Detect Register

| PARAMETER  | REGISTER ADDRESS | DESCRIPTION                           |

|------------|------------------|---------------------------------------|

| MCK detect | 020h[4]          | 0 = Disabled<br>1 = Enabled (default) |

#### **STANDBY FUNCTION**

For increased power savings, this device can be put into a standby mode (power-down mode) through serial interface control when the device is not in use. In this mode, all function blocks are disabled. Current consumption drops to about 2 mA. Because all the bypass capacitors discharge during this mode, a substantial time (usually on the order of 200 ms to 300 ms) is required to return from standby mode. A four-part standby is selected independently, as described in Table 15.

#### Table 15. Standby Control Register

| SECTION | REGISTER<br>ADDRESS | DESCRIPTION                                     | SIGNAL STATUS IN STANDBY                                          |

|---------|---------------------|-------------------------------------------------|-------------------------------------------------------------------|

| TG      | 020h[0]             | 0 = Standby (default)<br>1 = Normal operation   | Refer to the Signal section of the TG (Timing Generator) Section. |

| AFE     | 001h[0]             | 0 = Normal operation (default)<br>1 = Standby   | Digital output = high impedance                                   |

| DAC1    | 001h[1]             | 0 = Enabled<br>1 = Disabled (Standby) (default) | Analog output = low                                               |

| DAC2    | 001h[2]             | 0 = Enabled<br>1 = Disabled (Standby) (default) | —                                                                 |

AFE standby, DAC1 standby, or DAC2 standby should be completed before TG standby if using the VD update method for the the AFE section. If the AFE standby is completed after TG standby, the AFE standby, DAC1 standby, or DAC2 standby are not activated.

#### www.ti.com

#### SYSTEM RESET

All parameters are reset to the respective default values when the SYSRST pin goes low asynchronously with respect to the system clock. All register and memory values are cleared by SYSRST. SYSRST should be pulled up for operation. Figure 16 shows typical SYSRST implementation with a pull-up resistor.

Figure 16. SYSRST Pin

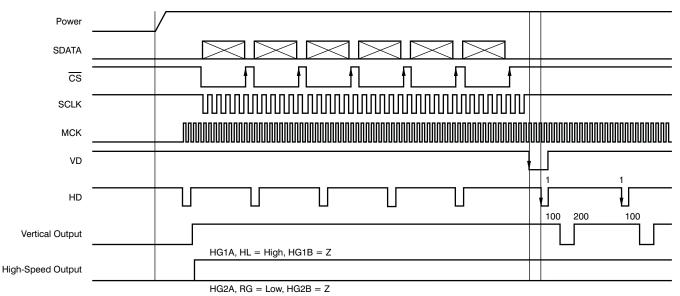

## **POWER-UP SEQUENCE**

When the device is powered up, follow this recommended sequence:

- 1. Turn on the power supplies for the device.

- 2. Apply the master clock input to the MCK, VD, and HD signals.

- Input the serial data for the 6-bit register setting. Input SRG for 16-bit serial data. (10-bit address + 6-bit data). TG disable must be complete. (020h[0] = 0)

- Input the serial data for V<sub>HIGH SPEED</sub> transfer toggling. Input SRG for 26-bit serial data. (10-bit address + 16-bit data)

- 5. Input the serial data for V<sub>RATE</sub> toggling. Input SRG for 32-bit serial data. (10-bit address + 22-bit data)

- 6. Input the serial data for H<sub>RATE</sub> toggling. Input SRG for 32-bit serial data. (10-bit address + 22-bit data)

- Input the serial data for TG enable. Input SRG for 16-bit serial data. (10-bit address + 16-bit data) TG enable must be complete. (020h[0] = 1)

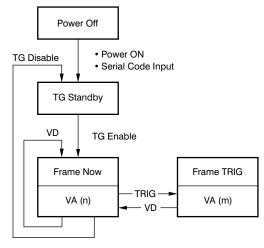

Figure 17 shows the timing for the power-up sequence.

Figure 17. Power-Up Sequence

www.ti.com

# AFE (ANALOG FRONT-END) SECTION

## OVERVIEW

## Composition

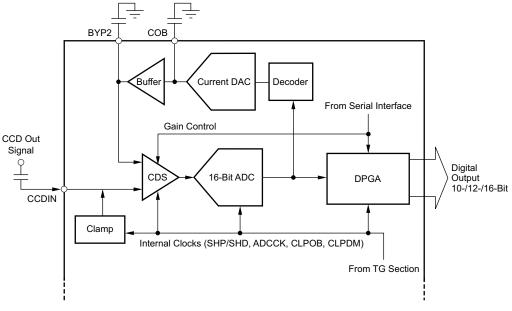

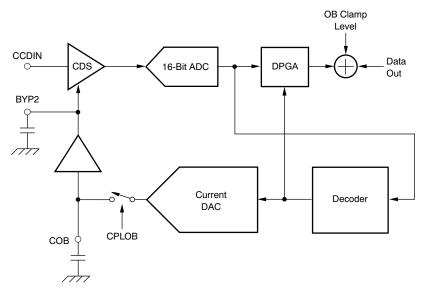

The VSP01M01/VSP01M02 are complete mixed-signal ICs that contain all of the key features associated with processing of the CCD imager output signal in video cameras, digital still cameras, security cameras, or similar applications. A simplified block diagram of the AFE section is shown in Figure 18. The AFE section includes these features:

- Correlated double sampler (CDS)

- Programmable gain amplifier (PGA)

- Analog-to-digital converter (ADC)

- Input clamp

- Optical black (OB) level clamp loop

- Timing control

- Internal reference voltage generator

It is recommended that an off-chip emitter follower buffer be placed between the CCD output and the device CCDIN input. The serial interface controls PGA gain, clock polarity setting, and operation mode.

#### Function

Table 16 shows the major functions of the AFE section.

| FUNCTION                     | RELATED REGISTER | SECTION                      |  |

|------------------------------|------------------|------------------------------|--|

| Selectable CDS (analog) gain | 008h             | Drammahla Onia               |  |

| Programmable digital gain    | 006h, 007h       | Programmable Gain            |  |

| Programmable OB clamp level  | 004h             | OB Loop and OB Clamp Level   |  |

| Standby mode                 | 001h[2:0]        | Standby Function             |  |

| Hot pixel rejection          | 005h             | Hot Pixel Rejection          |  |

| Selectable register update   | 000h[2:0]        | AFE Register Update Function |  |

| Data output enable control   | 002h[2]          | Data Output Enable           |  |

#### www.ti.com

#### CORRELATED DOUBLE SAMPLER (CDS)

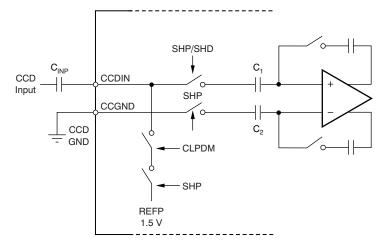

The output signal of the CCD image sensor is sampled twice during one pixel period: once at the reference interval and again at the data interval. Subtracting these two samples extracts the video information of the pixel as well as removes any noise, which is common to both intervals. Thus, CDS is very important to reduce the reset noise and the low-frequency noise that are present on the CCD output signal. Figure 19 shows the block diagram of the CDS section. SHP, SHD, CLPDM, and CLPOB are supplied from the TG section; these signals are active low (close).

Figure 19. Block Diagram of CDS and Input Clamp

#### **INPUT CLAMP**