## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

## CY7C65100 Four-port Universal Serial Bus Fixed-function Hub Controller

## **TABLE OF CONTENTS**

| 1.0 FEATURES                                       | 3  |

|----------------------------------------------------|----|

| 2.0 FUNCTIONAL OVERVIEW                            | 3  |

| 3.0 PRODUCT SUMMARY                                | 4  |

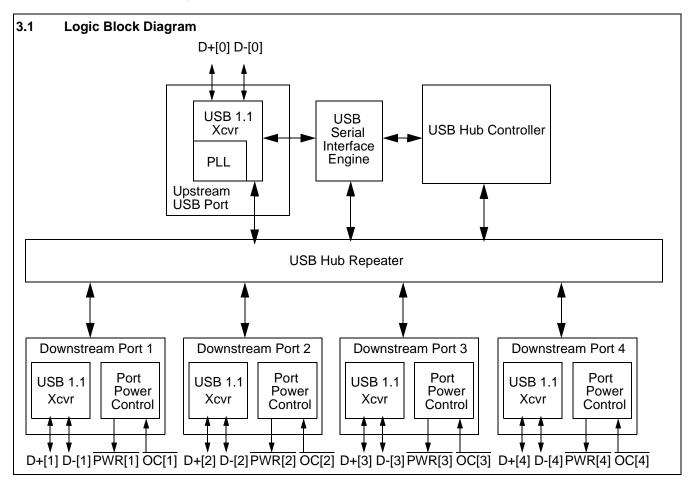

| 3.1 Logic Block Diagram                            | 4  |

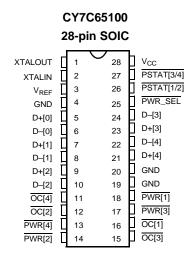

| 3.2 Pin Configuration                              | 4  |

| 3.3 Pin Assignments                                | 5  |

| 4.0 CLOCKING                                       | 5  |

| 5.0 USB OVERVIEW                                   | 5  |

| 5.1 USB SIE                                        | 5  |

| 5.2 Hub Design                                     |    |

| 5.3 Vendor ID and Product ID                       | 6  |

| 6.0 APPLICATION DIAGRAMS                           | 7  |

| 6.1 USB Standalone Hub Schematics                  | 8  |

| 7.0 ABSOLUTE MAXIMUM RATINGS                       | 9  |

| 8.0 ELECTRICAL CHARACTERISTICS                     | 9  |

| 9.0 SWITCHING CHARACTERISTICS                      | 10 |

| 10.0 ORDERING INFORMATION                          | 10 |

| 11.0 PACKAGE DIAGRAM                               | 11 |

| LIST OF FIGURES                                    |    |

| Figure 4-1. Clock Oscillator On-chip Circuit       |    |

| Figure 6-1. USB Standalone Hub Application Diagram |    |

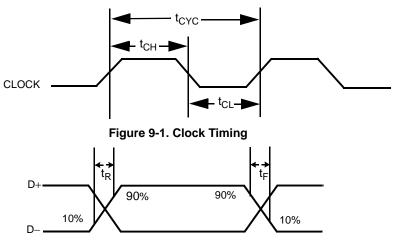

| Figure 9-1. Clock Timing                           | 10 |

| Figure 9-2. USB Data Signal Timing                 | 10 |

| LIST OF TABLES Table 3-1. Pin Assignments          | 5  |

| 10DIG J-1. 1 111 MOOINIIIIGIIIO                    | J  |

#### 1.0 Features

- Fixed-function four-port USB hub devices with integrated hub repeater, hub controller, Serial Interface Engine (SIE), and USB transceivers

- USB Specification Compliance

- Conforms to USB Specification, Rev. 1.1

- Complies with the USB HUB Device Class

- Supports self-powered and bus-powered applications

- · Individual downstream port power switching

- Individual downstream port overcurrent detection

- Integrated USB transceivers reduce EMI

- Internal 48-MHz phase-locked loop (PLL) reduces design cost by requiring only an external 6-MHz crystal

- Operating voltage from 4.0V-5.5V DC

- Operating temperature from 0°-70° Celsius

- Available in a space-saving 28-lead SOIC package

#### 2.0 Functional Overview

The CY7C65100 series offers high-performance fixed-function Universal Serial Bus (USB) hub devices that comply with *USB Specification, Rev. 1.1.* Up to four downstream USB ports are available to expand the USB attachment points available in your PC system. These self-contained devices require no firmware development for your design, thereby reducing the design risk associated with some microcontroller solutions. These Application Specific Standard Products (ASSP) can improve time-to-market in a number of USB designs, including standalone hubs, motherboard hubs, and monitor hubs.

The CY7C65100 series supports self-powered or bus-powered applications. Power management for all downstream ports supports power-switching and overcurrent detection with individual port control. The four downstream ports support both full-speed (12-Mbps signaling rate) and low-speed (1.5-Mbps signaling rate) devices. The CY7C65100 series has a reduced frequency (6-MHz) crystal oscillator for lower system cost as well as improved EMI performance. The four-port CY7C65100 series is available in a cost-effective and space-saving 28-lead SOIC package.

## 3.0 Product Summary

#### 3.2 Pin Configuration

### 3.3 Pin Assignments

Table 3-1. Pin Assignments

| Name                   | I/O | Pin                 | Description                                                                                                                 |  |

|------------------------|-----|---------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| D+[0], D-[0]           | I/O | 5,6                 | Upstream port, USB differential data                                                                                        |  |

| D+[1], D–[1]           | I/O | 7,8                 | Downstream port 1, USB differential data                                                                                    |  |

| D+[2], D-[2]           | I/O | 9,10                | Downstream port 2, USB differential data                                                                                    |  |

| D+[3], D-[3]           | I/O | 23,24               | Downstream port 3, USB differential data                                                                                    |  |

| D+[4], D-[4]           | I/O | 21,22               | Downstream port 4, USB differential data                                                                                    |  |

| PWR[1]- PWR[4]         | OUT | 18,14,17,13         | Downstream port power enable output                                                                                         |  |

| OC[1]-OC[4]            | IN  | 16,12,15,11         | Downstream port power over-current detection signals                                                                        |  |

| XTALIN                 | IN  | 2                   | 6-MHz crystal or external clock input                                                                                       |  |

| XTALOUT                | OUT | 1 6-MHz crystal out |                                                                                                                             |  |

| V <sub>CC</sub>        | PWR | 28 Voltage supply   |                                                                                                                             |  |

| GND                    | GND | 4,19,20             | Ground                                                                                                                      |  |

| V <sub>REF</sub>       | IN  | 3                   | Input for external 3.3V supply voltage for the upstream and down stream differential data output buffers and the D+ pull-up |  |

| PWR_SEL                | IN  | 25                  | Bus or self-power function select input                                                                                     |  |

| PSTAT[1/2], PSTAT[3/4] | OUT | 26,27               | Downstream port LED status enable                                                                                           |  |

#### 4.0 Clocking

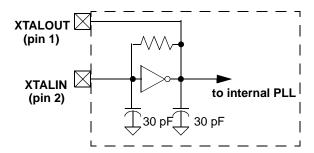

Figure 4-1. Clock Oscillator On-chip Circuit

XTALIN and XTALOUT are the clock pins to the CY7C65100 series. The user can connect either an external oscillator or a crystal to these pins. A 6-MHz fundamental crystal can be connected to these pins to provide a reference frequency for the internal PLL. When using an external crystal, keep PCB traces between the chip leads and crystal as short as possible (less than 2 cm). A ceramic resonator is not an adequate clock source to meet the timing specifications of a high-speed USB function and therefore cannot be used with these parts. An external 6-MHz clock can be applied to the XTALIN pin if the XTALOUT pin is left open. Please note that grounding the XTALOUT pin when driving XTALIN with an oscillator will not work as the internal clock is effectively shorted to ground.

#### 5.0 USB Overview

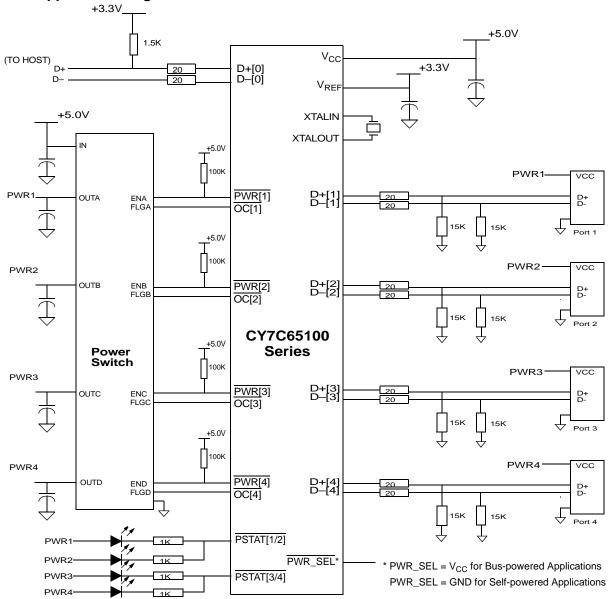

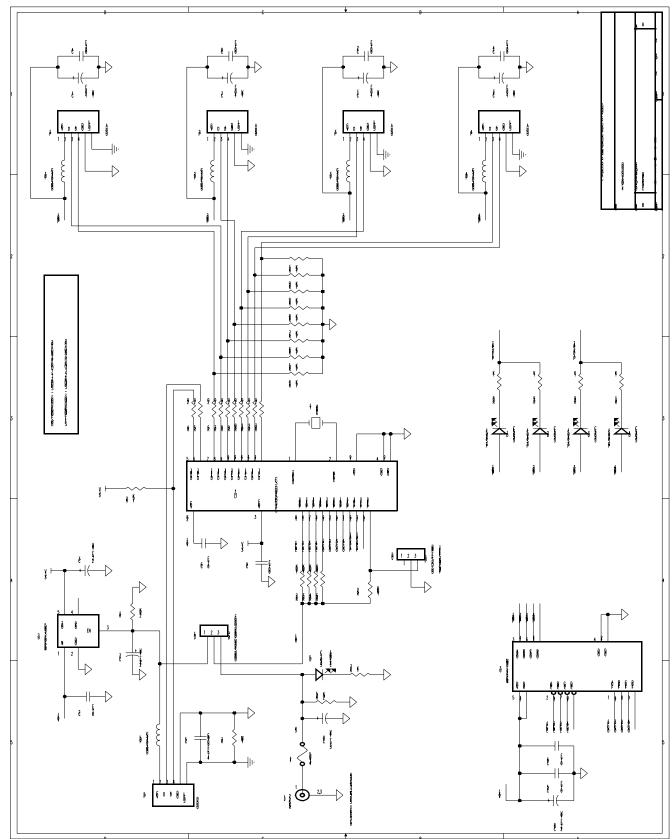

The USB hardware includes a USB Hub repeater with one upstream port and up to four downstream ports. An external series resistor of  $R_{\text{ext}} = 20\Omega \, (\pm \, 5\%)$  must be placed in series with all upstream and downstream USB I/O in order to meet the USB driver impedance requirements as defined by the USB specification (see *Figure 6-1*).

#### 5.1 USB SIE

The SIE allows the CY7C65100 series to communicate with the USB host through the USB repeater portion of the hub. The SIE handles the following USB bus activity independently of the hub microcontroller:

- · Bit stuffing/unstuffing

- · Checksum generation/checking

- ACK/NAK/STALL

- TOKEN type identification

- · Address checking.

The following protocol handling is done at a higher level by the Hub Control Block:

- Coordinate enumeration by responding to SETUP packets

- Fill and empty the FIFOs

- Suspend/Resume coordination

- Verify and select DATA toggle values

- Port power control and over-current detection.

#### 5.2 Hub Design

The power switching and over-current detection of downstream ports is managed by control pins connected to an external power switch device (see *Figure 6-1*). The active-LOW PWR[n] output pins of the CY7C65100 series are connected to the respective external power switch's port power enable signals. (Note that each port power output pin of the external power switch must be bypassed with an electrolytic or tantalum capacitor as required by the USB specification. These capacitors supply the inrush currents which occur during downstream device hot-attach events.) The active-LOW OC[n] pins of the CY7C65100 series are connected to the respective external power switch's port over-current indication (output) signals. Upon detecting an over-current condition, the hub device reports the over-current condition to the host and disables (sets to logic HIGH) the respective PWR[n] signal connected to the external power device.

#### 5.3 Vendor ID and Product ID

The CY7C65100 Series will enumerate with the default Vendor ID and Product ID as follows.

|            | Bus-powered | Self-powered |

|------------|-------------|--------------|

| Vendor ID  | 0x04b4      | 0x04b4       |

| Product ID | 0x5204      | 0x5203       |

Pin 25 (PWR\_SEL) is a strapping option that selects the device's power configuration report (PWR\_SEL = GND for self-powered, PWR\_SEL = Vcc for bus-powered).

For high-volume business, Cypress has the capability to factory-program a Custom Vendor ID and Product ID. Please contact your local Cypress sales office for more information.

## 6.0 Application Diagrams

Figure 6-1. USB Standalone Hub Application Diagram

### 6.1 USB Standalone Hub Schematics

## 7.0 Absolute Maximum Ratings

## **8.0** Electrical Characteristics $F_{OSC} = 6$ MHz; Operating Temperature = $0^{\circ}$ to $70^{\circ}$ C, $V_{CC} = 4.0$ V to 5.5V

| Parameter           | Description                          | Conditions                                                          | Min.  | Max.  | Unit |

|---------------------|--------------------------------------|---------------------------------------------------------------------|-------|-------|------|

| General             |                                      |                                                                     | •     |       |      |

| $V_{ref}$           | Reference Voltage                    | 3.3V ± 5%                                                           | 3.15  | 3.45  | V    |

| I <sub>cc</sub>     | V <sub>CC</sub> Operating Current    |                                                                     |       | 50    | mA   |

| I <sub>REF</sub>    | V <sub>ref</sub> Operating Current   | No USB Traffic                                                      |       | 10    | mA   |

| I <sub>SB1</sub>    | Standby Current                      |                                                                     |       | 50    | μΑ   |

| I <sub>IL</sub>     | Input Leakage Current                | any pin                                                             |       | 1     | μΑ   |

| USB Interface       | 9                                    |                                                                     | •     |       |      |

| $V_{di}$            | Differential Input Sensitivity       | (D+)-(D-)                                                           | 0.2   |       | V    |

| V <sub>cm</sub>     | Differential Input Common Mode Range |                                                                     | 0.8   | 2.5   | V    |

| V <sub>se</sub>     | Single Ended Receiver Threshold      |                                                                     | 0.8   | 2.0   | V    |

| C <sub>in</sub>     | Transceiver Capacitance              |                                                                     |       | 20    | pF   |

| I <sub>lo</sub>     | High-Z State Data Line Leakage       | 0V < V <sub>in</sub> < 3.3V                                         | -10   | 10    | μΑ   |

| R <sub>D+</sub>     | USB Power Setting Pull-up Resistor   |                                                                     | 1.425 | 1.575 | KW   |

| R <sub>ext1</sub>   | External USB Pull-down Resistor      | Downstream data lines                                               | 14.25 | 15.75 | KW   |

| R <sub>ext2</sub>   | External USB Series Resistor         | In series with each USB pin                                         | 19    | 21    | W    |

| Power-On Re         | set                                  |                                                                     | •     |       |      |

| t <sub>vccs</sub>   | V <sub>CC</sub> Ramp Rate            | Linear ramp: V <sub>CC</sub> =0 to Operating Voltage <sup>[1]</sup> | 0     | 100   | ms   |

| USB Upstream        | m/Downstream Port                    | -                                                                   |       |       |      |

| $V_{oh}$            | Static Output HIGH                   | RL of 15 kΩ± 5% to Gnd                                              | 2.8   | 3.6   | V    |

| V <sub>ol</sub>     | Static Output LOW                    | RL of 1.5 kΩ± 5% to 3.6V                                            |       | 0.3   | V    |

| V <sub>crs</sub>    | Crossover Voltage                    |                                                                     | 1.3   | 2.0   | V    |

| Z <sub>o</sub>      | USB Driver Output Impedance          | Including R <sub>ext</sub>                                          | 28    | 44    | W    |

| OC[n] Pins          |                                      | •                                                                   | •     |       |      |

| V <sub>IL</sub>     | Input LOW Threshold Voltage          |                                                                     |       | 8.0   | V    |

| V <sub>IH</sub>     | Input HIGH Threshold Voltage         |                                                                     | 2.0   |       | V    |

| PWREN[n] Pi         | ns                                   | •                                                                   |       |       |      |

| I <sub>PWR[n]</sub> | PWR[n] Sink Current (typical 7 mA)   | V <sub>out</sub> = 2.0V DC                                          | 3.5   | 10.6  | mA   |

#### Note

<sup>1.</sup> Power-on Reset will occur whenever the voltage on  $V_{CC}$  is below approximately 2.5V.

| Parameter        | Description                                                | Min.                  | Max.   | Unit |  |

|------------------|------------------------------------------------------------|-----------------------|--------|------|--|

| Clock Source     |                                                            | •                     |        |      |  |

| f <sub>osc</sub> | Clock Rate                                                 | 5.985                 | 6.015  | MHz  |  |

| t <sub>cyc</sub> | Clock Period                                               | 166.25                | 167.08 | nsec |  |

| t <sub>CH</sub>  | Clock HIGH Time                                            | 0.45 t <sub>CYC</sub> |        | ns   |  |

| t <sub>CL</sub>  | Clock LOW Time                                             | 0.45 t <sub>CYC</sub> |        | ns   |  |

| USB Full-speed S | Signaling                                                  |                       |        |      |  |

| r                | Transition Rise Time                                       | 4                     | 20     | ns   |  |

| t <sub>f</sub>   | Transition Fall Time                                       | 4                     | 20     | ns   |  |

| rfm              | Rise/Fall Time Matching; (t <sub>r</sub> /t <sub>f</sub> ) | 90                    | 110    | %    |  |

| tdrate           | Full-speed Data Rate                                       | 11.97                 | 12.03  | Mb/s |  |

| USB Low-speed    | Signaling                                                  |                       |        |      |  |

| t <sub>r</sub>   | Transition Rise Time                                       | 75                    | 300    | ns   |  |

| f                | Transition Fall Time                                       | 75                    | 300    | ns   |  |

| rfm              | Rise/Fall Time Matching; (t <sub>r</sub> /t <sub>f</sub> ) | 80                    | 120    | %    |  |

| tdrate           | Low-speed Data Rate                                        | 1.4775                | 1.5225 | Mb/s |  |

## 9.0 Switching Characteristics

Figure 9-2. USB Data Signal Timing

## 10.0 Ordering Information

| Ordering Code | Package Name | Description | Operating Range |

|---------------|--------------|-------------|-----------------|

| CY7C65100-SC  | S21          | 28-pin SOIC | Commercial      |

### 11.0 Package Diagram

##

All product and company names mentioned in this document are the trademarks of their respective holders.

| Document Title: CY7C65100 Four-port Universal Serial Bus Fixed-function Hub Controller Document Number: 38-08021 |         |               |                    |                       |

|------------------------------------------------------------------------------------------------------------------|---------|---------------|--------------------|-----------------------|

| REV.                                                                                                             | ECN NO. | Issue<br>Date | Orig. of<br>Change | Description of Change |

| **                                                                                                               | 113849  | 06/25/02      | BON                | New Data Sheet        |