1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## L6451

### 28 channel inkjet driver

### Features

- Multipower BCD technology

- 40 V DMOS output breakdown

- Precise output energy

- ESD output protection with clamping diodes

- Very low quiescent current

- PLCC44 package

#### Description

The L6451 is realized in Multipower BCD Technology which combines isolated DMOS power transistors with CMOS and Bipolar circuits on the same IC. By using mixed technology it has been possible to optimize the logic circuitry and the power stage to achieve the best possible performances.

#### Table 1.Device summary

| Order codes | Package                 |

|-------------|-------------------------|

| L6451       | PLCC44                  |

| L6451013TR  | PLCC44 in tape and reel |

| L6451DIE8   | DIE                     |

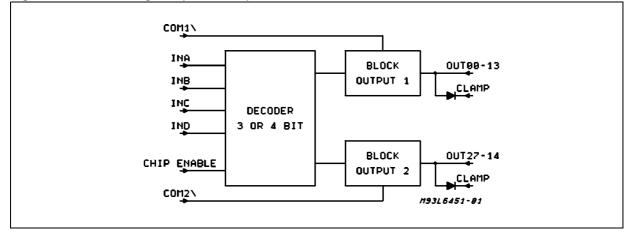

#### Figure 1. Block diagram (4-bit case)

Intended to be used in inkjet printer applications as a 4 to 28 (2 x 14) line selectable decoder/driver, the L6451 device driver has the advantages of low power CMOS inputs and logic, with 28 high current and high voltage DMOS outputs capable of sustaining a maximum of 40 V.

On system power up the output drivers are locked out using the chip enable function; two enable inputs are available for the different driver banks. An internal power-on system is implemented in order to avoid wrong output commutation during the supply voltage transients.

Using a mask option during manufacturing allows a different decoding. Control of the energy delivered to the print head is made by means of a special circuitry. All driver outputs are capable of withstanding a contact discharge of +/-8 kV with the IC biased.

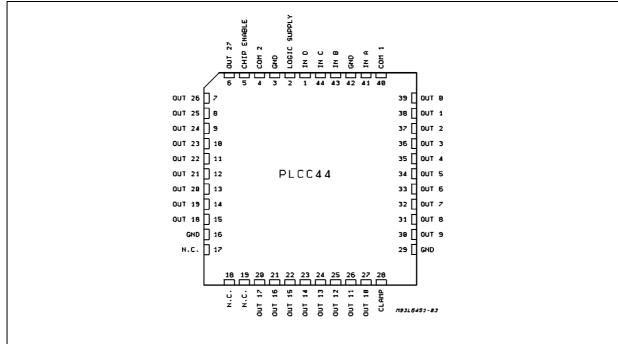

### 1 Pin information

#### Table 2. Pin description

| Pin Name           | Function                                                                                                                                                                                                                                                                                                                                   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>    | 5 V logic supply.                                                                                                                                                                                                                                                                                                                          |

| GND                | Logic and power ground.                                                                                                                                                                                                                                                                                                                    |

| OUT0 to OUT27      | DMOS outputs.                                                                                                                                                                                                                                                                                                                              |

| CLAMP              | This pin has to be connected to the power supply voltage of the head resistors. Each of the output DMOS have their drain connected with the anode of a protection diode, all the cathodes of the protection diodes are connected to the clamp pin. In order to have the device supplied, the CLAMP pin needs to be connected to the power. |

| INA, INB, INC, IND | Decoder inputs.                                                                                                                                                                                                                                                                                                                            |

| COM1, COM2         | A low logic input on these pins enables the outputs selected by the decoder inputs.                                                                                                                                                                                                                                                        |

| CHIP ENABLE        | A logic high enable the chip.                                                                                                                                                                                                                                                                                                              |

#### L6451

### 2 Electrical characteristics

| Symbol             | Parameter                                             | Value                         | Unit |

|--------------------|-------------------------------------------------------|-------------------------------|------|

| V <sub>OUT</sub>   | Output voltage                                        | 40                            | V    |

| V <sub>CLAMP</sub> | Output clamping voltage                               | 40                            | V    |

| I <sub>OUT</sub>   | Output continuous current                             | 0.8                           | A    |

| I <sub>PEAK</sub>  | Output peak current (with duty cycle = 10% TON= 4 ms) | 2                             | A    |

| TJ                 | Junction temperature                                  | 150                           | °C   |

| V <sub>DD</sub>    | Logic supply voltage                                  | 7                             | V    |

| V <sub>IN</sub>    | Input voltage range                                   | -0.3 V to V <sub>S</sub> +0.3 | V    |

| T <sub>amb</sub>   | Operating temperature range                           | 0 to 70                       | °C   |

| T <sub>stg</sub>   | Storage temperature range                             | -55 to 150                    | °C   |

#### Table 3.Absolute maximum ratings

#### Table 4. Thermal data

| Symbol                | Parameter                                | Value             | Unit  |

|-----------------------|------------------------------------------|-------------------|-------|

| R <sub>th j-amb</sub> | Thermal resistance junction-ambient max. | 65 <sup>(1)</sup> | ° C/W |

1. Device mounted on PCB.

#### Table 5.DC electrical characteristcs<sup>(1)</sup>

| Symbol             | Parameter                                                                                                    | Test Condition                                                     | Min.                 | Тур. | Max.          | Unit   |

|--------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------|------|---------------|--------|

| V <sub>DD</sub>    | Logic supply voltage                                                                                         |                                                                    | 4.75                 | 5    | 5.25          | V      |

| V <sub>CLAMP</sub> | Clamping voltage                                                                                             |                                                                    | 9                    |      | 38            | V      |

| V <sub>IL</sub>    | Low level input voltage                                                                                      |                                                                    |                      |      | 1.2           | V      |

| V <sub>IH</sub>    | High level input current                                                                                     |                                                                    | V <sub>DD</sub> -1.2 |      |               | V      |

| ILL                | Low level input current                                                                                      | V <sub>IN</sub> = V <sub>IL</sub>                                  |                      |      | -200          | μA     |

| I <sub>LH</sub>    | High level input current                                                                                     | V <sub>IN</sub> = V <sub>IH</sub>                                  |                      |      | 10            | μA     |

| I <sub>DD</sub>    | Logic supply current                                                                                         | (Independent from the output conditions)                           |                      |      | 5             | mA     |

|                    |                                                                                                              | Tj = 25 °C D.C. 0.4 A                                              |                      | 0.9  |               | V      |

| V                  | V <sub>OUT</sub> Output saturation voltage                                                                   | Tj = 25 °C D.C. 0.5 A                                              |                      | 1.1  |               | V      |

| VOUT               |                                                                                                              | Tj = 90 °C D.C. 0.4 A                                              |                      | 1.4  |               | V      |

|                    |                                                                                                              | Tj = 90 ° C D.C. 0.5 A                                             |                      | 1.7  |               | V      |

| ΔV <sub>CE</sub>   | Output saturation absolute<br>voltage variation around the<br>typ. values for extended<br>temperature ranges | Tj = 25° C to 90° C D.C.: 0.4 A<br>Tj = 25° C to 90° C D.C.: 0.5 A |                      |      | ±0.2<br>±0.25 | v<br>v |

| R <sub>DS</sub> ON |                                                                                                              |                                                                    |                      | 2.2  |               | Ω      |

1.  $T_{amb} = 25^{\circ}C$ ,  $V_{DD} = 5V$ ,  $V_{clamp} = 18$  V unless otherwise specified

| Symbol            | Signal Name                          | Parameter                                                    | Test<br>Condition                                                                     | Min. | Тур.             | Max. | Unit |

|-------------------|--------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------|------|------------------|------|------|

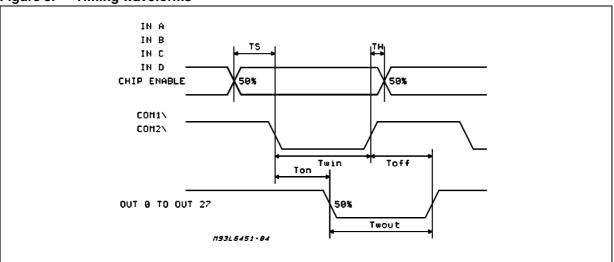

| Τ <sub>S</sub>    | INA, INB, INC,<br>IND Vs COMn        | SET - UP time                                                |                                                                                       | 30   |                  |      | ns   |

| т <sub>н</sub>    | INA, INB, INC,<br>IND Vs COMn        | HOLD time                                                    |                                                                                       | 0    |                  |      | ns   |

| T <sub>on</sub>   | COM1,2,3,4 V <sub>S</sub> OUT 0 to N | TURN - ON time                                               | I <sub>OUT</sub> = 0.5 A,<br>R <sub>L</sub> = 39 Ω<br>T <sub>j</sub> = 25 to<br>90 °C |      | 150              |      | ns   |

| T <sub>off</sub>  | COM1,2,3,4 V <sub>S</sub> OUT 0 to N | TURN - OFF time                                              | $I_{OUT}$ = 0.5 A,<br>R <sub>L</sub> = 39 Ω<br>T <sub>j</sub> = 25 to 90°C            |      | 150              |      | ns   |

| t <sub>r</sub>    |                                      | Rise time                                                    |                                                                                       |      | 100              |      | ns   |

| t <sub>f</sub>    |                                      | Fall time                                                    |                                                                                       |      | 100              |      | ns   |

| T <sub>wout</sub> |                                      | Output pulse<br>width                                        | $T_{win}$ = 3.5 ms<br>R <sub>L</sub> = 40 $\Omega$<br>I <sub>OUT</sub> = 0.5 A        | -20  | T <sub>win</sub> | +80  | ns   |

|                   |                                      | Maximum<br>allowable variation<br>of the output              | $R_L$ = 39 Ω<br>V <sub>CLAMP</sub> = 18 V                                             |      |                  | ±4   | %    |

| ΔP <sub>D</sub>   |                                      | power transmitted<br>by each driver to<br>the resistive load | R <sub>L</sub> = 40 Ω<br>V <sub>clamp</sub> = 18 V                                    |      | <u>+</u> 4       |      | %    |

| Table 6. AC electrical characteristics | Table 6. | AC electrical characteristics |

|----------------------------------------|----------|-------------------------------|

|----------------------------------------|----------|-------------------------------|

#### Figure 3. Timing waveforms

### 3 Functional description

#### Table 7.Decoder truth table

| IND | INC | INB | INA (LSB) | OUTPUTS |

|-----|-----|-----|-----------|---------|

| 0   | 0   | 0   | 0         | 0.27    |

| 0   | 0   | 0   | 1         | 1.26    |

| 0   | 0   | 1   | 0         | 2.25    |

| 0   | 0   | 1   | 1         | 3.24    |

| 0   | 1   | 0   | 0         | 4.23    |

| 0   | 1   | 0   | 1         | 5.22    |

| 0   | 1   | 1   | 0         | 6.21    |

| 0   | 1   | 1   | 1         | 7.20    |

| 1   | 0   | 0   | 0         | 8.19    |

| 1   | 0   | 0   | 1         | 9.18    |

| 1   | 0   | 1   | 0         | 10.17   |

| 1   | 0   | 1   | 1         | 11.16   |

| 1   | 1   | 0   | 0         | 12.15   |

| 1   | 1   | 0   | 1         | 13.14   |

| 1   | 1   | 1   | 0         | ALL OFF |

| 1   | 1   | 1   | 1         | ALL OFF |

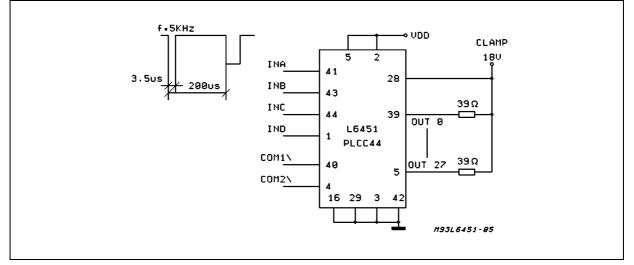

#### Figure 4. Application circuit

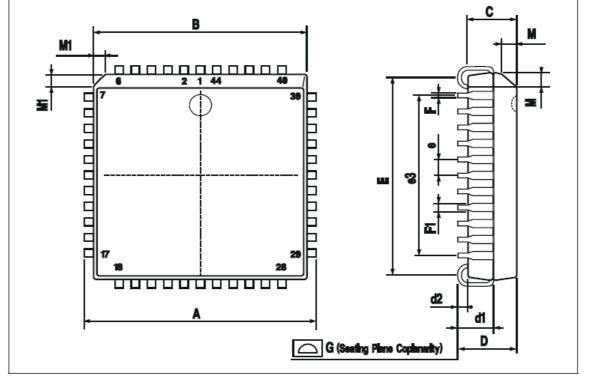

### 4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK® is an ST trademark.

| DIM. |       | mm   |       |       | inch  |       |

|------|-------|------|-------|-------|-------|-------|

|      | MIN.  | TYP. | MAX.  | MIN.  | TYP.  | MAX.  |

| А    | 17.4  |      | 17.65 | 0.685 |       | 0.695 |

| В    | 16.51 |      | 16.65 | 0.650 |       | 0.656 |

| С    | 3.65  |      | 3.7   | 0.144 |       | 0.146 |

| D    | 4.2   |      | 4.57  | 0.165 |       | 0.180 |

| d1   | 2.59  |      | 2.74  | 0.102 |       | 0.108 |

| d2   |       | 0.68 |       |       | 0.027 |       |

| E    | 14.99 |      | 16    | 0.590 |       | 0.630 |

| е    |       | 1.27 |       |       | 0.050 |       |

| e3   |       | 12.7 |       |       | 0.500 |       |

| F    |       | 0.46 |       |       | 0.018 |       |

| F1   |       | 0.71 |       |       | 0.028 |       |

| G    |       |      | 0.101 |       |       | 0.004 |

| М    |       | 1.16 |       |       | 0.046 |       |

| M1   |       | 1.14 |       |       | 0.045 |       |

Figure 5. PLCC44 mechanical data and package dimensions

57

### **Revision history**

| Date          | Revision | Description of Changes                                         |

|---------------|----------|----------------------------------------------------------------|

| Dec-2000      | 2        | First Issue in EDOCS dms                                       |

| May -2005     | 3        | Changed only look and feel layout                              |

| 02-Apr-2009 4 |          | Converted to corporate template.<br>Added ECOPACK information. |

Table 8.

Document revision history

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com