1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

December 2001 Revised December 2001

### FIN1532 5V LVDS 4-Bit High Speed Differential Receiver

#### **General Description**

FAIRCHILD

SEMICONDUCTOR

This quad receiver is designed for high speed interconnects utilizing Low Voltage Differential Signaling (LVDS) technology. The receiver translates LVDS levels, with a typical differential input threshold of 100 mV, to LVTTL signal levels. LVDS provides low EMI at ultra low power dissipation even at high frequencies. This device is ideal for high speed transfer of clock and data.

The FIN1532 can be paired with its companion driver, the FIN1531, or any other LVDS driver.

#### Features

- Greater than 400Mbs data rate

- 5V power supply operation

- 0.5 ns maximum differential pulse skew

- 3 ns maximum propagation delay

- Low power dissipation

- Power-Off protection for inputs and outputs

- Fail safe protection for open-circuit, shorted and terminated receiver inputs

- Meets or exceeds the TIA/EIA-644 LVDS standard

- Pin compatible with equivalent RS-422 and PECL devices

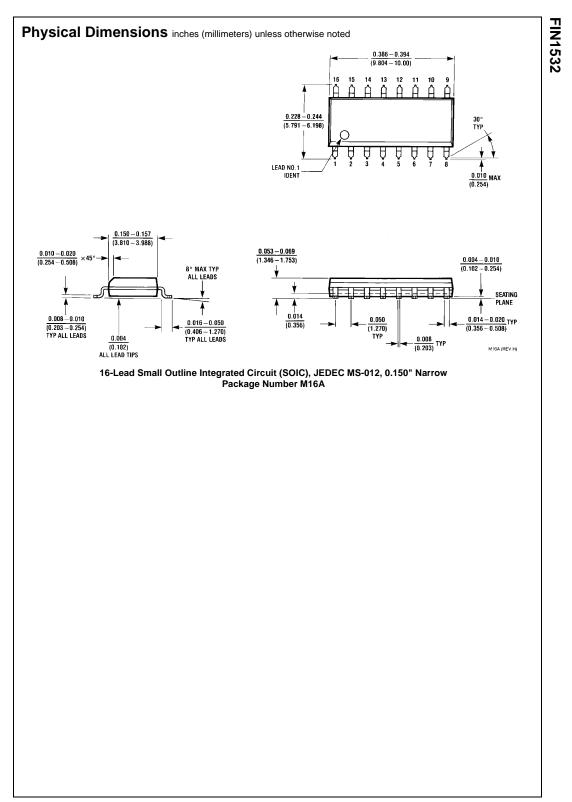

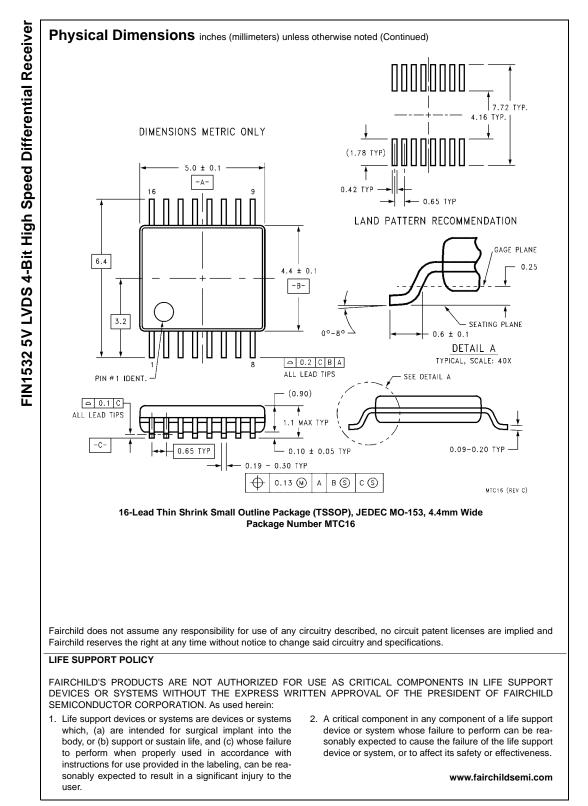

- 16-Lead SOIC and TSSOP packages save space

#### **Ordering Code:**

| Order Number                                                                                              | Package Number | Package Description                                                          |  |  |

|-----------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------|--|--|

| FIN1532M                                                                                                  | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |  |  |

| FIN1532MTC                                                                                                | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |  |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                              |  |  |

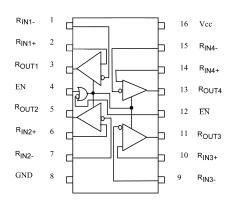

#### **Pin Descriptions**

| Pin Name                                                                      | Description                 |

|-------------------------------------------------------------------------------|-----------------------------|

| R <sub>OUT1</sub> , R <sub>OUT2</sub> , R <sub>OUT3</sub> , R <sub>OUT4</sub> | LVTTL Data Outputs          |

| $R_{IN1+}, R_{IN2+}, R_{IN3+}, R_{IN4+}$                                      | Non-inverting LVDS Inputs   |

| R <sub>IN1-</sub> , R <sub>IN2-</sub> , R <sub>IN3-</sub> , R <sub>IN4-</sub> | Inverting LVDS Inputs       |

| EN                                                                            | Driver Enable Pin           |

| EN                                                                            | Inverting Driver Enable Pin |

| V <sub>CC</sub>                                                               | Power Supply                |

| GND                                                                           | Ground                      |

#### **Function Table**

|    | Input |                  |                  | Outputs          |

|----|-------|------------------|------------------|------------------|

| EN | EN    | R <sub>IN+</sub> | R <sub>IN+</sub> | R <sub>OUT</sub> |

| Н  | Х     | Н                | L                | Н                |

| Н  | Х     | L                | Н                | L                |

| Н  | Х     | Fail Safe        | Condition        | Н                |

| Х  | L     | Н                | L                | Н                |

| Х  | L     | L                | Н                | L                |

| Х  | L     | Fail Safe        | Condition        | Н                |

| L  | Н     | )                | X                | Z                |

#### **Connection Diagram**

Top View

© 2001 Fairchild Semiconductor Corporation DS500504

#### Absolute Maximum Ratings(Note 1)

| Supply Voltage (V <sub>CC</sub> )             | -0.5 V to +6 V                    |

|-----------------------------------------------|-----------------------------------|

| DC Input Voltage (V <sub>IN</sub> )           |                                   |

| Enable Inputs                                 | -0.5 V to +6 V                    |

| Receiver Inputs                               | -0.5 V to +6 V                    |

| DC Output Voltage (V <sub>OUT</sub> )         | -0.5 V to +6 V                    |

| DC Output Current (I <sub>O</sub> )           | 16 mA                             |

| Storage Temperature Range (T <sub>STG</sub> ) | $-65^{\circ}C$ to $+150^{\circ}C$ |

| Max Junction Temperature (T <sub>J</sub> )    | 150°C                             |

| Lead Temperature (T <sub>L</sub> )            |                                   |

| (Soldering, 10 seconds)                       | 260°C                             |

| ESD (Human Body Model)                        | ≥ 8000 V                          |

| ESD (Machine Model)                           | ≥ 300 V                           |

|                                               |                                   |

## Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )       | 4.5 V to 5.5 V                                    |

|-----------------------------------------|---------------------------------------------------|

| Input Voltage (V <sub>IN</sub> )        |                                                   |

| Enable Inputs                           | 0 to V <sub>CC</sub>                              |

| Receiver Inputs                         | 0 to 2.4 V                                        |

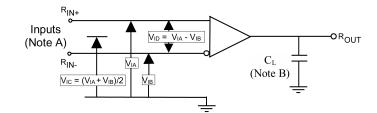

| Magnitude of Differential Voltage       |                                                   |

| ( V <sub>ID</sub>  )                    | 100 mV to 600 mV                                  |

| Common-mode Input Voltage               |                                                   |

| (V <sub>IC</sub> )                      | V <sub>ID</sub>  /2 to (2.4– V <sub>ID</sub>  /2) |

| Operating Temperature (T <sub>A</sub> ) | -40°C to +85°C                                    |

Note 1: The "Absolute Maximum Ratings": are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature and output/input loading variables. Fairchild does not recommend operation of circuits outside databook specification.

#### **DC Electrical Characteristics**

Over supply voltage and operating temperature ranges, unless otherwise specified

| Symbol              | Parameter                         | Test Conditions                                                                | Min                  | Typ<br>(Note 2) | Max             | Units |

|---------------------|-----------------------------------|--------------------------------------------------------------------------------|----------------------|-----------------|-----------------|-------|

| V <sub>TH</sub>     | Differential Input Threshold HIGH | V <sub>IC</sub> = +1.2V, See Figure 1                                          |                      |                 | 100             | mV    |

| V <sub>TL</sub>     | Differential Input Threshold LOW  | V <sub>IC</sub> = +1.2V, See Figure 1                                          | -100                 |                 |                 | mV    |

| I <sub>IN</sub>     | Input Current EN or EN            | $V_{IN} = 0V \text{ or } V_{CC}, V_{CC} = 5.5 \text{ or } 0V$                  |                      |                 | ±20             | μA    |

|                     | Input Current Receiver Inputs     | $V_{IN} = 0V \text{ or } 2.4 \text{ V}, V_{CC} = 5.5 \text{ or } 0V$           |                      |                 | ±20             | μA    |

| V <sub>IH</sub>     | Input High Voltage (EN or EN)     |                                                                                | 2.0                  |                 | V <sub>CC</sub> | V     |

| V <sub>IL</sub>     | Input Low Voltage (EN or EN)      |                                                                                | GND                  |                 | 0.8             | V     |

| V <sub>OH</sub>     | Output HIGH Voltage               | $I_{OH} = -100 \ \mu A$                                                        | V <sub>CC</sub> -0.2 | 4.98            |                 | v     |

|                     |                                   | I <sub>OH</sub> = -8 mA                                                        | 3.8                  | 4.68            |                 | v     |

| V <sub>OL</sub>     | Output LOW Voltage                | I <sub>OH</sub> = 100 μA                                                       |                      | 0.01            | 0.2             | v     |

|                     |                                   | I <sub>OL</sub> = 8 mA                                                         |                      | 0.22            | 0.5             |       |

| V <sub>IK</sub>     | Input Clamp Voltage               | $I_{IK} = -18 \text{ mA}$                                                      | -1.5                 | -0.8            |                 | V     |

| I <sub>OZ</sub>     | Disabled Output Leakage Current   | $EN = 0.8$ and $\overline{EN} = 2V$ , $V_{OUT} = 5.5V$ or $0V$                 |                      |                 | ±20             | μA    |

| I <sub>O(OFF)</sub> | Power-OFF Output Current          | $V_{OUT} = 0V$ or 5.5V, $V_{CC} = 0V$                                          |                      |                 | 50              | μA    |

| I <sub>OS</sub>     | Output Short Circuit Test         | Receiver Enabled, V <sub>OUT</sub> = 0V<br>(one output shorted at a time)      | -15                  |                 | -100            | mA    |

| I <sub>CCZ</sub>    | Disabled Power Supply Current     | Receiver Disabled                                                              |                      | 1.2             | 5               | mA    |

| I <sub>CC</sub>     | Power Supply Current              | Receiver Enabled, $R_{IN+} = 1V$ and $R_{IN-} = 1.4V$                          |                      | 11              | 17              | mA    |

| I <sub>PU/PD</sub>  | Output Power Up/Power Down        | Receiver Enabled, $R_{IN+} = 1.4V$ and $R_{IN-} = 1V$<br>$V_{CC} = 0V$ to 2.0V |                      | 15              | 23<br>+20       | μA    |

| יפט/פט              | High Z Leakage Current            |                                                                                |                      |                 | <u></u> 0       | μΑ    |

| C <sub>IN</sub>     | Input Capacitance                 |                                                                                |                      | 5.5             |                 | pF    |

| COUT                | Output Capacitance                |                                                                                |                      | 4.5             |                 | pF    |

Note 2: All typical values are at  $T_A$  = 25°C and with  $V_{CC}$  = 5V.

| Symbol                                       | Parameter                                       | Test Conditions                                                         | Min | Typ<br>(Note 3) | Max  | Units |

|----------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|-----|-----------------|------|-------|

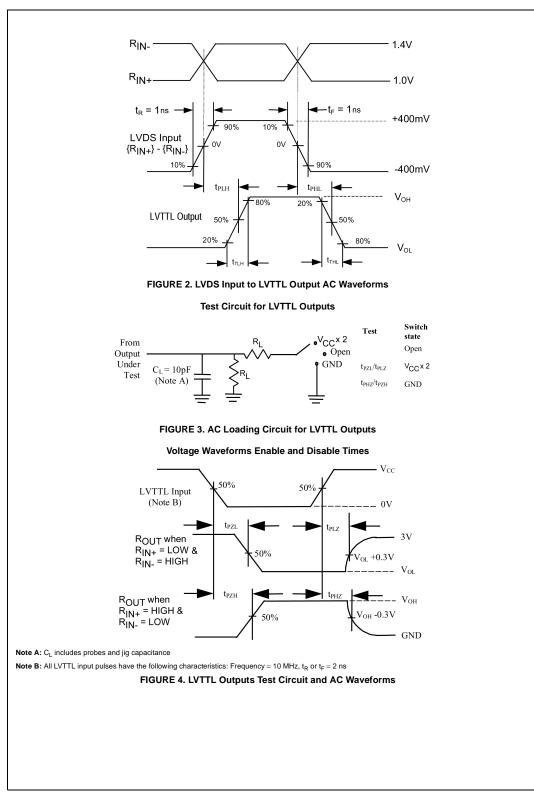

| t <sub>PLH</sub>                             | Propagation Delay<br>LOW-to-HIGH                |                                                                         | 1.0 | 2.0             | 3.0  | ns    |

| t <sub>PHL</sub>                             | Propagation Delay<br>HIGH-to-LOW                | $ V_{ID}  = 400$ mV, $C_L = 10$ pF, $R_L = 1k\Omega$                    | 1.0 | 2.0             | 3.0  | ns    |

| t <sub>TLH</sub>                             | Output Rise Time (20% to 80%)                   | See Figure 1 and Figure 2                                               |     | 1.3             |      | ns    |

| t <sub>THL</sub>                             | Output Fall Time (80% to 20%)                   |                                                                         |     | 1.1             |      | ns    |

| t <sub>SK(P)</sub>                           | Pulse Skew  t <sub>PLH</sub> - t <sub>PHL</sub> | -                                                                       |     | 0.2             | 0.5  | ns    |

| t <sub>SK(LH)</sub> ,<br>t <sub>SK(HL)</sub> | Channel-to-Channel Skew<br>(Note 4)             |                                                                         |     | 0.1             | 0.3  | ns    |

| t <sub>SK(PP)</sub>                          | Part-to-Part Skew (Note 5)                      |                                                                         |     |                 | 1.0  | ns    |

| f <sub>MAX</sub>                             | Maximum Operating Frequency<br>(Note 6)         | $R_L = 1k\Omega$ , $C_L = 10 \text{ pF}$ ,<br>See Figure 1 and Figure 2 | 200 | 260             |      | MHz   |

| t <sub>ZH</sub>                              | LVTTL Output Enable Time from Z to HIGH         | $R_L = 1k\Omega$ , $C_L = 10 \text{ pF}$ ,                              |     | 8               | 12.0 | ns    |

| t <sub>ZL</sub>                              | LVTTL Output Enable Time from Z to LOW          | See Figure 3 and Figure 4                                               |     | 8               | 12.0 | ns    |

| t <sub>HZ</sub>                              | LVTTL Output Disable Time from HIGH to Z        |                                                                         |     | 4               | 8.0  | ns    |

| t <sub>LZ</sub>                              | LVTTL Output Disable Time from LOW to Z         |                                                                         |     | 4               | 8.0  | ns    |

Note 3: All typical values are at  $T_A$  = 25°C and with  $V_{CC}$  = 5V.

Note 4: t<sub>SK(LH)</sub>, t<sub>SK(HL)</sub> is the skew between specified outputs of a single device when the outputs have identical loads and are switching in the same direction.

Note 5:  $t_{SK(PP)}$  is the magnitude of the difference in propagation delay times between any specified terminals of two devices switching in the same direction (either LOW-to-HIGH or HIGH-to-LOW) when both devices operate with the same supply voltage, same temperature, and have identical test circuits. Note 6:  $f_{MAX}$  Criteria: Input  $t_R = t_F < 1$  ns,  $V_{ID} = 300$  mV, (1.05V to 1.35V pp), 50% duty cycle; Output duty cycle 40% to 60%,  $V_{OL} < 0.5V$ ,  $V_{OH} > 2.4V$ . All channels switching in phase.

Note A: All input pulses have frequency = 10 MHz,  $t_R$  or  $t_F$  = 1 ns Note B:  $C_L$  includes all probe and jig capacitances

FIGURE 1. Differential Receiver Voltage Definitions and Propagation Delay