1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

November 1999 Revised January 2005

### FAIRCHILD

SEMICONDUCTOR TM

### USB1T11A Universal Serial Bus Transceiver

#### **General Description**

The USB1T11A is a one chip generic USB transceiver. It is designed to allow 5.0V or 3.3V programmable and standard logic to interface with the physical layer of the Universal Serial Bus. It is capable of transmitting and receiving serial data at both full speed (12Mbit/s) and low speed (1.5Mbit/s) data rates.

The input and output signals of the USB1T11A conform with the "Serial Interface Engine". Implementation of the Serial Interface Engine along with the USB1T11A allows the designer to make USB compatible devices with off-theshelf logic and easily modify and update the application.

#### **Features**

- Complies with Universal Serial Bus specification 1.1

- Utilizes digital inputs and outputs to transmit and receive USB cable data

- Supports 12Mbit/s "Full Speed" and 1.5Mbit/s "Low Speed" serial data transmission

- Compatible with the VHDL "Serial Interface Engine" from USB Implementers' Forum

- Supports single-ended data interface

- Single 3.3V supply

- ESD Performance: Human Body Model > 9.5 kV on D-, D+ pins only

- > 4 kV on all other pins

- 16-lead Pb-Free MLP package saves space

### **Ordering Code:**

| Order Number            | Package<br>Number | Package Description                                                                  |

|-------------------------|-------------------|--------------------------------------------------------------------------------------|

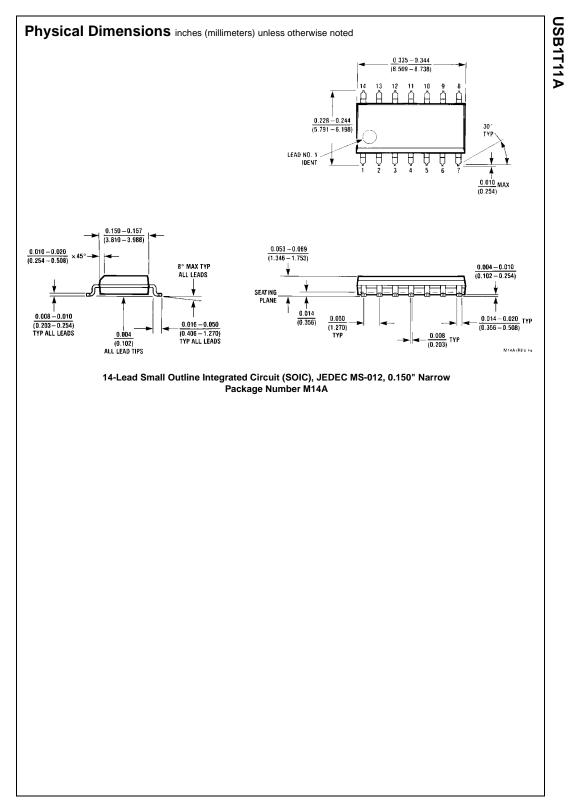

| USB1T11AM<br>(Note 1)   | M14A              | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow         |

| USB1T11AM_NL            | M14A              | Pb-Free 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

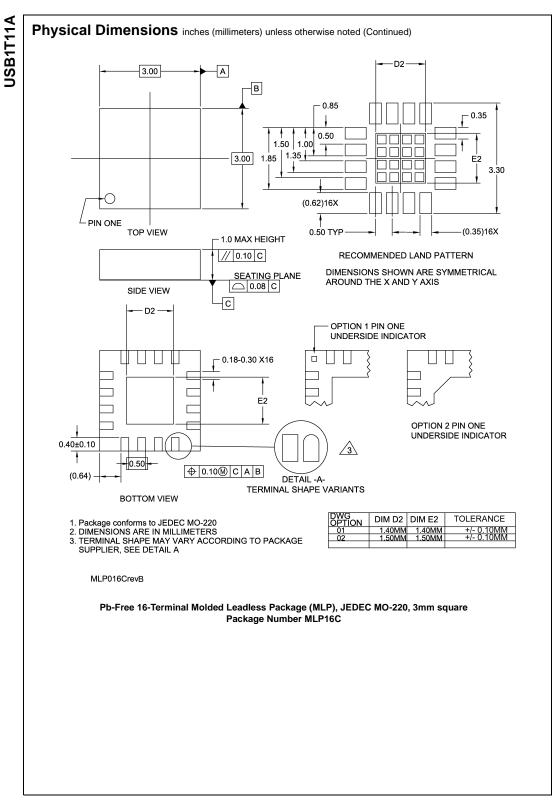

| USB1T11ABQX             | MLP16C            | Pb-Free 16-Terminal Molded Leadless Package (MLP), JEDEC MO-220, 3mm square          |

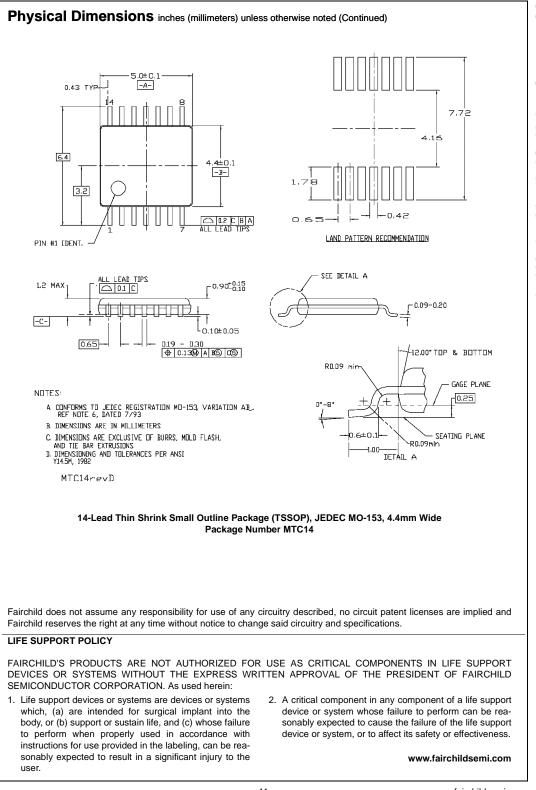

| USB1T11AMTC<br>(Note 1) | MTC14             | 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide          |

| USB1T11AMTC_NL          | MTC14             | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

| USB1T11AMTCX_NL         | MTC14             | Pb-Free 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

Pb-Free package per JEDEC J-STD-020B.

Note 1: Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

#### **Connection Diagrams**

#### Pin Assignments for SOIC and TSSOP Pin Assignments for MLP MODE 14 Vcc Speed S -VMO/FSEO ÷ 13 10 11 9 BCV 12 -VPO NC 8 -D+ VF NC 14 7 GND -D-VМ 10 6 SUSPND VMO/FSEC 15 SUSPND SPEED VM GND NC

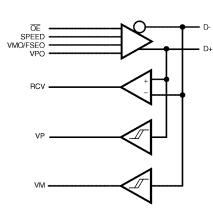

### Logic Diagram

### **Pin Descriptions**

| Pin Name                                            | I/O  |                                                  |                                                                                                                                                     | Description                                                 |                                         |  |  |  |  |

|-----------------------------------------------------|------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------|--|--|--|--|

| RCV                                                 | 0    | Receive data. CMOS                               | level output for US                                                                                                                                 | B differential input                                        |                                         |  |  |  |  |

| OE                                                  | Ι    | Output Enable. Active active the transceiver     |                                                                                                                                                     | transceiver to transmit da                                  | ta on the bus. When not                 |  |  |  |  |

| MODE                                                | Ι    |                                                  | ode. When left unconnected, a weak pull-up transistor pulls it to $V_{CC}$ and in this GND, the MO/FSEO pin takes the function of FSEO (Force SEO). |                                                             |                                         |  |  |  |  |

| V <sub>PO</sub> , V <sub>MO</sub> /F <sub>SEO</sub> | Ι    | Inputs to differential d                         | river. (Outputs fron                                                                                                                                | n SIE).                                                     |                                         |  |  |  |  |

|                                                     |      | MODE                                             | VPO                                                                                                                                                 | VMO/FSEO                                                    | RESULT                                  |  |  |  |  |

|                                                     |      | 0                                                | 0                                                                                                                                                   | 0                                                           | Logic "0"                               |  |  |  |  |

|                                                     |      |                                                  | 0                                                                                                                                                   | 1                                                           | SE0                                     |  |  |  |  |

|                                                     |      |                                                  | 1                                                                                                                                                   | 0                                                           | Logic "1"                               |  |  |  |  |

|                                                     |      |                                                  | 1                                                                                                                                                   | 1                                                           | SEO                                     |  |  |  |  |

|                                                     |      | 1                                                | 0                                                                                                                                                   | 0                                                           | SE0                                     |  |  |  |  |

|                                                     |      |                                                  | 0                                                                                                                                                   | 1                                                           | Logic "0"                               |  |  |  |  |

|                                                     |      |                                                  | 1                                                                                                                                                   | 0                                                           | Logic "1"                               |  |  |  |  |

|                                                     |      |                                                  | 1                                                                                                                                                   | 1                                                           | Illegal code                            |  |  |  |  |

| V <sub>P</sub> , V <sub>M</sub>                     | 0    |                                                  |                                                                                                                                                     | e logic "0" and logic "1". Us<br>nnect speed. (Input to SIE | sed to detect single ended ).           |  |  |  |  |

|                                                     |      | VP                                               | VM                                                                                                                                                  | RESULT                                                      |                                         |  |  |  |  |

|                                                     |      | 0                                                | 0                                                                                                                                                   | SE0                                                         |                                         |  |  |  |  |

|                                                     |      | 0                                                | 1                                                                                                                                                   | Low Speed                                                   |                                         |  |  |  |  |

|                                                     |      | 1                                                | 0                                                                                                                                                   | Full Speed                                                  |                                         |  |  |  |  |

|                                                     |      | 1                                                | 1                                                                                                                                                   | Error                                                       |                                         |  |  |  |  |

| D+, D–                                              | AI/O | Data+, Data Differer                             | ntial data bus confo                                                                                                                                | orming to the Universal Se                                  | rial Bus standard.                      |  |  |  |  |

| SUSPND                                              | Ι    |                                                  |                                                                                                                                                     | ile the USB bus is inactive<br>"0" state. Both D+ and D–    | . While the suspend pin is are 3-STATE. |  |  |  |  |

| SPEED                                               | Ι    | Edge rate control. Log<br>Logic "0" operates edg |                                                                                                                                                     | edge rates for "full speed".<br>beed".                      |                                         |  |  |  |  |

| V <sub>CC</sub>                                     |      | 3.0V to 3.6V power su                            | lpply                                                                                                                                               |                                                             |                                         |  |  |  |  |

| GND                                                 |      | Ground reference                                 |                                                                                                                                                     |                                                             |                                         |  |  |  |  |

### **Functional Truth Table**

|      |     | Input    |    |        | I/ | 0  |     | Outputs |                |             |

|------|-----|----------|----|--------|----|----|-----|---------|----------------|-------------|

| Mode | VPO | VMO/FSEO | OE | SUSPND | D+ | D- | RCV | VP      | V <sub>M</sub> | Result      |

| 0    | 0   | 0        | 0  | 0      | 0  | 1  | 0   | 0       | 1              | Logic 0     |

| 0    | 0   | 1        | 0  | 0      | 0  | 0  | U   | 0       | 0              | SEO         |

| 0    | 1   | 0        | 0  | 0      | 1  | 0  | 1   | 1       | 0              | Logic 1     |

| 0    | 1   | 1        | 0  | 0      | 0  | 0  | U   | 0       | 0              | SEO         |

| 1    | 0   | 0        | 0  | 0      | 0  | 0  | U   | 0       | 0              | SEO         |

| 1    | 0   | 1        | 0  | 0      | 0  | 1  | 0   | 0       | 1              | Logic 0     |

| 1    | 1   | 0        | 0  | 0      | 1  | 0  | 1   | 1       | 0              | Logic 1     |

| 1    | 1   | 1        | 0  | 0      | 1  | 1  | U   | U       | U              | Illegal Coc |

| Х    | Х   | Х        | 1  | 0      | Z  | Z  | U   | U       | U              | D+/D- Hi-   |

| Х    | Х   | Х        | 1  | 1      | Z  | Z  | U   | U       | U              | D+/D- Hi-   |

X = Don't Care Z = 3-STATE U = Undefined State

www.fairchildsemi.com

USB1T11A

USB1T11A

### Absolute Maximum Ratings(Note 2)

|                                                                      | -                                     |

|----------------------------------------------------------------------|---------------------------------------|

| DC Supply Voltage (V <sub>CC</sub> )                                 | -0.5V to +7.0V                        |

| DC Input Diode Current (IIK)                                         |                                       |

| V <sub>1</sub> < 0                                                   | –50 mA                                |

| Input Voltage (V <sub>I</sub> )                                      |                                       |

| (Note 3)                                                             | -0.5V to +5.5V                        |

| Input Voltage (V <sub>I/O</sub> )                                    | –0.5V to $V_{CC}$ + 0.5V              |

| Output Diode Current (I <sub>OK</sub> )                              |                                       |

| $V_{O} > V_{CC}$ or $V_{O} < 0$                                      | ±50 mA                                |

| Output Voltage (V <sub>O</sub> )                                     |                                       |

| (Note 3)                                                             | –0.5V to $V_{CC}$ + 0.5V              |

| Output Source or Sink Current (I <sub>O</sub> )                      |                                       |

| VP.VM, RCV pins                                                      |                                       |

| $V_0 = 0$ to $V_{CC}$                                                | ±15 mA                                |

| Output Source or Sink Current (I <sub>O</sub> )                      |                                       |

| D+/D- pins                                                           |                                       |

| $V_0 = 0$ to $V_{CC}$                                                | ±50 mA                                |

| V <sub>CC</sub> or GND Current (I <sub>CC</sub> , I <sub>GND</sub> ) | ±100 mA                               |

| Storage Temperature (T <sub>STO</sub> )                              | $-60^{\circ}C$ to $+$ 150 $^{\circ}C$ |

|                                                                      |                                       |

## Recommended Operating Conditions

| Supply Voltage V <sub>CC</sub>            | 3.0V to 3.6V                     |

|-------------------------------------------|----------------------------------|

| Input Voltage (V <sub>I</sub> )           | 0V to 5.5V                       |

| Input Range for AI/O (V <sub>AI/O</sub> ) | 0V to $V_{CC}$                   |

| Output Voltage (V <sub>O</sub> )          | 0V to $V_{CC}$                   |

| Operating Ambient Temperature             |                                  |

| in free air (T <sub>amb</sub> )           | $-40^{\circ}C$ to $+85^{\circ}C$ |

Note 2: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristic tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 3: The input and output voltage ratings may be exceeded if the input and output clamp current ratings are observed.

#### DC Electrical Characteristics (Digital Pins)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted).  $V_{CC} = 3.0V$  to 3.6V

|                   |                             |                                                      |                       | Limits       |       | Unit |

|-------------------|-----------------------------|------------------------------------------------------|-----------------------|--------------|-------|------|

| Symbol            | Parameter                   | Test Conditions                                      | Temp                  | = -40°C to - | +85°C |      |

|                   |                             |                                                      | Min                   | Тур          | Max   |      |

|                   | INPUT LEVELS:               | ·                                                    |                       |              |       |      |

| VIL               | LOW Level Input Voltage     |                                                      |                       |              | 0.8   | V    |

| VIH               | HIGH Level Input Voltage    |                                                      | 2.0                   |              |       | V    |

|                   | OUTPUT LEVELS:              |                                                      |                       |              |       |      |

| V <sub>OL</sub>   | LOW Level Output Voltage    | $I_{OL} = 4 \text{ mA}$                              |                       |              | 0.4   | V    |

|                   |                             | $I_{OL} = 20 \ \mu A$                                |                       |              | 0.1   | v    |

| V <sub>OH</sub>   | HIGH Level Output Voltage   | I <sub>OH</sub> = 4 mA                               | 2.4                   |              |       | V    |

|                   |                             | I <sub>OH</sub> = 20 μA                              | V <sub>CC</sub> - 0.1 |              |       | v    |

|                   | LEAKAGE CURRENT:            |                                                      |                       |              |       |      |

| IL.               | Input Leakage Current       | V <sub>CC</sub> = 3.0 to 3.6                         |                       |              | ±5    | μΑ   |

| I <sub>CCFS</sub> | Supply Current (Full Speed) | V <sub>CC</sub> = 3.0 to 3.6                         |                       |              | 5     | mA   |

| I <sub>CCLS</sub> | Supply Current (Low Speed)  | V <sub>CC</sub> = 3.0 to 3.6                         |                       |              | 5     | mA   |

| Iccq              | Quiescent Current           | V <sub>CC</sub> = 3.0 to 3.6                         |                       |              | 5     | mA   |

|                   |                             | $V_{IN} = V_{CC}$ or GND                             |                       |              | 5     | MA   |

| Iccs              | Supply Current in Suspend   | V <sub>CC</sub> = 3.0 to 3.6; Mode = V <sub>CC</sub> |                       |              | 10    | μΑ   |

|                           | er recommended range of supply voltage and operating free air temperature (unless otherwise noted). V <sub>CC</sub> = 3.0V to 3.6V Limits |                                 |      |              |       |       |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------|--------------|-------|-------|--|--|

| Symbol                    | Parameter                                                                                                                                 | Test Conditions                 | Temp | = −40°C to - | +85°C | Units |  |  |

| 0,                        |                                                                                                                                           |                                 | Min  | Тур          | Max   |       |  |  |

|                           | INPUT LEVELS:                                                                                                                             | ·                               | •    |              | •     |       |  |  |

| V <sub>DI</sub>           | Differential Input Sensitivity                                                                                                            | (D+) - (D-)                     | 0.2  |              |       | V     |  |  |

| V <sub>CM</sub>           | Differential Common Mode Range                                                                                                            | Includes V <sub>DI</sub> Range  | 0.8  |              | 2.5   | V     |  |  |

| V <sub>SE</sub>           | Single Ended Receiver Threshold                                                                                                           |                                 | 0.8  |              | 2.0   | V     |  |  |

|                           | OUTPUT LEVELS:                                                                                                                            | •                               | •    |              |       |       |  |  |

| V <sub>OL</sub>           | Static Output LOW Voltage                                                                                                                 | $R_L$ of 1.5 k $\Omega$ to 3.6V |      |              | 0.3   | V     |  |  |

| V <sub>OH</sub>           | Static Output HIGH Voltage                                                                                                                | $R_L$ of 15 k $\Omega$ to GND   | 2.8  |              | 3.6   | V     |  |  |

| V <sub>CR</sub>           | Differential Crossover                                                                                                                    |                                 | 1.3  |              | 2.0   | V     |  |  |

|                           | LEAKAGE CURRENT:                                                                                                                          | ·                               | •    |              |       |       |  |  |

| I <sub>OZ</sub>           | High Z State Data Line Leakage Current                                                                                                    | 0V < V <sub>IN</sub> < 3.3V     |      |              | ±5    | μΑ    |  |  |

|                           | CAPACITANCE:                                                                                                                              | ·                               | •    |              |       |       |  |  |

| C <sub>IN</sub> (Note 5)  | Transceiver Capacitance                                                                                                                   | Pin to GND                      |      |              | 10    | pF    |  |  |

|                           | Capacitance Match                                                                                                                         |                                 |      |              | 10    | %     |  |  |

|                           | OUTPUT RESISTANCE:                                                                                                                        | •                               | •    | •            | •     |       |  |  |

| Z <sub>DRV</sub> (Note 4) | Driver Output Resistance                                                                                                                  | Steady State Drive              | 4    |              | 20    | Ω     |  |  |

|                           | Resistance Match                                                                                                                          |                                 |      |              | 10    | %     |  |  |

Note 4: Excludes external resistor. In order to comply with USB Specification 1.1, external series resistors of  $24\Omega \pm 1\%$  each on D+ and D- are remended. This specification is guaranteed by design and statistical process distribution.

Note 5: This specification is guaranteed by design and statistical process distribution.

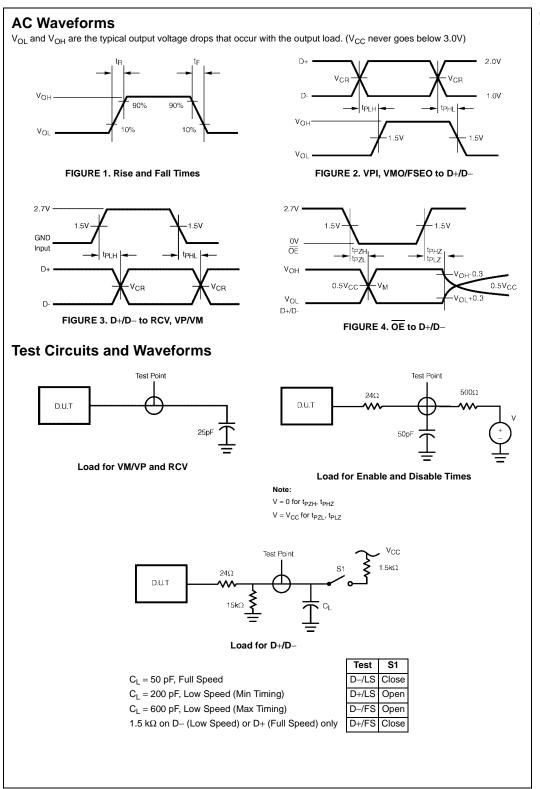

#### AC Electrical Characteristics (D+/D- Pins, Full Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted). V<sub>CC</sub> = 3.0V to 3.6V C<sub>L</sub> = 50 pF; R<sub>L</sub> = 1.5 k $\Omega$  on D+ to V<sub>CC</sub>

|                  |                                 |                |         | Limits |     |    |

|------------------|---------------------------------|----------------|---------|--------|-----|----|

| Symbol           | Parameter                       | Test Condition | Temp    | Units  |     |    |

|                  |                                 |                | Min Typ |        | Max | 1  |

|                  | DRIVER CHARACTERISTICS:         |                | •       |        |     |    |

|                  |                                 | 10% and 90%    |         |        |     | ns |

| t <sub>R</sub>   | Rise Time                       | Figure 1       | 4       |        | 20  |    |

| t <sub>F</sub>   | Fall Time                       | Figure 1       | 4       |        | 20  |    |

| t <sub>RFM</sub> | Rise/Fall Time Matching         | $(t_r/t_f)$    | 90      |        | 110 | %  |

| V <sub>CRS</sub> | Output Signal Crossover Voltage |                | 1.3     |        | 2.0 | V  |

|                  | DRIVER TIMINGS:                 | ·              |         |        |     |    |

| t <sub>PLH</sub> | Driver Propagation Delay        | Figure 2       |         |        | 18  | ns |

| t <sub>PLH</sub> | (VPO, VMO/FSEO to D+/D-)        | Figure 2       |         |        | 18  | ns |

| t <sub>PHZ</sub> | Driver Disable Delay            | Figure 4       |         |        | 13  | ns |

| t <sub>PLZ</sub> | (OE to D+/D-)                   | Figure 4       |         |        | 13  | ns |

| t <sub>PZH</sub> | Driver Enable Delay             | Figure 4       |         |        | 17  | ns |

| t <sub>PZL</sub> | (OE to D+/D-)                   | Figure 4       |         |        | 17  | ns |

|                  | RECEIVER TIMINGS:               | ·              |         |        |     |    |

| t <sub>PLH</sub> | Receiver Propagation Delay      | Figure 3       |         |        | 16  | ns |

| t <sub>PHL</sub> | (D+, D- to RCV)                 | Figure 3       |         |        | 19  | ns |

| t <sub>PLH</sub> | Single-ended Receiver Delay     | Figure 3       |         |        | 8   | ns |

| t <sub>PHL</sub> | (D+, D- to VP, VM)              | Figure 3       |         |        | 8   | ns |

5

**USB1T11A**

### AC Electrical Characteristics (D+/D- Pins, Low Speed)

Over recommended range of supply voltage and operating free air temperature (unless otherwise noted). V<sub>CC</sub> = 3.0V to 3.6V  $C_L$  = 200 pF to 600 pF;  $R_L$  = 1.5k $\Omega$  on D– to V<sub>CC</sub>

|                  |                                 |                 |                                                   | Limits |     |      |

|------------------|---------------------------------|-----------------|---------------------------------------------------|--------|-----|------|

| Symbol           | Parameter                       | Test Conditions | $T_{amb} = -40^{\circ}C \text{ to } +85^{\circ}C$ |        |     | Unit |

|                  |                                 |                 | Min Typ                                           |        | Max |      |

|                  | DRIVER CHARACTERISTICS:         | •               |                                                   |        |     |      |

|                  |                                 | 10% and 90%     |                                                   |        |     |      |

| t <sub>LR</sub>  | Rise Time                       | Figure 1        | 75                                                |        | 300 | ns   |

| t <sub>LF</sub>  | Fall Time                       | Figure 1        | 75                                                |        | 300 |      |

| t <sub>RFM</sub> | Rise/Fall Time Matching         | $(t_r/t_f)$     | 80                                                |        | 120 | %    |

| V <sub>CRS</sub> | Output Signal Crossover Voltage |                 | 1.3                                               |        | 2.0 | V    |

|                  | DRIVER TIMINGS:                 |                 | •                                                 |        |     |      |

| t <sub>PLH</sub> | Driver Propagation Delay        | Figure 2        |                                                   |        | 300 | ns   |

| t <sub>PHL</sub> | (VPO, VMO/FSEO to D+/D-)        | Figure 2        |                                                   |        | 300 | ns   |

| t <sub>PHZ</sub> | Driver Disable Delay            | Figure 4        |                                                   |        | 13  | ns   |

| t <sub>PLZ</sub> | (OE to D+/D-)                   | Figure 4        |                                                   |        | 13  | ns   |

| t <sub>PZH</sub> | Driver Enable Delay             | Figure 4        |                                                   |        | 205 | ns   |

| t <sub>PZL</sub> | (OE to D+/D-)                   | Figure 4        |                                                   |        | 205 | ns   |

|                  | RECEIVER TIMINGS:               |                 |                                                   |        | •   |      |

| t <sub>PLH</sub> | Receiver Propagation Delay      | Figure 3        |                                                   |        | 18  | ns   |

| t <sub>PHL</sub> | (D+, D- to RCV)                 | Figure 3        |                                                   |        | 18  | ns   |

| t <sub>PLH</sub> | Single-ended Receiver Delay     | Figure 3        |                                                   |        | 28  | ns   |

| t <sub>PHL</sub> | (D+, D- to VP, VM)              | Figure 3        |                                                   |        | 28  | ns   |

USB1T11A

-11A

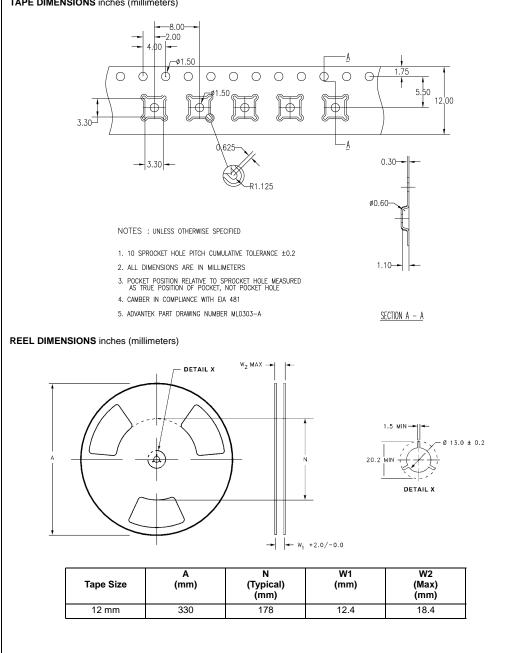

### **Tape and Reel Specification**

| F  | Tape Format for M | LP                 |           |        |            |

|----|-------------------|--------------------|-----------|--------|------------|

| à  | Package           | Таре               | Number    | Cavity | Cover Tape |

| JS | Designator        | Section            | Cavities  | Status | Status     |

|    |                   | Leader (Start End) | 125 (typ) | Empty  | Sealed     |

|    | BQX               | Carrier            | 2500      | Filled | Sealed     |

|    |                   | Trailer (Hub End)  | 75 (typ)  | Empty  | Sealed     |

TAPE DIMENSIONS inches (millimeters)

**USB1T11A Universal Serial Bus Transceiver**

11