1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

SLLS507 - JUNE 2001

- Single Chip With Easy Interface Between UART and Two Serial-Port Connectors of IBM™ PC/AT™ and Compatibles

- Meets or Exceeds the Requirements of TIA/EIA-232-F and ITU Recommendation V.28

- Supports Data Rates up to 120 kbit/s

- Package Options Include Plastic Thin Shrink Small-Outline (DGG) and Shrink Small-Outline (DL) Packages

#### description

The SN752232 consists of dual ports, each containing three drivers and five receivers, which reduce board space and allow easy interconnection of the UART and two serial-port connectors of an IBM<sup>™</sup> PC/AT<sup>™</sup> and compatibles. The bipolar circuits and processing of this "dual GD75232" provide, a rugged, low-cost solution for this function.

The SN752232 complies with the requirements of the TIA/EIA-232-F and ITU V.28 standards. These standards are for data interchange between a host computer and a peripheral at signaling rates up to 20 kbit/s. The device supports data rates up to 120 kbit/s with lower capacitive loads (shorter cables). Interoperability at the higher signaling rates cannot be expected unless the designer has design control of the cable and the interface circuits at both ends. For interoperability at signaling rates up to 120 kbit/s, use of TIA/EIA-423-B (ITU V.10) and TIA/EIA-422-B (ITU V.11) standards is recommended.

The SN752232 is characterized for operation over the temperature range of 0°C to 70°C.

|                   | (TOP VI | EW) |                   |

|-------------------|---------|-----|-------------------|

| V <sub>DD</sub> [ | ι U     | 48  | ] v <sub>cc</sub> |

| RIN1A             | 2       | 40  |                   |

| RIN2A             | 3       | 46  | ROUT2A            |

| RIN3A             | 4       | 45  | ROUT3A            |

| DOUT1A            | 5       | 44  | DIN1A             |

| DOUT2A [          | 6       | 43  | DIN2A             |

| RIN4A [           | 7       | 42  | ROUT4A            |

| DOUT3A [          | 8       | 41  | DIN3A             |

| RIN5A             | 9       | 40  | ROUT5A            |

| V <sub>SS</sub> [ | 10      | 39  | GND               |

| NC [              | 11      | 38  | NC                |

| NC [              | 12      | 37  | NC                |

| V <sub>DD</sub> [ | 13      | 36  | V <sub>CC</sub>   |

| RIN1B             | 14      | 35  | ROUT1B            |

| RIN2B             | 15      | 34  | ROUT2B            |

| RIN3B             | 16      | 33  | ROUT3B            |

| DOUT1B            | 17      | 32  | DIN1B             |

| DOUT2B            | 18      | 31  | DIN2B             |

| RIN4B             | 19      | 30  | ROUT4B            |

| DOUT3B            | 20      | 29  | DIN3B             |

| RIN5B             | 21      | 28  | ROUT5B            |

| v <sub>ss</sub> [ | 22      | 27  | ] GND             |

| NC [              | 23      | 26  | NC                |

| NC [              | 24      | 25  | ] NC              |

DGG OR DL PACKAGE

#### AVAILABLE OPTIONS

|             | PACKAGED DEVICES                        |                                                  |  |  |  |  |

|-------------|-----------------------------------------|--------------------------------------------------|--|--|--|--|

| TA          | PLASTIC SHRINK<br>SMALL OUTLINE<br>(DL) | PLASTIC<br>THIN SHRINK<br>SMALL OUTLINE<br>(DGG) |  |  |  |  |

| 0°C to 70°C | SN752232DL                              | SN752232DGG                                      |  |  |  |  |

The DL package also is available taped and reeled. Add the suffix R to the device type (e.g., SN752232DLR). The DGG package is only available taped and reeled.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

IBM and PC/AT are trademarks of International Business Machines Corporation.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLLS507 - JUNE 2001

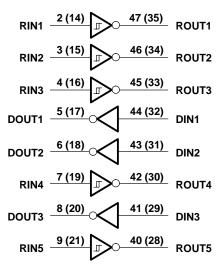

#### logic diagram (positive logic)

NOTE A: Numbers in parentheses are for B section.

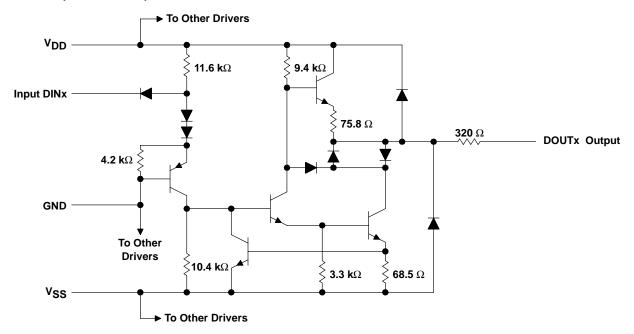

#### schematic (each driver)

NOTE A: Resistor values shown are nominal.

SLLS507 - JUNE 2001

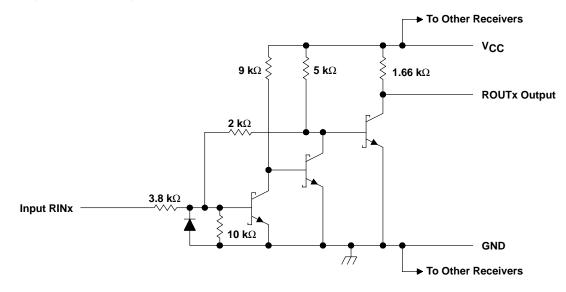

#### schematic (each receiver)

NOTE A: Resistor values shown are nominal.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage (see Note 1): V <sub>CC</sub>                         |

|----------------------------------------------------------------------|

| V <sub>DD</sub> 15 V                                                 |

| V <sub>SS</sub> –15 V                                                |

| Input voltage range, V <sub>I</sub> : Driver                         |

| Receiver                                                             |

| Driver output voltage range, V <sub>O</sub> –15 V to 15 V            |

| Receiver low-level output current, I <sub>OL</sub>                   |

| Package thermal impedance, θ <sub>JA</sub> (see Note 2): DGG package |

| DL package                                                           |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds         |

| Storage temperature range, T <sub>stg</sub> –65°C to 150°C           |

|                                                                      |

<sup>+</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltages are with respect to network GND.

2. The package thermal impedance is calculated in accordance with JESD 51-7.

SLLS507 – JUNE 2001

#### recommended operating conditions

|     |                                        | MIN    | NOM | MAX  | UNIT |

|-----|----------------------------------------|--------|-----|------|------|

| VDD | Supply voltage                         | 7.5    | 9   | 15   | V    |

| VSS | Supply voltage                         | -7.5   | -9  | -15  | V    |

| VCC | Supply voltage                         | 4.5    | 5   | 5.5  | V    |

| VIH | High-level input voltage (driver only) | 1.9    |     |      | V    |

| VIL | Low-level input voltage (driver only)  |        |     | 0.8  | V    |

| 1   | High-level output current              |        |     | -6   | mA   |

| ЮН  | Receiver                               |        |     | -0.5 | IIIA |

| 1   | Driver                                 | Driver |     | 6    | ~ ^  |

| IOL | Low-level output current Receiver      |        |     | 16   | mA   |

| ТĄ  | Operating free-air temperature         | 0      |     | 70   | °C   |

#### supply currents over recommended operating free-air temperature range

|     | PARAMETER                    |                                                  | TEST CONDIT             | IONS                    |                         | MIN | MAX  | UNIT |

|-----|------------------------------|--------------------------------------------------|-------------------------|-------------------------|-------------------------|-----|------|------|

|     |                              |                                                  |                         | V <sub>DD</sub> = 9 V,  | V <sub>SS</sub> = -9 V  |     | 30   |      |

|     |                              | All inputs at 1.9 V,                             | No load                 | V <sub>DD</sub> = 12 V, | $V_{SS} = -12 V$        |     | 38   |      |

| 1   | Supply current from V        |                                                  |                         | V <sub>DD</sub> = 15 V, | V <sub>SS</sub> = -15 V |     | 50   | mA   |

| IDD | Supply current nonin vDD     |                                                  |                         | V <sub>DD</sub> = 9 V,  | $V_{SS} = -9 V$         |     | 9    | IIIA |

|     |                              | All inputs at 0.8 V,                             | No load                 | V <sub>DD</sub> = 12 V, | $V_{SS} = -12 V$        |     | 11   |      |

|     |                              |                                                  |                         | V <sub>DD</sub> = 15 V, | V <sub>SS</sub> = -15 V |     | 18   |      |

|     |                              |                                                  |                         | V <sub>DD</sub> = 9 V,  | V <sub>SS</sub> = -9 V  |     | -30  |      |

|     |                              | All inputs at 1.9 V,                             | No load                 | V <sub>DD</sub> = 12 V, | $V_{SS} = -12 V$        |     | -38  |      |

|     | Cumply ourreast from V/a a   |                                                  |                         | V <sub>DD</sub> = 15 V, | V <sub>SS</sub> = -15 V |     | -50  | ~ ^  |

| ISS | Supply current from VSS      |                                                  |                         | V <sub>DD</sub> = 9 V,  | $V_{SS} = -9 V$         |     | -6.4 | mA   |

|     |                              | All inputs at 0.8 V, No load $V_{DD} = 12 V$ , V | V <sub>SS</sub> = -12 V |                         | -6.4                    |     |      |      |

|     |                              |                                                  |                         | V <sub>DD</sub> = 15 V, | V <sub>SS</sub> = -15 V |     | -6.4 |      |

| ICC | Supply current from $V_{CC}$ | V <sub>CC</sub> = 5 V,                           | All inputs at 5 V,      | No load                 |                         |     | 60   | mA   |

#### **DRIVER SECTION**

## electrical characteristics over recommended operating free-air temperature range, $V_{DD}$ = 9 V, $V_{SS}$ = -9 V, $V_{CC}$ = 5 V (unless otherwise noted)

|                 | PARAMETER                                            |                            | TEST CONDITIC        | NS                             | MIN  | TYP  | MAX   | UNIT |

|-----------------|------------------------------------------------------|----------------------------|----------------------|--------------------------------|------|------|-------|------|

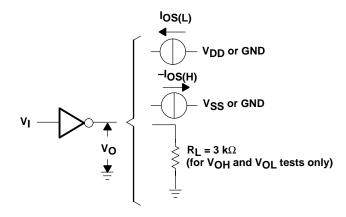

| VOH             | High-level output voltage                            | V <sub>IL</sub> = 0.8 V,   | $R_L = 3 k\Omega$ ,  | See Figure 1                   | 6    | 7.5  |       | V    |

| VOL             | Low-level output voltage<br>(see Note 3)             | V <sub>IH</sub> = 1.9 V,   | $R_L = 3 k\Omega$ ,  | See Figure 1                   |      | -7.5 | -6    | V    |

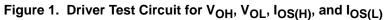

| lн              | High-level input current                             | V <sub>I</sub> = 5 V,      | See Figure 2         |                                |      |      | 10    | μA   |

| ۱ <sub>۱L</sub> | Low-level input current                              | $V_{I} = 0,$               | See Figure 2         |                                |      |      | -1.6  | mA   |

| IOS(H)          | High-level short-circuit output current (see Note 4) | V <sub>IL</sub> = 0.8 V,   | V <sub>O</sub> = 0,  | See Figure 1                   | -4.5 | -12  | -19.5 | mA   |

| IOS(L)          | Low-level short-circuit output current               | V <sub>IH</sub> = 2 V,     | $V_{O} = 0,$         | See Figure 1                   | 4.5  | 12   | 19.5  | mA   |

| rO              | Output resistance (see Note 5)                       | $V_{CC} = V_{DD} = V_{CC}$ | / <sub>SS</sub> = 0, | $V_{O} = -2 V \text{ to } 2 V$ | 300  |      |       | Ω    |

NOTES: 3. The algebraic convention, where the more positive (less negative) limit is designated as maximum, is used in this data sheet for logic levels only (e.g., if –10 V is maximum, the typical value is a more negative voltage).

4. Output short-circuit conditions must maintain the total power dissipation below absolute maximum ratings.

5. Test conditions are those specified by TIA/EIA-232-F and as listed above.

SLLS507 - JUNE 2001

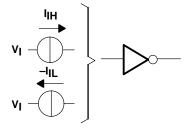

## switching characteristics, $V_{CC}$ = 5 V, $V_{DD}$ = 12 V, $V_{SS}$ = -12 V, $T_A$ = 25°C (see Figure 3)

|                  | PARAMETER                                            | TEST                                                           | CONDITIONS                |            | MIN | TYP | MAX                             | UNIT |

|------------------|------------------------------------------------------|----------------------------------------------------------------|---------------------------|------------|-----|-----|---------------------------------|------|

| tPLH             | Propagation delay time,<br>low- to high-level output | $R_L$ = 3 kΩ to 7 kΩ,                                          | C <sub>L</sub> = 15 pF    |            |     | 315 | 500                             | ns   |

| <sup>t</sup> PHL | Propagation delay time,<br>high- to low-level output | $R_L = 3 k\Omega$ to 7 k $\Omega$ ,                            | C <sub>L</sub> = 15 pF    |            |     | 75  | 175                             | ns   |

| +                | Transition time, low, to high lovel output           | $\mathbf{P}_{\mathbf{k}} = 2 \mathbf{k} 0$ to $7 \mathbf{k} 0$ | C <sub>L</sub> = 15 pF    |            |     | 60  | 100                             | ns   |

| <sup>t</sup> TLH | Transition time, low- to high-level output           | $R_{L} = 3 k\Omega \text{ to } 7 k\Omega$                      | C <sub>L</sub> = 2500 pF, | See Note 6 |     | 1.7 | 2.5                             | μs   |

|                  | Transition time, high- to low-level output           | $P_{\rm L} = 2 k\Omega to 7 k\Omega$                           | CL = 15 pF                |            |     | 40  | 75                              | ns   |

| <sup>t</sup> THL | Transition time, high- to low-level output           | $R_{L} = 3 R_{22} 10 7 R_{22}$                                 | C <sub>L</sub> = 2500 pF, | See Note 6 |     | 1.5 | 5 175<br>0 100<br>7 2.5<br>0 75 | μs   |

NOTE 6: Measured between ±3-V and ±3-V points of the output waveform (TIA/EIA-232-F conditions), all unused inputs are tied either high or low.

#### **RECEIVER SECTION**

#### electrical characteristics over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                                                       | TEST C                               | ONDITIONS                | MIN   | TYP <sup>†</sup> | MAX  | UNIT |

|------------------|-----------------------------------------------------------------|--------------------------------------|--------------------------|-------|------------------|------|------|

| \/. <b>_</b>     | Desitive asing input threshold voltage                          | $T_A = 25^{\circ}C$                  | See Figure 5             | 1.75  | 1.9              | 2.3  | V    |

| VIT+             | Positive-going input threshold voltage                          | $T_A = 0^{\circ}C$ to 70 $^{\circ}C$ | See Figure 5             | 1.55  |                  | 2.3  | v    |

| $V_{IT-}$        | Negative-going input threshold voltage                          |                                      |                          | 0.75  | 0.97             | 1.25 | V    |

| V <sub>hys</sub> | Input hysteresis voltage (V <sub>IT+</sub> – V <sub>IT</sub> –) |                                      |                          | 0.5   |                  |      | V    |

| Varia            |                                                                 | 1au 0.5 mA                           | V <sub>IH</sub> = 0.75 V | 2.6   | 4                | 5    | V    |

| VOH              | High-level output voltage                                       | I <sub>OH</sub> = -0.5 mA            | Inputs open              | 2.6   |                  |      | V    |

| VOL              | Low-level input voltage                                         | I <sub>OL</sub> = 10 mA,             | V <sub>I</sub> = 3 V     |       | 0.2              | 0.45 | V    |

|                  | High-level input current                                        | V <sub>I</sub> = 25 V,               | See Figure 5             | 3.6   |                  | 8.8  | mA   |

| ΙН               | High-level liput current                                        | V <sub>I</sub> = 3 V,                | See Figure 5             | 0.43  |                  |      | ША   |

| 1                | Low-level output current                                        | V <sub>I</sub> = -25 V,              | See Figure 5             | -3.6  |                  | -8.8 | mA   |

| ΊĽ               |                                                                 | $V_{I} = -3 V,$                      | See Figure 5             | -0.43 |                  |      | ША   |

| los              | Short-circuit output current                                    | See Figure 4                         |                          |       | -3.4             | -12  | mA   |

<sup>†</sup> All typical values are at  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5$  V,  $V_{DD} = 9$  V, and  $V_{SS} = -9$  V.

## switching characteristics, V<sub>CC</sub> = 5 V, V<sub>DD</sub> = 12 V, V<sub>SS</sub> = –12 V, T<sub>A</sub> = 25°C (see Figure 6)

|                  | PARAMETER                                         | TEST C                  | ONDITIONS                        | MIN                      | TYP                      | MAX                      | UNIT       |  |     |     |    |

|------------------|---------------------------------------------------|-------------------------|----------------------------------|--------------------------|--------------------------|--------------------------|------------|--|-----|-----|----|

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output |                         |                                  |                          | 107                      | 250                      | ns         |  |     |     |    |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output | С <sub>L</sub> = 50 рF, | $R_1 = 5 k\Omega$                |                          | 42                       | 150                      | ns         |  |     |     |    |

| <sup>t</sup> TLH | Transition time, low- to high-level output        |                         | CL = 50 pr,                      | $C_{L} = 50 \text{ pr},$ | $C_{L} = 50 \text{ pr},$ | $C_{L} = 50 \text{ pr},$ | KL = 0 K22 |  | 175 | 350 | ns |

| <sup>t</sup> THL | Transition time, high- to low-level output        |                         |                                  |                          | 16                       | 60                       | ns         |  |     |     |    |

| <sup>t</sup> PLH | Propagation delay time, low- to high-level output |                         |                                  |                          | 100                      | 160                      | ns         |  |     |     |    |

| <sup>t</sup> PHL | Propagation delay time, high- to low-level output | $C_{1} = 15 \text{ pc}$ | Rլ = 1.5 kΩ                      |                          | 60                       | 100                      | ns         |  |     |     |    |

| <sup>t</sup> TLH | Transition time, low- to high-level output        | C <sub>L</sub> = 15 pF, | κ <u>Γ</u> = 1.3 κ <sub>22</sub> |                          | 90                       | 175                      | ns         |  |     |     |    |

| <sup>t</sup> THL | Transition time, high- to low-level output        |                         |                                  |                          | 15                       | 50                       | ns         |  |     |     |    |

SLLS507 - JUNE 2001

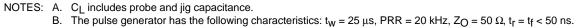

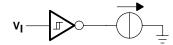

#### PARAMETER MEASUREMENT INFORMATION

Figure 2. Driver Test Circuit for IIH and IIL

Figure 3. Driver Test Circuit and Voltage Waveforms

SLLS507 - JUNE 2001

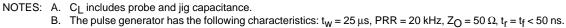

#### PARAMETER MEASUREMENT INFORMATION

Figure 4. Receiver Test Circuit for IOS

Figure 5. Receiver Test Circuit for  $V_{IT}$ ,  $V_{OH}$ , and  $V_{OL}$

#### Figure 6. Receiver Propagation and Transition Times

SLLS507 - JUNE 2001

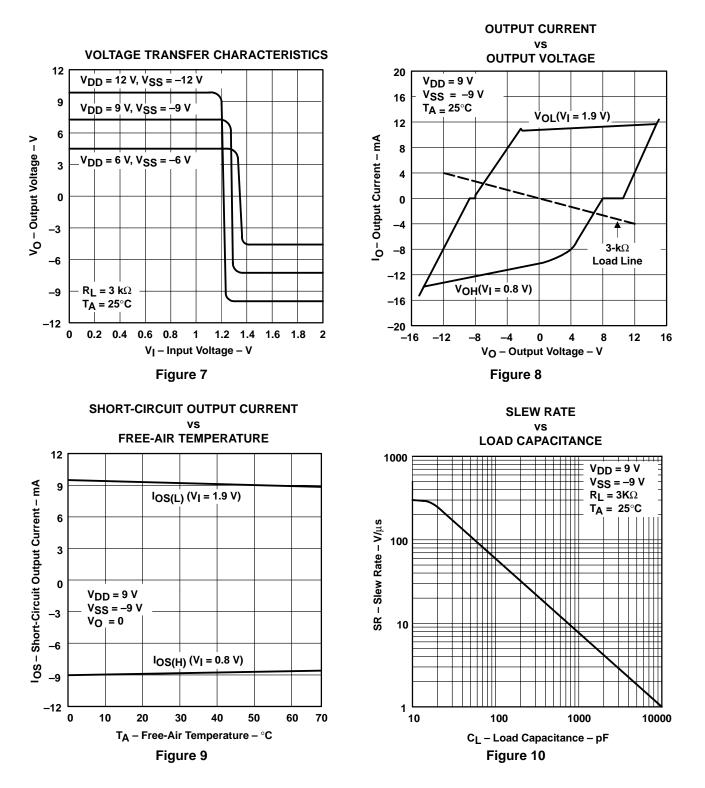

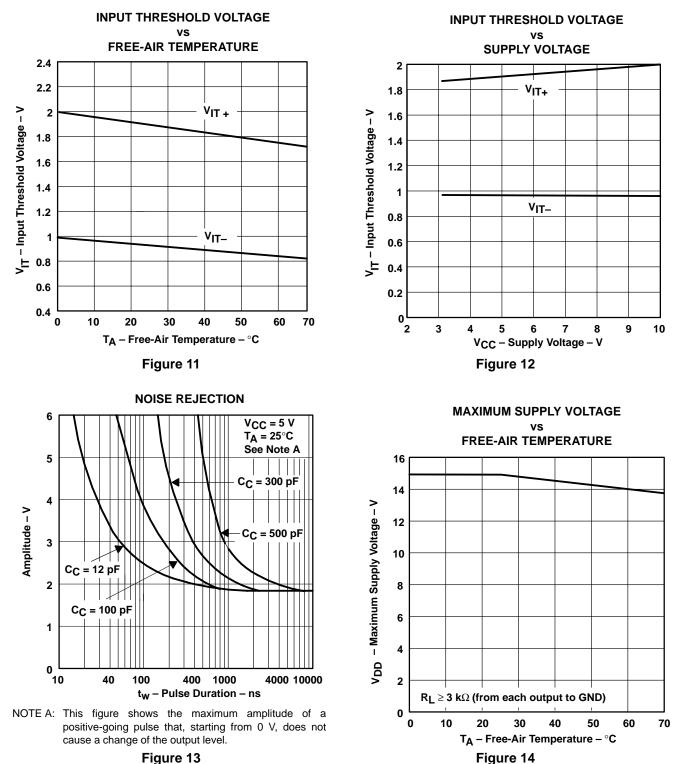

## TYPICAL CHARACTERISTICS

#### **DRIVER SECTION**

SLLS507 - JUNE 2001

#### **TYPICAL CHARACTERISTICS**

Figure 13

SLLS507 – JUNE 2001

#### **APPLICATION INFORMATION**

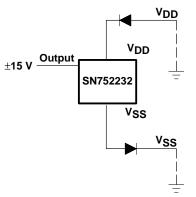

Diodes placed in series with the  $V_{DD}$  and  $V_{SS}$  leads protect the SN752232 in the fault condition in which the device outputs are shorted to ±15 V, and the power supplies are at low and provide low-impedance paths to ground (see Figure 15).

Figure 15. Power-Supply Protection to Meet Power-Off Fault Conditions of TIA/EIA-232-F

NOTE A: Numbers in parentheses are for B section.

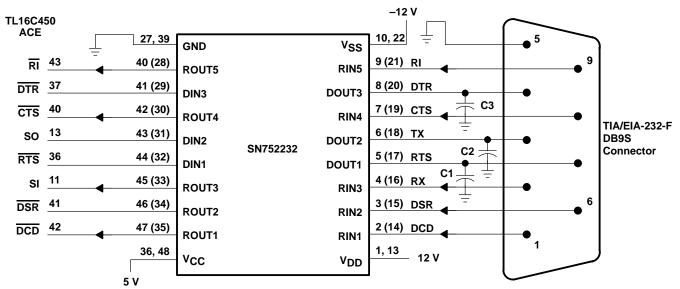

Figure 16. Typical Connection Per Port

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, license, warranty or endorsement thereof.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Resale of TI's products or services with <u>statements different from or beyond the parameters</u> stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service, is an unfair and deceptive business practice, and TI is not responsible nor liable for any such use.

Also see: Standard Terms and Conditions of Sale for Semiconductor Products. www.ti.com/sc/docs/stdterms.htm

Mailing Address:

Texas Instruments Post Office Box 655303 Dallas, Texas 75265

Copyright © 2001, Texas Instruments Incorporated