1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

### **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

DATACOM PRODUCTS

# *VSC7145*

### VSC7145 - Dual Speed 10-bit Serializer/Deserializer

### FEATURES:

- Dual Speed Operation:

- Fibre Channel: 1.06/2.12Gb/s

- Gigabit Ethernet: 1.25Gb/s

- InfiniBand™: 2.5Gb/s

- ▶ 10-bit, SSTL\_2 or SSTL\_3 Interface

- ▶ HSPI Interface Compliant

- ▶ ASIC-Friendly™ Timing to the Transmitter

- Separate Transmitter/Receiver Rate Controls support Auto Speed Negotiation

- ▶ No Passives needed on High Speed Signals

- > On-chip, 100 Ohm Termination

- ▶ Write Pre-Emphasis in Transmitter

- ▶ Cable Equalization in Receiver

- Analog/Digital Signal Detection

- ▶ Flexible Reference Clock

- ▶ Single 3.3V Supply, 800mW

- ▶ 64-pin, 14 mm PQFP Package

- ▶ Pin Compatible to Agilent HDMP-263x

### SPECIFICATIONS:

- Data Rate: 1.0 2.5 Gb/s

- ▶ REFCLK: 52.5 to 126 MHz

- ▶ Frequency Offset: +/-200 ppm

- ▶ Fast Locking: <300 data edges

- ▶ Transmitter Output: 1.0V p-p Minimum

- ▶ Receiver Input: 200mV p-p Minimum

- > 3.3V +/- 5% Supply

- ▶ 0° 70°C Ambient Operation

### APPLICATIONS:

- Fibre Channel

-Host Adapters

-Hubs/Switches

-RAID systems

- Gigabit Ethernet

-NICs

-Switches

-Proprietary Uplinks

- InfiniBand

Host Channel Adapters

Target Channel Adapters

Switches

- Proprietary Serial Links

#### **PRODUCT OPTIONS:**

| Part Number  | Low Speed I/O | Speed (Gb/s)                                                  | HS Termination | Compatibility     |

|--------------|---------------|---------------------------------------------------------------|----------------|-------------------|

| VSC7145RU-30 | SSTL_2        | 1.05 - 1.26<br>(Half Speed)<br>or 2.10 - 2.52<br>(Full Speed) | 100 Ohms       | Agilent HDMP-2630 |

| VSC7145RU-31 | SSTL_3        |                                                               |                | Agilent HDMP-2631 |

| VSC7145RU-34 | SSTL_2        |                                                               |                | Agilent HDMP-2634 |

InfiniBand<sup>™/SM</sup> is a trademark and service mark of the InfiniBand Trade Association ASIC-Friendly<sup>™</sup> is a trademark of Vitesse Semiconductor Corporation

VITESSE

## *VSC7145*

### VSC7145 - Dual Speed 10-bit Serializer/Deserializer

### GENERAL DESCRIPTION:

The VSC7145 is a dual-speed Fibre Channel, Gigabit Ethernet and InfiniBand Serializer/ Deserializer (SerDes) optimized for performance and power in an industrystandard pinout. It accepts 10-bits of SSTL, 8B/10B encoded transmit data, latches it

synchronously to the Transmit Byte Clock (TBC) and serializes it onto the S0 differential output at a baud rate which is 10, 20 or 40 times the REFCLK frequency. The VSC7145 samples serial receive data on the SI input, recovers the clock and data, deserializes it onto a 10-bit SSTL bus and outputs two recovered clocks at 1/10th or 1/20th of the baud rate. Both disparities of the K28.5 characters are detected and used for aligning the serial data to the parallel output bus. Independent speed selectors control the transmitter and receiver separately to support industry-standard automatic speed negotiation protocols. A combined analog/digital signal detect circuit indicates the presence of valid signal levels on the SI input. The VSC7145 contains on-chip PLL circuitry for synthesis of the bit rate transmit clock, and extraction of the clock from the received serial stream. The parallel bus of the VSC7145 is compliant with the High Speed Parallel Interface (HSPI) standard developed by the T11.2 Fibre Channel Committee.

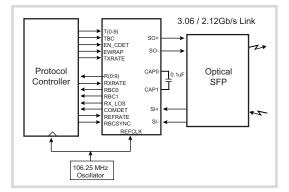

### DUAL SPEED AUTO NEGOTIATION FIBRE CHANNEL APPLICATION:

### Your Partner for Success.

For more information on Vitesse Products visit the Vitesse web site at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or sales@vitesse.com

741 Calle Plano Camarillo, CA 93012 Tel: 805.388.3700 Fax: 805.388.7565 www.vitesse.com

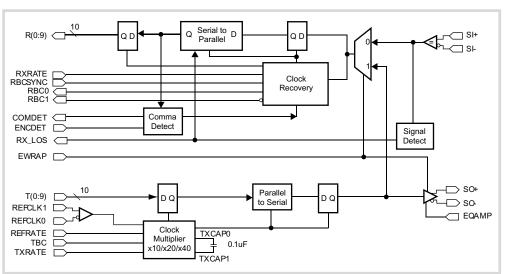

### VSC7145 BLOCK DIAGRAM: