# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# EQ50F100 6.25Gbps Backplane Equalizer Evaluation Kit User Manual

Part Number: EQ50EVK

Oct 2004

Communication Interface Division

National Semiconductor Corporation

Document Revision 1.0

# **Table of Contents**

| Application Evaluation Board | 4 |

|------------------------------|---|

| Evaluation Board             |   |

| Overview                     |   |

| Troubleshooting              | 6 |

| Other Resources              |   |

#### Introduction

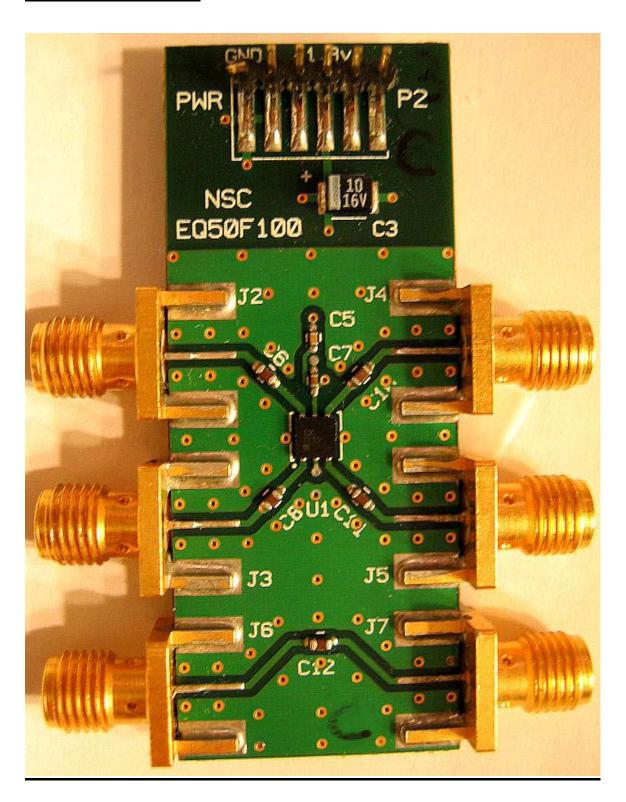

The National Semiconductor EQ50F100 evaluation kit (EQ50EVK) demonstrates the performance of the 6.25Gbps Backplane Equalizer.

The printed circuit board (PCB) is optimized for giga-bit operation. The CML differential traces impedance is 100 Ohms differential and it is equipped with AC-coupling capacitors on both input and output trace. All CML traces have matched trace lengths for low skew.

This evaluation kit can be used to test and verify the performance of the EQ50F100 equalizer in backplane and cable application.

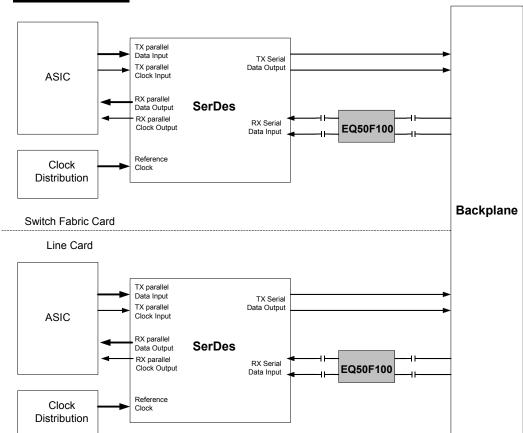

## **Application**

The diagram above illustrates the use of the EQ50EVK along with a Backplane SerDes, in a giga-bit backplane transmission application.

Please refer to datasheet for information.

# **Evaluation Board**

#### <u>Setup</u>

The setup of EQ50EVK evaluation board is very straightforward. To start using the evaluation kit, follow these steps:

- 1) Connect signal source positive output to EQ50EVK positive input (J2).

- 2) Connect signal source negative output to EQ50EVK negative input (J3).

- 3) Connect EQ50EVK positive output (J4) to the positive input of SerDes/ASIC/FPGA/Test Equipment.

- 4) Connect EQ50EVK positive output (J5) to negative input of SerDes/ASIC/FPGA/Test Equipment.

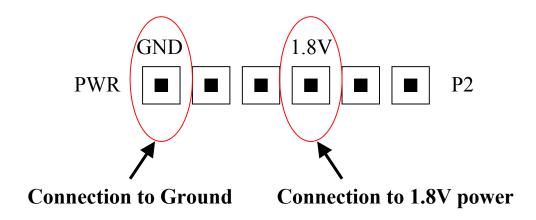

- 5) Apply power (+1.8V) and ground to EQ50EVK PWR section (P2). See Figure 1 for detail.

Figure 1

#### **Overview**

The EQ50EVK has total of 4 layers: 1) Signal layer, 2) GND layer, 3) +1.8V power layer and 4) bottom layer. The total board thickness is 62mil. The high-speed CML signal traces are 20mil wide with impedance of 100-Ohm differential.

The CML input and output of the EQ50F100 is access through SMA connector (J2 – J5). Power and ground are supplied through 2mm Header-pin connector P2. See Figure 1 for detail.

Tantalum 10uF capacitors (C3) placed near the power connection provide bulk energy storage. In addition to excellent bypassing provided by the closely sandwiched power and ground planes, a network of 10nF (C5) and 100pF (C7) bypass capacitors is placed between Vcc and ground to provide additional bypassing near the device.

### **Troubleshooting**

If the demo boards are not performing properly, use the following as a guide for quick solutions to common problems. If the problem persists, contact the hotline number listed under Additional Information section of this document.

#### Check the following:

- 1. Power and Ground are connected to the power connections of the board.

- 2. Supply voltage (+1.8V) and current (It's around 40mA).

- 3. Input signal to input SMA connectors.

- 4. Connection and signal to the input SMA connectors (J2, J3) on the board.

- 5. Connection from the output SMA connectors (J4, J5) on the board.

- 6. Soldering on the input and output SMA connectors.

## **Other Resources**

For more information on High Speed Backplane Solution, refer to the National's LVDS website at:

LVDS.national.com

© National Semiconductor, 2003. National Semiconductor and the "N" logo are registered trademarks of National Semiconductor Corporation. All other brand or product names are trademarks of their respective owners.

All rights reserved.