## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# 16-Lane 4-Port Gen2 PCI Express® Switch

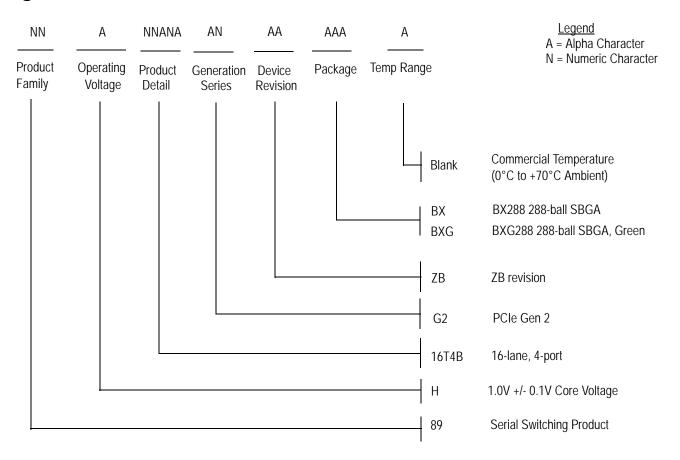

## 89HPES16T4BG2 Data Sheet

## **Device Overview**

The 89HPES16T4BG2 is a member of IDT's PRECISE™ family of PCI Express® switching solutions. The PES16T4BG2 is a 16-lane, 4-port Gen2 peripheral chip that performs PCI Express Base switching with a feature set optimized for high performance applications such as servers, storage, and communications/networking. It provides connectivity and switching functions between a PCI Express upstream port and up to three downstream ports and supports switching between downstream ports.

#### **Features**

- High Performance PCI Express Switch

- Sixteen 5 Gbps Gen2 PCI Express lanes

- Four switch ports

- · One x4 upstream port

- Three x4 downstream ports

- Low latency cut-through switch architecture

- Support for Max Payload Size up to 2048 bytes

- One virtual channel

- Eight traffic classes

- PCI Express Base Specification Revision 2.0 compliant

- Implements the following optional PCI Express features

- · Advanced Error Reporting (AER) on all ports

- End-to-End CRC (ECRC)

- Access Control Services (ACS)

- · Power Budgeting Enhanced Capability

- · Device Serial Number Enhanced Capability

- · Sub-System ID and Sub-System Vendor ID Capability

- VGA and ISA enable

- L0s and L1 ASPM

- ARI ECN

## Flexible Architecture with Numerous Configuration Options

- Automatic per port link width negotiation to x4, x2 or x1

- Automatic lane reversal on all ports

- Automatic polarity inversion

- Ability to load device configuration from serial EEPROM

#### On-Die Temperature Sensor

- Range of 0 to 127.5 degrees Celsius

- Three programmable temperature thresholds with over and under temperature threshold alarms

- Automatic recording of maximum high or minimum low temperature

#### Legacy Support

- PCI compatible INTx emulation

- Bus locking

#### Highly Integrated Solution

Incorporates on-chip internal memory for packet buffering and queueing

## **Block Diagram**

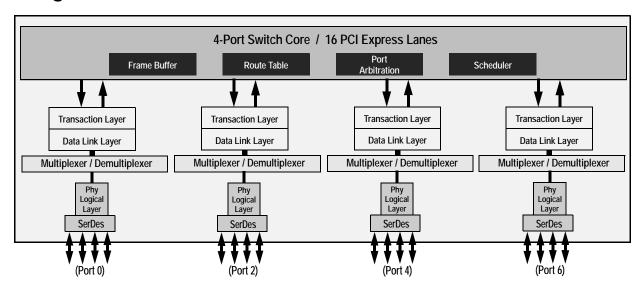

Figure 1 Internal Block Diagram

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

- Integrates sixteen 5 Gbps embedded SerDes with 8b/10b encoder/decoder (no separate transceivers needed)

- · Receive equalization (RxEQ)

#### Reliability, Availability, and Serviceability (RAS) Features

- Internal end-to-end parity protection on all TLPs ensures data integrity even in systems that do not implement end-to-end CRC (ECRC)

- Supports ECRC and Advanced Error Reporting

- Supports PCI Express Native Hot-Plug, Hot-Swap capable I/O

- Compatible with Hot-Plug I/O expanders used on PC motherboards

- Supports Hot-Swap

#### Power Management

- Utilizes advanced low-power design techniques to achieve low typical power consumption

- Support PCI Express Power Management Interface specification (PCI-PM 1.2)

- Supports PCI Express Active State Power Management (ASPM) link state

- Supports PCI Express Power Budgeting Capability

- Supports the optional PCI Express SerDes Transmit Low-Swing Voltage Mode

- Unused SerDes are disabled and can be powered-off

#### Testability and Debug Features

- Supports IEEE 1149.1 JTAG and IEEE 1149.6 AC JTAG

- Built in Pseudo-Random Bit Stream (PRBS) generator

- Numerous SerDes test modes

- Ability to read and write any internal register via the SMBus

- Ability to bypass link training and force any link into any mode

- Provides statistics and performance counters

#### Sixteen General Purpose Input/Output Pins

- Each pin may be individually configured as an input or output

- Each pin may be individually configured as an interrupt input

- Some pins have selectable alternate functions

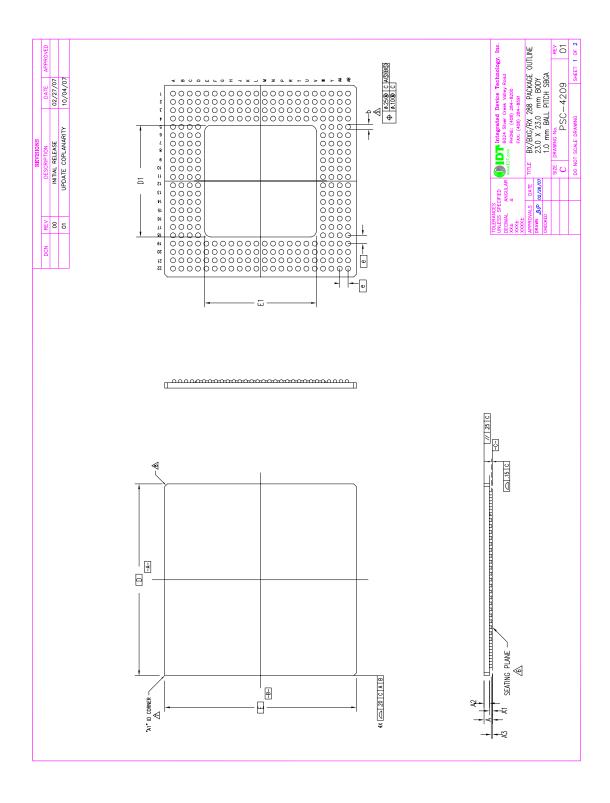

- Packaged in a 23mm x 23mm, 288-ball BGA with 1mm ball spacing

#### **Product Description**

Utilizing standard PCI Express interconnect, the PES16T4BG2 provides the most efficient fan-out solution for applications requiring high throughput, low latency, and simple board layout with a minimum number of board layers. It provides 16 GBps (128 Gbps) of aggregated, full-duplex switching capacity through 16 integrated serial lanes, using proven and robust IDT technology. Each lane provides 5 Gbps of bandwidth in both directions and is fully compliant with PCI Express Base Specification, Revision 2.0.

The PES16T4BG2 is based on a flexible and efficient layered architecture. The PCI Express layer consists of SerDes, Physical, Data Link and Transaction layers in compliance with PCI Express Base specification Revision 2.0. The PES16T4BG2 can operate either as a store and forward or cut-through switch and is designed to switch memory and I/O

transactions. It supports eight Traffic Classes (TCs) and one Virtual Channel (VC) with sophisticated resource management to enable efficient switching and I/O connectivity for servers, storage, and embedded processors with limited connectivity.

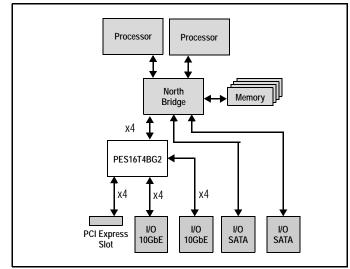

Figure 2 I/O Expansion Application

#### **SMBus Interface**

The PES16T4BG2 contains two SMBus interfaces. The slave interface provides full access to the configuration registers in the PES16T4BG2, allowing every configuration register in the device to be read or written by an external agent. The master interface allows the default configuration register values of the PES16T4BG2 to be overridden following a reset with values programmed in an external serial EEPROM. The master interface is also used by an external Hot-Plug I/O expander.

Six pins make up each of the two SMBus interfaces. These pins consist of an SMBus clock pin, an SMBus data pin, and 4 SMBus address pins. In the slave interface, these address pins allow the SMBus address to which the device responds to be configured. In the master interface, these address pins allow the SMBus address of the serial configuration EEPROM from which data is loaded to be configured. The SMBus address is set up on negation of PERSTN by sampling the corresponding address pins. When the pins are sampled, the resulting address is assigned as shown in Table 1.

| Bit | Slave<br>SMBus<br>Address | Master<br>SMBus<br>Address |

|-----|---------------------------|----------------------------|

| 1   | SSMBADDR[1]               | MSMBADDR[1]                |

| 2   | SSMBADDR[2]               | MSMBADDR[2]                |

| 3   | SSMBADDR[3]               | MSMBADDR[3]                |

| 4   | 0                         | MSMBADDR[4]                |

Table 1 Master and Slave SMBus Address Assignment

| Bit | Slave<br>SMBus<br>Address | Master<br>SMBus<br>Address |

|-----|---------------------------|----------------------------|

| 5   | SSMBADDR[5]               | 1                          |

| 6   | 1                         | 0                          |

| 7   | 1                         | 1                          |

Table 1 Master and Slave SMBus Address Assignment

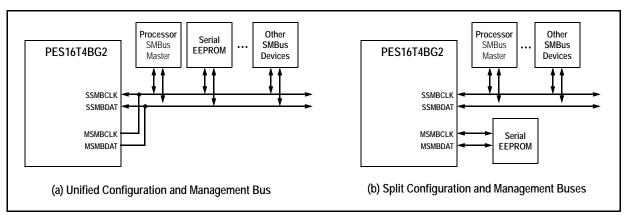

As shown in Figure 3, the master and slave SMBuses may be used in a unified or split configuration. In the unified configuration, shown in Figure 3(a), the master and slave SMBuses are tied together and the PES16T4BG2 acts both as a SMBus master as well as a SMBus slave on this bus. This requires that the SMBus master or processor that has access to PES16T4BG2 registers supports SMBus arbitration. In some systems, this SMBus master interface may be implemented using general purpose I/O pins on a processor or micro controller, and may not support SMBus arbitration. To support these systems, the PES16T4BG2 may be configured to operate in a split configuration as shown in Figure 3(b).

In the split configuration, the master and slave SMBuses operate as two independent buses and thus multi-master arbitration is never required. The PES16T4BG2 supports reading and writing of the serial EEPROM on the master SMBus via the slave SMBus, allowing in system programming of the serial EEPROM.

Figure 3 SMBus Interface Configuration Examples

#### **Hot-Plug Interface**

The PES16T4BG2 supports PCI Express Hot-Plug on each downstream port. To reduce the number of pins required on the device, the PES16T4BG2 utilizes an external I/O expander, such as that used on PC motherboards, connected to the SMBus master interface. Following reset and configuration, whenever the state of a Hot-Plug output needs to be modified, the PES16T4BG2 generates an SMBus transaction to the I/O expander with the new value of all of the outputs. Whenever a Hot-Plug input changes, the I/O expander generates an interrupt which is received on the IOEXPINTN input pin (alternate function of GPIO) of the PES16T4BG2. In response to an I/O expander interrupt, the PES16T4BG2 generates an SMBus transaction to read the state of all of the Hot-Plug inputs from the I/O expander.

#### **General Purpose Input/Output**

The PES16T4BG2 provides 16 General Purpose Input/Output (GPIO) pins that may be used by the system designer as bit I/O ports. Each GPIO pin may be configured independently as an input or output through software control. Some GPIO pins are shared with other on-chip functions. These alternate functions may be enabled via software, SMBus slave interface, or serial configuration EEPROM.

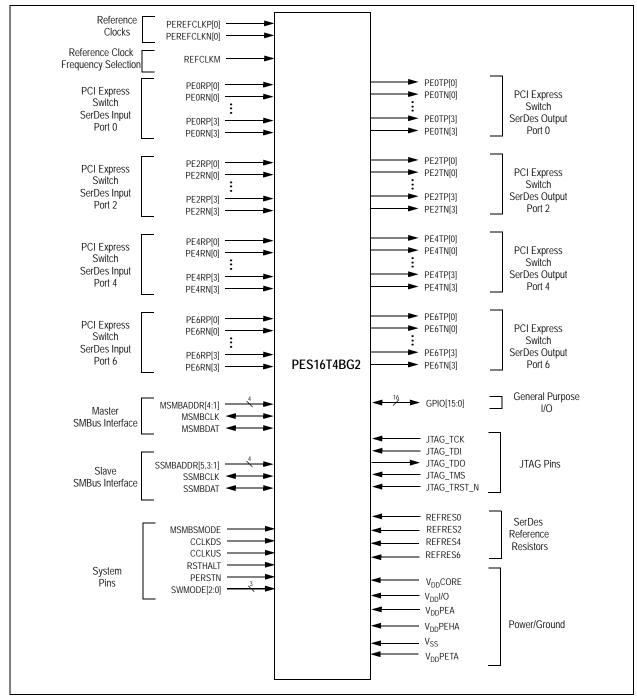

## **Pin Description**

The following tables list the functions of the pins provided on the PES16T4BG2. Some of the functions listed may be multiplexed onto the same pin. The active polarity of a signal is defined using a suffix. Signals ending with an "N" are defined as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses, and select lines) will be interpreted as being active, or asserted, when at a logic one (high) level.

Note: In the PES16T4BG2, the three downstream ports are labeled port 2, port 4, and port 6.

| Signal                       | Туре | Name/Description                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PE0RP[3:0]<br>PE0RN[3:0]     | I    | PCI Express Port 0 Serial Data Receive. Differential PCI Express receive pairs for port 0. Port 0 is the upstream port.                                                                                                                                                                         |  |  |  |

| PE0TP[3:0]<br>PE0TN[3:0]     | 0    | PCI Express Port 0 Serial Data Transmit. Differential PCI Express transmit pairs for port 0. Port 0 is the upstream port.                                                                                                                                                                       |  |  |  |

| PE2RP[3:0]<br>PE2RN[3:0]     | I    | PCI Express Port 2 Serial Data Receive. Differential PCI Express receive pairs for port 2.                                                                                                                                                                                                      |  |  |  |

| PE2TP[3:0]<br>PE2TN[3:0]     | 0    | PCI Express Port 2 Serial Data Transmit. Differential PCI Express transmit pairs for port 2.                                                                                                                                                                                                    |  |  |  |

| PE4RP[3:0]<br>PE4RN[3:0]     | I    | PCI Express Port 4 Serial Data Receive. Differential PCI Express receive pairs for port 4.                                                                                                                                                                                                      |  |  |  |

| PE4TP[3:0]<br>PE4TN[3:0]     | 0    | PCI Express Port 4 Serial Data Transmit. Differential PCI Express transmit pairs for port 4.                                                                                                                                                                                                    |  |  |  |

| PE6RP[3:0]<br>PE6RN[3:0]     | I    | PCI Express Port 6 Serial Data Receive. Differential PCI Express receive pairs for port 6.                                                                                                                                                                                                      |  |  |  |

| PE6TP[3:0]<br>PE6TN[3:0]     | 0    | PCI Express Port 6 Serial Data Transmit. Differential PCI Express transmit pairs for port 6.                                                                                                                                                                                                    |  |  |  |

| PEREFCLKP[0]<br>PEREFCLKN[0] | I    | PCI Express Reference Clock. Differential reference clock pair input. This clock is used as the reference clock by on-chip PLLs to generate the clocks required for the system logic and on-chip SerDes. The frequency of the differential reference clock is determined by the REFCLKM signal. |  |  |  |

| REFCLKM                      | I    | PCI Express Reference Clock Mode Select. This signal selects the frequency of the reference clock input.  0x0 - 100 MHz  0x1 - 125 MHz  This pin should be static and not change following the negation of PERSTN.                                                                              |  |  |  |

Table 2 PCI Express Interface Pins

| Signal        | Туре | Name/Description                                                                                                                         |  |  |  |  |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MSMBADDR[4:1] | I    | <b>Master SMBus Address.</b> These pins determine the SMBus address of the serial EEPROM from which configuration information is loaded. |  |  |  |  |

| MSMBCLK       | I/O  | <b>Master SMBus Clock</b> . This bidirectional signal is used to synchronize transfers on the master SMBus.                              |  |  |  |  |

| MSMBDAT       | I/O  | <b>Master SMBus Data</b> . This bidirectional signal is used for data on the master SMBus.                                               |  |  |  |  |

Table 3 SMBus Interface Pins (Part 1 of 2)

| Signal          | Туре | Name/Description                                                                                          |  |  |  |  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|

| SSMBADDR[5,3:1] | l    | Slave SMBus Address. These pins determine the SMBus address to which the slave SMBus interface responds.  |  |  |  |  |

| SSMBCLK         | I/O  | <b>Slave SMBus Clock</b> . This bidirectional signal is used to synchronize transfers on the slave SMBus. |  |  |  |  |

| SSMBDAT         | I/O  | Slave SMBus Data. This bidirectional signal is used for data on the slave SMBus.                          |  |  |  |  |

Table 3 SMBus Interface Pins (Part 2 of 2)

| Signal   | Туре | Name/Description                                                                                                                                                                                                                                                          |  |  |  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPIO[0]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: P2RSTN Alternate function pin type: Output Alternate function: Reset output for downstream port 2.                                                             |  |  |  |

| GPIO[1]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: P4RSTN Alternate function pin type: Output Alternate function: Reset output for downstream port 4.                                                             |  |  |  |

| GPIO[2]  | I/O  | Alternate function: Reset output for downstream port 4.  General Purpose I/O.  This pin can be configured as a general purpose I/O pin.  Alternate function pin name: IOEXPINTNO  Alternate function pin type: Input  Alternate function: I/O expander interrupt 0 input. |  |  |  |

| GPIO[3]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

| GPIO[4]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: IOEXPINTN2 Alternate function pin type: Input Alternate function: I/O Expander interrupt 2 input                                                               |  |  |  |

| GPIO[5]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

| GPIO[6]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

| GPIO[7]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: GPEN Alternate function pin type: Output Alternate function: General Purpose Event (GPE) output                                                                |  |  |  |

| GPIO[8]  | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

| GPIO[9]  | 1/0  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

| GPIO[10] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                                                                             |  |  |  |

Table 4 General Purpose I/O Pins (Part 1 of 2)

| Signal   | Туре | Name/Description                                                                                                                                                                                              |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[11] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin. Alternate function pin name: P6RSTN Alternate function pin type: Output Alternate function: Reset output for downstream port 6. |

| GPIO[12] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                 |

| GPIO[13] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                 |

| GPIO[14] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                 |

| GPIO[15] | I/O  | General Purpose I/O. This pin can be configured as a general purpose I/O pin.                                                                                                                                 |

Table 4 General Purpose I/O Pins (Part 2 of 2)

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CCLKDS      | I    | Common Clock Downstream. The assertion of this pin indicates that all downstream ports are using the same clock source as that provided to downstream devices. This bit is used as the initial value of the Slot Clock Configuration bit in all of the Link Status Registers for downstream ports. The value may be overridden by modifying the SCLK bit in each downstream port's PCIELSTS register.                     |  |  |  |  |

| CCLKUS      | I    | Common Clock Upstream. The assertion of this pin indicates that the upstream port is using the same clock source as the upstream device. This bit is used as the initial value of the Slot Clock Configuration bit in the Link Status Register for the upstream port. The value may be overridden by modifying the SCLK bit in the P0_PCIELSTS register.                                                                  |  |  |  |  |

| MSMBSMODE   | I    | Master SMBus Slow Mode. The assertion of this pin indicates that the master SMBus should operate at 100 KHz instead of 400 KHz. This value may not be overridden.                                                                                                                                                                                                                                                         |  |  |  |  |

| PERSTN      | I    | Fundamental Reset. Assertion of this signal resets all logic inside PES16T4BG2 and initiates a PCI Express fundamental reset.                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RSTHALT     | I    | Reset Halt. When this signal is asserted during a PCI Express fundamental reset, PES16T4BG2 executes the reset procedure and remains in a reset state with the Master and Slave SMBuses active. This allows software to read and write registers internal to the device before normal device operation begins. The device exits the reset state when the RSTHALT bit is cleared in the SWCTL register by an SMBus master. |  |  |  |  |

| SWMODE[2:0] | I    | Switch Mode. These configuration pins determine the PES16T4BG2 switch operating mode.  0x0 - Normal switch mode  0x1 - Normal switch mode with Serial EEPROM initialization  0x2 - through 0x7 Reserved  These pins should be static and not change following the negation of PERSTN.                                                                                                                                     |  |  |  |  |

Table 5 System Pins

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| JTAG_TCK    | I    | JTAG Clock. This is an input test clock used to clock the shifting of data into or out of the boundary scan logic or JTAG Controller. JTAG_TCK is independent of the system clock with a nominal 50% duty cycle.                                                                                                                                                                                                                                                 |  |  |  |  |

| JTAG_TDI    | I    | JTAG Data Input. This is the serial data input to the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| JTAG_TDO    | 0    | JTAG Data Output. This is the serial data shifted out from the boundary scan logic or JTAG Controller. When no data is being shifted out, this signal is tri-stated.                                                                                                                                                                                                                                                                                             |  |  |  |  |

| JTAG_TMS    | I    | JTAG Mode. The value on this signal controls the test mode select of the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| JTAG_TRST_N | I    | JTAG Reset. This active low signal asynchronously resets the boundary scan logic and JTAG TAP Controller. An external pull-up on the board is recommended to meet the JTAG specification in cases where the tester can access this signal. However, for systems running in functional mode, one of the following should occur:  1) actively drive this signal low with control logic 2) statically drive this signal low with an external pull-down on the board |  |  |  |  |

Table 6 Test Pins

| Signal               | Туре | Name/Description                                                                                                                                                                                  |  |  |  |

|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REFRES0              | I/O  | Port 0 External Reference Resistor. Provides a reference for the Port 0 SerDes bias currents and PLL calibration circuitry. A 3 kOhm +/- 1% resistor should be connected from this pin to ground. |  |  |  |

| REFRES2              | I/O  | Port 2 External Reference Resistor. Provides a reference for the Port 2 SerDes bias currents and PLL calibration circuitry. A 3 kOhm +/- 1% resistor should be connected from this pin to ground. |  |  |  |

| REFRES4              | I/O  | Port 4 External Reference Resistor. Provides a reference for the Port 4 SerDes bias currents and PLL calibration circuitry. A 3 kOhm +/- 1% resistor should be connected from this pin to ground. |  |  |  |

| REFRES6              | I/O  | Port 6 External Reference Resistor. Provides a reference for the Port 6 SerDes bias currents and PLL calibration circuitry. A 3 kOhm +/- 1% resistor should be connected from this pin to ground. |  |  |  |

| V <sub>DD</sub> CORE | I    | Core V <sub>DD.</sub> Power supply for core logic.                                                                                                                                                |  |  |  |

| V <sub>DD</sub> I/O  | I    | I/O V <sub>DD.</sub> LVTTL I/O buffer power supply.                                                                                                                                               |  |  |  |

| V <sub>DD</sub> PEA  | I    | PCI Express Analog Power. Serdes analog power supply (1.0V).                                                                                                                                      |  |  |  |

| V <sub>DD</sub> PEHA | I    | PCI Express Analog High Power. Serdes analog power supply (2.5V).                                                                                                                                 |  |  |  |

| V <sub>DD</sub> PETA | I    | PCI Express Transmitter Analog Voltage. Serdes transmitter analog power supply (1.0V).                                                                                                            |  |  |  |

| V <sub>SS</sub>      | I    | Ground.                                                                                                                                                                                           |  |  |  |

Table 7 Power, Ground, and SerDes Resistor Pins

## **Pin Characteristics**

**Note:** Some input pads of the PES16T4BG2 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate levels. This is especially critical for unused control signal inputs which, if left floating, could adversely affect operation. Also, any input pin left floating can cause a slight increase in power consumption.

| Function            | Pin Name        | Туре | Buffer                    | I/O<br>Type        | Internal<br>Resistor <sup>1</sup> | Notes            |

|---------------------|-----------------|------|---------------------------|--------------------|-----------------------------------|------------------|

| PCI Express Inter-  | PE0RN[3:0]      | I    | PCle                      | Serial Link        |                                   |                  |

| face                | PE0RP[3:0]      | I    | differential <sup>2</sup> |                    |                                   |                  |

|                     | PE0TN[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE0TP[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE2RN[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE2RP[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE2TN[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE2TP[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE4RN[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE4RP[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE4TN[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE4TP[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE6RN[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE6RP[3:0]      | I    |                           |                    |                                   |                  |

|                     | PE6TN[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PE6TP[3:0]      | 0    |                           |                    |                                   |                  |

|                     | PEREFCLKN[0]    | I    | HCSL                      | Diff. Clock        |                                   | Refer to Table 9 |

|                     | PEREFCLKP[0]    | I    |                           | Input              |                                   |                  |

|                     | REFCLKM         | I    | LVTTL                     | Input              | pull-down                         |                  |

| SMBus               | MSMBADDR[4:1]   | I    | LVTTL                     | Input              | pull-up                           |                  |

|                     | MSMBCLK         | I/O  |                           | STI <sup>3</sup>   |                                   | pull-up on board |

|                     | MSMBDAT         | I/O  |                           | STI                |                                   | pull-up on board |

|                     | SSMBADDR[5,3:1] | I    |                           | Input              | pull-up                           |                  |

|                     | SSMBCLK         | I/O  |                           | STI                |                                   | pull-up on board |

|                     | SSMBDAT         | I/O  |                           | STI                |                                   | pull-up on board |

| General Purpose I/O | GPIO[15:0]      | I/O  | LVTTL                     | STI,<br>High Drive | pull-up                           |                  |

| System Pins         | CCLKDS          | I    | LVTTL                     | Input              | pull-up                           |                  |

|                     | CCLKUS          | I    |                           | Input              | pull-up                           |                  |

|                     | MSMBSMODE       | I    |                           | Input              | pull-down                         |                  |

|                     | PERSTN          | I    |                           | STI                |                                   |                  |

|                     | RSTHALT         | I    |                           | Input              | pull-down                         |                  |

|                     | SWMODE[2:0]     | I    |                           | Input              | pull-down                         |                  |

Table 8 Pin Characteristics (Part 1 of 2)

| Function         | Pin Name    | Туре | Buffer | I/O<br>Type | Internal<br>Resistor <sup>1</sup> | Notes |

|------------------|-------------|------|--------|-------------|-----------------------------------|-------|

| EJTAG / JTAG     | JTAG_TCK    | I    | LVTTL  | STI         | pull-up                           |       |

|                  | JTAG_TDI    | I    |        | STI         | pull-up                           |       |

|                  | JTAG_TDO    | 0    |        |             |                                   |       |

|                  | JTAG_TMS    | I    |        | STI         | pull-up                           |       |

|                  | JTAG_TRST_N | I    |        | STI         | pull-up                           |       |

| SerDes Reference | REFRES0     | I/O  | Analog |             |                                   |       |

| Resistors        | REFRES2     | I/O  |        |             |                                   |       |

|                  | REFRES4     | I/O  |        |             |                                   |       |

|                  | REFRES6     | I/O  |        |             |                                   |       |

## Table 8 Pin Characteristics (Part 2 of 2)

$<sup>^{1\</sup>cdot}$  Internal resistor values under typical operating conditions are 92K  $\Omega$  for pull-up and 90K  $\Omega$  for pull-down.

$<sup>^{2\</sup>cdot}$  All receiver pins set the DC common mode voltage to ground. All transmitters must be AC coupled to the media.

<sup>&</sup>lt;sup>3.</sup> Schmitt Trigger Input (STI).

## Logic Diagram — PES16T4BG2

Figure 4 PES16T4BG2 Logic Diagram

## **System Clock Parameters**

Values based on systems running at recommended supply voltages and operating temperatures, as shown in Tables 13 and 15.

| Parameter                | Description                                                          | Condition    | Min   | Typical | Max              | Unit |

|--------------------------|----------------------------------------------------------------------|--------------|-------|---------|------------------|------|

| Refclk <sub>FREQ</sub>   | Input reference clock frequency range                                |              | 100   |         | 125 <sup>1</sup> | MHz  |

| T <sub>C-RISE</sub>      | Rising edge rate                                                     | Differential | 0.6   |         | 4                | V/ns |

| T <sub>C-FALL</sub>      | Falling edge rate                                                    | Differential | 0.6   |         | 4                | V/ns |

| V <sub>IH</sub>          | Differential input high voltage                                      | Differential | +150  |         |                  | mV   |

| V <sub>IL</sub>          | Differential input low voltage                                       | Differential |       |         | -150             | mV   |

| V <sub>CROSS</sub>       | Absolute single-ended crossing point voltage                         | Single-ended | +250  |         | +550             | mV   |

| V <sub>CROSS-DELTA</sub> | Variation of V <sub>CROSS</sub> over all rising clock edges          | Single-ended |       |         | +140             | mV   |

| V <sub>RB</sub>          | Ring back voltage margin                                             | Differential | -100  |         | +100             | mV   |

| T <sub>STABLE</sub>      | Time before V <sub>RB</sub> is allowed                               | Differential | 500   |         |                  | ps   |

| T <sub>PERIOD-AVG</sub>  | Average clock period accuracy                                        |              | -300  |         | 2800             | ppm  |

| T <sub>PERIOD-ABS</sub>  | Absolute period, including spread-spectrum and jitter                |              | 9.847 |         | 10.203           | ns   |

| T <sub>CC-JITTER</sub>   | Cycle to cycle jitter                                                |              |       |         | 150              | ps   |

| V <sub>MAX</sub>         | Absolute maximum input voltage                                       |              |       |         | +1.15            | V    |

| V <sub>MIN</sub>         | Absolute minimum input voltage                                       |              | -0.3  |         |                  | V    |

| Duty Cycle               | Duty cycle                                                           |              | 40    |         | 60               | %    |

| Rise/Fall Matching       | Single ended rising Refclk edge rate versus falling Refclk edge rate |              |       | 20      |                  | %    |

| Z <sub>C-DC</sub>        | Clock source output DC impedance                                     |              | 40    |         | 60               | Ω    |

Table 9 Input Clock Requirements

## **AC Timing Characteristics**

| Parameter                                    | Description                                                                  |        | Gen 1            |                  |                  | Units            |                  |       |

|----------------------------------------------|------------------------------------------------------------------------------|--------|------------------|------------------|------------------|------------------|------------------|-------|

| Parameter                                    | Description                                                                  |        | Typ <sup>1</sup> | Max <sup>1</sup> | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> | Units |

| PCIe Transmit                                |                                                                              |        |                  |                  |                  |                  |                  |       |

| UI                                           | Unit Interval                                                                | 399.88 | 400              | 400.12           | 199.94           | 200              | 200.06           | ps    |

| T <sub>TX-EYE</sub>                          | Minimum Tx Eye Width                                                         | 0.75   |                  |                  | 0.75             |                  |                  | UI    |

| T <sub>TX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time between the jitter median and maximum deviation from the median |        |                  | 0.125            |                  |                  |                  | UI    |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | TX Rise/Fall Time: 20% - 80%                                                 | 0.125  |                  |                  | 0.15             |                  |                  | UI    |

| T <sub>TX- IDLE-MIN</sub>                    | Minimum time in idle                                                         | 20     |                  |                  | 20               |                  |                  | UI    |

Table 10 PCle AC Timing Characteristics (Part 1 of 2)

<sup>&</sup>lt;sup>1.</sup> The input clock frequency will be either 100 or 125 MHz depending on signal REFCLKM.

| Parameter                                | Decembra                                                                     |                  | Gen 1            |                  |                  | Gen 2            |                  | Units |

|------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|-------|

| Parameter                                | Description                                                                  | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> | Units |

| T <sub>TX-IDLE-SET-TO-IDLE</sub>         | Maximum time to transition to a valid Idle after sending an Idle ordered set |                  |                  | 8                |                  |                  | 8                | ns    |

| T <sub>TX-IDLE-TO-DIFF</sub> -           | Maximum time to transition from valid idle to diff data                      |                  |                  | 8                |                  |                  | 8                | ns    |

| T <sub>TX-SKEW</sub>                     | Transmitter data skew between any 2 lanes                                    |                  |                  | 1.3              |                  |                  | 1.3              | ns    |

| T <sub>MIN-PULSED</sub>                  | Minimum Instantaneous Lone Pulse Width                                       |                  | NA               |                  | 0.9              |                  |                  | UI    |

| T <sub>TX-HF-DJ-DD</sub>                 | Transmitter Deterministic Jitter > 1.5MHz Bandwidth                          |                  | NA               |                  |                  |                  | 0.15             | UI    |

| T <sub>RF-MISMATCH</sub>                 | Rise/Fall Time Differential Mismatch                                         |                  | NA               |                  |                  |                  | 0.1              | UI    |

| PCIe Receive                             |                                                                              | •                |                  |                  |                  | •                |                  |       |

| UI                                       | Unit Interval                                                                | 399.88           | 400              | 400.12           | 199.94           |                  | 200.06           | ps    |

| T <sub>RX-EYE</sub> (with jitter)        | Minimum Receiver Eye Width (jitter tolerance)                                | 0.4              |                  |                  | 0.4              |                  |                  | UI    |

| T <sub>RX-EYE-MEDIUM</sub> TO MAX JITTER | Max time between jitter median & max deviation                               |                  |                  | 0.3              |                  |                  |                  | UI    |

| T <sub>RX-SKEW</sub>                     | Lane to lane input skew                                                      |                  |                  | 20               |                  |                  | 8                | ns    |

| T <sub>RX-HF-RMS</sub>                   | 1.5 — 100 MHz RMS jitter (common clock)                                      |                  | NA               |                  |                  |                  | 3.4              | ps    |

| T <sub>RX-HF-DJ-DD</sub>                 | Maximum tolerable DJ by the receiver (common clock)                          |                  | NA               |                  |                  |                  | 88               | ps    |

| T <sub>RX-LF-RMS</sub>                   | 10 KHz to 1.5 MHz RMS jitter (common clock)                                  | NA               |                  |                  |                  |                  | 4.2              | ps    |

| T <sub>RX-MIN-PULSE</sub>                | Minimum receiver instantaneous eye width                                     |                  | NA               |                  | 0.6              |                  |                  | UI    |

Table 10 PCIe AC Timing Characteristics (Part 2 of 2)

<sup>&</sup>lt;sup>1.</sup> Minimum, Typical, and Maximum values meet the requirements under PCI Specification 2.0

| Signal                  | Symbol           | Reference<br>Edge | Min | Max | Unit | Timing<br>Diagram<br>Reference |

|-------------------------|------------------|-------------------|-----|-----|------|--------------------------------|

| GPI0                    |                  |                   |     |     |      |                                |

| GPIO[15:0] <sup>1</sup> | Tpw <sup>2</sup> | None              | 50  | _   | ns   |                                |

Table 11 GPIO AC Timing Characteristics

$<sup>^{1\</sup>cdot}$  GPIO signals must meet the setup and hold times if they are synchronous or the minimum pulse width if they are asynchronous.

<sup>&</sup>lt;sup>2.</sup> The values for this symbol were determined by calculation, not by testing.

| Signal                  | Symbol                 | Reference<br>Edge | Min  | Max  | Unit | Timing<br>Diagram<br>Reference |

|-------------------------|------------------------|-------------------|------|------|------|--------------------------------|

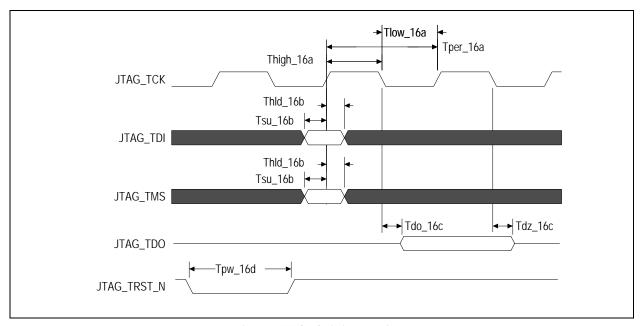

| JTAG                    |                        |                   |      |      |      |                                |

| JTAG_TCK                | Tper_16a               | none              | 50.0 | _    | ns   | See Figure 5.                  |

|                         | Thigh_16a,<br>Tlow_16a |                   | 10.0 | 25.0 | ns   |                                |

| JTAG_TMS <sup>1</sup> , | Tsu_16b                | JTAG_TCK rising   | 2.4  | _    | ns   |                                |

| JTAG_TDI                | Thld_16b               |                   | 1.0  | _    | ns   |                                |

| JTAG_TDO                | Tdo_16c                | JTAG_TCK falling  | _    | 20   | ns   |                                |

|                         | Tdz_16c <sup>2</sup>   |                   | _    | 20   | ns   |                                |

| JTAG_TRST_N             | Tpw_16d <sup>2</sup>   | none              | 25.0 | _    | ns   |                                |

Table 12 JTAG AC Timing Characteristics

$<sup>^{2\</sup>cdot}$  The values for this symbol were determined by calculation, not by testing.

Figure 5 JTAG AC Timing Waveform

<sup>1.</sup> The JTAG specification, IEEE 1149.1, recommends that JTAG\_TMS should be held at 1 while the signal applied at JTAG\_TRST\_N changes from 0 to 1. Otherwise, a race may occur if JTAG\_TRST\_N is deasserted (going from low to high) on a rising edge of JTAG\_TCK when JTAG\_TMS is low, because the TAP controller might go to either the Run-Test/Idle state or stay in the Test-Logic-Reset state.

## **Recommended Operating Supply Voltages**

| Symbol                            | Parameter                               | Minimum | Typical | Maximum | Unit |

|-----------------------------------|-----------------------------------------|---------|---------|---------|------|

| V <sub>DD</sub> CORE              | Internal logic supply                   | 0.9     | 1.0     | 1.1     | V    |

| V <sub>DD</sub> I/O               | I/O supply except for SerDes LVPECL/CML | 3.135   | 3.3     | 3.465   | V    |

| V <sub>DD</sub> PEA <sup>1</sup>  | PCI Express Analog Power                | 0.95    | 1.0     | 1.1     | V    |

| V <sub>DD</sub> PEHA <sup>2</sup> | PCI Express Analog High Power           | 2.25    | 2.5     | 2.75    | V    |

| V <sub>DD</sub> PETA              | PCI Express Transmitter Analog Voltage  | 0.95    | 1.0     | 1.1     | V    |

| V <sub>SS</sub>                   | Common ground                           | 0       | 0       | 0       | V    |

#### Table 13 PES16T4BG2 Operating Voltages

#### **Absolute Maximum Voltage Rating**

| Core Supply | PCIe Analog<br>Supply | 9   9   1 |      | I/O Supply |

|-------------|-----------------------|-----------|------|------------|

| 1.5V        | 1.5V                  | 4.6V      | 1.5V | 4.6V       |

Table 14 PES24T3G2 Absolute Maximum Voltage Rating

**Warning:** For proper and reliable operation in adherence with this data sheet, the device should not exceed the recommended operating voltages in Table 13. The absolute maximum operating voltages in Table 14 are offered to provide guidelines for voltage excursions outside the recommended voltage ranges. Device functionality is not guaranteed at these conditions and sustained operation at these values or any exposure to voltages outside the maximum range may adversely affect device functionality and reliability.

## Power-Up/Power-Down Sequence

During power supply ramp-up,  $V_{DD}CORE$  must remain at least 1.0V below  $V_{DD}I/O$  at all times. There are no other power-up sequence requirements for the various operating supply voltages.

The power-down sequence can occur in any order.

## **Recommended Operating Temperature**

| Grade      | Temperature          |

|------------|----------------------|

| Commercial | 0°C to +70°C Ambient |

Table 15 PES16T4BG2 Operating Temperatures

$<sup>^{1.}</sup>$   $V_{DD}$ PEA should have no more than  $25 mV_{peak-peak}$  AC power supply noise superimposed on the 1.0V nominal DC value.

<sup>&</sup>lt;sup>2.</sup> V<sub>DD</sub>PEHA should have no more than 50mV<sub>peak-peak</sub> AC power supply noise superimposed on the 2.5V nominal DC value.

## **Power Consumption**

Typical power is measured under the following conditions: 25°C Ambient, 35% total link usage on all ports, typical voltages defined in Table 13 (and also listed below).

Maximum power is measured under the following conditions: 70°C Ambient, 85% total link usage on all ports, maximum voltages defined in Table 13 (and also listed below).

| Number of active |                  | Core Supply |             | PCIe Analog<br>Supply |             | PCIe Analog<br>High Supply |              | PCIe Termin-<br>ation Supply |             | I/O Supply  |               | Total        |              |

|------------------|------------------|-------------|-------------|-----------------------|-------------|----------------------------|--------------|------------------------------|-------------|-------------|---------------|--------------|--------------|

| Lanes per        | es per Port<br>1 |             | Max<br>1.1V | Тур<br>1.0V           | Max<br>1.1V | Тур<br>2.5V                | Max<br>2.75V | Тур<br>1.0V                  | Max<br>1.1V | Тур<br>3.3V | Max<br>3.465V | Typ<br>Power | Max<br>Power |

| 4/4/4/4          | mA               | 700         | 968         | 750                   | 880         | 260                        | 330          | 361                          | 429         | 3           | 4             |              |              |

| (Full swing)     | Watts            | 0.70        | 1.06        | 0.75                  | 1.0         | 0.65                       | 0.91         | 0.36                         | 0.47        | 0.01        | 0.02          | 2.47         | 3.46         |

| 4/4/1/1          | mA               | 550         | 720         | 540                   | 660         | 150                        | 220          | 160                          | 165         | 3           | 4             |              |              |

| (Full swing)     | Watts            | 0.55        | 0.79        | 0.54                  | 0.73        | 0.38                       | 0.61         | 0.16                         | 0.18        | 0.01        | 0.02          | 1.64         | 2.33         |

Table 16 PES16T4BG2 Power Consumption

#### Thermal Considerations

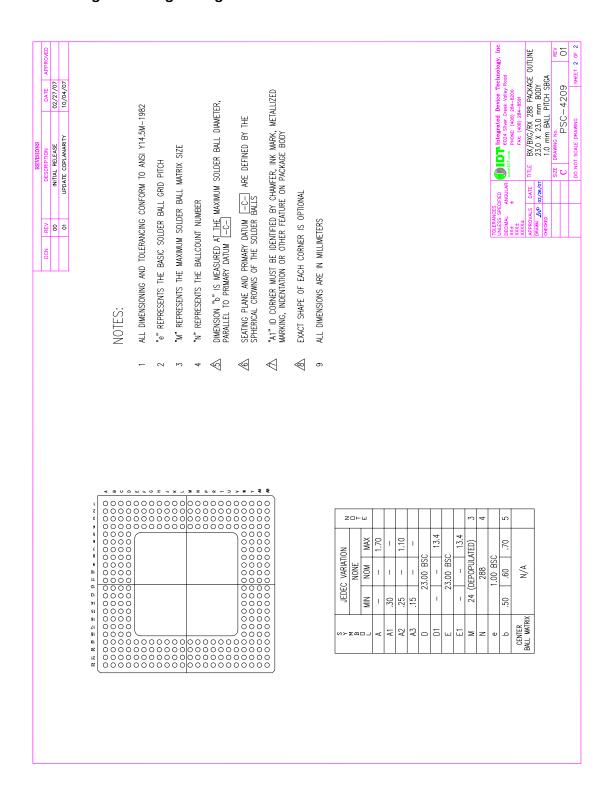

This section describes thermal considerations for the PES16T4BG2 (23mm<sup>2</sup> SBGA288 package). The data in Table 17 below contains information that is relevant to the thermal performance of the PES16T4BG2 switch.

| Symbol                   | Parameter                                         | Value | Units | Conditions     |

|--------------------------|---------------------------------------------------|-------|-------|----------------|

| T <sub>J(max)</sub>      | Junction Temperature                              | 125   | °C    | Maximum        |

| T <sub>A(max)</sub>      | Ambient Temperature                               | 70    | oC.   | Maximum        |

|                          |                                                   | 19.8  | °C/W  | Zero air flow  |

| $\theta_{JA(effective)}$ | Effective Thermal Resistance, Junction-to-Ambient | 13.3  | °C/W  | 1 m/S air flow |

|                          |                                                   | 11.8  | °C/W  | 2 m/S air flow |

| $\theta_{JB}$            | Thermal Resistance, Junction-to-Board             | 9.5   | °C/W  |                |

| θЈС                      | Thermal Resistance, Junction-to-Case              | 1.1   | °C/W  |                |

| Р                        | Power Dissipation of the Device                   | 3.24  | Watts | Maximum        |

Table 17 Thermal Specifications for PES16T4BG2, 23x23 mm SBGA288 Package

**Note:** It is important for the reliability of this device in any user environment that the junction temperature not exceed the  $T_{J(max)}$  value specified in Table 17. Consequently, the effective junction to ambient thermal resistance ( $\theta_{JA}$ ) for the worst case scenario must be maintained below the value determined by the formula:

$$\theta_{JA} = (T_{J(max)} - T_{A(max)})/P$$

Given that the values of  $T_{J(max)}$ ,  $T_{A(max)}$ , and P are known, the value of desired  $\theta_{JA}$  becomes a known entity to the system designer. How to achieve the desired  $\theta_{JA}$  is left up to the board or system designer, but in general, it can be achieved by adding the effects of  $\theta_{JC}$  (value provided in Table 17), thermal resistance of the chosen adhesive ( $\theta_{CS}$ ), that of the heat sink ( $\theta_{SA}$ ), amount of airflow, and properties of the circuit board (number of layers and size of the board). As a general guideline, this device will not need a heat sink if the board has 8 or more layers AND the board size is larger than 4"x12" AND airflow in excess of 0.5 m/s is available. It is strongly recommended that users perform their own thermal analysis for their own board and system design scenarios.

## **DC Electrical Characteristics**

Values based on systems running at recommended supply voltages, as shown in Table 13.

Note: See Table 8, Pin Characteristics, for a complete I/O listing.

| I/O Type    | Parameter                                | Description                                                    |                  | Gen1             |                  |                  | Gen2             |                  | Unit | Condi-<br>tions |

|-------------|------------------------------------------|----------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------|-----------------|

| J.          |                                          |                                                                | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> |      |                 |

| Serial Link | PCIe Transmit                            |                                                                |                  |                  |                  |                  |                  |                  |      |                 |

|             | V <sub>TX-DIFFp-p</sub>                  | Differential peak-to-peak output voltage                       | 800              |                  | 1200             | 800              |                  | 1200             | mV   |                 |

|             | V <sub>TX-DIFFp-p-LOW</sub>              | Low-Drive Differential Peak to<br>Peak Output Voltage          | 400              |                  | 1200             | 400              |                  | 1200             | mV   |                 |

|             | V <sub>TX-DE-RATIO-</sub><br>3.5dB       | De-emphasized differential output voltage                      | -3               |                  | -4               | -3.0             | -3.5             | -4.0             | dB   |                 |

|             | V <sub>TX-DE-RATIO-</sub><br>6.0dB       | De-emphasized differential output voltage                      | NA               |                  |                  | -5.5             | -6.0             | -6.5             | dB   |                 |

|             | V <sub>TX-DC-CM</sub>                    | DC Common mode voltage                                         | 0                |                  | 3.6              | 0                |                  | 3.6              | V    |                 |

|             | V <sub>TX-CM-ACP</sub>                   | RMS AC peak common mode output voltage                         |                  |                  | 20               |                  |                  |                  | mV   |                 |

|             | V <sub>TX-CM-DC-active-</sub> idle-delta | Abs delta of DC common mode voltage between L0 and idle        |                  |                  | 100              |                  |                  | 100              | mV   |                 |

|             | V <sub>TX-CM-DC-line-</sub><br>delta     | Abs delta of DC common mode voltage between D+ and D-          |                  |                  | 25               |                  |                  | 25               | mV   |                 |

|             | V <sub>TX-Idle-DiffP</sub>               | Electrical idle diff peak output                               |                  |                  | 20               |                  |                  | 20               | mV   |                 |

|             | RL <sub>TX-DIFF</sub>                    | Transmitter Differential Return                                | 10               |                  |                  |                  |                  | 10               | dB   | 0.05 - 1.25GHz  |

|             |                                          | loss                                                           |                  |                  |                  |                  |                  | 8                | dB   | 1.25 - 2.5GHz   |

|             | RL <sub>TX-CM</sub>                      | Transmitter Common Mode<br>Return loss                         | 6                |                  |                  |                  |                  | 6                | dB   |                 |

|             | Z <sub>TX-DIFF-DC</sub>                  | DC Differential TX impedance                                   | 80               | 100              | 120              |                  |                  | 120              | Ω    |                 |

|             | VTX-CM-ACpp                              | Peak-Peak AC Common                                            |                  | NA               |                  |                  |                  | 100              | mV   |                 |

|             | V <sub>TX-DC-CM</sub>                    | Transmit Driver DC Common<br>Mode Voltage                      | 0                |                  | 3.6              | 0                |                  | 3.6              | V    |                 |

|             | V <sub>TX-RCV-DETECT</sub>               | The amount of voltage change allowed during Receiver Detection |                  |                  | 600              |                  |                  | 600              | mV   |                 |

|             | I <sub>TX-SHORT</sub>                    | Transmitter Short Circuit Current Limit                        | 0                |                  | 90               |                  |                  |                  | 90   | mA              |

Table 18 DC Electrical Characteristics (Part 1 of 2)

| I/O Type           | Parameter                                  | Description                                                    |                  | Gen1             |                           |                  | Gen2             |                           | Unit | Condi-<br>tions           |

|--------------------|--------------------------------------------|----------------------------------------------------------------|------------------|------------------|---------------------------|------------------|------------------|---------------------------|------|---------------------------|

|                    |                                            |                                                                | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup>          | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup>          | -    |                           |

| Serial Link        | PCIe Receive                               |                                                                |                  |                  |                           |                  |                  |                           |      |                           |

| (cont.)            | V <sub>RX-DIFFp-p</sub>                    | Differential input voltage (peak-to-peak)                      | 175              |                  | 1200                      | 120              |                  | 1200                      | mV   |                           |

|                    | RL <sub>RX-DIFF</sub>                      | Receiver Differential Return Loss                              | 10               |                  |                           |                  |                  | 10                        | dB   | 0.05 - 1.25GHz            |

|                    |                                            |                                                                |                  |                  |                           |                  |                  | 8                         |      | 1.25 - 2.5GHz             |

|                    | RL <sub>RX-CM</sub>                        | Receiver Common Mode Return<br>Loss                            | 6                |                  |                           |                  |                  | 6                         | dB   |                           |

|                    | Z <sub>RX-DIFF-DC</sub>                    | Differential input impedance (DC)                              | 80               | 100              | 120                       | Refer            | to return lo     | ss spec                   | Ω    |                           |

|                    | Z <sub>RXDC</sub>                          | DC common mode impedance                                       | 40               | 50               | 60                        | 40               |                  | 60                        | Ω    |                           |

|                    | Z <sub>RX-COMM-DC</sub>                    | Powered down input common mode impedance (DC)                  | 200k             | 350k             |                           |                  |                  | 50k                       | Ω    |                           |

|                    | Z <sub>RX-HIGH-IMP-DC-</sub><br>POS        | DC input CM input impedance for V>0 during reset or power down |                  |                  | 50k                       |                  |                  | 50k                       | Ω    |                           |

|                    | Z <sub>RX-HIGH-IMP-DC-</sub><br>NEG        | DC input CM input impedance for V<0 during reset or power down |                  |                  | 1.0k                      |                  |                  | 1.0k                      | Ω    |                           |

|                    | V <sub>RX-IDLE-DET-</sub><br>DIFFp-p       | Electrical idle detect threshold                               | 65               |                  | 175                       | 65               |                  | 175                       | mV   |                           |

|                    | V <sub>RX-CM-ACp</sub>                     | Receiver AC common-mode peak voltage                           |                  |                  | 150                       |                  |                  | 150                       | mV   | V <sub>RX-CM-ACp</sub>    |

| PCIe REFCL         | <                                          |                                                                |                  | l                |                           | H                | I.               |                           | l    |                           |

|                    | C <sub>IN</sub>                            | Input Capacitance                                              | 1.5              | _                |                           | 1.5              | _                |                           | pF   |                           |

| Other I/Os         |                                            |                                                                |                  | •                |                           |                  |                  |                           | •    |                           |

| LOW Drive          | I <sub>OL</sub>                            |                                                                | _                | 2.5              | _                         | _                | 2.5              | _                         | mA   | V <sub>OL</sub> = 0.4v    |

| Output             | I <sub>OH</sub>                            |                                                                | _                | -5.5             | _                         | _                | -5.5             | _                         | mA   | V <sub>OH</sub> = 1.5V    |

| High Drive         | I <sub>OL</sub>                            |                                                                | ı                | 12.0             | _                         | -                | 12.0             |                           | mA   | V <sub>OL</sub> = 0.4v    |

| Output             | I <sub>OH</sub>                            |                                                                | 1                | -20.0            | _                         | 1                | -20.0            |                           | mA   | V <sub>OH</sub> = 1.5V    |

| Schmitt Trig-      | $V_{IL}$                                   |                                                                | -0.3             | _                | 0.8                       | -0.3             | _                | 0.8                       | V    | _                         |

| ger Input<br>(STI) | V <sub>IH</sub>                            |                                                                | 2.0              | _                | V <sub>DD</sub> I/O + 0.5 | 2.0              | _                | V <sub>DD</sub> I/O + 0.5 | V    | _                         |

| Input              | $V_{IL}$                                   |                                                                | -0.3             | _                | 0.8                       | -0.3             | _                | 0.8                       | V    | _                         |

|                    | V <sub>IH</sub>                            |                                                                | 2.0              | _                | V <sub>DD</sub> I/O + 0.5 | 2.0              | _                | V <sub>DD</sub> I/O + 0.5 | V    | _                         |

| Capacitance        | C <sub>IN</sub>                            |                                                                | _                | _                | 8.5                       | _                | _                | 8.5                       | pF   | _                         |

| Leakage            | Inputs                                     |                                                                | _                | _                | <u>+</u> 10               | _                | _                | <u>+</u> 10               | μА   | V <sub>DD</sub> I/O (max) |

|                    | I/O <sub>LEAK W/O</sub><br>Pull-ups/downs  |                                                                | _                | _                | <u>+</u> 10               | _                | _                | <u>+</u> 10               | μА   | V <sub>DD</sub> I/O (max) |

|                    | I/O <sub>LEAK WITH</sub><br>Pull-ups/downs |                                                                | _                | _                | <u>+</u> 80               | _                | _                | <u>+</u> 80               | μА   | V <sub>DD</sub> I/O (max) |

Table 18 DC Electrical Characteristics (Part 2 of 2)

$<sup>^{1\</sup>cdot}$  Minimum, Typical, and Maximum values meet the requirements under PCI Specification 2.0.

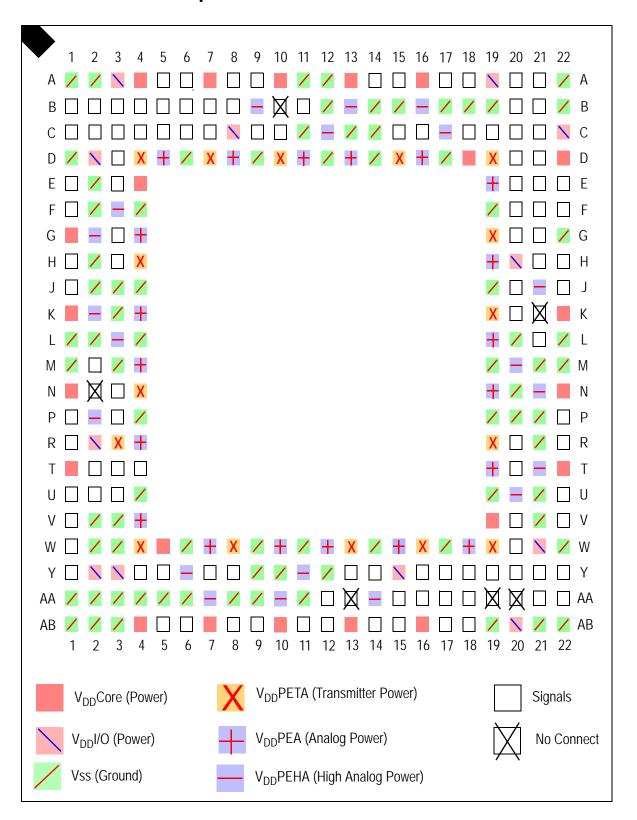

## Package Pinout — 288-BGA Signal Pinout for PES16T4BG2

The following table lists the pin numbers and signal names for the PES16T4BG2 device.

| Pin        | Function             | Alt | Pin | Function             | Alt | Pin | Function             | Alt | Pin | Function             | Alt |

|------------|----------------------|-----|-----|----------------------|-----|-----|----------------------|-----|-----|----------------------|-----|

| A1         | $V_{SS}$             |     | B13 | V <sub>DD</sub> PEHA |     | D3  | PE2TP00              |     | F21 | GPIO_06              |     |

| A2         | V <sub>SS</sub>      |     | B14 | V <sub>SS</sub>      |     | D4  | V <sub>DD</sub> PETA |     | F22 | PE4RN03              |     |

| A3         | V <sub>DD</sub> I/O  |     | B15 | V <sub>SS</sub>      |     | D5  | V <sub>DD</sub> PEA  |     | G1  | V <sub>DD</sub> CORE |     |

| A4         | V <sub>DD</sub> CORE |     | B16 | V <sub>DD</sub> PEHA |     | D6  | V <sub>SS</sub>      |     | G2  | V <sub>DD</sub> PEHA |     |

| <b>A</b> 5 | PE6RP03              |     | B17 | V <sub>SS</sub>      |     | D7  | V <sub>DD</sub> PETA |     | G3  | PE2TP01              |     |

| A6         | PE6RN03              |     | B18 | V <sub>SS</sub>      |     | D8  | V <sub>DD</sub> PEA  |     | G4  | V <sub>DD</sub> PEA  |     |

| A7         | V <sub>DD</sub> CORE |     | B19 | V <sub>SS</sub>      |     | D9  | V <sub>SS</sub>      |     | G19 | V <sub>DD</sub> PETA |     |

| A8         | PE6RP02              |     | B20 | REFCLKM              |     | D10 | V <sub>DD</sub> PETA |     | G20 | PE4TP03              |     |

| A9         | PE6RN02              |     | B21 | GPIO_13              |     | D11 | V <sub>DD</sub> PEA  |     | G21 | GPIO_05              |     |

| A10        | V <sub>DD</sub> CORE |     | B22 | V <sub>SS</sub>      |     | D12 | V <sub>SS</sub>      |     | G22 | V <sub>SS</sub>      |     |

| A11        | V <sub>SS</sub>      |     | C1  | SSMBCLK              |     | D13 | V <sub>DD</sub> PEA  |     | H1  | PE2RN01              |     |

| A12        | V <sub>SS</sub>      |     | C2  | SSMBDAT              |     | D14 | V <sub>SS</sub>      |     | H2  | V <sub>SS</sub>      |     |

| A13        | V <sub>DD</sub> CORE |     | C3  | MSMBSMODE            |     | D15 | V <sub>DD</sub> PETA |     | H3  | PE2TN01              |     |

| A14        | PE6RP01              |     | C4  | MSMBDAT              |     | D16 | V <sub>DD</sub> PEA  |     | H4  | V <sub>DD</sub> PETA |     |

| A15        | PE6RN01              |     | C5  | MSMBADDR_4           |     | D17 | V <sub>SS</sub>      |     | H19 | V <sub>DD</sub> PEA  |     |