1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

### SYNC SEPARATOR WITH VARIABLE FILTER

#### **DEVICE DESCRIPTION**

The ZXFV4583 provides the ability to separate out video synchronization signals for a wide variety of TV and CRT display systems, standard and non-standard.

Flexibility arises from the use of just three external resistors to adapt to each application. One resistor controls a fully integrated internal color carrier filter with variable bandwidth. This filter avoids disturbance from the color carrier, permitting accurate threshold slicing for timing extraction.

A second resistor controls the voltage threshold for loss of signal detection after a time-out interval. The third resistor controls the timing functions.

DC restoration for displays is facilitated by the Back Porch synch output, which can be used to drive an external circuit to clamp the blanking voltage to a fixed level.

#### **ORDERING INFORMATION**

| Part Number   | Container | Increment |

|---------------|-----------|-----------|

| ZXFV4583N16TA | Reel 7"   | 500       |

| ZXFV4583N16TC | Reel 13"  | 2500      |

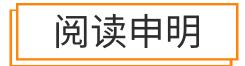

### CONNECTION DIAGRAM

### FEATURES AND BENEFITS

- PAL, NTSC, SECAM

- Variable filter for optimal accuracy

- Sync outputs: composite, horizontal, vertical, back porch, odd/even

- No-signal detector

- On chip sample / hold capacitors

- +5V single supply

- Default vertical output where there are no serration pulses

- Pin and layout compatible with part EL4583 in SO16N surface mount package

#### **APPLICATIONS**

- Digital image capture

- Video input systems requiring separation of picture timing

- Video distribution

- CCTV surveillance

- Digital multimedia

- Timing for black level clamp

### ABSOLUTE MAXIMUM RATINGS

| Supply voltage V <sub>CC</sub>         | -0.5V to +7V                   |

|----------------------------------------|--------------------------------|

| Inputs to ground*                      | -0.5V to V <sub>CC</sub> +0.5V |

| Operating temperature range            | -40°C to 85°C                  |

| Storage                                | -65°C to +150°C                |

| Operating ambient junction temperature | T <sub>JMAX</sub> 150°C**      |

\*\*The thermal resistance from the semiconductor die to ambient is typically 120°C/W when the SO16 package is mounted on a PCB in free air. The power dissipation of the device when loaded must be designed to keep the device junction temperature below  $T_{JMAX}$ .

\*During power-up and power-down, these voltage ratings require that signals be applied only when the power supply is connected.

### ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 5V,  $R_{SET}$  = 681k $\Omega$ ,  $R_{FILT}$  = 22k $\Omega$ ,  $R_{NOSIG}$  = 82k $\Omega$ ,  $T_{amb}$  = 25°C unless otherwise stated.

Test level: P = 100% production test

C = Characterized only

| PARAMETER                                 | CONDITIONS              | TEST | MIN  | ТҮР  | MAX  | UNIT |

|-------------------------------------------|-------------------------|------|------|------|------|------|

| DC Characteristics                        |                         |      |      |      |      |      |

| Supply current                            |                         | Р    | 2    | 4.5  | 6.5  | mA   |

| Clamp voltage at FILTIN                   | Pin 4 unloaded          | Р    | 1.2  | 1.35 | 1.5  | V    |

| Discharge current at FILTIN               | Pin 4, Vin = 2V pk-pk   | С    |      | 1    |      | μA   |

| Discharge current at FILTIN               | Pin 4, no signal        | С    | 3    | 6    | 12   | μA   |

| Clamp charge current at FILTIN            | Pin 4, Vin = 1V pk-pk   | Р    | 2    | 3    | 4    | mA   |

| Clamp voltage at FVIDIN                   | Pin 8 unloaded          | Р    | 1.2  | 1.35 | 1.5  | V    |

| Discharge current at FVIDIN               | Pin 8, Vin = 2V pk-pk   | С    |      | 1    |      | μA   |

| Discharge current at FVIDIN               | Pin 8, no signal        | С    | 3    | 6    | 12   | μA   |

| Clamp charge current at FVIDIN            | Pin 8, Vin = 1V pk-pk   | Р    | 2    | 3    | 4    | mA   |

| R <sub>SET</sub> voltage, pin 12          |                         | Р    | 1.5  | 1.75 | 2    | V    |

| R <sub>FILT</sub> voltage, pin 1          |                         | Р    | 0.35 | 0.5  | 0.65 | V    |

| RNOSIG current, pin 2                     |                         | Р    | 1.5  | 2.5  | 3.5  | μA   |

| Logic output low voltage, V <sub>OL</sub> | I <sub>OL</sub> = 1.6mA | Р    |      | 0.35 | 0.8  | V    |

### **ELECTRICAL CHARACTERISTICS (Cont.)**

$V_{CC}$  = 5V,  $R_{SET}$  = 681k $\Omega$ ,  $R_{FILT}$  = 22k $\Omega$ ,  $R_{NOSIG}$  = 82k $\Omega$ ,  $T_{amb}$  = 25°C unless otherwise stated.

| PARAMETER                                    | CONDITIONS                         | TEST   | MIN      | ТҮР      | MAX | UNIT     |

|----------------------------------------------|------------------------------------|--------|----------|----------|-----|----------|

| AC Characteristics                           |                                    |        |          |          |     |          |

| FILTIN function input voltage range          | PAL/NTSC                           | Р      | 0.5      |          | 2   | V pk-pk  |

| Filter voltage gain                          | FILTIN to FILOUT                   | Р      | 4.9      | 5.7      | 6.5 | dB       |

| Filter attenuation                           | 4.4MHz for PAL,<br>3.6MHz for NTSC | P<br>P | 15<br>10 | 19<br>14 |     | dB<br>dB |

| Slice level                                  | Vin = 1V pk-pk                     | Р      | 40       | 50       | 60  | %        |

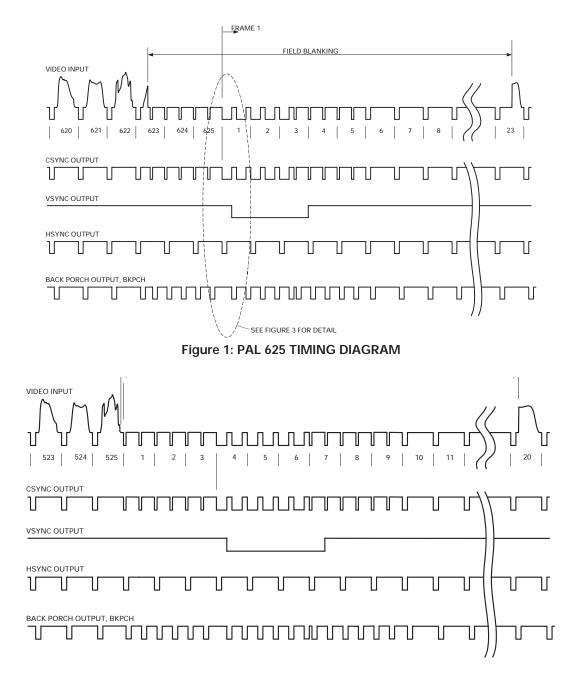

| CSYNC prop. Delay, t <sub>CS</sub>           | Relative to pin 4 input            | Р      |          | 250      | 400 | ns       |

| VSYNC delay                                  |                                    | С      |          | 250      |     | ns       |

| VSYNC pulse width, t <sub>VSYNC</sub> (PAL)  |                                    | С      |          | 165      |     | μS       |

| VSYNC pulse width, t <sub>VSYNC</sub> (NTSC) |                                    | С      |          | 195      |     | μS       |

| VSYNC default delay, t <sub>VSD</sub>        |                                    | Р      | 30       | 36       | 45  | μS       |

| HSYNC delay                                  |                                    | Р      |          | 250      |     | ns       |

| HSYNC pulse width, t <sub>HSYNC</sub>        |                                    | Р      | 3.8      | 5        | 6.2 | μS       |

| BKPCH delay, t <sub>BD</sub>                 | Relative to pin 4 input            | Р      |          | 250      | 400 | ns       |

| BKPCH pulse width, t <sub>B</sub>            |                                    | Р      | 2.7      | 3.7      | 4.7 | μS       |

Note: In order to avoid coupling between high speed logic output signals and analog inputs, the test circuit layout uses connections from the logic output pins routed away from the analog pins. In the application, similar care in the layout is required, keeping resistors R<sub>FILT</sub>, R<sub>NOSIG</sub> and R<sub>SET</sub> close to their respective pins, in particular routing signal CSYNC away from pins 1, 2 and 12.

### CONNECTIONS

| PIN No. | PIN NAME           | ТҮРЕ                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|--------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | R <sub>FILT</sub>  | Resistor<br>control | Controls the input color carrier filter characteristic. An external resistor $R_{FILT}$ connected from this pin to 0V sets the bandwidth. Smaller $R_{FILT}$ gives increased bandwidth. See the detailed operating description below.                                                                                                                                                                                      |

| 2       | R <sub>NOSIG</sub> | Resistor<br>control | Controls the no-signal detector level. An external resistor $R_{NOSIG}$ connected from this pin to 0V sets the threshold voltage level, according to the equation $V_{PMIN} = 0.75 R_{NOSIG} / R_{SET}$ where $V_{PMIN}$ is the minimum detected sync pulse amplitude at pin 4 and $R_{SET}$ is the resistor value at pin 12.                                                                                              |

| 3       | CSYNC              | Logic out           | Composite sync logic output. Includes all sync pulses derived from the input video.                                                                                                                                                                                                                                                                                                                                        |

| 4       | FILTIN             | Analog in           | Input to color carrier filter. This is the main analog (unfiltered)<br>composite video input used when color carrier filtering is required. A<br>voltage clamp circuit and adaptive current source are also included<br>at this node. See the detailed operating description. When the filter<br>is not used, this pin must be left open circuit.                                                                          |

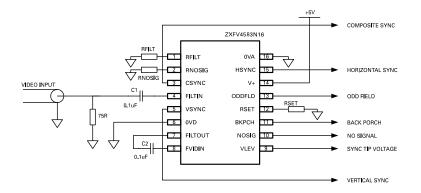

| 5       | VSYNC              | Logic out           | Vertical sync output. This is an active low pulse commencing on the first vertical sync pulse trailing (rising) edge and ending near the second next equalizing pulse. See timing diagram.                                                                                                                                                                                                                                 |

| 6       | OVD                | Ground              | Provides ground return path for internal logic output buffer circuits.<br>Normally connected externally to a common PCB ground plane.                                                                                                                                                                                                                                                                                      |

| 7       | FILTOUT            | Analog out          | Analog output signal from color carrier filter. The filter voltage gain is nominally 2. This output is normally capacitor-coupled to pin 8.                                                                                                                                                                                                                                                                                |

| 8       | FVIDIN             | Analog in           | Input for filtered analog video signal input. This is the direct input<br>to the sample/hold and sync slicing comparator providing the logic<br>timing edges. This input is normally coupled via an external<br>capacitor from FILTOUT, pin 7. It may be used as the signal input<br>where the color carrier filter is not required. Includes a clamp<br>similar that of pin 4.                                            |

| 9       | VLEV               | Analog out          | Analog output, a positive voltage typically equal to twice the (negative) peak sync pulse amplitude if the filter is used.                                                                                                                                                                                                                                                                                                 |

| 10      | NOSIG              | Logic out           | Logic output, which goes high after a time-out delay when no signal is present. The threshold level is controlled at pin 2.                                                                                                                                                                                                                                                                                                |

| 11      | вкрсн              | Logic out           | Burst or Back Porch logic output, an active low monostable pulse<br>triggered from rising composite sync pulse edges. The width is set<br>by R <sub>SET</sub> to overlap most of the steady part of the back porch,<br>assuming the color carrier burst has been attenuated sufficiently by<br>filtering. This pulse is then suitable for controlling an external black<br>level clamping circuit. See the timing diagram. |

| 12      | R <sub>SET</sub>   | Resistor<br>control | Controls the timing interval of the sample/hold circuit and the monostable interval for the sync outputs according to the application. An external resistor, $R_{SET}$ connected from this pin to 0V establishes the timing parameter, to which these times are scaled together. See the detailed operating description.                                                                                                   |

| 13      | ODDFLD             | Logic out           | Odd field logic output. High during an odd numbered field, low during even. This output is timed with the start of the VSYNC pulse.                                                                                                                                                                                                                                                                                        |

| 14      | V+                 | Power in            | Power supply input, +5V.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 15      | HSYNC              | Logic out           | Horizontal sync logic output. Monostable output derived from<br>CSYNC falling edges, it achieves a steady stream of 5µs pulses. The<br>half line events during the field blanking interval are eliminated. See<br>timing diagram.                                                                                                                                                                                          |

### DETAILED DESCRIPTION

#### Introduction

This device includes all the functions required to separate out the critical timing points of most types of video signal. A sample-and-hold process is used to establish accurately the 50% point of the sync pulse. The input is also filtered to avoid the effect of the color carrier. The filter is coupled externally. The following paragraphs give a simplified description of the signal processing.

#### Color carrier filter

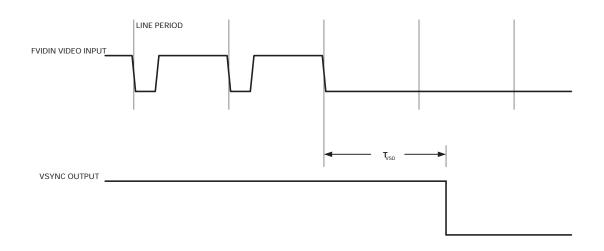

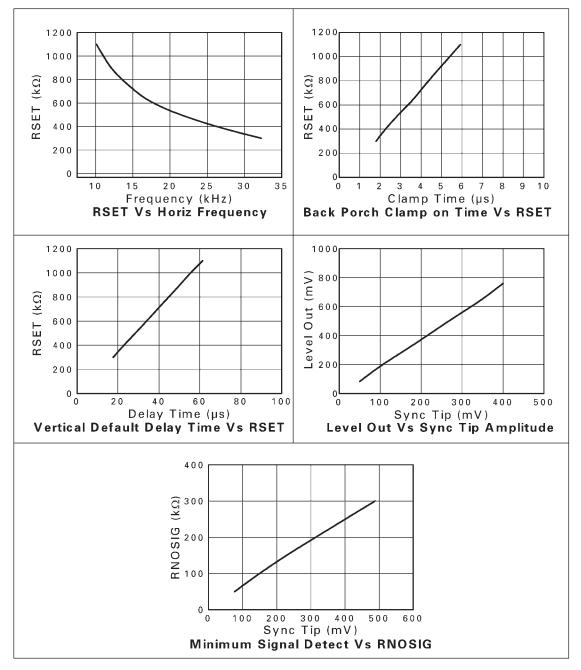

This low-pass filter provides adjustable attenuation of the color carrier with low distortion of the remaining sync pulses so as to ensure accurate timing of the extracted logic outputs. The control is via an external resistor R<sub>FILT</sub> connected from pin 1 to ground. R<sub>FILT</sub>=22k $\Omega$  gives corner frequency of ~1.3MHz corresponding to ~12dB attenuation @ 3.58MHz.(Corner freq. Proportional to 1/R<sub>FILT</sub>, minimum value 18k $\Omega$ ). A graph shows how the bandwidth varies with the resistor value.

#### **Clamping circuits**

Clamping circuits are use to limit the signal swing excursion after AC coupling at both the input to the filter, FILTIN and the timing extractor input, FVIDIN. In each case, the sync tip level is maintained at a value of nominally 1.35V.

#### Sync timing extraction circuits

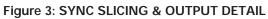

The waveforms are depicted in Timing Diagrams, Figure 1 for PAL (625 lines) and Figure 2 for NTSC (525 lines). Sample-and-hold circuits are used to obtain time-delayed voltage values of the sync tip and the back porch. The sample gates are controlled by a comparator sensing the video input relative to a threshold at a fixed offset above the sync tip clamp level. The sampled voltages are combined in a potential divider to derive the mean voltage (50% amplitude), which is used as the sync pulse threshold. A second comparator then provides CSYNC, the logic version of the composite sync signal. This is delayed slightly as shown in Figure 3. The time delay comprises that of the input filter and also the smaller delay of the comparator and logic. The timing of the sample hold and other time parameters are all controlled together in unison by the external resistor R<sub>SET</sub>. A 1% resistor tolerance is recommended. The sync tip voltage level from the sample-and-hold is buffered and provided as an analog output, VLEV.

**ISSUE 3 - NOVEMBER 2003**

The vertical sync output **VSYNC** is derived from the Field pulse group. Where there are short equalization pulses in the standard systems, these short pulses are ignored. Essentially, a pulse width discriminator circuit senses the first of the Field pulses, as they are wider than those of the rest of the sequence. The trailing edge of the first negative-going Frame Pulse (i.e. the rising edge of the first "serration" pulse) triggers the VSYNC output. In systems with a frame interval with no serration pulses, a vertical sync output is provided after a default delay as in **Figure 4**. Also provided is an **ODDFLD** logic output, which is high during an odd-numbered field and low during an even one.

The horizontal sync **HSYNC** is a monostable output derived from the leading (falling) edge of the composite sync. The pulse width is about 5 µs. Also, during the Field blanking sequence, the additional half-line pulses are removed by a timing circuit with a pulse interval discrimination function controlled by  $R_{SET}$ .  $R_{SET}$  is normally set to 681k $\Omega$  for standard PAL or NTSC timings. Consequently the scan rate is inversely proportional to  $R_{SET}$ .

The Back Porch monostable output **BKPCH** is initiated from the trailing edge of the composite sync. The pulse is active low and the width is set according to  $R_{SFT}$ .

#### Loss-of-Signal detector

Loss of signal is indicated by a logic high level at the output **NOSIG**. The decision threshold is set by an external resistor  $R_{NOSIG}$  connected from pin 2 to ground.  $R_{NOSIG}$  =100k $\Omega$  gives a shut off threshold of ~250mV of sync amplitude at FVIDIN or ~130mV on FILTIN (Threshold proportional to  $R_{NOSIG}$ , minimum value 82k $\Omega$ ) The table of connections above gives the equation used to determine a suitable resistor value. A waiting time of nominally 600 µs occurs before the loss of signal is flagged.

### Figure 2: NTSC TIMING DIAGRAM

Figure 4: VERTICAL SYNC DEFAULT

### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS (Cont.)**

### APPLICATIONS INFORMATION

#### General guidance

The ZXFV4583 is a high speed mixed analog/digital signal processing component requiring the appropriate care in the layout of the application printed circuit board. A continuous ground plane construction is preferred. Suitable power supply decoupling suggested includes a 100nF leadless ceramic capacitor close to the power supply connection at pin 14.

In order to avoid coupling between high speed logic output signals and analog inputs, the test circuit layout uses connections from the logic output pins routed away from the analog pins. In the application, similar care in the layout is required, keeping resistors,  $R_{FILT}, R_{NOSIG'}$  and  $R_{SET}$  close to their respective pins, in particular routing signal CSYNC away from pins 1, 2 and 12.

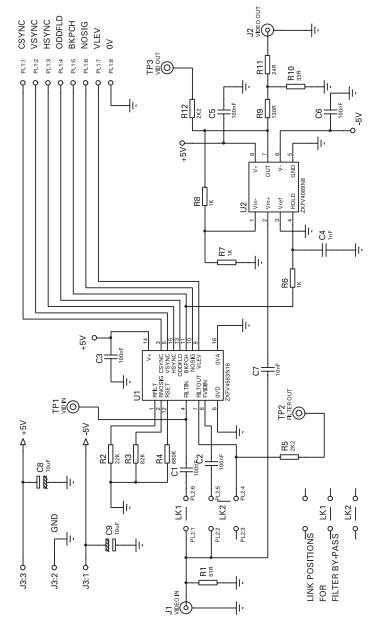

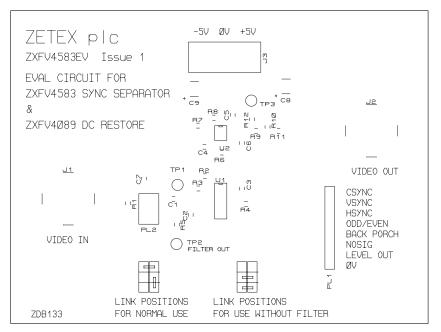

#### **Evaluation circuit**

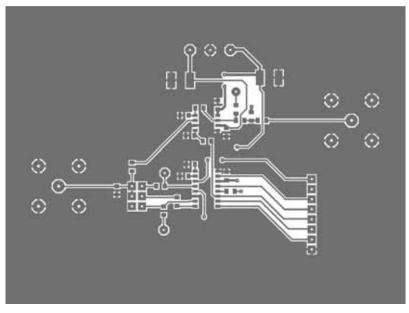

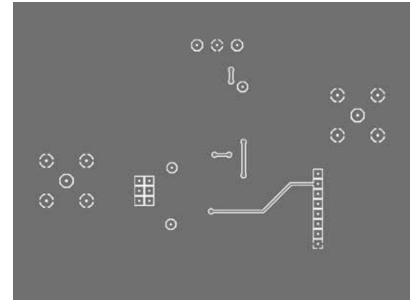

An evaluation circuit is available, designed to provide demonstration of the ZXFV4583 function using 50  $\Omega$  test instruments. The schematic diagram is shown in Figure 5 and the printed circuit layout is shown in Figures 6, 7 and 8. The circuit includes the Zetex ZXFV4089 DC Restoration Circuit, which is described in the data sheet for that part. The ZXFV4089 uses the Back Porch output from the ZXFV4583 in order to control and stabilize the black level of a video waveform.

BNC connector sockets allow connection of the analog video and output to laboratory test instruments via 50  $\Omega$  BNC cables. The circuit can be adapted for 75  $\Omega$  use. The output circuit includes a resistor matching circuit to present a load of 150  $\Omega$  to the amplifier and simultaneously provide 50  $\Omega$  output impedance. The attenuation of this matching circuit is 15.45 dB. As the amplifier is configured for a voltage gain of 2, the overall gain in a 50  $\Omega$  system is:

#### 6 - 15.45 = -9.45 dB.

The synchronized logic outputs are brought to a header for examination using oscilloscope probes. A set of jumper links allow the selection of operation with or without the built in color carrier filter. The selection is depicted on the board itself.

#### Parts List

| Parts List               |                       |               |                                                              |  |  |

|--------------------------|-----------------------|---------------|--------------------------------------------------------------|--|--|

| QTY                      | CCTREF                | VALUE         | DESCRIPTION                                                  |  |  |

| Resistors, surface mount |                       |               |                                                              |  |  |

| 1                        | R1                    | 51Ω           | 0805                                                         |  |  |

| 1                        | R2                    | 22k $\Omega$  | 0805                                                         |  |  |

| 1                        | R3                    | 82k $\Omega$  | 0805                                                         |  |  |

| 1                        | R4                    | 681k $\Omega$ | 0805                                                         |  |  |

| 2                        | R5, R12               | $2.2k\Omega$  | 0805                                                         |  |  |

| 3                        | R6, R7, R8            | 1kΩ           | 0805                                                         |  |  |

| 1                        | R9                    | 130Ω          | 0805                                                         |  |  |

| 1                        | R10                   | 33Ω           | 0805                                                         |  |  |

| 1                        | R11                   | 24Ω           | 0805                                                         |  |  |

| Capac                    | itors, surfac         | e mount       |                                                              |  |  |

| 5                        | C1, C2,<br>C3, C5, C6 | 100nF         | ceramic X7R 50V 0805                                         |  |  |

| 1                        | C4                    | 1nF           | ceramic NPO 50V 0805                                         |  |  |

| 1                        | C7                    | 10nF          | ceramic X7R 50V 0805                                         |  |  |

| 2                        | C8, C9                | 10µF          | tantalum elec 16V<br>size C                                  |  |  |

| Integr                   | ated circuits         |               |                                                              |  |  |

| 1                        | U1                    | -             | ZXFV4583N16 - Zetex                                          |  |  |

| 1                        | U2                    | -             | ZXFV4089N8 - Zetex                                           |  |  |

| Miscel                   | laneous               |               |                                                              |  |  |

| 2                        | J1, J2                | -             | Socket BNC PCB<br>straight flange e.g.<br>Tyco B35N14H999X99 |  |  |

| 1                        | 73                    | -             | Terminal block 3-way<br>IMO 20.501/3SB                       |  |  |

| 1                        | PL1                   | -             | Header 8 way single<br>row 2.54mm, Harwin<br>M20-9990805     |  |  |

| 1                        | PL2                   | -             | Header 8 way double<br>row 2.54mm, Harwin M                  |  |  |

| 3                        | TP1, TP2,<br>TP3      | -             | Test terminal, W.<br>Hughes 200-207                          |  |  |

| 2                        | LK1, LK2              | -             | Jumper Link, Harwin<br>M7567-05                              |  |  |

Figure 5: Evaluation circuit board schematic

Figure 6: Evaluation circuit layout: Top side

Figure 7: Evaluation circuit layout: Bottom side (viewed through board)

Figure 8: Evaluation circuit layout: Component layout

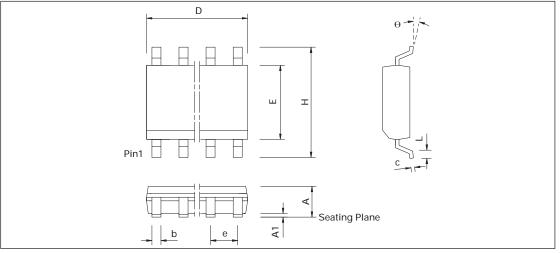

### PACKAGE OUTLINE

| DIM | Millim  | neters | Inches   |       |  |

|-----|---------|--------|----------|-------|--|

| DIN | MIN     | MAX    | MIN      | МАХ   |  |

| А   | 1.35    | 1.75   | 0.053    | 0.069 |  |

| A1  | 0.10    | 0.25   | 0.004    | 0.010 |  |

| b   | 0.33    | 0.51   | 0.013    | 0.020 |  |

| с   | 0.19    | 0.25   | 0.008    | 0.010 |  |

| D   | 9.80    | 10.00  | 0.386    | 0.394 |  |

| E   | 3.80    | 4.00   | 0.150    | 0.157 |  |

| е   | 1.27BSC |        | 0.050BSC |       |  |

| Н   | 5.80    | 6.20   | 0.228    | 0.244 |  |

| h   | 0.25    | 0.50   | 0.010    | 0.020 |  |

| L   | 0.40    | 1.27   | 0.016    | 0.050 |  |

| θ   | 0°      | 8°     | 0°       | 8°    |  |

Conforms to JEDEC MS-012AC Iss C (SO16N)

### © Zetex plc 2003

|                                                      | Americas                                                                         | Asia Pacific                                                                                                                                                                                                                        |

|------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zetex GmbH<br>Streitfeldstraße 19<br>D-81673 München | Zetex Inc<br>700 Veterans Memorial Hwy<br>Hauppauge, NY 11788                    | Zetex (Asia) Ltd<br>3701-04 Metroplaza Tower 1<br>Hing Fong Road<br>Kwai Fong                                                                                                                                                       |

| Germany                                              | USA                                                                              | Hong Kong                                                                                                                                                                                                                           |

| Fax: (49) 89 45 49 49 49                             | Fax: (1) 631 360 8222                                                            | Telephone: (852) 26100 611<br>Fax: (852) 24250 494<br>asia.sales@zetex.com                                                                                                                                                          |

|                                                      | Streitfeldstraße 19<br>D-81673 München<br>Germany<br>Telefon: (49) 89 45 49 49 0 | Zetex GmbH Zetex Inc   Streitfeldstraße 19 700 Veterans Memorial Hwy   D-81673 München Hauppauge, NY 11788   Germany USA   Telefon: (49) 89 45 49 49 0 Telephone: (1) 631 360 2222   Fax: (49) 89 45 49 49 49 Fax: (1) 631 360 8222 |

These offices are supported by agents and distributors in major countries world-wide.

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.

For the latest product information, log on to www.zetex.com