## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

August 1989 Revised August 2000

#### 100302

## Low Power Quint 2-Input OR/NOR Gate

#### **General Description**

The 100302 is a monolithic quint 2-input OR/NOR gate with common enable. All inputs have 50 k $\Omega$  pull-down resistors and all outputs are buffered.

#### **Features**

- 43% power reduction of the 100102

- 2000V ESD protection

- Pin/function compatible with 100102

- Voltage compensated operating range = -4.2V to -5.7V

- Available to industrial grade temperature range (PLCC package only)

#### **Ordering Code:**

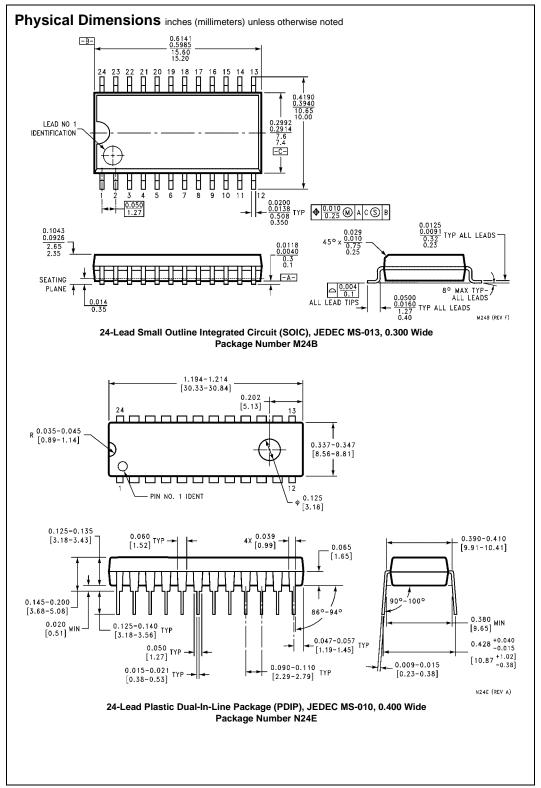

| Order Number | Package Number | Package Description                                                                                                |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| 100302SC     | M24B           | 24-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide                                          |

| 100302PC     | N24E           | 24-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-010, 0.400 Wide                                              |

| 100302QC     | V28A           | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square                                               |

| 100302QI     |                | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square Industrial Temperature Range (-40°C to +85°C) |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

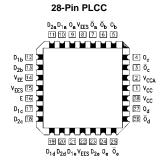

#### **Connection Diagrams**

#### **Pin Descriptions**

| Pin Names                           | Description                |

|-------------------------------------|----------------------------|

| D <sub>na</sub> -D <sub>ne</sub>    | Data Inputs                |

| E                                   | Enable Input               |

| O <sub>a</sub> -O <sub>e</sub>      | Data Outputs               |

| $\overline{O}_a$ – $\overline{O}_e$ | Complementary Data Outputs |

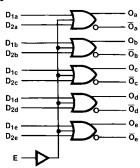

## Logic Symbol

### **Truth Table**

| D <sub>1X</sub> | D <sub>2X</sub> | E | o <sub>x</sub> | ō <sub>x</sub> |

|-----------------|-----------------|---|----------------|----------------|

| L               | L               | L | L              | Н              |

| L               | L               | Н | Н              | L              |

| L               | Н               | L | Н              | L              |

| L               | Н               | Н | Н              | L              |

| Н               | L               | L | Н              | L              |

| Н               | L               | Н | Н              | L              |

| Н               | Н               | L | Н              | L              |

| Н               | Н               | Н | Н              | L              |

H = HIGH Voltage Level

L = LOW Voltage Level

#### **Absolute Maximum Ratings**(Note 1)

## Recommended Operating Conditions

Case Temperature (T<sub>C</sub>)

$\begin{array}{ccc} \text{Commercial} & 0^{\circ}\text{C to } +85^{\circ}\text{C} \\ \text{Industrial} & -40^{\circ}\text{C to } +85^{\circ}\text{C} \\ \text{Supply Voltage (V}_{\text{EE}}) & -5.7\text{V to } -4.2\text{V} \end{array}$

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum rating. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

#### **Commercial Version**

#### **DC Electrical Characteristics** (Note 3)

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = 0$ °C to +85°C

| Symbol           | Parameter            | Min   | Тур   | Max   | Units | Conditions                              |              |  |

|------------------|----------------------|-------|-------|-------|-------|-----------------------------------------|--------------|--|

| V <sub>OH</sub>  | Output HIGH Voltage  | -1025 | -955  | -870  | mV    | $V_{IN} = V_{IH(Max)}$ or $V_{IL(Min)}$ | Loading with |  |

| V <sub>OL</sub>  | Output LOW Voltage   | -1830 | -1705 | -1620 | mV    | VIN - VIH(Max) OI VIL(Min)              | 50Ω to −2.0V |  |

| V <sub>OHC</sub> | Output HIGH Voltage  | -1035 |       |       | mV    | V V Or V                                | Loading with |  |

| V <sub>OLC</sub> | Output LOW Voltage   |       |       | -1610 | mV    | $V_{IN} = V_{IH(Min)}$ or $V_{IL(Max)}$ | 50Ω to –2.0V |  |

| V <sub>IH</sub>  | Input HIGH Voltage   | -1165 |       | -870  | mV    | Guaranteed HIGH Signal for All Inputs   |              |  |

| V <sub>IL</sub>  | Input LOW Voltage    | -1830 |       | -1475 | mV    | Guaranteed LOW Signal for All Inputs    |              |  |

| I <sub>IL</sub>  | Input LOW Current    | 0.50  |       |       | μΑ    | $V_{IN} = V_{IL(Min)}$                  |              |  |

| I <sub>IH</sub>  | Input HIGH Current   |       |       | 240   | μΑ    | $V_{IN} = V_{IH(Max)}$                  |              |  |

| I <sub>EE</sub>  | Power Supply Current | -45   | -36   | -20   | mA    | Inputs OPEN                             |              |  |

**Note 3:** The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

#### **DIP AC Electrical Characteristics**

$\rm V_{EE} = -4.2V$  to  $-5.7V,~V_{CC} = V_{CCA} = GND$

| Symbol           | Parameter              | $T_C = 0^{\circ}C$ |      | $T_C = +25^{\circ}C$ |      | T <sub>C</sub> = +85°C |      | Units | Conditions    |

|------------------|------------------------|--------------------|------|----------------------|------|------------------------|------|-------|---------------|

| - Cymbol         |                        | Min                | Max  | Min                  | Max  | Min                    | Max  | 0     | Conditions    |

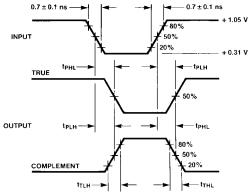

| t <sub>PLH</sub> | Propagation Delay      | 0.50               | 1.15 | 0.50                 | 1.15 | 0.50                   | 1.25 | ns    |               |

| t <sub>PHL</sub> | Data to Output         | 0.50               | 1.15 | 0.50                 | 1.15 | 0.50                   | 1.25 | 115   | Figures 1, 2  |

| t <sub>PLH</sub> | Propagation Delay      | 0.70               | 1.90 | 0.70                 | 1.90 | 0.80                   | 2.00 | ns    | (Note 4)      |

| t <sub>PHL</sub> | Enable to Output       | 0.70               | 1.50 | 0.70                 | 1.50 | 0.00                   | 2.00 | 110   |               |

| t <sub>TLH</sub> | Transition Time        | 0.40               | 1.20 | 0.40                 | 1.20 | 0.40                   | 1.20 | ns    | Figures 1, 2  |

| t <sub>THL</sub> | 20% to 80%, 80% to 20% | 0.40               | 1.20 | 0.40                 | 1.20 | 0.40                   | 1.20 | 115   | i iguies i, 2 |

Note 4: The propagation delay specified is for single output switching. Delays may vary up to 100 ps with multiple outputs switching.

## Commercial Version (Continued) SOIC and PLCC AC Electrical Characteristics

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$

| Symbol            | Parameter                         | T <sub>C</sub> = 0°C |      | $T_C = +25^{\circ}C$ |      | $T_C = +85^{\circ}C$ |      | Units  | Conditions   |  |

|-------------------|-----------------------------------|----------------------|------|----------------------|------|----------------------|------|--------|--------------|--|

| Syllibol          |                                   | Min                  | Max  | Min                  | Max  | Min                  | Max  | Ullits | Conditions   |  |

| t <sub>PLH</sub>  | Propagation Delay                 | 0.50                 | 1.05 | 0.50                 | 1.05 | 0.50                 | 1.15 |        |              |  |

| t <sub>PHL</sub>  | Data to Output                    | 0.50                 | 1.05 | 0.50                 | 1.05 | 0.50                 | 1.15 | ns     | Figures 1, 2 |  |

| t <sub>PLH</sub>  | Propagation Delay                 | 0.70                 | 1.80 | 0.70                 | 1.80 | 0.80                 | 1.90 | 200    | (Note 5)     |  |

| t <sub>PHL</sub>  | Enable to Output                  | 0.70                 | 1.00 | 0.70                 | 1.00 | 0.60                 | 1.90 | ns     |              |  |

| t <sub>TLH</sub>  | Transition Time                   | 0.40                 | 1.10 | 0.40                 | 1.10 | 0.40                 | 1.10 | ns     | Figures 1, 2 |  |

| t <sub>THL</sub>  | 20% to 80%, 80% to 20%            | 0.40                 | 1.10 | 0.40                 | 1.10 | 0.40                 | 1.10 | 115    | rigules 1, 2 |  |

| t <sub>OSHL</sub> | Maximum Skew Common Edge          |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 250  |                      | 250  |                      | 250  | ps     | (Note 6)     |  |

|                   | Data to Output Path               |                      |      |                      |      |                      |      |        |              |  |

| t <sub>OSHL</sub> | Maximum Skew Common Edge          |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 310  |                      | 310  |                      | 310  | ps     | (Note 6)     |  |

|                   | Enable to Output Path             |                      |      |                      |      |                      |      |        |              |  |

| t <sub>OSLH</sub> | Maximum Skew Common Edge          |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 200  |                      | 200  |                      | 200  | ps     | (Note 6)     |  |

|                   | Data to Output Path               |                      |      |                      |      |                      |      |        |              |  |

| t <sub>OSLH</sub> | Maximum Skew Common Edge          |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 330  |                      | 330  |                      | 330  | ps     | (Note 6)     |  |

|                   | Enable to Output Path             |                      |      |                      |      |                      |      |        |              |  |

| t <sub>OST</sub>  | Maximum Skew Opposite Edge        |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 250  |                      | 250  |                      | 250  | ps     | (Note 6)     |  |

|                   | Data to Output Path               |                      |      |                      |      |                      |      |        |              |  |

| t <sub>OST</sub>  | Maximum Skew Opposite Edge        |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Output-to-Output Variation        |                      | 330  |                      | 330  |                      | 330  | ps     | ((Note 6)    |  |

|                   | Enable to Output Path             |                      |      |                      |      |                      |      |        |              |  |

| t <sub>PS</sub>   | Maximum Skew                      |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Pin (Signal) Transition Variation |                      | 200  |                      | 200  |                      | 200  | ps     | (Note 6)     |  |

|                   | Data to Output Path               |                      |      |                      |      |                      |      |        |              |  |

| t <sub>PS</sub>   | Maximum Skew                      |                      |      |                      |      |                      |      |        | PLCC Only    |  |

|                   | Pin (Signal) Transition Variation |                      | 280  |                      | 280  |                      | 280  | ps     | (Note 6)     |  |

|                   | Enable to Output Path             |                      |      |                      |      |                      |      |        |              |  |

Note 5: The propagation delay specified is for single output switching. Delays may vary up to 100 ps with multiple outputs switching.

Note 6: Output-to-Output Skew is defined as the absolute value of the difference between the actual propagation delay for any outputs within the same packaged device. The specifications apply to any outputs switching in the same direction either HIGH-to-LOW (t<sub>OSHL</sub>), or LOW-to-HIGH (t<sub>OSLH</sub>), or in opposite directions both HL and LH (t<sub>OST</sub>). Parameters t<sub>OST</sub> and t<sub>PS</sub> guaranteed by design.

#### **Industrial Version**

#### PLCC DC Electrical Characteristics (Note 7)

$V_{EE} = -4.2V$  to -5.7V,  $V_{CC} = V_{CCA} = GND$ ,  $T_{C} = -40^{\circ}C$  to  $+85^{\circ}C$

| Symbol           | T <sub>C</sub> = -40°0 |       | -40°C | T <sub>C</sub> = 0°C | to +85°C | Units | Conditions                 |                       |

|------------------|------------------------|-------|-------|----------------------|----------|-------|----------------------------|-----------------------|

| Cymbol           | r arameter             | Min   | Max   | Min                  | Max      | Omits | Conditions                 | •                     |

| V <sub>OH</sub>  | Output HIGH Voltage    | -1085 | -870  | -1025                | -870     | mV    | $V_{IN} = V_{IH(Max)}$     | Loading with          |

| V <sub>OL</sub>  | Output LOW Voltage     | -1830 | -1575 | -1830                | -1620    | 1110  | or V <sub>IL(Min)</sub>    | $50\Omega$ to $-2.0V$ |

| V <sub>OHC</sub> | Output HIGH Voltage    | -1095 |       | -1035                |          | mV    | $V_{IN} = V_{IH(Min)}$     | Loading with          |

| V <sub>OLC</sub> | Output LOW Voltage     |       | -1565 |                      | -1610    | IIIV  | or V <sub>IL(Max)</sub>    | $50\Omega$ to $-2.0V$ |

| V <sub>IH</sub>  | Input HIGH Voltage     | -1170 | -870  | -1165                | -870     | mV    | Guaranteed HIGH Signal for | or ALL Inputs         |

| V <sub>IL</sub>  | Input LOW Voltage      | -1830 | -1480 | -1830                | -1475    | mV    | Guaranteed LOW Signal for  | or ALL Inputs         |

| I <sub>IL</sub>  | Input LOW Current      | 0.05  |       | 0.05                 |          | μΑ    | $V_{IN} = V_{IL(Min)}$     |                       |

| I <sub>IH</sub>  | Input HIGH Current     |       | 300   |                      | 240      | μΑ    | $V_{IN} = V_{IH(Max)}$     |                       |

| I <sub>EE</sub>  | Power Supply Current   | -45   | -20   | -45                  | -20      | mA    | Inputs OPEN                |                       |

Note 7: The specified limits represent the "worst case" value for the parameter. Since these values normally occur at the temperature extremes, additional noise immunity and guardbanding can be achieved by decreasing the allowable system operating ranges. Conditions for testing shown in the tables are chosen to guarantee operation under the "worst case" conditions.

#### **PLCC AC Electrical Characteristics**

$\rm V_{EE} = -4.2V$  to  $-5.7V,~V_{CC} = V_{CCA} = GND$

| Symbol           | Parameter              | $T_C = -40^{\circ}C$ |      | T <sub>C</sub> = +25°C |      | $T_C = +85^{\circ}C$ |      | Units  | Conditions     |

|------------------|------------------------|----------------------|------|------------------------|------|----------------------|------|--------|----------------|

| - Cymbol         | T didilictor           | Min                  | Max  | Min                    | Max  | Min                  | Max  | Oilles | Conditions     |

| t <sub>PLH</sub> | Propagation Delay      | 0.40                 | 1.05 | 0.50                   | 1.05 | 0.50                 | 1.15 | ns     |                |

| t <sub>PHL</sub> | Data to Output         | 0.40                 | 1.00 | 0.50                   | 1.00 | 0.50                 | 1.15 | 113    | Figures 1, 2   |

| t <sub>PLH</sub> | Propagation Delay      | 0.70                 | 1.80 | 0.70                   | 1.80 | 0.80                 | 1.90 | ns     | (Note 8)       |

| t <sub>PHL</sub> | Enable to Output       | 0.70                 | 1.00 | 0.70                   | 1.00 | 0.00                 | 1.90 | 115    |                |

| t <sub>TLH</sub> | Transition Time        | 0.30                 | 1.10 | 0.40                   | 1.10 | 0.40                 | 1.10 | ns     | Figures 1, 2   |

| t <sub>THL</sub> | 20% to 80%, 80% to 20% | 0.50                 | 1.10 | 0.40                   | 1.10 | 0.40                 | 1.10 | 115    | 1 igui 65 1, 2 |

Note 8: The propagation delay specified is for single output switching. Delays may vary up to 200 ps with multiple outputs switching.

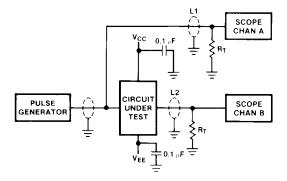

## **Test Circuitry**

#### Notes:

$V_{CC},\,V_{CCA}=+2V,\,V_{EE}=-2.5V$

L1 and L2 = equal length  $50\Omega$  impedance lines

$R_T = 50\Omega$  terminator internal to scope

Decoupling 0.1  $\mu\text{F}$  from GND to  $V_{\text{CC}}$  and  $V_{\text{EE}}$

All unused outputs are loaded with  $50\Omega$  to GND

$C_L = \mbox{Fixture}$  and stray capacitance  $\leq 3 \mbox{ pF}$

FIGURE 1. AC Test Circuit

### **Switching Waveforms**

FIGURE 2. Propagation Delay and Transition Times

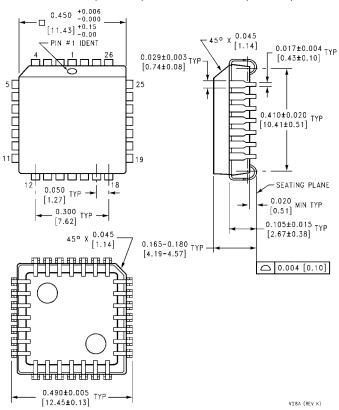

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450 Square Package Number V28A

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com