## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

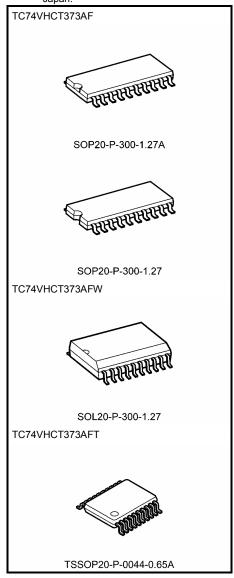

## TC74VHCT373AF,TC74VHCT373AFW,TC74VHCT373AFT

#### Octal D-Type Latch with 3-State Output

The TC74VHCT373A is an advanced high speed CMOS OCTAL LATCH with 3-STATE OUTPUT fabricated with silicon gate  $C^2MOS$  technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

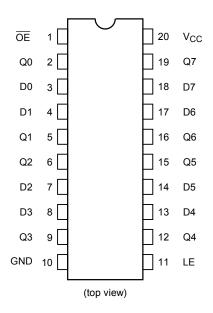

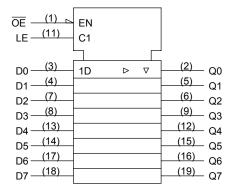

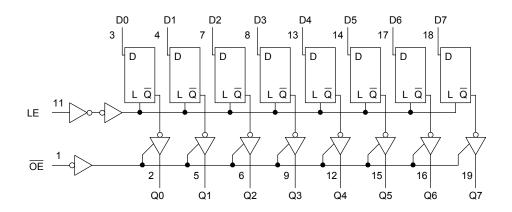

This 8-bit D-type latch is controlled by a latch enable input (LE) and a output enable input ( $\overline{OE}$ ).

When the  $\overline{OE}$  input is high, the eight outputs are in a high impedance state.

The input voltage are compatible with TTL output voltage. This device may be used as a level converter for interfacing  $3.3\ V$  to  $5\ V$  system.

Input protection and output circuit ensure that 0 to 5.5 V can be applied to the input and output  $^{\rm (Note)}$  pins without regard to the supply voltage. These structure prevents device destruction due to mismatched supply and input/output voltages such as battery back up, hot board insertion, etc.

Note: Output in off-state

#### **Features**

- High speed:  $t_{pd} = 7.7$  ns (typ.) at  $V_{CC} = 5$  V

- Low power dissipation:  $ICC = 4 \mu A \text{ (max)}$  at  $Ta = 25^{\circ}C$

- Power down protection is provided on all inputs and outputs.

- Balanced propagation delays: t<sub>p</sub>LH ≃ t<sub>p</sub>HL

- Low noise: VOLP = 1.6 V (max)

- Pin and function compatible with the 74 series (74AC/HC/F/ALS/LS etc.) 373 type.

Note: xxxFW (JEDEC SOP) is not available in Japan.

Weight

SOP20-P-300-1.27A

: 0.22 g (typ.)

SOP20-P-300-1.27

: 0.22 g (typ.)

SOL20-P-300-1.27

: 0.46 g (typ.)

TSSOP20-P-0044-0.65A

: 0.08 g (typ.)

## **Pin Assignment**

## **IEC Logic Symbol**

#### **Truth Table**

|    | Inputs |   | Output         |

|----|--------|---|----------------|

| ŌE | LE     | D | Output         |

| Н  | Х      | Х | Z              |

| L  | L      | Х | Q <sub>n</sub> |

| L  | Н      | L | L              |

| L  | Н      | Н | Н              |

X: Don't care

Z: High impedance

$\mathsf{Q}_{\mathsf{n}} . \, \mathsf{Q}$  outputs are latched at the time when the LE input is taken to a low logic level.

#### **System Diagram**

#### **Absolute Maximum Ratings (Note 1)**

| Characteristics                    | Symbol           | Rating                                 | Unit |

|------------------------------------|------------------|----------------------------------------|------|

| Supply voltage range               | V <sub>CC</sub>  | −0.5 to 7.0                            | V    |

| DC input voltage                   | V <sub>IN</sub>  | -0.5 to 7.0                            | V    |

| DC output voltage                  | \/a              | -0.5 to 7.0 (Note 2)                   | V    |

| DC output voltage                  | V <sub>OUT</sub> | -0.5 to V <sub>CC</sub> + 0.5 (Note 3) | V    |

| Input diode current                | I <sub>IK</sub>  | -20                                    | mA   |

| Output diode current               | lok              | ±20 (Note 4)                           | mA   |

| DC output current                  | lout             | ±25                                    | mA   |

| DC V <sub>CC</sub> /ground current | Icc              | ±75                                    | mA   |

| Power dissipation                  | $P_{D}$          | 180                                    | mW   |

| Storage temperature                | T <sub>stg</sub> | −65 to 150                             | °C   |

Note 1: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or even destruction.

Note 2: Output in off-state

Note 3: High or low state.  $I_{\mbox{OUT}}$  absolute maximum rating must be observed.

Note 4:  $V_{OUT} < GND$ ,  $V_{OUT} > V_{CC}$

## **Recommended Operating Conditions (Note 1)**

| Characteristics          | Symbol           | Rating                        | Unit |

|--------------------------|------------------|-------------------------------|------|

| Supply voltage           | V <sub>CC</sub>  | 4.5 to 5.5                    | V    |

| Input voltage            | V <sub>IN</sub>  | 0 to 5.5                      | V    |

| Output voltage           | V <sub>OUT</sub> | 0 to 5.5 (Note 2)             | V    |

| Output voltage           | VOU1             | 0 to V <sub>CC</sub> (Note 3) |      |

| Operating temperature    | T <sub>opr</sub> | −40 to 85                     | °C   |

| Input rise and fall time | dt/dV            | 0 to 20                       | ns/V |

Note 1: The recommended operating conditions are required to ensure the normal operation of the device.

Unused inputs must be tied to either VCC or GND.

3

Note 2: Output in off-state

Note 3: High or low state

## **Electrical Characteristics**

#### **DC Characteristics**

| Characteristics                  | Symbol           |                                                                                                   | Test Condition                           |                     | Ta = 25°C |      |       | Ta =<br>-40 to 85°C |       | Unit |

|----------------------------------|------------------|---------------------------------------------------------------------------------------------------|------------------------------------------|---------------------|-----------|------|-------|---------------------|-------|------|

|                                  |                  |                                                                                                   |                                          | V <sub>CC</sub> (V) | Min       | Тур. | Max   | Min                 | Max   |      |

| High-level input voltage         | V <sub>IH</sub>  | _                                                                                                 |                                          | 4.5 to 5.5          | 2.0       | _    | -     | 2.0                 | _     | V    |

| Low-level input voltage          | V <sub>IL</sub>  |                                                                                                   | _                                        | 4.5 to 5.5          | _         | _    | 0.8   | _                   | 0.8   | V    |

| High-level output                | \/               | V <sub>IN</sub>                                                                                   | I <sub>OH</sub> = -50 μA                 | 4.5                 | 4.40      | 4.50 | _     | 4.40                | _     | V    |

| voltage                          | Voн              | = V <sub>IH</sub> or<br>V <sub>IL</sub>                                                           | I <sub>OH</sub> = -8 mA                  | 4.5                 | 3.94      | _    | -     | 3.80                | _     |      |

| Low-level output voltage         |                  | V <sub>IN</sub><br>= V <sub>IH</sub> or<br>V <sub>IL</sub>                                        | I <sub>OL</sub> = 50 μA                  | 4.5                 | _         | 0.0  | 0.1   | _                   | 0.1   | ٧    |

|                                  | V <sub>OL</sub>  |                                                                                                   | I <sub>OL</sub> = 8 mA                   | 4.5                 | 1         | _    | 0.36  | _                   | 0.44  |      |

| 3-state output off-state current | I <sub>OZ</sub>  | V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub><br>V <sub>OUT</sub> = V <sub>CC</sub> or GND |                                          | 5.5                 | _         | _    | ±0.25 | _                   | ±2.50 | μΑ   |

| Input leakage current            | I <sub>IN</sub>  | V <sub>IN</sub> = 5.5 V or GND                                                                    |                                          | 0 to 5.5            | _         | _    | ±0.1  | _                   | ±1.0  | μΑ   |

|                                  | Icc              | V <sub>IN</sub> = V <sub>C</sub>                                                                  | V <sub>IN</sub> = V <sub>CC</sub> or GND |                     | _         | _    | 4.0   | _                   | 40.0  | μA   |

| Quiescent supply current         | Ісст             | Per input: V <sub>IN</sub> = 3.4 V Other input: V <sub>CC</sub> or GND                            |                                          | 5.5                 | _         | _    | 1.35  | _                   | 1.50  | mA   |

| Output leakage current           | I <sub>OPD</sub> | V <sub>OUT</sub> = 5                                                                              | 5.5 V                                    | 0                   |           |      | 0.5   |                     | 5.0   | μΑ   |

## Timing Requirements (input: $t_r = t_f = 3 \text{ ns}$ )

| Characteristics          | Symbol             | Test Condition |                     | Ta = 25°C |       | Ta =<br>-40 to<br>85°C | Unit |

|--------------------------|--------------------|----------------|---------------------|-----------|-------|------------------------|------|

|                          |                    |                | V <sub>CC</sub> (V) | Тур.      | Limit | Limit                  |      |

| Minimum pulse width (LE) | t <sub>w (H)</sub> | _              | 5.0 ± 0.5           | _         | 6.5   | 8.5                    | ns   |

| Minimum set-up time      | ts                 | _              | 5.0 ± 0.5           | _         | 1.5   | 1.5                    | ns   |

| Minimum hold time        | t <sub>h</sub>     | _              | 5.0 ± 0.5           | _         | 3.5   | 3.5                    | ns   |

4

#### AC Characteristics (input: $t_r = t_f = 3$ ns)

| Characteristics               | Symbol            | Test Condition        |                     |                     | Ta = 25°C |      |      | Ta =<br>-40 to 85°C |      | Unit |

|-------------------------------|-------------------|-----------------------|---------------------|---------------------|-----------|------|------|---------------------|------|------|

|                               |                   |                       | V <sub>CC</sub> (V) | C <sub>L</sub> (pF) | Min       | Тур. | Max  | Min                 | Max  |      |

| Propagation delay time        | t <sub>pLH</sub>  | _                     | 5.0 ± 0.5           | 15                  | _         | 7.7  | 12.3 | 1.0                 | 13.5 | ns   |

| (LE-Q)                        | $t_{pHL}$         |                       | 0.0 2 0.0           | 50                  |           | 8.5  | 13.3 | 1.0                 | 14.5 | 113  |

| Propagation delay time        | t <sub>pLH</sub>  | _                     | 5.0 ± 0.5           | 15                  | 1         | 5.1  | 8.5  | 1.0                 | 9.5  | ns   |

| (D-Q)                         | $t_{pHL}$         | _                     | 5.0 ± 0.5           | 50                  | _         | 5.9  | 9.5  | 1.0                 | 10.5 |      |

| 3-state output enable         | t <sub>pZL</sub>  | R <sub>L</sub> = 1 kΩ | 5.0 ± 0.5           | 15                  |           | 6.3  | 10.9 | 1.0                 | 12.5 | ns   |

| time                          | <sup>t</sup> pZH  |                       |                     | 50                  | 1         | 7.1  | 11.9 | 1.0                 | 13.5 |      |

| 3-state output disable time   | t <sub>pLZ</sub>  | R <sub>L</sub> = 1 kΩ | 5.0 ± 0.5           | 50                  | _         | 8.8  | 11.2 | 1.0                 | 12.0 | ns   |

| Output to output skew         | t <sub>osLH</sub> | (Note 1)              | 5.0 ± 0.5           | 50                  | _         | _    | 1.0  | _                   | 1.0  | ns   |

| Input capacitance             | C <sub>IN</sub>   |                       | _                   |                     | _         | 4    | 10   | _                   | 10   | pF   |

| Output capacitance            | C <sub>OUT</sub>  |                       | _                   |                     | _         | 9    | _    | _                   | _    | pF   |

| Power dissipation capacitance | C <sub>PD</sub>   |                       |                     | (Note 2)            | -         | 25   | -    | _                   | _    | pF   |

Note 1: Parameter guaranteed by design.

$t_{OSLH} = |t_{DLHm} - t_{DLHn}|, t_{OSHL} = |t_{DHLm} - t_{DHLn}|$

Note 2: C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Average operating current can be obtained by the equation:

$$I_{CC (opr)} = C_{PD} \cdot V_{CC} \cdot f_{IN} + I_{CC}/8 (per latch)$$

And the total C<sub>PD</sub> when n pcs. of latch operate can be gained by the following equation:

$C_{PD}$  (total) = 14 + 11·n

#### Noise Characteristics (input: $t_r = t_f = 3$ ns) (Note)

| Characteristics                              | Symbol           | Test Condition         |                     | Ta = 25°C |        | Unit |

|----------------------------------------------|------------------|------------------------|---------------------|-----------|--------|------|

| Gharacteristics                              | Symbol           |                        | V <sub>CC</sub> (V) | Тур.      | Max    | Oill |

| Quiet output maximum dynamia V               | V                | 0 50 75                | 5.0                 | 1.1       | 1.5    | V    |

| Quiet output maximum dynamic V <sub>OL</sub> | V <sub>OLP</sub> | C <sub>L</sub> = 50 pF |                     | (1.2)     | (1.6)  |      |

| Quiet output minimum dynamic V               | V <sub>OLV</sub> | C <sub>L</sub> = 50 pF | 5.0                 | -1.1      | -1.5   | V    |

| Quiet output minimum dynamic V <sub>OL</sub> |                  |                        |                     | (-1.2)    | (-1.6) |      |

| Minimum high level dynamic input voltage     | V <sub>IHD</sub> | C <sub>L</sub> = 50 pF | 5.0                 | _         | 2.0    | V    |

| Maximum low level dynamic input voltage      | V <sub>ILD</sub> | C <sub>L</sub> = 50 pF | 5.0                 | -         | 0.8    | ٧    |

5

Note: The value in ( ) only applies to JEDEC SOP (FW) devices.

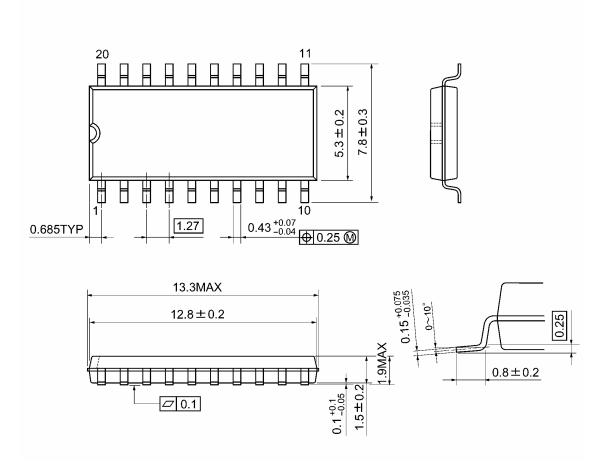

## **Package Dimensions**

SOP20-P-300-1.27A Unit: mm

Weight: 0.22 g (typ.)

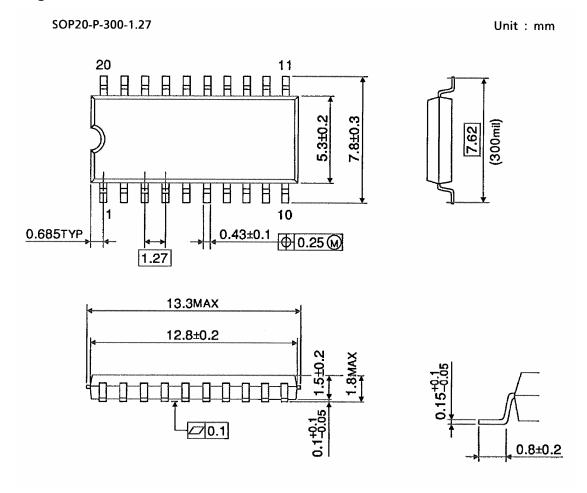

## **Package Dimensions**

7

Weight: 0.22 g (typ.)

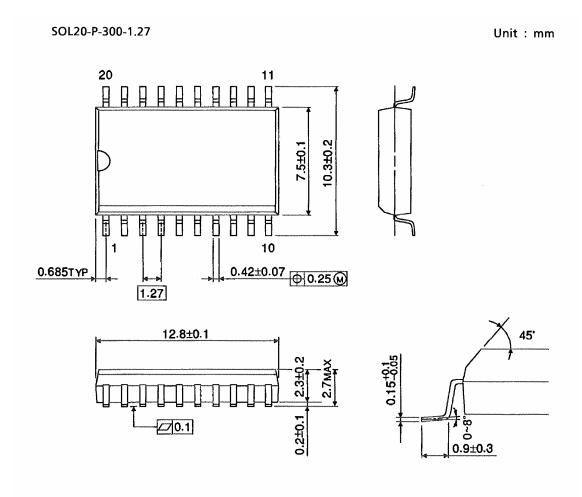

## **Package Dimensions (Note)**

8

Note: This package is not available in Japan.

Weight: 0.46 g (typ.)

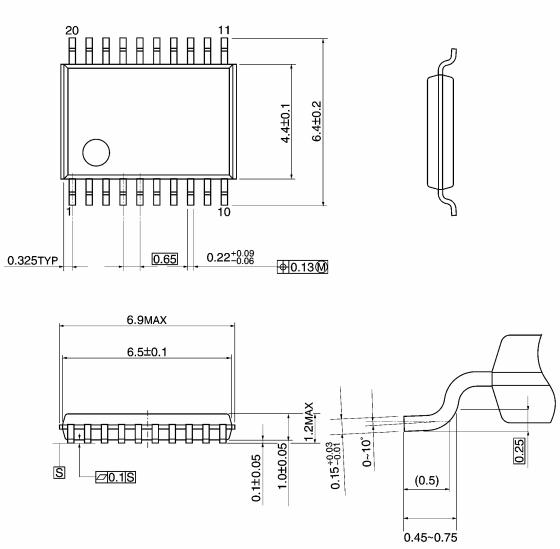

## **Package Dimensions**

TSSOP20-P-0044-0.65A Unit: mm

Weight: 0.08 g (typ.)

Note: Lead (Pb)-Free Packages

SOP20-P-300-1.27A TSSOP20-P-0044-0.65A

#### **RESTRICTIONS ON PRODUCT USE**

060116EBA

- The information contained herein is subject to change without notice. 021023\_D

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc. 021023\_A

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk. 021023 B

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations. 060106\_Q

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others. 021023\_c

10

The products described in this document are subject to the foreign exchange and foreign trade laws. 021023\_E