# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# 32-Channel Serial to Parallel Converter With High Voltage Push-Pull Outputs

#### **Features**

- Processed with HVCMOS® technology

- Low power level shifting

- Shift register speed 8.0MHz

- Latched data outputs

- 5.0V CMOS compatible inputs

- Forward and reverse shifting options

- ▶ Diode to V<sub>PP</sub> allows efficient power recovery

#### **General Description**

The HV9408 is a low voltage serial to high voltage parallel converters with push-pull outputs. This device has been designed for use as a driver for AC-electroluminescent displays. It can also be used in any application requiring multiple output, high voltage current sourcing and sinking capabilities such as driving plasma panels, vacuum fluorescent, or large matrix LCD displays.

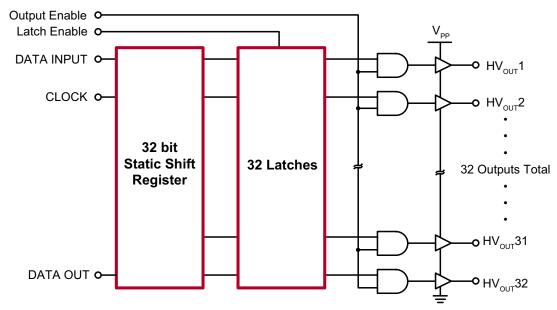

These devices consist of a 32-bit shift register, 32 latches, and control logic to enable outputs.  $HV_{OUT}1$  is connected to the first stage of the shift register through the Output Enable logic. Data is shifted through the shift register on the low to high transition of the clock. The HV9408 shifts in the counter-clockwise direction when viewed from the top of the package. A data output buffer is provided for cascading devices. This output reflects the current status of the last bit of the shift register (32). Operation of the shift register is not affected by the LE (latch enable) or the OE (output enable) inputs. Transfer of data from the shift register to the latch occurs when the LE input is high. The data in the latch is retained when LE is low.

### **Block Diagram**

#### **Ordering Information**

|        | Package Options                     |

|--------|-------------------------------------|

|        | 44-Lead Quad                        |

| Device | Plastic Chip Carrier                |

|        | .653x.653in body                    |

|        | .180in height (max)<br>.050in pitch |

|        | .osom piten                         |

| HV9408 | HV9408PJ-G                          |

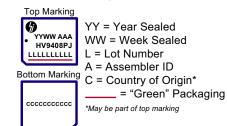

-G indicates package is RoHS compliant ('Green')

### **Absolute Maximum Ratings**

| Parameter                                       | Value                          |

|-------------------------------------------------|--------------------------------|

| Supply voltage, V <sub>DD</sub>                 | -0.5V to +7.0V                 |

| Supply voltage, V <sub>PP</sub>                 | -0.5V to +90V                  |

| Logic input levels                              | -0.5V to V <sub>DD</sub> +0.5V |

| Ground current <sup>1</sup>                     | 1.5A                           |

| Continuous total power dissipation <sup>2</sup> | 1200W                          |

| Operating temperature range                     | -40 to +85°C                   |

| Storage temperature range                       | -65 to +150°C                  |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### Notes:

- Duty cycle is limited by the total power dissipated in the package.

- For operation above 25°C ambient derate linearly to maximum operatin temperature at 20mW/°C.

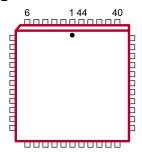

#### **Pin Configurations**

44-Lead Quad Plastic Chip Carrier (PJ)

#### **Product Marking**

Package may or may not include the following marks: Si or

44-Lead Quad Plastic Chip Carrier (PJ)

## **Recommended Operating Conditions**

| Sym              | Parameter                      | Min                   | Max             | Units |

|------------------|--------------------------------|-----------------------|-----------------|-------|

| V <sub>DD</sub>  | Logic voltage supply           | 4.5                   | 5.5             | V     |

| $V_{pp}$         | High voltage supply            | 8.0                   | 80              | V     |

| V <sub>IH</sub>  | Input high voltage             | V <sub>DD</sub> - 0.5 | V <sub>DD</sub> | V     |

| V <sub>IL</sub>  | Input low voltage              | 0                     | 0.5             | V     |

| f <sub>CLK</sub> | Clock frequency                | 0                     | 8.0             | MHz   |

| T <sub>A</sub>   | Operating free-air temperature | -40                   | +85             | °C    |

#### **Electrical Characteristics** $(V_{PP} = 60V, V_{DD} = 5.0V, T_A = 25^{\circ}C)$ **DC Characteristics**

| Sym                    | Parameter                                  | Min                  | Max  | Units | Conditions                                               |

|------------------------|--------------------------------------------|----------------------|------|-------|----------------------------------------------------------|

| l <sub>PP</sub>        | V <sub>PP</sub> supply current             | -                    | 100  | μA    | HV <sub>OUTPUTS</sub> high to low                        |

| I <sub>DDQ</sub>       | I <sub>DD</sub> supply current (quiescent) | -                    | 100  | μA    | All inputs = V <sub>DD</sub> or GND                      |

| I <sub>DD</sub>        | I <sub>DD</sub> supply current (operating) | -                    | 15   | mA    | $V_{DD} = V_{DD} \text{ max}, f_{CLK} = 8.0 \text{ MHz}$ |

| V <sub>OH</sub> (Data) | Shift register output voltage              | V <sub>DD</sub> -0.5 | -    | V     | I <sub>o</sub> = -100μA                                  |

| V <sub>OL</sub> (Data) | Shift register output voltage              | -                    | 0.5  | V     | Ι <sub>ο</sub> = 100μΑ                                   |

| I <sub>IH</sub>        | Current leakage, any input                 | -                    | 1.0  | μA    | Input = V <sub>DD</sub>                                  |

| I <sub>IL</sub>        | Current leakage, any input                 | -                    | -1.0 | μA    | Input = GND                                              |

| V <sub>oc</sub>        | HV output clamp diode voltage              | -                    | -1.5 | V     | I <sub>oc</sub> = -5.0mA                                 |

| V <sub>OH</sub>        | HV output when sourcing                    | 52                   | -    | V     | I <sub>OH</sub> = -20mA, 0 to 70°C                       |

| V <sub>OL</sub>        | HV output when sinking                     | -                    | 4.0  | V     | I <sub>OL</sub> = 5.0mA, 0 to 70°C                       |

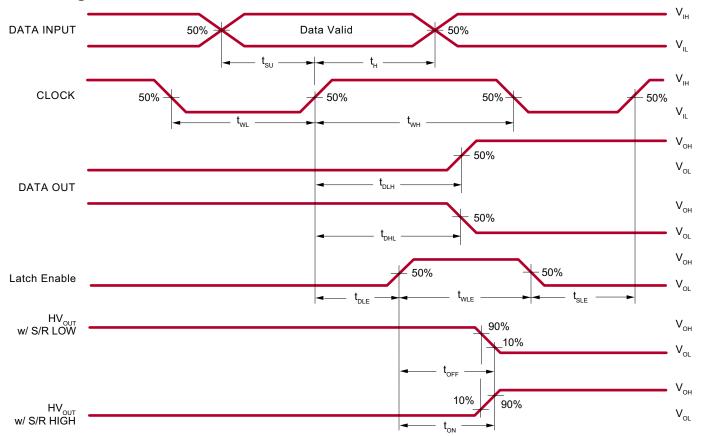

#### **AC Characteristics**

| Sym                                                        | Parameter                                   |    | Max | Units | Conditions |

|------------------------------------------------------------|---------------------------------------------|----|-----|-------|------------|

| f <sub>CLK</sub>                                           | Clock frequency                             | -  | 8.0 | MHz   |            |

| $t_{\scriptscriptstyle WL}$ or $t_{\scriptscriptstyle WH}$ | Clock width, high or low                    | 62 | -   | ns    |            |

| t <sub>su</sub>                                            | Setup time before CLK rises                 | 25 | -   | ns    |            |

| t <sub>H</sub>                                             | Hold time after CLK rises                   | 10 | -   | ns    |            |

| t <sub>DLH</sub> (Data)                                    | Data output delay after L to H CLK          | -  | 110 | ns    | CL = 15pF  |

| t <sub>DHL</sub> (Data)                                    | Data output delay after H to L CLK          | -  | 110 | ns    | CL = 15pF  |

| t <sub>DLE</sub>                                           | LE delay after L to H CLK                   | 50 | -   | ns    |            |

| t <sub>wle</sub>                                           | Width of LE pulse                           | 50 | -   | ns    |            |

| t <sub>SLE</sub>                                           | LE setup time before L to H CLK             | 50 | -   | ns    |            |

| t <sub>on</sub>                                            | Delay from LE to HV <sub>OUT</sub> , L to H | -  | 500 | ns    |            |

| t <sub>OFF</sub>                                           | Delay from LE to HV <sub>OUT</sub> , H to L | -  | 500 | ns    |            |

# **Power-Up Sequence**

- 1. Connect ground

- 2. Apply  $V_{DD}$ 3. Set all inputs (Data, CLK, Enable, etc.) to a known state

Power-down sequence should be the reverse of the above.

The  $V_{PP}$  should not drop below  $V_{DD}$  during operations.

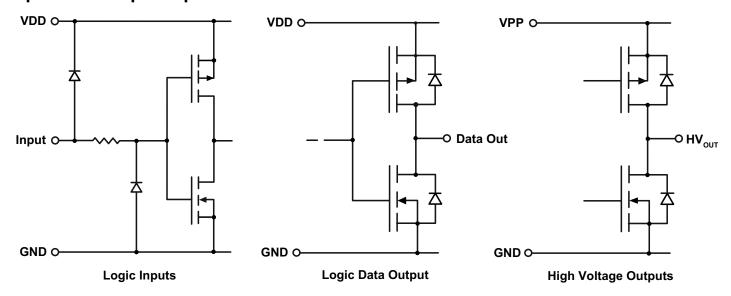

# **Input and Output Equivalent Circuits**

### **Switching Waveforms**

#### **Function Tables**

| Data Input | CLK         | Data Output |

|------------|-------------|-------------|

| Н          |             | Н           |

| L          |             | L           |

| X          | No_ <b></b> | No change   |

| Data Input | LE | OE | HV Output                   |

|------------|----|----|-----------------------------|

| Х          | X  | L  | All HV <sub>OUT</sub> = low |

| X          | L  | Н  | Previous latched data       |

| Н          | Н  | Н  | Н                           |

| L          | Н  | Н  | L                           |

# **Pin Description**

| Pin | Function             | Function                                                                                    |

|-----|----------------------|---------------------------------------------------------------------------------------------|

| 1   | HV <sub>out</sub> 16 |                                                                                             |

| 2   | HV <sub>OUT</sub> 17 |                                                                                             |

| 3   | HV <sub>OUT</sub> 18 |                                                                                             |

| 4   | HV <sub>OUT</sub> 19 |                                                                                             |

| 5   | HV <sub>OUT</sub> 20 |                                                                                             |

| 6   | HV <sub>OUT</sub> 21 |                                                                                             |

| 7   | HV <sub>OUT</sub> 22 |                                                                                             |

| 8   | HV <sub>OUT</sub> 23 | High voltage outputs.                                                                       |

| 9   | HV <sub>OUT</sub> 24 | High voltage push-pull outputs, which, depending on controlling low voltage data, can drive |

| 10  | HV <sub>OUT</sub> 25 | loads either to a GND, or to $V_{pp}$ rail levels.                                          |

| 11  | HV <sub>OUT</sub> 26 |                                                                                             |

| 12  | HV <sub>OUT</sub> 27 |                                                                                             |

| 13  | HV <sub>OUT</sub> 28 |                                                                                             |

| 14  | HV <sub>OUT</sub> 29 |                                                                                             |

| 15  | HV <sub>OUT</sub> 30 |                                                                                             |

| 16  | HV <sub>OUT</sub> 31 |                                                                                             |

| 17  | HV <sub>OUT</sub> 32 |                                                                                             |

|     |                      | Serial data output                                                                          |

| 18  | Data Out             | Data output for cascading to the data input of the next device.                             |

| 19  | N/C                  |                                                                                             |

| 20  | N/C                  | No connect.                                                                                 |

| 21  | N/C                  | TWO GOTTINGSE.                                                                              |

| 21  | 14/0                 | Data shift register clock.                                                                  |

| 22  | CLK                  |                                                                                             |

|     |                      | Input are shifted into the shift register on the positive edge of the clock.                |

| 23  | GND                  | Logic and high voltage ground.                                                              |

| 24  | VPP                  | High voltage power rail.                                                                    |

| 25  | VDD                  | Low voltage logic power rail.                                                               |

| Pin | Function             | Function                                                                                                                                                     |  |  |  |  |  |  |  |  |

|-----|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|     |                      | Latch enable input.                                                                                                                                          |  |  |  |  |  |  |  |  |

| 26  | Latch Enable         | When LE is high, shift register data is transferred into a data latch. When LE is low, data is latched, and new data can be clocked into the shift register. |  |  |  |  |  |  |  |  |

| 0.7 | Data la              | Serial data input.                                                                                                                                           |  |  |  |  |  |  |  |  |

| 27  | Data In              | Data needs to be present before each rising edge of the clock.                                                                                               |  |  |  |  |  |  |  |  |

|     |                      | Output enable input.                                                                                                                                         |  |  |  |  |  |  |  |  |

| 28  | Output Enable        | When OE is low, all HV outputs are forced into a low state, regardless of data in each channel. When OE is high, all HV outputs reflect data latched.        |  |  |  |  |  |  |  |  |

| 29  | N/C                  | No connect.                                                                                                                                                  |  |  |  |  |  |  |  |  |

| 30  | HV <sub>out</sub> 1  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 31  | HV <sub>OUT</sub> 2  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 32  | HV <sub>OUT</sub> 3  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 33  | HV <sub>OUT</sub> 4  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 34  | HV <sub>OUT</sub> 5  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 35  | HV <sub>OUT</sub> 6  |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 36  | HV <sub>out</sub> 7  | High voltage outputs.                                                                                                                                        |  |  |  |  |  |  |  |  |

| 37  | HV <sub>out</sub> 8  | High voltage push-pull outputs, which, depending on controlling low voltage data, can drive                                                                  |  |  |  |  |  |  |  |  |

| 38  | HV <sub>OUT</sub> 9  | loads either to a GND, or to $V_{PP}$ rail levels.                                                                                                           |  |  |  |  |  |  |  |  |

| 39  | HV <sub>OUT</sub> 10 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 40  | HV <sub>OUT</sub> 11 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 41  | HV <sub>OUT</sub> 12 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 42  | HV <sub>OUT</sub> 13 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 43  | HV <sub>OUT</sub> 14 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

| 44  | HV <sub>OUT</sub> 15 |                                                                                                                                                              |  |  |  |  |  |  |  |  |

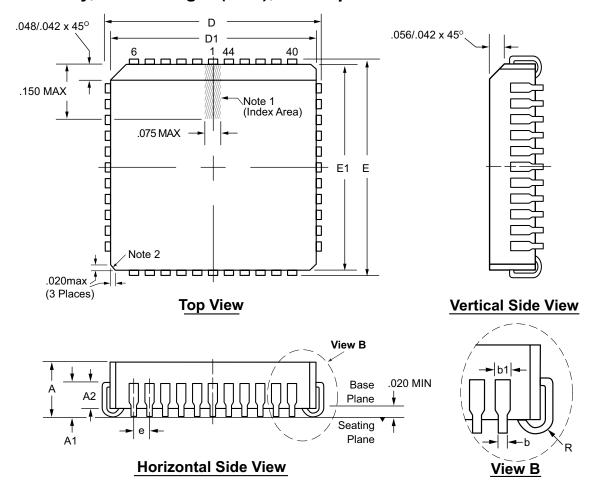

# 44-Lead PLCC Package Outline (PJ)

.653x.653in body, .180in height (max), .050in pitch

#### Notes:

- A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Actual shape of this feature may vary.

| Symbol             |     | Α    | <b>A1</b> | A2   | b    | b1                | D    | D1   | E    | E1   | е           | R    |

|--------------------|-----|------|-----------|------|------|-------------------|------|------|------|------|-------------|------|

|                    | MIN | .165 | .090      | .062 | .013 | .026              | .685 | .650 | .685 | .650 |             | .025 |

| Dimension (inches) | NOM | .172 | .105      | -    | -    | -                 | .690 | .653 | .690 | .653 | .050<br>BSC | .035 |

|                    | MAX | .180 | .120      | .083 | .021 | .036 <sup>†</sup> | .695 | .656 | .695 | .656 | 230         | .045 |

JEDEC Registration MS-018, Variation AC, Issue A, June, 1993.

† This dimension differs from the JEDEC drawing.

Drawings not to scale.

Supertex Doc. #: DSPD-44PLCCPJ, Version F031111.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2011 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.