# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

### **DS10CP154**

# 1.5 Gbps 4x4 LVDS Crosspoint Switch

### **General Description**

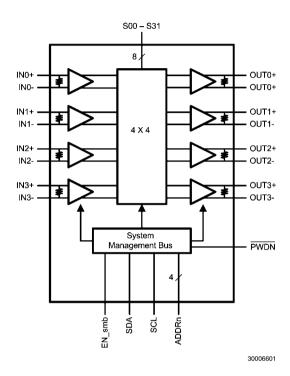

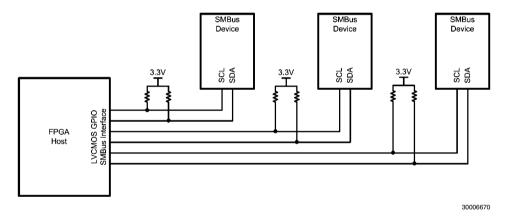

The DS10CP154 is a 1.5 Gbps 4x4 LVDS crosspoint switch optimized for high-speed signal routing and switching over FR-4 printed circuit board backplanes and balanced cables. Fully differential signal paths ensure exceptional signal integrity and noise immunity. The non-blocking architecture allows connections of any input to any output or outputs. The switch configuration can be accomplished via external pins or the System Management Bus (SMBus) interface. In addition, the SMBus circuitry enables the loss of signal (LOS) monitors that can inform a system of the presence of an open inputs condition (e.g. disconnected cable).

The DS10CP154 supports only a restricted SMBus application of a point-to-point connection between the master and a single slave device. The DS25CP104 SMBus cannot be shared with multiple SMBus slave devices on the same bus. For applications that require multiple SMBus slave devices using the same bus, the DS10CP154A is recommended.

Wide input common mode range allows the switch to accept signals with LVDS, CML and LVPECL levels; the output levels are LVDS. A very small package footprint requires a minimal space on the board while the flow-through pinout allows easy board layout. Each differential input and output is internally terminated with a  $100\Omega$  resistor to lower device insertion and return losses, reduce component count and further minimize board space.

#### **Features**

- DC 1.5 Gbps low jitter, low skew, low power operation

- Pin and SMBus configurable, fully differential, nonblocking architecture

- Wide input common mode range enables DC coupled interface to CML or LVPECL drivers

- LOS circuitry detects open inputs fault condition

- On-chip 100 Ω input and output termination minimizes insertion and return losses, reduces component count and minimizes board space

- 8 kV ESD on LVDS I/O pins protects adjoining components

- Small 6 mm x 6 mm LLP-40 space saving package

### **Applications**

- High-speed channel select applications

- Clock and data buffering and muxing

- SD / HD SDI Routers

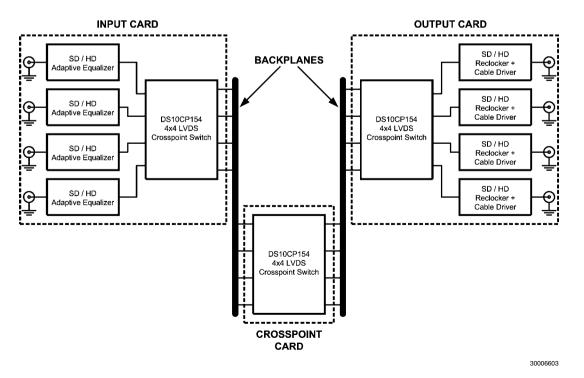

# **Typical Application**

ration

300066

# **Ordering Code**

| NSID         | Function          |

|--------------|-------------------|

| DS10CP154TSQ | Crosspoint Switch |

# **Block Diagram**

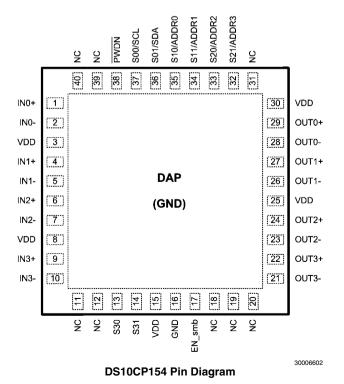

# **Connection Diagram**

# **Pin Descriptions**

| Pin Name                                                        | Pin<br>Number                           | I/O, Type   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------|-----------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN0+, IN0- ,<br>IN1+, IN1-,<br>IN2+, IN2-,<br>IN3+, IN3-        | 1, 2,<br>4, 5,<br>6, 7,<br>9, 10        | I, LVDS     | Inverting and non-inverting high speed LVDS input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT0+, OUT0-,<br>OUT1+, OUT1-,<br>OUT2+, OUT2-,<br>OUT3+, OUT3- | 29, 28,<br>27, 26,<br>24, 23,<br>22, 21 | O, LVDS     | Inverting and non-inverting high speed LVDS output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| EN_smb                                                          | 17                                      | I, LVCMOS   | System Management Bus (SMBus) mode enable pin. The pin has an internal 20k pull down. When the pin is set to a [1], the device is in the SMBus mode. All SMBus registers are reset when the pin is toggled.                                                                                                                                                                                                                                                                                  |

| S00/SCL,<br>S01/SDA                                             | 37,<br>36                               | I/O, LVCMOS | For EN_smb = [1], these pins select which LVDS input is routed to the OUT0.  In the SMBus mode, when the EN_smb = [1], these pins are the SMBus clock input and data I/O pins respectively.                                                                                                                                                                                                                                                                                                  |

| S10/ADDR0,<br>S11/ADDR1                                         | 35,<br>34                               | I/O, LVCMOS | For EN_smb = [0], these pins select which LVDS input is routed to the OUT1. In the SMBus mode, when the EN_smb = [1], these pins are the User-Set SMBus Slave Address inputs.                                                                                                                                                                                                                                                                                                                |

| S20/ADDR2,<br>S21/ADDR3                                         | 33,<br>32                               | I/O, LVCMOS | For EN_smb = [0], these pins select which LVDS input is routed to the OUT2.  In the SMBus mode, when the EN_smb = [1], these pins are the User-Set SMBus Slave Address inputs.                                                                                                                                                                                                                                                                                                               |

| S30, S31                                                        | 13, 14                                  | I, LVCMOS   | For EN_smb = [0], these pins select which LVDS input is routed to the OUT3.  In the SMBus mode, when the EN_smb = [1], these pins are nonfunctional and should be tied to either logic [0] or [1].                                                                                                                                                                                                                                                                                           |

| PWDN                                                            | 38                                      | I, LVCMOS   | For EN_smb = [0], this is the power down pin. When the PWDN is set to a [0], the device is in the power down mode. The SMBus circuitry can still be accessed provided the EN_smb pin is set to a [1].  In the SMBus mode, the device is powered up by either setting the PWDN pin to [1] OR by writing a [1] to the Control Register D[7] bit ( SoftPWDN). The device will be powered down by setting the PWDN pin to [0] AND by writing a [0] to the Control Register D[7] bit ( SoftPWDN). |

| NC                                                              | 11, 12,<br>18, 19,<br>20, 31,<br>39, 40 |             | No connect pins. May be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VDD                                                             | 3, 8,<br>15,25, 30                      | Power       | Power supply pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND                                                             | 16, DAP                                 | Power       | Ground pin and pad (DAP - die attach pad).                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **Absolute Maximum Ratings** (Note 4)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Supply Voltage -0.3V to +4V -0.3V to  $(V_{CC} + 0.3V)$ LVCMOS Input Voltage LVCMOS Output Voltage -0.3V to  $(V_{CC} + 0.3V)$ LVDS Input Voltage -0.3V to +4VLVDS Differential Input Voltage 0V to 1.0V LVDS Output Voltage -0.3V to  $(V_{CC} + 0.3V)$ 0V to 1.0V LVDS Differential Output Voltage LVDS Output Short Circuit Current Duration +150°C Junction Temperature Storage Temperature Range -65°C to +150°C Lead Temperature Range

Soldering (4 sec.) +260°C Maximum Package Power Dissipation at 25°C

SQA Package 4.65W Derate SQA Package

37.2 mW/°C above +25°C

CDM (Note 3)

| $\theta_{JA}$      | +26.9°C/W |

|--------------------|-----------|

| $\theta_{JC}$      | +3.8°C/W  |

| ESD Susceptibility |           |

| HBM (Note 1)       | ≥8 kV     |

| MM (Note 2)        | ≥250V     |

≥1250V

Note 1: Human Body Model, applicable std. JESD22-A114C Note 2: Machine Model, applicable std. JESD22-A115-A Note 3: Field Induced Charge Device Model, applicable std. JESD22-C101-C

### **Recommended Operating Conditions**

|                                                           | Min | Тур | Max | Units |

|-----------------------------------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>CC</sub> )                         | 3.0 | 3.3 | 3.6 | V     |

| Receiver Differential Input<br>Voltage (V <sub>ID</sub> ) | 0   |     | 1.0 | V     |

| Operating Free Air<br>Temperature (T <sub>A</sub> )       | -40 | +25 | +85 | °C    |

| SMBus (SDA, SCL)                                          |     |     | 3.6 | V     |

### **Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 5, 6, 7)

| Symbol                   | Parameter                         | Conditions                                  |            | Min  | Тур  | Max               | Units |

|--------------------------|-----------------------------------|---------------------------------------------|------------|------|------|-------------------|-------|

| LVCMOS DC SPECIFICATIONS |                                   |                                             |            |      |      |                   |       |

| V <sub>IH</sub>          | High Level Input Voltage          |                                             |            | 2.0  |      | $V_{DD}$          | V     |

| V <sub>IL</sub>          | Low Level Input Voltage           |                                             |            | GND  |      | 0.8               | V     |

| I <sub>IH</sub>          | High Level Input Current          | V <sub>IN</sub> = 3.6V                      |            |      | 0    | ±10               | μΑ    |

|                          |                                   | $V_{CC} = 3.6V$                             | EN_smb pin | 40   | 175  | 250               | μΑ    |

| I <sub>IL</sub>          | Low Level Input Current           | V <sub>IN</sub> = GND                       |            |      | 0    | ±10               | μΑ    |

|                          |                                   | $V_{CC} = 3.6V$                             |            |      |      |                   |       |

| $V_{CL}$                 | Input Clamp Voltage               | $I_{CL} = -18 \text{ mA}, V_{CC} = 0V$      |            |      | -0.9 | -1.5              | V     |

| V <sub>OL</sub>          | Low Level Output Voltage          | I <sub>OL</sub> = 4 mA                      | SDA pin    |      |      | 0.4               | V     |

| LVDS IN                  | PUT DC SPECIFICATIONS             |                                             | •          |      |      |                   |       |

| V <sub>ID</sub>          | Input Differential Voltage        |                                             |            | 0    |      | 1                 | V     |

| V <sub>TH</sub>          | Differential Input High Threshold | $V_{CM} = +0.05V \text{ or } V_{CC} -0.05V$ |            |      | 0    | +100              | mV    |

| V <sub>TL</sub>          | Differential Input Low Threshold  |                                             |            | -100 | 0    |                   | mV    |

| V <sub>CMR</sub>         | Common Mode Voltage Range         | V <sub>ID</sub> = 100 mV                    |            | 0.05 |      | V <sub>CC</sub> - | V     |

|                          |                                   |                                             |            |      |      | 0.05              |       |

| I <sub>IN</sub>          | Input Current                     | $V_{IN} = 3.6V \text{ or } 0$               |            |      | ±1   | ±10               | μA    |

| -IN                      | Impar darrone                     | $V_{CC} = 3.6V \text{ or } 0$               | )V         |      |      |                   |       |

| C <sub>IN</sub>          | Input Capacitance                 | Any LVDS Input Pin to GND                   |            |      | 1.7  |                   | pF    |

| R <sub>IN</sub>          | Input Termination Resistor        | Between IN+ and IN-                         |            |      | 100  |                   | Ω     |

|                          |                                   |                                             |            |      |      |                   |       |

| Symbol                        | Parameter                                                                 | Conditions                 | Min  | Тур | Max   | Units |  |

|-------------------------------|---------------------------------------------------------------------------|----------------------------|------|-----|-------|-------|--|

| LVDS OUTPUT DC SPECIFICATIONS |                                                                           |                            |      |     |       |       |  |

| $\overline{V_{OD}}$           | Differential Output Voltage                                               |                            | 250  | 350 | 450   | mV    |  |

| ΔV <sub>OD</sub>              | Change in Magnitude of V <sub>OD</sub> for Complimentary<br>Output States | $R_L = 100\Omega$          | -35  |     | 35    | mV    |  |

| V <sub>os</sub>               | Offset Voltage                                                            |                            | 1.05 | 1.2 | 1.375 | V     |  |

| ΔV <sub>OS</sub>              | Change in Magnitude of V <sub>OS</sub> for Complimentary<br>Output States | $R_L = 100\Omega$          | -35  |     | 35    | mV    |  |

| I <sub>os</sub>               | Output Short Circuit Current (Note 8)                                     | OUT to GND                 |      | -25 | -55   | mA    |  |

|                               |                                                                           | OUT to V <sub>CC</sub>     |      | 7   | 55    | mA    |  |

| C <sub>OUT</sub>              | Output Capacitance                                                        | Any LVDS Output Pin to GND |      | 1.2 |       | pF    |  |

| R <sub>OUT</sub>              | Output Termination Resistor                                               | Between OUT+ and OUT-      |      | 100 |       | Ω     |  |

| SUPPLY                        | CURRENT                                                                   |                            | •    | ,   |       |       |  |

| I <sub>CC1</sub>              | Supply Current                                                            | PWDN = 0                   |      | 40  | 50    | mA    |  |

| I <sub>CC2</sub>              | Supply Current                                                            | PWDN = 1                   |      | 103 | 125   | mA    |  |

|                               |                                                                           | Broadcast Mode (1:4)       |      |     |       |       |  |

| I <sub>CC3</sub>              | Supply Current                                                            | PWDN = 1                   |      | 115 | 140   | mA    |  |

|                               |                                                                           | Quad Buffer Mode (4:4)     |      |     |       |       |  |

Note 4: "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions at which the device is functional and the device should not be operated beyond such conditions.

Note 5: The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 6: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ .

Note 7: Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 8: Output short circuit current ( $I_{OS}$ ) is specified as magnitude only, minus sign indicates direction only.

# **AC Electrical Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (Notes 9, 10)

| Symbol            | Parameter                                                       | Cone                                          | ditions             | Min | Тур   | Max   | Units             |

|-------------------|-----------------------------------------------------------------|-----------------------------------------------|---------------------|-----|-------|-------|-------------------|

| LVDS OUTPU        | T AC SPECIFICATIONS (Note 11)                                   | •                                             |                     |     |       |       |                   |

| t <sub>PLHD</sub> | Differential Propagation Delay Low to High                      |                                               |                     |     | 500   | 675   | ps                |

| t <sub>PHLD</sub> | Differential Propagation Delay High to Low                      | $R_L = 100\Omega$                             |                     |     | 460   | 675   | ps                |

| t <sub>SKD1</sub> | Pulse Skew It <sub>PLHD</sub> – t <sub>PHLD</sub> I , (Note 12) |                                               |                     |     | 40    | 100   | ps                |

| t <sub>SKD2</sub> | Channel to Channel Skew , (Note 13)                             |                                               |                     |     | 40    | 125   | ps                |

| t <sub>SKD3</sub> | Part to Part Skew , (Note 14)                                   |                                               |                     |     | 50    | 225   | ps                |

| t <sub>LHT</sub>  | Rise Time                                                       | D = 4000                                      |                     |     | 145   | 350   | ps                |

| t <sub>HLT</sub>  | Fall Time                                                       | $R_L = 100\Omega$                             |                     |     | 145   | 350   | ps                |

| t <sub>on</sub>   | Power Up Time                                                   | Time from PWDN                                | = LH to OUTn active |     | 7     | 20    | μs                |

| t <sub>OFF</sub>  | Power Down Time                                                 | Time from PWDN = HL to OUTn inactive          |                     |     | 6     | 25    | ns                |

| t <sub>SEL</sub>  | Select Time                                                     | Time from Sn = LH or HL to new signal at OUTn |                     |     | 8     | 12    | ns                |

| JITTER PERF       | ORMANCE (Note 11)                                               |                                               |                     |     |       |       |                   |

| t <sub>RJ1</sub>  |                                                                 | V <sub>ID</sub> = 350 mV                      | 135 MHz             |     | 1     | 2.0   | ps                |

| t <sub>RJ2</sub>  | Random Jitter (RMS Value)                                       | $V_{CM} = 1.2V$                               | 311 MHz             |     | 0.5   | 1.2   | ps                |

| t <sub>RJ3</sub>  | (Note 15)                                                       | Clock (RZ)                                    | 503 MHz             |     | 0.5   | 1.0   | ps                |

| t <sub>RJ4</sub>  | (Note 10)                                                       |                                               | 750 MHz             |     | 0.5   | 1.0   | ps                |

| t <sub>DJ1</sub>  |                                                                 | V <sub>ID</sub> = 350 mV                      | 270 Mbps            |     | 7     | 30    | ps                |

| t <sub>DJ2</sub>  | Deterministic Jitter                                            | $V_{CM} = 1.2V$                               | 622 Mbps            |     | 12    | 26    | ps                |

| t <sub>DJ3</sub>  | (Peak to Peak Value) (Note 16)                                  | K28.5 (NRZ)                                   | 1.06 Gbps           |     | 9     | 24    | ps                |

| t <sub>DJ4</sub>  | (Note 16)                                                       |                                               | 1.5 Gbps            |     | 12    | 28    | ps                |

| t <sub>TJ1</sub>  |                                                                 | V <sub>ID</sub> = 350 mV                      | 270 mbps            |     | 0.008 | 0.036 | UI <sub>P-F</sub> |

| t <sub>TJ2</sub>  | Total Jitter                                                    | $V_{CM} = 1.2V$                               | 622 Mbps            |     | 0.007 | 0.043 | UI <sub>P-F</sub> |

| t <sub>TJ3</sub>  | (Peak to Peak Value) (Note 17)                                  | PRBS-23 (NRZ)                                 | 1.06Gbps            |     | 0.008 | 0.064 | UI <sub>P-F</sub> |

| t <sub>TJ4</sub>  |                                                                 |                                               | 1.5 Gbps            |     | 0.007 | 0.072 | UI <sub>P-F</sub> |

| Symbol               | Parameter                                                                                          | Conditions | Min | Тур | Max | Units |  |  |

|----------------------|----------------------------------------------------------------------------------------------------|------------|-----|-----|-----|-------|--|--|

| SMBus AC SP          | SMBus AC SPECIFICATIONS                                                                            |            |     |     |     |       |  |  |

| f <sub>SMB</sub>     | SMBus Operating Frequency                                                                          |            | 10  |     | 100 | kHz   |  |  |

| t <sub>BUF</sub>     | Bus free time between Stop and Start<br>Conditions                                                 |            | 4.7 |     |     | μs    |  |  |

| t <sub>HD:SDA</sub>  | Hold time after (Repeated) Start<br>Condition. After this period, the first clock<br>is generated. |            | 4.0 |     |     | μs    |  |  |

| t <sub>SU:SDA</sub>  | Repeated Start Condition setup time.                                                               |            | 4.7 |     |     | μs    |  |  |

| t <sub>SU:SDO</sub>  | Stop Condition setup time                                                                          |            | 4.0 |     |     | μs    |  |  |

| t <sub>HD:DAT</sub>  | Data hold time                                                                                     |            | 300 |     |     | ns    |  |  |

| t <sub>SU:DAT</sub>  | Data setup time                                                                                    |            | 250 |     |     | ns    |  |  |

| t <sub>TIMEOUT</sub> | Detect clock low timeout                                                                           |            | 25  |     | 35  | ms    |  |  |

| t <sub>LOW</sub>     | Clock low period                                                                                   |            | 4.7 |     |     | μs    |  |  |

| t <sub>HIGH</sub>    | Clock high period                                                                                  |            | 4.0 |     | 50  | μs    |  |  |

| t <sub>POR</sub>     | Time in which a device must be operational after power-on reset                                    |            |     |     | 500 | ms    |  |  |

**Note 9:** The Electrical Characteristics tables list guaranteed specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not guaranteed.

Note 10: Typical values represent most likely parametric norms for  $V_{CC} = +3.3V$  and  $T_A = +25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not guaranteed.

Note 11: Specification is guaranteed by characterization and is not tested in production.

Note 12: t<sub>SKD1</sub>, lt<sub>PLHD</sub> – t<sub>PHLD</sub>I, Pulse Skew, is the magnitude difference in differential propagation delay time between the positive going edge and the negative going edge of the same channel.

Note 13:  $t_{SKD2}$ . Channel to Channel Skew, is the difference in propagation delay  $(t_{PLHD} \text{ or } t_{PHLD})$  among all output channels in Broadcast mode (any one input to all outputs).

Note 14: t<sub>SKD3</sub>, Part to Part Skew, is defined as the difference between the minimum and maximum differential propagation delays. This specification applies to devices at the same V<sub>CC</sub> and within 5°C of each other within the operating temperature range.

Note 15: Measured on a clock edge with a histogram and an acummulation of 1500 histogram hits. Input stimulus jitter is subtracted geometrically.

Note 16: Tested with a combination of the 1100000101 (K28.5+ character) and 0011111010 (K28.5- character) patterns. Input stimulus jitter is subtracted algebraically.

Note 17: Measured on an eye diagram with a histogram and an acummulation of 3500 histogram hits. Input stimulus jitter is subtracted.

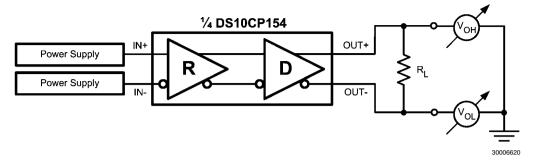

## **DC Test Circuits**

FIGURE 1. Differential Driver DC Test Circuit

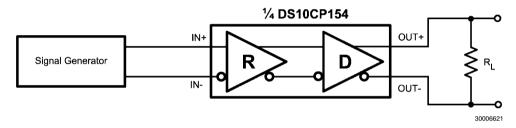

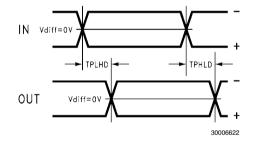

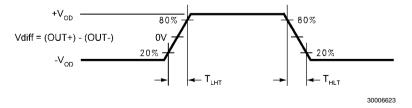

# **AC Test Circuits and Timing Diagrams**

FIGURE 2. Differential Driver AC Test Circuit

FIGURE 3. Propagation Delay Timing Diagram

FIGURE 4. LVDS Output Transition Times

### **Functional Description**

The DS10CP154 is a 1.5 Gbps 4x4 LVDS digital crosspoint switch optimized for high-speed signal routing and switching over lossy FR-4 printed circuit board backplanes and balanced cables. The DS10CP154 operates in two modes: Pin Mode (EN\_smb = 0) and SMBus Mode (EN\_smb = 1).

When in the Pin Mode, the switch is fully configurable with external pins. This is possible with two input select pins per output (e.g. S00 and S01 pins for OUT0).

In the Pin Mode, feedback from the  $\overline{\text{LOS}}$  (Loss Of Signal) monitor circuitry is not available (there is not an  $\overline{\text{LOS}}$  output pin).

The DS10CP154 supports only a restricted SMBus application of a point-to-point connection between the master and a single slave device. The DS10CP154 SMBus cannot be shared with multiple SMBus slave devices on the same bus. For applications that require multiple SMBus slave devices using the same bus, the DS10CP154A is recommended. For more information about the DS10CP154 SMBus application restrictions read the SMBus User Information Note at http://www.national.com/appinfo/interface/files/

SMBus UIN Crosspoints.pdf.

When in the SMBus Mode, the full switch configuration and  $\overline{\text{SoftPWDN}}$  can be programmed via the SMBus interface. In addition, by using the SMBus interface, a user can obtain the feedback from the built-in  $\overline{\text{LOS}}$  circuitry which detects an open inputs fault condition.

In the SMBus Mode, the S00 and S01 pins become SMBus clock (SCL) input and data (SDA) input pins respectively; the S10, S11, S21 and S21 pins become the User-Set SMBus Slave Address input pins (ADDR0, 1, 2 and 3) while the S30 and S31 pins become non-functional (tieing these two pins to either H or L is recommended if the device will function only in the SMBus mode).

In the SMBus Mode, the  $\overline{\text{PWDN}}$  pin remains functional. How this pin functions in each mode is detailed in the following sections.

#### **DS10CP154 OPERATION IN THE PIN MODE**

#### **Power Up**

In the Pin Mode, when the power is applied to the device power suppy pins, the DS10CP154 enters the Power Up mode when the  $\overline{\text{PWDN}}$  pin is set to logic H. When in the Power Down mode ( $\overline{\text{PWDN}}$  pin is set to logic L), all circuitry is shut down except the minimum required circuitry for the  $\overline{\text{LOS}}$  and SMBus Slave operation.

#### **Switch Configuration**

In the Pin Mode, the DS10CP154 operates as a fully pin-configurable crosspoint switch. The following truth tables illustrate how the swich can be configured with external pins.

#### **Switch Configuration Truth Tables**

**TABLE 1. Input Select Pins Configuration for the Output OUT0**

| S01 | S00 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

TABLE 2. Input Select Pins Configuration for the Output OUT1

| S11 | S10 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

9

TABLE 3. Input Select Pins Configuration for the Output OUT2

| S21 | S20 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

**TABLE 4. Input Select Pins Configuration for the Output OUT3**

| S31 | S30 | INPUT SELECTED |

|-----|-----|----------------|

| 0   | 0   | IN0            |

| 0   | 1   | IN1            |

| 1   | 0   | IN2            |

| 1   | 1   | IN3            |

#### **DS10CP154 OPERATION IN THE SMBUS MODE**

The DS10CP154 operates as a slave on the System Management Bus (SMBus) when the EN\_smb pin is set to a high (1). Under these conditions, the SCL pin is a clock input while the SDA pin is a serial data input pin.

The DS10CP154 supports only a restricted SMBus application of a point-to-point connection between the master and a single slave device. The DS10CP154 SMBus cannot be

shared with multiple SMBus slave devices on the same bus. For applications that require multiple SMBus slave devices using the same bus, the DS10CP154A is recommended. For more information about the DS10CP154 SMBus application restrictions read the SMBus User Information Note at http://www.national.com/appinfo/interface/files/

SMBus\_UIN\_Crosspoints.pdf.

FIGURE 5. DS10CP154 SMBus Only Supports a Point-to-Point Connection with a Master

#### **Device Address**

Based on the SMBus 2.0 specification, the DS10CP154 has a 7-bit slave address. The three most significant bits of the slave address are hard wired inside the DS10CP154 and are

"101". The four least significant bits of the address are assigned to pins ADDR3-ADDR0 and are set by connecting these pins to GND for a low (0) or to VCC for a high (1). The complete slave address is shown in the following table:

TABLE 5. DS10CP154 Slave Address

| 1   | 0 | 1 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

|-----|---|---|-------|-------|-------|-------|

| MSB |   |   |       |       |       | LSB   |

#### Transfer of Data via the SMBus

During normal operation the data on SDA must be stable during the time when SCK is high.

There are three unique states for the SMBus:

$\begin{tabular}{ll} \textbf{START:} A HIGH to LOW transition on SDA while SCK is high indicates a message START condition. \\ \end{tabular}$

**STOP:** A LOW to HIGH transition on SDA while SCK is high indicates a message STOP condition.

**IDLE:** If SCK and SDA are both high for a time exceeding tBUF from the last detected STOP condition or if they are high for a total exceeding the maximum specification for tHIGH then the bus will transfer to the IDLE state.

#### **SMBus Transactions**

A transaction begins with the host placing the DS10CP154 SMBus into the START condition, then a byte (8 bits) is transferred, MSB first, followed by a ninth ACK bit. ACK bits are '0' to signify an ACK, or '1' to signify NACK, after this the host

holds the SCL line low, and waits for the receiver to raise the SDA line as an ACKnowledge that the byte has been received.

#### Writing to a Register

To write a register, the following protocol is used (see SMBus 2.0 specification):

- 1) The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2) The Device (Slave) drives an ACK bit ("0").

- 3) The Host drives the 8-bit Register Address.

- 4) The Device drives an ACK bit ("0").

- 5) The Host drives the 8-bit data byte.

- 6) The Device drives an ACK bit "0".

- 7) The Host drives a STOP condition.

The WRITE transaction is completed, the bus goes Idle and communication with other SMBus devices may now occur.

#### Reading From a Register

To read a register, the following protocol is used (see SMBus 2.0 specification):

- 1) The Host drives a START condition, the 7-bit SMBus address, and a "0" indicating a WRITE.

- 2) The Device (Slave) drives an ACK bit ("0").

- 3) The Host drives the 8-bit Register Address.

- 4) The Device drives an ACK bit ("0").

- 5) The Host drives a START condition.

- 6) The Host drives the 7-bit SMBus Address, and a "1" indicating a READ.

- 7) The Device drives an ACK bit "0".

- 8) The Device drives the 8-bit data value (register contents).

- 9) The Host drives a NACK bit "1" indicating end of READ transfer.

- 10) The Host drives a STOP condition.

The READ transaction is completed, the bus goes Idle and communication with other SMBus devices may now occur.

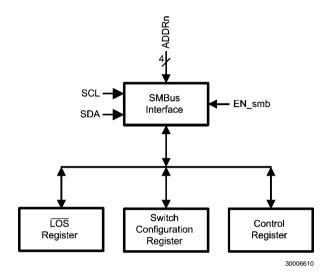

#### **REGISTER DESCRIPTIONS**

There are three data registers in the DS10CP154 accessible via the SMBus interface.

TABLE 6. DS10CP154 SMBus Data Registers

| Address<br>(hex) | Name                 | Access | Description                                    |  |

|------------------|----------------------|--------|------------------------------------------------|--|

| 0                | Switch Configuration | R/W    | Switch Configuration Register                  |  |

| 3                | Control              | R/W    | Powerdown, LOS Enable and Pin Control Register |  |

| 4                | LOS                  | RO     | Loss Of Signal (LOS) Reporting Register        |  |

FIGURE 6. DS10CP154 Registers Block Diagram

#### **SWITCH CONFIGURATION REGISTER**

The Switch Configuration register is utilized to configure the switch. The following two tables show the Switch Configuration Register mapping and associated truth table.

| Bit    | Default | Bit Name       | Access | Description                                |

|--------|---------|----------------|--------|--------------------------------------------|

| D[1:0] | 00      | Input Select 0 | R/W    | Selects which input is routed to the OUT0. |

| D[3:2] | 00      | Input Select 1 | R/W    | Selects which input is routed to the OUT1. |

| D[5:4] | 00      | Input Select 2 | R/W    | Selects which input is routed to the OUT2. |

| D[7:6] | 00      | Input Select 3 | R/W    | Selects which input is routed to the OUT3. |

#### **TABLE 7. Switch Configuration Register Truth Table**

| D1 | D0 | Input Routed to the OUT0 |

|----|----|--------------------------|

| 0  | 0  | INO                      |

| 0  | 1  | IN1                      |

| 1  | 0  | IN2                      |

| 1  | 1  | IN3                      |

The truth tables for the OUT1, OUT2, and OUT3 outputs are identical to this table.

The switch configuration logic has a SmartPWDN circuitry which automatically optimizes the device's power consumption based on the switch configuration (i.e. It places unused I/O blocks and other unused circuitry in the power down state).

#### **CONTROL REGISTER**

The Control register enables SoftPWDN control, individual output power down (PWDNn) control and LOS Circuitry Enable control via the SMBus. The following table shows the register mapping.

| Bit    | Default | Bit Name | Access | Description                                                                                                                                                                                                                                                              |

|--------|---------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[3:0] | 1111    | PWDNn    | R/W    | Writing a [0] to the bit D[n] will power down the output OUTn when either the PWDN pin OR the Control Register bit D[7] (SoftPWDN) is set to a high [1].                                                                                                                 |

| D[4]   | х       | n/a      | R/W    | Undefined.                                                                                                                                                                                                                                                               |

| D[5]   | х       | n/a      | R/W    | Undefined.                                                                                                                                                                                                                                                               |

| D[6]   | 0       | EN_LOS   | R/W    | Writing a [1] to the bit D[6] will enable the $\overline{\text{LOS}}$ circuitry and receivers on all four inputs. The SmartPWDN circuitry will not disable any of the inputs nor any supporting $\overline{\text{LOS}}$ circuitry depending on the switch configuration. |

| D[7]   | 0       | SoftPWDN | R/W    | Writing a [0] to the bit D[7] will place the device into the power down mode. This pin is ORed together with the PWDN pin.                                                                                                                                               |

#### **TABLE 8. DS10CP154 Power Modes Truth Table**

| PWDN | SoftPWDN | PWDNn | DS25CP104 Power Mode                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0        | х     | Power Down Mode. In this mode, all circuitry is shut down except the minimum required circuitry for the $\overline{LOS}$ and SMBus Slave operation. The SMBus circuitry allows enabling the $\overline{LOS}$ circuitry and receivers on all inputs in this mode by setting the EN_ $\overline{LOS}$ bit to a [1].                                                                                                                                  |

| 0    | 1        | х     | Power Up Mode. In this mode, the SmartPWDN circuitry will automatically                                                                                                                                                                                                                                                                                                                                                                            |

| 1    | 0        | х     | power down any unused I/O and logic blocks and other supporting circuitry                                                                                                                                                                                                                                                                                                                                                                          |

| 1    | 1        | х     | depending on the switch configuration.  An output will be enabled <b>only</b> when the SmartPWDN circuitry indicates that that particular output is needed for the particular switch configuration <b>and</b> the respective PWDNn bit has logic high [1].  An input will be enabled when the SmartPWDN circuitry indicates that that particular input is needed for the particular switch configuration <b>or</b> the EN_LOS bit is set to a [1]. |

#### **LOS REGISTER**

The LOS register reports an open inputs fault condition for each of the inputs. The following table shows the register mapping.

| Bit    | Default | Bit Name | Access | Description                                                                 |  |

|--------|---------|----------|--------|-----------------------------------------------------------------------------|--|

| D[0]   | 0       | LOS0     | RO     | Reading a [0] from the bit D[0] indicates an open inputs fault condition on |  |

|        |         |          |        | the INO. A [1] indicates presence of a valid signal.                        |  |

| D[1]   | 0       | LOS1     | RO     | Reading a [0] from the bit D[1] indicates an open inputs fault condition on |  |

|        |         |          |        | the IN1. A [1] indicates presence of a valid signal.                        |  |

| D[2]   | 0       | LOS2     | RO     | Reading a [0] from the bit D[2] indicates an open inputs fault condition on |  |

|        |         |          |        | the IN2. A [1] indicates presence of a valid signal.                        |  |

| D[3]   | 0       | LOS3     | RO     | Reading a [0] from the bit D[3] indicates an open inputs fault condition on |  |

|        |         |          |        | the IN3. A [1] indicates presence of a valid signal.                        |  |

| D[7:4] | 0000    | Reserved | RO     | Reserved for future use. Returns undefined value when read.                 |  |

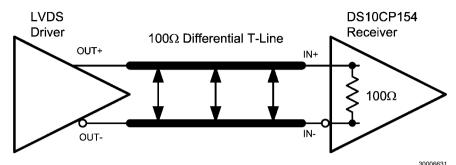

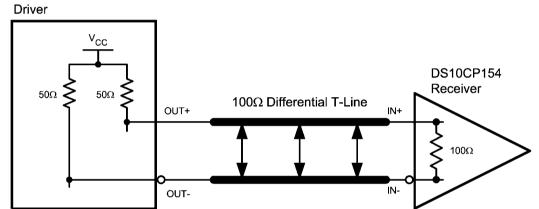

#### **INPUT INTERFACING**

The DS10CP154 accepts differential signals and allows simple AC or DC coupling. With a wide common mode range, the DS10CP154 can be DC-coupled with all common differential

drivers (i.e. LVPECL, LVDS, CML). The following three figures illustrate typical DC-coupled interface to common differential drivers. Note that the DS10CP154 inputs are internally terminated with a  $100\Omega$  resistor.

Typical LVDS Driver DC-Coupled Interface to DS10CP154 Input

#### CML3.3V or CML2.5V

Typical CML Driver DC-Coupled Interface to DS10CP154 Input

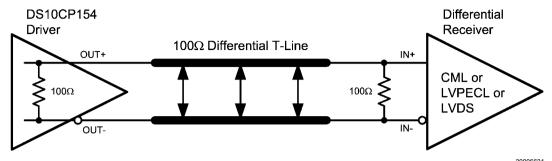

LVPECL Driver

OUT+

100Ω Differential T-Line

IN

100Ω

100Ω

100Ω

100Ω

100Ω

Typical LVPECL Driver DC-Coupled Interface to DS10CP154 Input

15 www.national.com

30006632

#### **OUTPUT INTERFACING**

The DS10CP154 outputs signals that are compliant to the LVDS standard. Its outputs can be DC-coupled to most common differential receivers. The following figure illustrates typical DC-coupled interface to common differential receivers

and assumes that the receivers have high impedance inputs. While most differential receivers have a common mode input range that can accomodate LVDS compliant signals, it is recommended to check respective receiver's data sheet prior to implementing the suggested interface implementation.

Typical DS10CP154 Output DC-Coupled Interface to an LVDS, CML or LVPECL Receiver

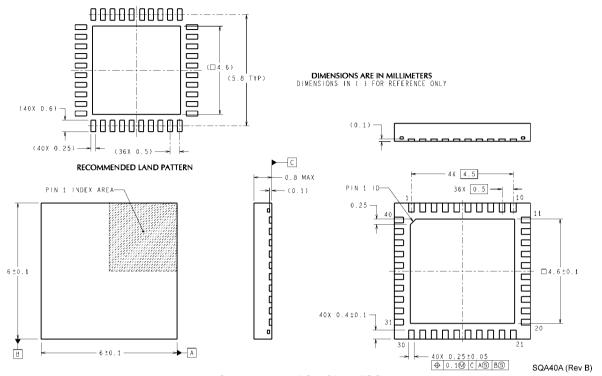

# Physical Dimensions inches (millimeters) unless otherwise noted

Order Number DS10CP154TSQ

NS Package Number SQA40A

(See AN-1187 for PCB Design and Assembly Recommendations)

17

### **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com National Semiconductor Japan Technical Support Center Email: ion.feedback@nsc.com