1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# Enhanced Current Mode PWM Controller

The CS51021A/2A/3A/4A Fixed Frequency PWM Current Mode Controller family provides all necessary features required for AC–DC or DC–DC primary side control. Several features are included eliminating the additional components needed to implement them externally. In addition to low start–up current (75  $\mu$ A) and high frequency operation capability, the CS51021A/2A/3A/4A family includes overvoltage and undervoltage monitoring, externally programmable dual threshold overcurrent protection, current sense leading edge blanking, current slope compensation, accurate duty cycle control and an externally available 5.0 V reference. The CS51021A and CS51023A feature bidirectional synchronization capability, while the CS51022A and CS51024A offer a sleep mode with 100  $\mu$ A maximum IC current consumption. The CS51021A/2A/3A/4A family is available in a 16 lead narrow body SO package.

| Device   | Sleep/Synch | V <sub>CC</sub> Start/Stop |

|----------|-------------|----------------------------|

| CS51021A | Synch       | 8.25 V/7.7 V               |

| CS51022A | Sleep       | 8.25 V/7.7 V               |

| CS51023A | Synch       | 13 V/7.7 V                 |

| CS51024A | Sleep       | 13 V/7.7 V                 |

#### Features

- 75 µA Max. Startup Current

- Fixed Frequency Current Mode Control

- 1.0 MHz Switching Frequency

- Undervoltage Protection Monitor

- Overvoltage Protection Monitor with Programmable Hysteresis

- Programmable Dual Threshold Overcurrent Protection with Delayed Restart

- Programmable Soft Start

- Accurate Maximum Duty Cycle Limit

- Programmable Slope Compensation

- Leading Edge Current Sense Blanking

- 1.0 A Sink/Source Gate Drive

- Bidirectional Synchronization (CS51021A/3A)

- 50 ns PWM Propagation Delay

- 100 µA Max Sleep Current (CS51022A/4A)

#### WW, W = Work Week

#### **ORDERING INFORMATION\***

| Device        | Package | Shipping         |

|---------------|---------|------------------|

| CS51021AED16  | SO–16   | 48 Units/Rail    |

| CS51021AEDR16 | SO–16   | 2500 Tape & Reel |

| CS51022AED16  | SO-16   | 48 Units/Rail    |

| CS51022AEDR16 | SO-16   | 2500 Tape & Reel |

| CS51023AED16  | SO-16   | 48 Units/Rail    |

| CS51023AEDR16 | SO-16   | 2500 Tape & Reel |

| CS51024AED16  | SO–16   | 48 Units/Rail    |

| CS51024AEDR16 | SO-16   | 2500 Tape & Reel |

\* Consult your local sales representative for other package options.

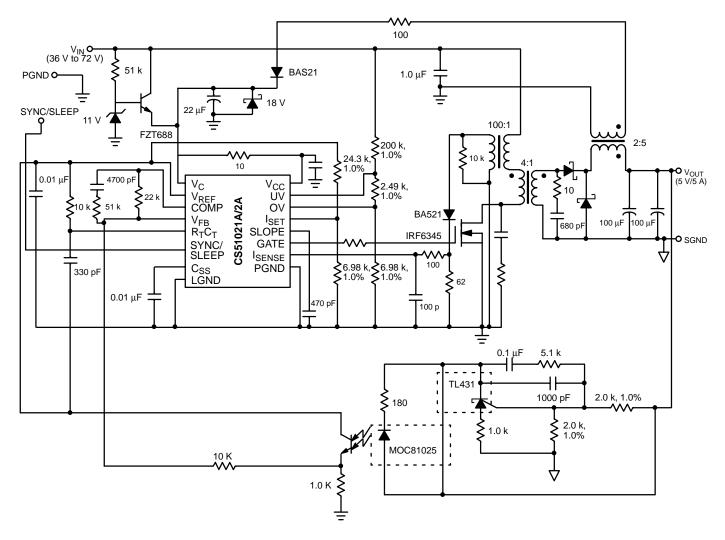

Figure 1. Typical Application Diagram, 36-72 V to 5.0 V, 5.0 A DC-DC Converter

#### MAXIMUM RATINGS\*

| Rating                                                               |                                    | Value                    | Unit |

|----------------------------------------------------------------------|------------------------------------|--------------------------|------|

| Power Supply Voltage, V <sub>CC</sub>                                |                                    | -0.3, 20                 | V    |

| Driver Supply Voltage, V <sub>C</sub>                                |                                    | -0.3, 20                 | V    |

| SYNC, SLEEP, RTCT, SOFT START, VFB, SLOPE, ISENSE, UV, OV, ISET (Log | jic Pins)                          | 0.25 to V <sub>REF</sub> | V    |

| Peak GATE Output Current                                             |                                    | 1.0                      | А    |

| Steady State Output Current                                          |                                    | ±0.2                     | А    |

| Operating Junction Temperature, T <sub>J</sub>                       |                                    | 150                      | °C   |

| Storage Temperature Range, T <sub>S</sub>                            |                                    | -65 to +150              | °C   |

| ESD (Human Body Model)                                               |                                    | 2.0                      | kV   |

| Lead Temperature Soldering:                                          | Reflow: (SMD styles only) (Note 1) | 230 peak                 | °C   |

| 60 accord maximum above 192°C                                        |                                    |                          |      |

1. 60 second maximum above 183°C.

\*The maximum package power dissipation must be observed.

| ELECTRICAL CHARACTERISTICS                                        | (Unless otherwise stated, specifications apply for $-40^{\circ}C < T_A < 85^{\circ}C$ , |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| −40°C < T <sub>J</sub> < 150°C, 3.0 V < V <sub>C</sub> < 20 V, 8. | 2 V < V <sub>CC</sub> < 20 V, R <sub>T</sub> = 12 kΩ, C <sub>T</sub> = 390 pF)          |

| Characteristic                          | Test Conditions                                                                        | Min                   | Тур                   | Мах                    | Unit |

|-----------------------------------------|----------------------------------------------------------------------------------------|-----------------------|-----------------------|------------------------|------|

| Under Voltage Lockout                   |                                                                                        |                       |                       |                        |      |

| START Threshold (CS51021A/2A)           | _                                                                                      | 7.95                  | 8.25                  | 8.8                    | V    |

| START Threshold (CS51023A/4A)           | _                                                                                      | 12.4                  | 13                    | 13.4                   | V    |

| STOP Threshold                          | _                                                                                      | 7.4                   | 7.7                   | 8.2                    | V    |

| Hysteresis (CS51021A/2A)                | _                                                                                      | 0.50                  | 0.75                  | 1.00                   | V    |

| Hysteresis (CS51023A/4A)                | _                                                                                      | 4.0                   | 5.0                   | 6.0                    | V    |

| I <sub>CC</sub> @ Startup (CS51021A/2A) | $V_{CC} < UV_{START}$ Threshold                                                        | -                     | 40                    | 75                     | μΑ   |

| I <sub>CC</sub> @ Startup (CS51023A/4A) | V <sub>CC</sub> < UV <sub>START</sub> Threshold                                        | -                     | 45                    | 75                     | μΑ   |

| I <sub>CC</sub> Operating (CS51021A/3A) | _                                                                                      | -                     | 7.0                   | 9.0                    | mA   |

| I <sub>CC</sub> Operating (CS51022A/4A) | _                                                                                      | -                     | 6.0                   | 8.0                    | mA   |

| I <sub>CC</sub> Operating               | Includes 1.0 nF Load                                                                   | -                     | 7.0                   | 12                     | mA   |

| Voltage Reference                       |                                                                                        |                       |                       |                        |      |

| Initial Accuracy                        | $T_A = 25^{\circ}C$ , $I_{REF} = 2.0$ mA, $V_{CC} = 14$ V, Note 2                      | 4.95                  | 5.0                   | 5.05                   | V    |

| Total Accuracy                          | 1.0 mA < I <sub>REF</sub> < 10 mA                                                      | 4.9                   | 5.0                   | 5.15                   | V    |

| Line Regulation                         | 8.2 V < V <sub>CC</sub> < 18 V, I <sub>REF</sub> = 2.0 mA                              | -                     | 6.0                   | 20                     | mV   |

| Load Regulation                         | 1.0 mA < I <sub>REF</sub> < 10 mA                                                      | -                     | 6.0                   | 15                     | mV   |

| NOISE Voltage                           | Note 2                                                                                 | -                     | 50                    | _                      | μV   |

| OP Life Shift                           | T = 1000 Hours, Note 2                                                                 | -                     | 4.0                   | 20                     | mV   |

| FAULT Voltage                           | Force V <sub>REF</sub>                                                                 | $0.90 \times V_{REF}$ | $0.93 \times V_{REF}$ | $0.95 \times V_{REF}$  | V    |

| OK Voltage                              | Force V <sub>REF</sub>                                                                 | $0.94 \times V_{REF}$ | $0.96 \times V_{REF}$ | $0.985 \times V_{REF}$ | V    |

| OK Hysteresis                           | Force V <sub>REF</sub>                                                                 | 75                    | 165                   | 250                    | mV   |

| Current Limit                           | Force V <sub>REF</sub>                                                                 | -20                   | _                     | _                      | mA   |

| Error Amplifier                         |                                                                                        |                       |                       |                        |      |

| Initial Accuracy                        | $T_A = 25^{\circ}C$ , $I_{REF} = 2.0$ mA, $V_{CC} = 14$ V,<br>$V_{FB} = COMP$ , Note 2 | 2.465                 | 2.515                 | 2.565                  | V    |

| Reference Voltage                       | V <sub>FB</sub> = COMP                                                                 | 2.440                 | 2.515                 | 2.590                  | V    |

| V <sub>FB</sub> Leakage Current         | V <sub>FB</sub> = 0 V                                                                  | -                     | -0.2                  | -2.0                   | μΑ   |

| Open Loop Gain                          | 1.4 V < COMP < 4.0 V, Note 2                                                           | 60                    | 90                    | -                      | dB   |

| Unity Gain Bandwidth                    | Note 2                                                                                 | 1.5                   | 2.5                   | _                      | MHz  |

| COMP Sink Current                       | COMP = 1.5 V, V <sub>FB</sub> = 2.7 V                                                  | 2.0                   | 6.0                   | _                      | mA   |

| COMP Source Current                     | COMP = 1.5 V, V <sub>FB</sub> = 2.3 V                                                  | -0.2                  | -0.5                  | -                      | mA   |

| COMP High Voltage                       | V <sub>FB</sub> = 2.3 V                                                                | 4.35                  | 4.8                   | 5.0                    | V    |

| COMP Low Voltage                        | V <sub>FB</sub> = 2.7 V                                                                | 0.4                   | 0.8                   | 1.2                    | V    |

| PS Ripple Rejection                     | FREQ = 120 Hz, Note 2                                                                  | 60                    | 85                    | _                      | dB   |

| SS Clamp, V <sub>COMP</sub>             | $V_{SS}$ = 2.5 V, $V_{FB}$ = 0 V, $I_{SET}$ = 2.0 V                                    | 2.4                   | 2.5                   | 2.6                    | V    |

| I <sub>LIM(SET)</sub> Clamp             | Note 2                                                                                 | 0.95                  | 1.0                   | 1.15                   | V    |

2. Guaranteed by design, not 100% tested in production.

| <b>ELECTRICAL CHARACTERISTICS (continued)</b> (Unless otherwise stated, specifications apply for -40°C < T <sub>A</sub> < 85°C,                                                                                                                            |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, 3.0 \text{ V} < \text{V}_{\text{C}} < 20 \text{ V}, 8.2 \text{ V} < \text{V}_{\text{CC}} < 20 \text{ V}, \text{R}_{\text{T}} = 12 \text{ k}\Omega, \text{C}_{\text{T}} = 390 \text{ pF}$ |  |

| Characteristic                | Test Conditions                                                                      | Min   | Тур   | Max   | Unit |

|-------------------------------|--------------------------------------------------------------------------------------|-------|-------|-------|------|

| Oscillator                    |                                                                                      |       |       |       |      |

| Accuracy                      | R <sub>T</sub> = 12 k, C <sub>T</sub> = 390 pF                                       | 230   | 255   | 280   | kHz  |

| Voltage Stability             | Delta Frequency 8.2 V < $V_{CC}$ < 20 V                                              | -     | 2.0   | 3.0   | %    |

| Temperature Stability         | $T_{MIN} < T_A < T_{MAX}$ , Note 3                                                   | -     | 8.0   | -     | %    |

| Min Charge & Discharge Time   | Note 3                                                                               | 0.333 | -     | -     | μs   |

| Duty Cycle Accuracy           | R <sub>T</sub> = 12 k, C <sub>T</sub> = 390 pF                                       | 70    | 77    | 83    | %    |

| Peak Voltage                  | Note 3                                                                               | _     | 3.0   | _     | V    |

| Valley Voltage                | Note 3                                                                               | _     | 1.5   | _     | V    |

| Valley Clamp Voltage          | 10 k Resistor to ground on R <sub>T</sub> C <sub>T</sub>                             | 1.2   | 1.4   | 1.6   | V    |

| Discharge Current             | -                                                                                    | 0.8   | 1.0   | 1.2   | mA   |

| Discharge Current             | TA = 25°C, Note 3                                                                    | 0.925 | 1.0   | 1.075 | mA   |

| Synchronization (CS51021A/3A) |                                                                                      |       |       |       | •    |

| Input Threshold               | -                                                                                    | 1.0   | 1.5   | 2.7   | V    |

| Output Pulsewidth             | -                                                                                    | 160   | 260   | 400   | ns   |

| Output High Voltage           | I <sub>SYNC</sub> = 100 μA                                                           | 3.5   | 4.3   | 4.8   | V    |

| Input Resistance              | Note 3                                                                               | 35    | 70    | 140   | kΩ   |

| Drive Delay                   | SYNC to GATE RESET                                                                   | 80    | 120   | 150   | ns   |

| Output Drive Current          | 1.0 k Load                                                                           | 1.25  | 2.0   | 3.5   | mA   |

| SLEEP (CS51022A/4A)           | · · · · ·                                                                            |       | •     | •     | •    |

| SLEEP Input Threshold         | Active High                                                                          | 1.0   | 1.5   | 2.7   | V    |

| SLEEP Input Current           | V <sub>SLEEP</sub> = 4.0 V                                                           | 11    | 25    | 46    | μA   |

| I <sub>CC</sub> @ SLEEP       | $V_{CC} \le 15 V$                                                                    | -     | 50    | 100   | μA   |

| GATE Driver                   | · · · · ·                                                                            |       | •     | •     | •    |

| HIGH Voltage                  | Measure $V_{C}$ – GATE, $V_{C}$ = 10 V, 150 mA Load                                  | -     | 1.5   | 2.2   | V    |

| LOW Voltage                   | Measure GATE – PGND, 150 mA SINK                                                     | -     | 1.2   | 1.5   | V    |

| HIGH Voltage Clamp            | V <sub>C</sub> = 20 V, 1.0 nF                                                        | 11    | 13.5  | 16    | V    |

| LOW Voltage Clamp             | Measured at 10 mA Output Current                                                     | -     | 0.6   | 0.8   | V    |

| Peak Current                  | V <sub>C</sub> = 20 V, 1.0 nF, Note 3                                                | -     | 1.0   | -     | А    |

| UVL Leakage                   | V <sub>C</sub> = 20 V measured at 0 V                                                | -     | -1.0  | -50   | μA   |

| RISE Time                     | Load = 1.0 nF, 1.0 V < GATE < 9.0 V,<br>V <sub>C</sub> = 20 V, T <sub>A</sub> = 25°C | _     | 60    | 100   | ns   |

| FALL Time                     | Load = 1.0 nF, 9.0 V > GATE > 1 .0 V,<br>V <sub>C</sub> = 20 V                       | _     | 15    | 40    | ns   |

| SLOPE Compensation            | · · · ·                                                                              |       |       |       |      |

| Charge Current                | SLOPE = 2.0 V                                                                        | -63   | -53   | -43   | μA   |

| COMP Gain                     | Fraction of slope voltage added to I <sub>SENSE</sub> ,<br>Note 3                    | 0.095 | 0.100 | 0.105 | V/V  |

| Discharge Voltage             | SYNC = 0 V                                                                           | _     | 0.1   | 0.2   | V    |

3. Guaranteed by design, not 100% tested in production.

| ELECTRICAL CHARACTERISTICS (continued) (Unless otherwise stated, specifications apply for -40°C < T <sub>A</sub> < 85°C                                                                                                                                                   | C, |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| $-40^{\circ}\text{C} < \text{T}_{\text{J}} < 150^{\circ}\text{C}, \ 3.0 \ \text{V} < \text{V}_{\text{C}} < 20 \ \text{V}, \ 8.2 \ \text{V} < \text{V}_{\text{CC}} < 20 \ \text{V}, \ \text{R}_{\text{T}} = 12 \ \text{k}\Omega, \ \text{C}_{\text{T}} = 390 \ \text{pF})$ |    |

| Characteristic                     | Test Conditions        | Min  | Тур   | Max  | Unit |

|------------------------------------|------------------------|------|-------|------|------|

| Current Sense                      | -                      |      |       |      |      |

| OFFSET Voltage                     | Note 4                 | 0.09 | 0.10  | 0.11 | V    |

| Blanking Time                      | _                      | -    | 55    | 160  | ns   |

| Blanking Disable Voltage           | Adjust V <sub>FB</sub> | 1.8  | 2.0   | 2.2  | V    |

| Second Current Threshold Gain      | _                      | 1.21 | 1.33  | 1.45 | V/V  |

| ISENSE Input Resistance            | -                      | _    | 5.0   | -    | kΩ   |

| Minimum On Time                    | GATE High to Low       | 30   | 70    | 110  | ns   |

| Gain                               | Note 4                 | 0.78 | 0.80  | 0.82 | V/V  |

| OV & UV Voltage Monitors           | -                      |      |       |      |      |

| OV Monitor Threshold               | -                      | 2.4  | 2.5   | 2.6  | V    |

| OV Hysteresis Current              | -                      | -10  | -12.5 | -15  | μΑ   |

| UV Monitor Threshold               | -                      | 1.38 | 1.45  | 1.52 | V    |

| UV Monitor Hysteresis              | _                      | 25   | 75    | 100  | mV   |

| SOFT START (SS)                    | -                      |      |       |      |      |

| Charge Current                     | SS = 2.0 V             | -70  | -55   | -40  | μA   |

| Discharge Current                  | SS = 2.0 V             | 250  | 1000  | _    | μΑ   |

| Charge Voltage, V <sub>SS</sub>    | -                      | 4.4  | 4.7   | 5.0  | V    |

| Discharge Voltage, V <sub>SS</sub> | _                      | 0.25 | 0.27  | 0.30 | V    |

4. Guaranteed by design, not 100% tested in production.

#### PACKAGE PIN DESCRIPTION

| PACKAGE PIN #     | PIN SYMBOL                    | FUNCTION                                                                                                                                              |

|-------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16 Lead SO Narrow |                               |                                                                                                                                                       |

| 1                 | GATE                          | External power switch driver with 1.0 A peak capability.                                                                                              |

| 2                 | I <sub>SENSE</sub>            | Current sense amplifier input.                                                                                                                        |

| 3                 | SYNC (CS51021A/3A)            | Bi-directional synchronization. Locks to the highest frequency.                                                                                       |

| 3                 | SLEEP (CS51022A/4A)           | Active high chip disable. In sleep mode, $V_{REF}$ and GATE are turned off.                                                                           |

| 4                 | SLOPE                         | Additional slope to the current sense signal. Internal current source charges the external capacitor.                                                 |

| 5                 | UV                            | Undervoltage protection monitor.                                                                                                                      |

| 6                 | OV                            | Overvoltage protection monitor.                                                                                                                       |

| 7                 | R <sub>T</sub> C <sub>T</sub> | Timing resistor $R_T$ and capacitor $C_T$ determine oscillator frequency and maximum duty cycle, $D_{MAX.}$                                           |

| 8                 | I <sub>SET</sub>              | Voltage at this pin sets pulse–by–pulse overcurrent threshold, and sec-<br>ond threshold (1.33 times higher) with Soft Start retrigger (hiccup mode). |

| 9                 | V <sub>FB</sub>               | Feedback voltage input. Connected to the error amplifier inverting input.                                                                             |

| 10                | COMP                          | Error amplifier output. Frequency compensation network is usually connected between COMP and $V_{FB}$ pins.                                           |

| 11                | SS                            | Charging external capacitor restricts error amplifier output voltage dur-<br>ing the start or fault conditions (hiccup).                              |

| 12                | LGND                          | Logic ground.                                                                                                                                         |

#### PACKAGE PIN DESCRIPTION (continued)

| PACKAGE PIN #     | PIN SYMBOL       | FUNCTION                              |

|-------------------|------------------|---------------------------------------|

| 16 Lead SO Narrow |                  |                                       |

| 13                | V <sub>REF</sub> | 5.0 V reference voltage output.       |

| 14                | V <sub>CC</sub>  | Logic supply voltage.                 |

| 15                | PGND             | Output power stage ground connection. |

| 16                | V <sub>C</sub>   | Output power stage supply voltage.    |

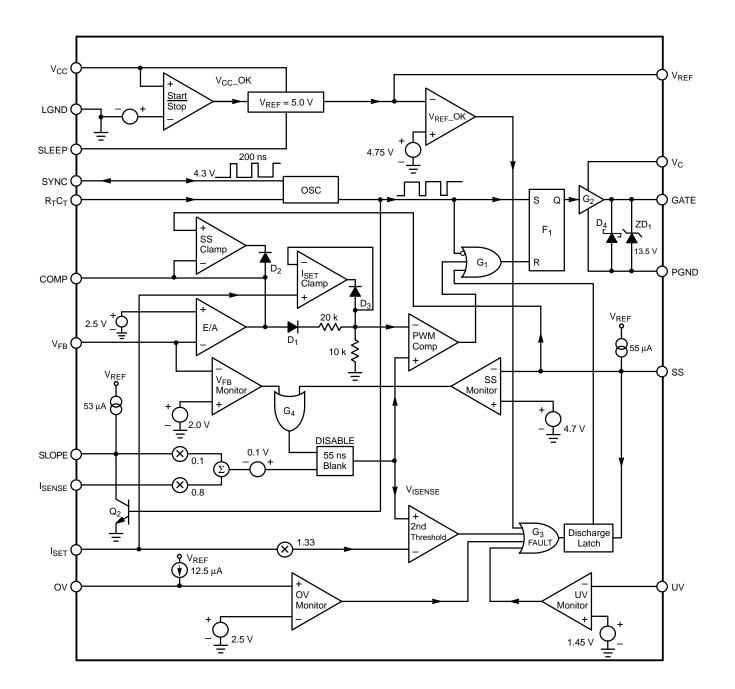

Figure 2. Block Diagram

#### **CIRCUIT DESCRIPTION**

#### **Current Sense and Protection**

The current is monitored at the ISENSE pin. The CS51021A/2A/3A/4A has leading edge blanking circuitry that ignores the first 55 ns of each switching period. Blanking is disabled when VFB is less than 2.0 V so that the minimum on-time of the controller does not have an additional 55 ns of delay time during fault conditions. For the remaining portion of the switching period, the current sense signal, combined with a fraction of the slope compensation voltage, is applied to the positive input of the PWM comparator where it is compared with the divided by three error amplifier output voltage. The pulse-by-pulse overcurrent protection threshold is set by the voltage at the ISET pin. This voltage is passed through the ISET Clamp and appears at the non-inverting input of the PWM comparator, limiting its dynamic range according to the following formula:

Overcurrent Threshold =  $0.8 \times VI(SENSE)$ + 0.1 V + 0.1 VSLOPE

where

VI(SENSE) is voltage at the ISENSE pin.

and

VSLOPE is voltage at the SLOPE pin.

During extreme overcurrent or short circuit conditions, the slope of the current sense signal will become much steeper than during normal operation. Due to loop propagation delay, the sensed signal will overshoot the pulse–by–pulse threshold eventually reaching the second overcurrent protection threshold which is 1.33 times higher than the first threshold and is described by the following equation:

#### 2nd Threshold = $1.33 \times VI(SET)$

Exceeding the second threshold will reset the Soft Start capacitor  $C_{SS}$  and reinitiate the Soft Start sequence, repeating for as long as the fault condition persists.

#### Soft Start

During power up, when the output filter capacitor is discharged and the output voltage is low, the voltage across the Soft Start capacitor ( $V_{SS}$ ) controls the duty cycle. An internal current source of 55  $\mu$ A charges  $C_{SS}$ . The maximum error amplifier output voltage is clamped by the SS Clamp. When the Soft Start capacitor voltage exceeds the error amplifier output voltage, the feedback loop takes over the duty cycle control. The Soft Start time can be estimated with the following formula:

#### $t_{SS} = 9 \times 10^4 \times C_{SS}$

The Soft Start voltage,  $V_{SS},$  charges and discharges between 0.25 V and 4.7 V.

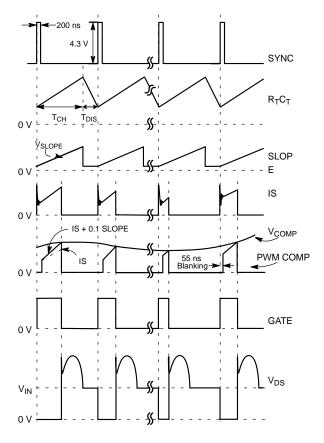

#### Figure 3. Typical Waveforms

#### THEORY OF OPERATION

#### Powering the IC

The IC has two supply and two ground pins. V<sub>C</sub> and PGND pins provide high speed power drive for the external power switch. V<sub>CC</sub> and LGND pins power the control portion of the IC. The internal logic monitors the supply voltage, V<sub>CC</sub>. During abnormal operating conditions, the output is held low. The CS51021A/2A/3A/4A requires only 75  $\mu$ A of startup current.

#### Voltage Feedback

The output voltage is monitored via the  $V_{FB}$  pin and is compared with the internal 2.5 V reference. The error amplifier output minus one diode drop is divided by 3 and connected to the negative input of the PWM comparator. The positive input of the PWM comparator is connected to the modified current sense signal. The oscillator turns the external power switch on at the beginning of each cycle. When current sense ramp voltage exceeds the reference side of PWM comparator, the output stage latches off. It is turned on again at the beginning of the next oscillator cycle.

#### **Slope Compensation**

DC–DC converters with current mode control require a current sense signal with slope compensation to avoid instability at duty cycles greater than 50%. Slope capacitor C<sub>S</sub> is charged by an internal 53  $\mu$ A current source and is discharged during the oscillator discharge time. The slope compensation voltage is divided by 10 and is added to the current sense voltage, V<sub>I(SENSE)</sub>. The signal applied to the input of the PWM comparator is a combination of these two voltages. The slope compensation, dV<sub>SLOPE</sub>/dt, is calculated using the following formula:

$$\frac{dV_{\text{SLOPE}}}{dt} = 0.1 \times \frac{53 \,\mu\text{A}}{C_{\text{S}}}$$

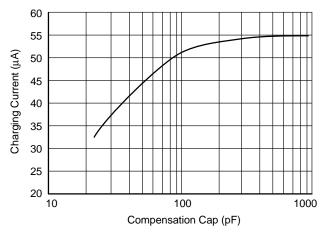

It should be noted that internal capacitance of the IC will cause an error when determining slope compensation capacitance  $C_S$ . This error is typically small for large values of  $C_S$ , but increases as  $C_S$  becomes small and comparable to the internal capacitance. The effect is apparent as a reduction in charging current due to the need to charge the internal capacitance in parallel with  $C_S$ .Figure 4 shows a typical curve indicating this decrease in available charging current.

Figure 4. The Slope Compensation Pin Charge Current Reduces When a Small Capacitor Is Used.

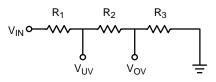

#### Undervoltage (UV) and Overvoltage (OV) Monitor

Two independent comparators monitor OV and UV conditions. A string of three resistors is connected in series between the monitored voltage (usually the input voltage) and ground (see Figure 5). When voltage at the OV pin exceeds 2.5 V, an overvoltage condition is detected and GATE shuts down. An internal 12.5  $\mu$ A current source turns on and feeds current into the external resistor, R<sub>3</sub>, creating a hysteresis determined by the value of this resistor (the higher the value, the greater the hysteresis). The hysteresis voltage of the OV monitor is determined by the following formula:

$$VOV(HYST) = 12.5 \ \mu A \times R_3$$

where R<sub>3</sub> is a resistor connected from the OV pin to ground.

When the monitored voltage is low and the UV pin is less than 1.45 V, GATE shuts down. The UV pin has fixed 75 mV hysteresis.

Both OV and UV conditions are latched until the Soft Start capacitor is discharged. This way, every time a fault condition is detected the controller goes through the power up sequence.

Figure 5. UV/OV Monitor Divider

To calculate the OV?UV resistor divider :

1. Solve for R<sub>3</sub>, based on OV hysteresis requirements.

$$R_{3} = \frac{V_{OV}(HYST) \times 2.5 V}{V_{MAX} \times 12.5 \mu A}$$

where  $V_{\rm OV(HYST)}$  is the desired amount of overvoltage hysteresis, and  $V_{\rm MAX}$  is the input voltage at which the supply will shut down.

2. Find the total impedance of the divider.

$$R_{TOT} = R_1 + R_2 + R_3 = \frac{V_{MAX} \times R_3}{2.5}$$

3. Determine the value of  $R_2$  from the UV threshold conditions.

$$\mathsf{R}_2 = \frac{1.45 \times \mathsf{R}_{TOT}}{\mathsf{V}_{MIN}} - \mathsf{R}_3$$

where  $V_{\mbox{MIN}}$  is the UV voltage at which the supply will shut down.

- 4. Calculate  $R_1$ .

- $R_1 = R_{TOT} R_2 R_3$

- 5. The undervoltage hysteresis is given by :

$$V_{UV(HYST)} = \frac{V_{MIN} \times 0.075}{1.45}$$

#### V<sub>REF</sub> Monitor

The 5.0 V reference voltage is internally monitored to ensure that it remains within specifications. The monitor, which outputs a fault, can be tripped by two methods:

- If the reference voltage drops below 4.75 V

- If V<sub>CC</sub> falls below the STOP threshold

As indicated in the block diagram, any fault causes the output to stop switching and begins the discharge of the Soft Start capacitor  $C_{SS}$ .

#### Synchronization

A bi-directional synchronization is provided to synchronize several controllers. When SYNC pins are connected together, the converters will lock to the highest switching frequency. The fastest controller becomes the master, producing a 4.3 V, 200 ns pulse train. Only one, the highest frequency SYNC signal, will appear on the SYNC line.

#### Sleep

The sleep input is an active high input. The CS51022A/4A is placed in sleep mode when SLEEP is driven high. In sleep mode, the controller and MOSFET are turned off. Connect to GND for normal operation. The sleep mode operates at VCC  $\leq$  15 V.

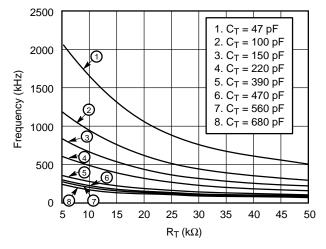

Figure 6. Frequency vs. R<sub>T</sub> for Discrete Capacitor Values

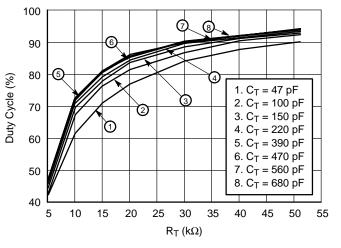

#### **Oscillator and Duty Cycle Limit**

The switching frequency is set by  $R_T$  and  $C_T$  connected to the  $R_TC_T$  pin.  $C_T$  charges and discharges between 3.0 V and 1.5 V.

The maximum duty cycle is set by the ratio of the on time,  $t_{ON}$ , and the whole period,  $T = t_{ON} + t_{OFF}$ . Because the timing capacitor's discharge current is trimmed, the maximum duty cycle is well defined. It is determined by the ratio between the timing resistor  $R_T$  and the timing capacitor  $C_T$ . Refer to figures 6 and 7 to select appropriate values for  $R_T$  and  $C_T$ .

$$f_{SW} = \frac{1}{T_{SW}}; T_{SW} = t_{CH} + t_{DIS}$$

Figure 7. Duty Cycle vs. R<sub>T</sub> for Discrete Capacitor Values

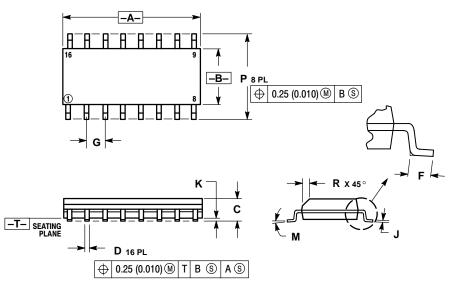

#### PACKAGE DIMENSIONS

SO-16 **D SUFFIX** CASE 751B-05 **ISSUE J**

- NOTES:

DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 9.80        | 10.00 | 0.386 | 0.393 |

| В   | 3.80        | 4.00  | 0.150 | 0.157 |

| C   | 1.35        | 1.75  | 0.054 | 0.068 |

| D   | 0.35        | 0.49  | 0.014 | 0.019 |

| F   | 0.40        | 1.25  | 0.016 | 0.049 |

| G   | 1.27        | BSC   | 0.050 | ) BSC |

| J   | 0.19        | 0.25  | 0.008 | 0.009 |

| K   | 0.10        | 0.25  | 0.004 | 0.009 |

| Μ   | 0 °         | 7°    | 0°    | 7°    |

| Р   | 5.80        | 6.20  | 0.229 | 0.244 |

| R   | 0.25        | 0.50  | 0.010 | 0.019 |

#### PACKAGE THERMAL DATA

| Parameter        |         | SO-16 | Unit |

|------------------|---------|-------|------|

| R <sub>OJC</sub> | Typical | 28    | °C/W |

| $R_{\Theta JA}$  | Typical | 115   | °C/W |

# <u>Notes</u>

**ON Semiconductor** and without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.