## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

### Pulse Width Modulation Amplifiers

#### **FEATURES**

- ♦ 500kHz SWITCHING

- ♦ FULL BRIDGE OUTPUT 5-40V (80V P-P)

- ◆ 5A OUTPUT

- ♦ 1 IN<sup>2</sup> FOOTPRINT

- ◆ FAULT PROTECTION

- **♦ SHUTDOWN CONTROL**

- ♦ SYNCHRONIZABLE CLOCK

- ♦ HERMETIC PACKAGE

#### **APPLICATIONS**

- **♦ HIGH FIDELITY AUDIO AMPLIFIER**

- ◆ BRUSH TYPE MOTOR CONTROL

- ♦ VIBRATION CANCELLING AMPLIFIER

#### **DESCRIPTION**

The SA07 amplifier is a 40 volt, 500kHz PWM amplifier. The full bridge output circuit provides 5 amps of continuous drive current for applications as diverse as high fidelity audio and brush type motors. Clock output and input pins can be used for synchronization with other amplifiers or an externally generated clock. An integrator amplifier is provided. Direct access to the pwm input is provided for connection to digital motion control circuits. Protection circuits guard against thermal overloads as well as shorts to supply or ground. The current limit is programmable with one or two external resistors depending on the application. A shutdown input disables all output bridge drivers. The 18 pin steel package is hermetically sealed.

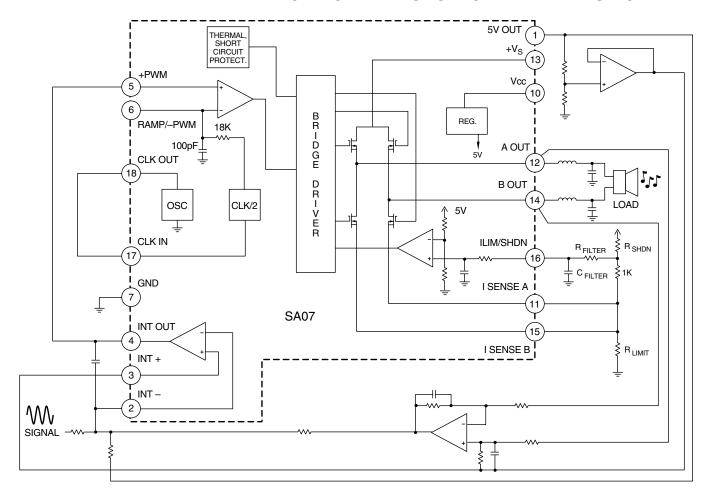

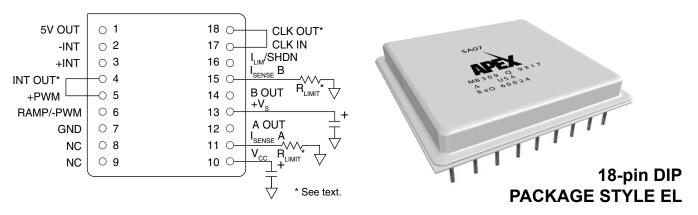

# BLOCK DIAGRAM AND TYPICAL APPLICATION CONNECTIONS HIGH FIDELITY AUDIO

#### **EXTERNAL CONNECTIONS**

Case tied to Pin 7. Allow no current in case. Bypassing of supplies is required. If +PWM > RAMP then A OUT > B OUT.

### 1. CHARACTERISTICS AND SPECIFICATIONS

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                               | Symbol | Min  | Max  | Units |

|-----------------------------------------|--------|------|------|-------|

| SUPPLY VOLTAGE, +Vs to GND, 10mS surge  |        |      | 60   | V     |

| SUPPLY VOLTAGE, +V <sub>cc</sub> to GND |        |      | 16   | V     |

| OUTPUT CURRENT, peak                    |        |      | 7.5  | Α     |

| POWER DISSIPATION, internal (Note 3)    |        |      | 80   | W     |

| TEMPERATURE, pin solder, 10s            |        |      | 300  | °C    |

| TEMPERATURE, junction (Note 1)          |        |      | 150  | °C    |

| TEMPERATURE, storage                    |        | -65  | 150  | °C    |

| OPERATING TEMPERATURE RANGE, case       |        | -55  | 125  | °C    |

| INPUTS                                  |        | -0.4 | +5.4 | V     |

**CAUTION** The SA07 is constructed from MOSFET transistors. ESD handling procedures must be observed.

The internal substrate contains beryllia (BeO). Do not break the seal. If accidentally broken, do not crush, machine, or subject to temperatures in excess of 850°C to avoid generating toxic fumes.

### **SPECIFICATIONS**

| Parameter                          | (Note 1) | Test Conditions                 | Min   | Тур | Max             | Units |

|------------------------------------|----------|---------------------------------|-------|-----|-----------------|-------|

| ERROR AMP, CLOCK REF               | (Note 4) |                                 |       |     |                 |       |

| OFFSET VOLTAGE                     |          |                                 |       |     | 10              | mV    |

| BIAS CURRENT                       |          |                                 |       |     | 50              | pA    |

| OFFSET CURRENT                     |          |                                 |       |     | 30              | pA    |

| COMMON MODE VOLTAGE                | RANGE    |                                 | 0     |     | 3               | V     |

| COMMON MODE REJECTION              | ON, DC   |                                 | 70    |     |                 | dB    |

| SLEW RATE                          |          |                                 |       | 12  |                 | V/µS  |

| OPEN LOOP GAIN                     |          |                                 |       | 100 |                 | dB    |

| GAIN BANDWIDTH PRODU               | CT       |                                 |       | 10  |                 | MHz   |

| CLOCK OUT                          |          |                                 | 0.98  | 1   | 1.02            | MHz   |

| CLOCK OUT, high level              |          |                                 | 4.7   |     | 5.3             | V     |

| CLOCK OUT, low level               |          |                                 | 0     |     | 0.2             | V     |

| 5V OUT                             |          | LOAD ≤ 5mA                      | 4.988 | 5   | 5.012           | V     |

| OUTPUT                             |          |                                 |       |     |                 |       |

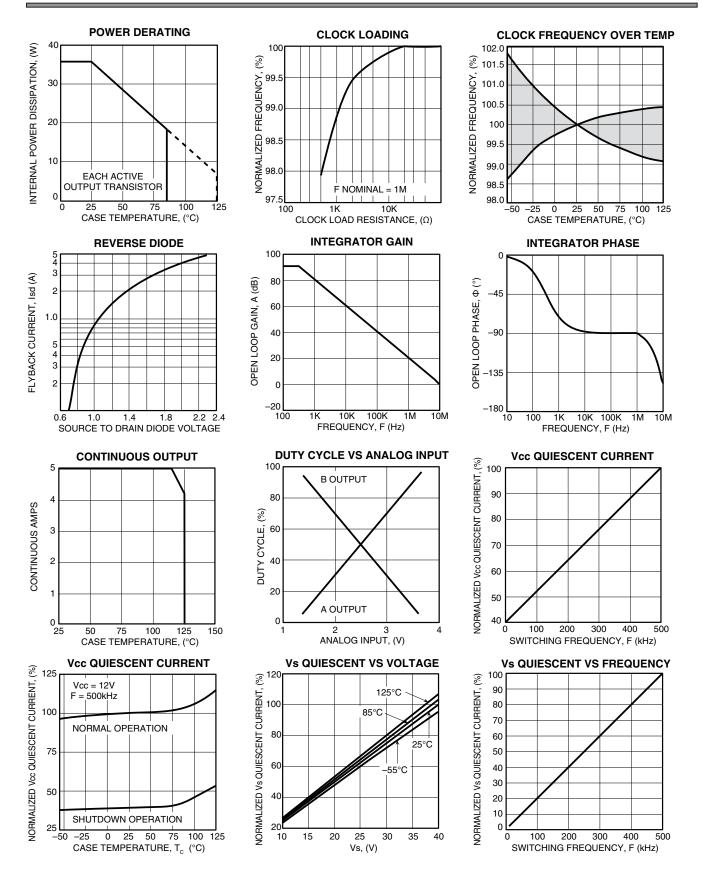

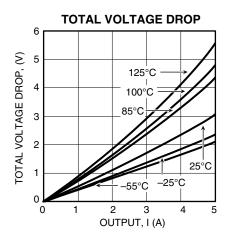

| EFFICIENCY, 5A output              |          | V <sub>S</sub> = 40V            |       | 94  |                 | %     |

| SWITCHING FREQUENCY                |          |                                 |       | 500 |                 | kHz   |

| CURRENT, continuous                |          |                                 | 5     |     |                 | А     |

| CURRENT, peak                      | (Note 4) | 100 ms, 10% duty cycle          | 7     |     |                 | Α     |

| R <sub>DS(ON)</sub>                | (Note 4) |                                 |       |     | 0.55            | Ω     |

| POWER SUPPLY                       |          |                                 |       |     |                 |       |

| VOLTAGE, V <sub>CC</sub>           |          | Full temperature range          | 10    | 12  | 16              | V     |

| VOLTAGE, V <sub>s</sub>            |          | Full temperature range          | 5     |     | 40              | V     |

| CURRENT, V <sub>CC</sub>           |          | Switching                       |       |     | 50              | mA    |

| CURRENT, V <sub>s</sub>            |          | Switching, no load              |       |     | 90              | mA    |

| INPUTS                             | (Note 4) |                                 |       |     |                 |       |

| I <sub>LIM</sub> /SHDN, trip point |          |                                 | 90    |     | 110             | mV    |

| –PWM, +PWM, low level              |          |                                 | 0     |     | 0.8             | V     |

| –PWM, +PWM, high level             |          |                                 | 2.7   |     | V <sub>cc</sub> | V     |

| CLOCK IN, low level                |          |                                 | 0     |     | 0.3             | V     |

| CLOCK IN, high level               |          |                                 | 3     |     | 5.6             | V     |

| THERMAL                            | (Note 2) |                                 |       |     |                 |       |

| RESISTANCE, junction to ca         | se       | Full temperature range          |       |     | 3.5             | °C/W  |

| RESISTANCE, junction to air        |          | Full temperature range          |       | 15  |                 | °C/W  |

| TEMPERATURE RANGE, ca              | se       | Meets full range specifications | -25   |     | 85              | °C    |

#### NOTES:

- 1. All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical performance characteristics and specifications are derived from measurements taken at typical supply voltages and  $T_{\rm C}$  = 25°C.

- 2. Long term operation at the maximum junction temperature will result in reduced product life. Derate internal power dissipation to achieve high MTTF. For guidance, refer to the heatsink datasheet.

- 3. 40W in each of the two active output transistors on at any one time.

- 4. Min max values guaranteed but not tested.

#### **GENERAL**

Please read Application Note 30 on "PWM Basics". Refer to Application Note 1 "General Operating Considerations" for helpful information regarding power supplies, heat sinking and mounting. Visit www.apexmicrotech. com for design tools that help automate pwm filter design and heat sink selection. The "Application Notes" and "Technical Seminar" sections contain a wealth of information on specific types of applications. Information on package outlines, heat sinks, mounting hardware and other accessories are located in the "Packages and Accessories" section. Evaluation Kits are available for most Apex product models, consult the "Evaluation Kit" section for details. For the most current version of all Apex product data sheets, visit www.apexmicrotech.com.

#### **CLOCK CIRCUIT AND RAMP GENERATOR**

The clock frequency is internally set to a frequency of approximately 1MHz. The CLK OUT pin will normally be tied to the CLK IN pin. The clock is divided by two and applied to an RC network which produces a ramp signal at the RAMP pin. An external clock signal can be applied to the CLK IN pin for synchronization purposes. If a clock frequency lower than 1MHz is chosen an external capacitor must be tied to the RAMP pin. This capacitor, which parallels an internal capacitor, must be selected so that the ramp oscillates 2.5 volts p-p with the lower peak 1.25 volts above ground.

#### **BYPASSING**

Adequate bypassing of the power supplies is required for proper operation. Failure to do so can cause erratic and low efficiency operation as well as excessive ringing at the outputs. The Vs supply should be bypassed with at least a 1µF ceramic capacitor in parallel with another low ESR capacitor of at least 10µF per amp of output current. Capacitor types rated for switching applications are the only types that should be considered. The bypass capacitors must be physically connected directly to the power supply pins. Even one inch of lead length will cause excessive ringing at the outputs. This is due to the very fast switching times and the inductance of the lead connection. The bypassing requirements of the  $V_{CC}$  supply are less stringent, but still necessary. A 0.1µF to 0.47µF ceramic capacitor connected directly to the  $V_{CC}$  pin will suffice.

#### NOISE FILTERING

Switching noise can enter the SA07 through the INT OUT to +PWM connection. A wise precaution is to low pass filter this connection. Adjust the pass band of the filter to 10 times the bandwidth required by the application. Keep the resistor value to 100 ohms or less since this resistor becomes part of the hysteresis circuit on the pwm comparator.

#### **PCB LAYOUT**

The designer needs to appreciate that the SA07 combines in one circuit both high speed high power switching and low level analog signals. Certain layout rules of thumb must be considered when a circuit board layout is designed using the SA07:

- 1. Bypassing of the power supplies is critical. Capacitors must be connected directly to the power supply pins with very short lead lengths (well under 1 inch). Ceramic chip capacitors are best.

- 2. Make all ground connections with a star pattern at pin 7.

- 3. Beware of capacitive coupling between output connections and signal inputs through the parasitic capacitance between layers in multilayer PCB designs.

- 4. Do not run small signal traces between the pins of the output section (pins 11-16).

- 5. Do not allow high currents to flow into the ground plane.

- 6. Separate switching and analog grounds and connect the two only at pin 7 as part of the star pattern.

#### **INTEGRATOR**

The integrator provides the inverted signal for negative feedback and also the open loop gain for the overall application circuit accuracy. Recommended value of  $C_{INT}$  is 10 pF for stability. However, poles and zeroes can be added to the circuit for overall loop stability as required.

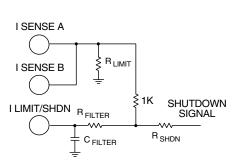

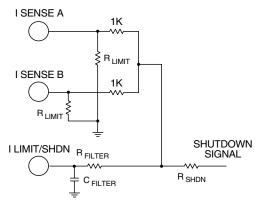

#### **CURRENT LIMIT**

There are two load current sensing pins, I SENSE A and I SENSE B. The two pins can be shorted in the voltage mode connection but both must be used in the current mode connection (see figures A and B). It is recommended that  $R_{\text{LIMIT}}$  resistors be non-inductive. Load current flows in the I SENSE pins. To avoid errors due to lead lengths connect the I LIMIT/SHDN pin directly to the  $R_{\text{LIMIT}}$  resistors (through the filter network and shutdown divider resistor) and connect the  $R_{\text{LIMIT}}$  resistors directly to the GND pin. Do not connect  $R_{\text{LIMIT}}$  sense resistors to the ground plane.

FIGURE A. CURRENT LIMIT WITH SHUTDOWN VOLTAGE MODE.

FIGURE B. CURRENT LIMIT WITH SHUTDOWN CURRENT MODE.

Switching noise spikes will invariably be found at the I SENSE pins. The noise spikes could trip the current limit threshold which is only 100 mV.  $R_{\text{FILTER}}$  and  $C_{\text{FILTER}}$  should be adjusted so as to reduce the switching noise well below 100 mV to prevent false current limiting. The sum of the DC level plus the noise peak will determine the current limiting value. As in most switching circuits it may be difficult to determine the true noise amplitude without careful attention to grounding of the oscilloscope probe. Use the shortest possible ground lead for the probe and connect exactly at the GND terminal of the amplifier. Suggested starting values are  $C_{\text{FILTER}} = 0.001 \text{uF}$ ,  $R_{\text{FILTER}} = 5 \text{k}$ .

The required value of R<sub>I MIT</sub> in voltage mode may be calculated by:

$$R_{IIMIT} = 0.1 \text{ V} / I_{IIMIT}$$

where  $R_{\text{LIMIT}}$  is the required resistor value, and  $I_{\text{LIMIT}}$  is the maximum desired current. In current mode the required value of each  $R_{\text{LIMIT}}$  is 2 times this value since the sense voltage is divided down by 2 (see Figure B). If  $R_{\text{SHDN}}$  is used it will further divide down the sense voltage. The shutdown divider network will also have an effect on the filtering circuit.

#### SHUTDOWN

The shutdown circuitry makes use of the internal current limiting circuitry. The two functions may be externally combined in voltage and current modes as shown below in Figures A and B. The  $R_{\text{LIMIT}}$  resistors will normally be very low values and can be considered zero for this application. In Figure A,  $R_{\text{SHDN}}$  and 1K form a voltage divider for the shutdown signal. After a suitable noise filter is designed for the current limit, adjust the value of  $R_{\text{SHDN}}$  to give a minimum 110 mV of shutdown signal at the I LIMIT/SHDN pin when the shutdown signal is high. Note that  $C_{\text{FILTER}}$  will filter both the current limit noise spikes and the shutdown signal. Shutdown and current limit operate on each cycle of the internal switching rate. As long as the shutdown signal is high the output will be disabled.

#### PROTECTION CIRCUITS

Circuits monitor the temperature and load on each of the bridge output transistors. On each cycle should any fault condition be detected all output transistors in the bridge are shut off. Faults protected against are: shorts across the outputs, shorts to ground, and over temperature conditions. Should any of these faults be detected, the output transistors will be latched off \*. In addition there is a built in dead time during which all the output transistors are off. The dead time removes the possibility of a momentary conduction path through the upper and lower transistors of each half bridge during the switching interval. Noise or flyback may be observed at the outputs during this time due to the high impedance of the outputs in the off state. This will vary with the nature of the load.

\* To restart the SA07 remove the fault and recycle V<sub>CC</sub> or, alternatively, toggle the I LIMIT/SHDN (pin16) with a shut down pulse.

#### CONTACTING CIRRUS LOGIC SUPPORT

For all Apex Precision Power product questions and inquiries, call toll free 800-546-2739 in North America. For inquiries via email, please contact tucson.support@cirrus.com.

International customers can also request support by contacting their local Cirrus Logic Sales Representative. To find the one nearest to you, go to www.cirrus.com

#### IMPORTANT NOTICE

Cirrus Logic, Inc. and its subsidiaries ("Cirrus") believe that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, indemnification, and limitation of liability. No responsibility is assumed by Cirrus for the use of this information, including use of this information as the basis for manufacture or sale of any items, or for infringement of patents or other rights of third parties. This document is the property of Cirrus and by furnishing this information, Cirrus grants no license, express or implied under any patents, mask work rights, copyrights, trademarks, trade secrets or other intellectual property rights. Cirrus owns the copyrights associated with the information contained herein and gives consent for copies to be made of the information only for use within your organization with respect to Cirrus integrated circuits or other products of Cirrus. This consent does not extend to other copying such as copying for general distribution, advertising or promotional purposes, or for creating any work for resale.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). CIRRUS PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED TO BE SUITABLE FOR USE IN PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF CIRRUS PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND CIRRUS DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY CIRRUS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF CIRRUS PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY CIRRUS, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

Cirrus Logic, Cirrus, and the Cirrus Logic logo designs, Apex and Apex Precision Power are trademarks of Cirrus Logic, Inc. All other brand and product names in this document may be trademarks or service marks of their respective owners.