# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# M02095/6

# 3.3/5V Laser Driver / Limiting Amplifier for Operation to 2.5 Gbps

The M02095 and M02096 are integrated laser drivers and limiting amplifiers for applications to 1.25 Gbps and 2.5 Gbps, respectively. The laser driver modulation output can be AC or DC coupled to an FP/DFB laser. The devices can operate from a 3.3V or 5V supply.

The devices include monitors for bias and laser power. Integrated safety circuitry provides latched bias and modulation current shutdown if a fault condition is detected and provides an internal  $V_{CC}$  switch.

The limiting amplifier also includes a programmable signal-level detector, allowing the user to set thresholds at which the logic outputs are enabled. PECL or CML outputs are available on the limiting amplifier.

Configuration logic provides flexibility in setting data path polarity, safety logic configuration, and LOS behavior.

#### **Applications**

- 2.5 Gbps STM-16/OC-48 SDH/SONET (M02096)

- 1.06 and 2.12 Gbps Fibre Channel (M02095/6)

- 1.25 Gbps Ethernet (M02095/6)

- 1.25 Gbps SDH/SONET (M02095/6)

- 2.67 Gbps SDH/SONET with FEC (M02096)

- SDH/SONET 155 Mbps Transceivers

- · FTTx and Media Converters

#### **Features**

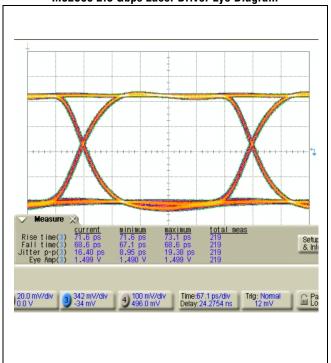

- High speed operation; suitable for applications to 2.5 Gbps. 55 ps typical rise/fall time into  $25\Omega$

- Independently programmable bias and modulation currents Modulation current to 85 mA and bias current to 100 mA

#### Features (con't)

- Integrated power supply switch for redundant shutdown under a fault condition

- Temperature compensation for modulation current

- Automatic Power Control

- · SFP compliant safety circuitry (configurable)

- 3.3 mV typical input limiting amp sensitivity at 2.5 Gbps

- · CML or PECL limiting amplifier outputs

- · Limiting amplifier includes integrated DC offset cancellation circuit

- · Polarity Control for both the driver and limiting amplifier data paths

- Operates with 3.3V or 5V supply with an internal auto-sensing regulator that enables with 5V supplies and is bypassed with 3.3V supplies

- Powers 3.3V ROSAs from its Receiver Regulator output enabling true 3.3/5V designs using all 3.3V Mindspeed TIAs

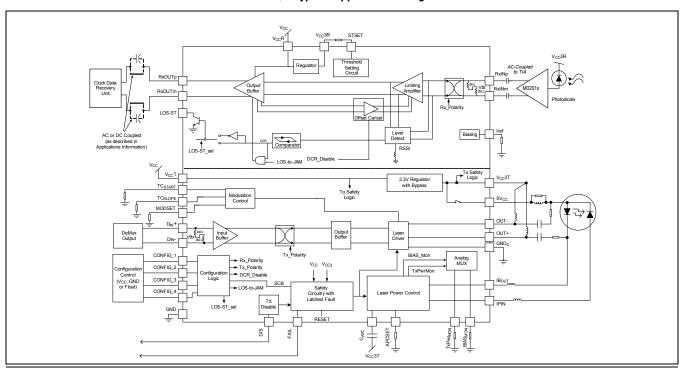

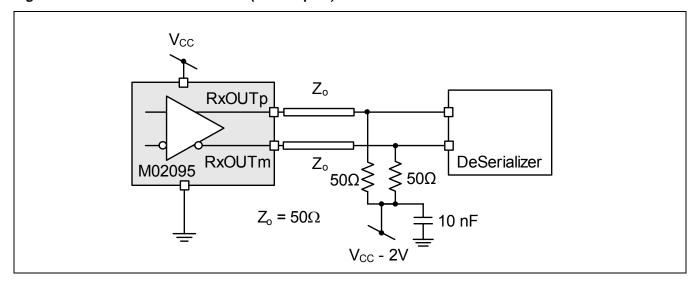

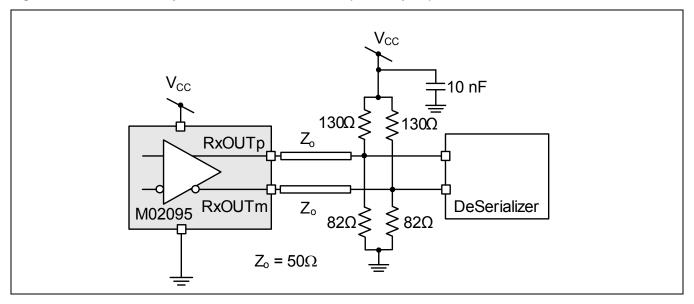

#### M02095/6 Typical Applications Diagram

## **Ordering Information**

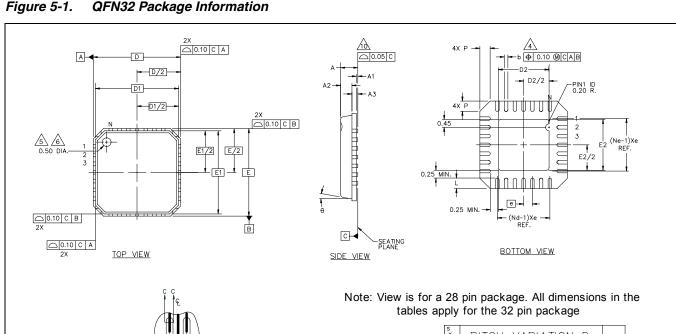

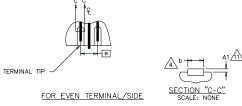

| Part Number | Package | Operating Temperature |

|-------------|---------|-----------------------|

| M02095G-XX* | QFN32   | −40°C to 95°C         |

| M02096G-XX* | QFN32   | −40°C to 95°C         |

<sup>\*</sup> The letter "G" designator after the part number indicates that the device is RoHS-compliant. Refer to www.mindspeed.com for additional information.

# **Revision History**

| Revision | Level       | Date          | ASIC<br>Revision | Description                                                                                                                          |

|----------|-------------|---------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| E        | Release     | August 2007   | -12              | Finalize limiting amplifier jitter specifications, combine laser driver and limiting amplifier supply current together in Table 1-3. |

| D        | Preliminary | May 2007      | -12              | Add TxPwrMon and BIAS <sub>MON</sub> pins to device. Update DC specifications, Functional Description and Applications Information.  |

| С        | Preliminary | November 2006 | -11              | Reflect current device pinout.                                                                                                       |

| В        | Advance     | August 2006   | -11              | Update several specifications based on initial device evaluation.                                                                    |

| А        | Advance     | June 2006     | NA               | Initial Release.                                                                                                                     |

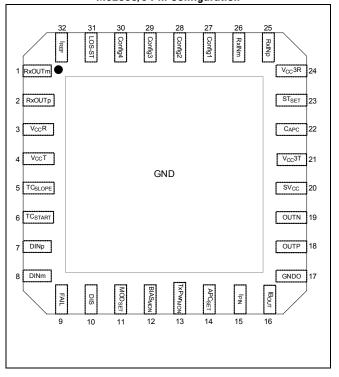

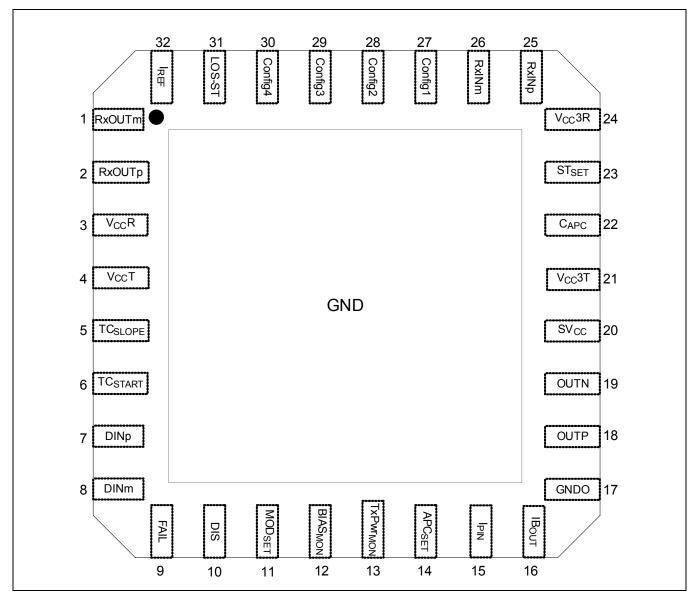

#### M02095/6 Pin Configuration

# 1.0 Product Specification

# 1.1 Absolute Maximum Ratings

These are the absolute maximum ratings at or beyond which the IC can be expected to fail or be damaged. Reliable operation at these extremes for any length of time is not implied.

Table 1-1. Absolute Maximum Ratings

| Symbol                | Parameter                                                                           | Rating       | Units |

|-----------------------|-------------------------------------------------------------------------------------|--------------|-------|

| V <sub>CC</sub>       | Power supply voltage                                                                | -0.4 to +6.0 | V     |

| V <sub>CC</sub> 3     | 3.3V power supply voltage (when V <sub>CC</sub> 3 is connected to V <sub>CC</sub> ) | -0.4 to +4.0 | V     |

| T <sub>STG</sub>      | Storage temperature                                                                 | -65 to +150  | °C    |

| IB <sub>OUT_MAX</sub> | Maximum bias output current at IB <sub>OUT</sub>                                    | 140          | mA    |

| I <sub>MOD_MAX</sub>  | Maximum modulation current                                                          | 120          | mA    |

# 1.2 Recommended Operating Conditions

Table 1-2. Recommended Operating Conditions

| Parameter                                                                                                                                 | Rating                          | Units |

|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|

| Power supply: ( $V_{CC}$ -GND) (apply no potential to $V_{CC}$ 3) or ( $V_{CC}$ 3-GND) (connect $V_{CC}$ to same potential as $V_{CC}$ 3) | +4.7 to 5.5V or<br>+3.3V ± 7.5% | V     |

| Junction temperature                                                                                                                      | -40 to +125                     | °C    |

| Operating ambient                                                                                                                         | -40 to +95                      | °C    |

## 1.3 DC Characteristics

#### 1.3.1 Device Power

$V_{CC}$  = 3.05 to 3.55V or 4.7 to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $IB_{OUT}$  = 20 mA,  $I_{MOD}$  = 30 mA.

Table 1-3. Device Power

| Symbol          | Parameter                                                        | Conditions                                                                                 | Minimum | Typical | Maximum | Units |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| I <sub>CC</sub> | V <sub>CC</sub> (sum of V <sub>CC</sub> T and V <sub>CC</sub> R) | Using external 3.3V supply V <sub>CC</sub> = 3.3V <sup>(1)</sup> With CML Outputs (M02096) | -       | 68      | 96      | mA    |

|                 | supply current                                                   | With PECL Outputs (M02095 - includes PECL load)                                            | _       | 93      | 108     |       |

|                 |                                                                  | Additional current when operating from 5V supply <sup>(2)</sup>                            | _       | 4       | -       |       |

#### **NOTES:**

- 1. Excludes bias and modulation currents delivered to the laser. Maximum supply current based on maximum settings for bias and modulation.

- 2. Bias and modulation currents add directly to power supply current in 5V applications; additional supply current noted excludes these currents.

#### 1.3.2 DC Electrical Characteristics - Laser Driver

$V_{CC}$  = 3.05 to 3.55V or 4.7 to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $IB_{OUT}$  = 20 mA,  $I_{MOD}$  = 30 mA.

Table 1-4. DC Electrical Characteristics - Laser Driver

| Symbol               | Parameter                                                                                                                                 | Conditions                                                         | Minimum                  | Typical                     | Maximum | Units |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------|-----------------------------|---------|-------|

| V <sub>CC</sub> 3THL | 3.3V supply detection (low voltage) threshold <sup>(1)</sup>                                                                              |                                                                    | 2.5                      | 2.8                         | 3.05    | V     |

| V <sub>CC</sub> 3HH  | 3.3V supply detection (high voltage) threshold <sup>(1)</sup>                                                                             |                                                                    | 3.65                     | 3.95                        | 4.2     | V     |

| V <sub>CC</sub> 5THL | 5V supply detection (low voltage) threshold                                                                                               |                                                                    | 3.9                      | 4.35                        | 4.7     | V     |

| V <sub>CC</sub> 5THH | 5V supply detection (high voltage) threshold                                                                                              |                                                                    | 5.5                      | -                           | _       | V     |

| V <sub>MODSET</sub>  | Modulation current ref.                                                                                                                   | Voltage reference for MOD <sub>SET</sub>                           | 1.1                      | 1.25                        | 1.4     | V     |

| V <sub>APCSET</sub>  | Automatic power control loop voltage reference                                                                                            | Voltage at APC <sub>SET</sub> with APC loop operational            | 0.90                     | 1.20                        | 1.4     | V     |

| V <sub>FAULTL</sub>  | Low fault voltage detection<br>threshold (IB <sub>OUT</sub> , OUTP, C <sub>APC</sub> ,<br>IPIN, MOD <sub>SET</sub> , APC <sub>SET</sub> ) | Fault condition occurs when voltage drops below this level         | -                        | 100                         | 200     | mV    |

| V <sub>FAULTH</sub>  | High fault voltage detection threshold (IPIN)                                                                                             | Fault condition occurs when voltage goes above this level $\sp(2)$ | V <sub>CC</sub> 3T - 0.2 | V <sub>CC</sub> 3T<br>- 0.1 | _       | V     |

| V <sub>SELFL</sub>   | Self-biased voltage for IB <sub>OUT</sub> and OUTP                                                                                        | During disable condition                                           | 0.5                      | 1.65                        | 2.0     | V     |

Table 1-4. DC Electrical Characteristics - Laser Driver

| Symbol                 | Parameter                                                      | Conditions                                                                                                       | Minimum                  | Typical                     | Maximum                                          | Units |

|------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|--------------------------------------------------|-------|

| I <sub>BIAS</sub>      | Bias current adjust range                                      | At IB <sub>OUT</sub> . V <sub>IBOUT</sub> > 0.7V                                                                 | 1                        | -                           | 100                                              | mA    |

| I <sub>BIAS(OFF)</sub> | Bias current with output disabled                              | $\begin{aligned} & \text{DIS} = \text{high} \\ & \text{V}_{\text{IBOUT}} = \text{V}_{\text{CC}} 3 \end{aligned}$ | _                        | -                           | 150                                              | μА    |

|                        | Ratio of bias output current to APC <sub>SET</sub> current     | = I <sub>BIAS</sub> / I <sub>APCSET</sub> in open loop operation                                                 | -                        | 90                          | _                                                | A/A   |

|                        | Ratio of bias current to BIAS <sub>MON</sub> current           | = I <sub>BIAS</sub> / I <sub>BIASMON</sub>                                                                       | 79                       | 89                          | 99                                               | A/A   |

| $V_{MD}$               | Monitor diode reverse bias voltage                             |                                                                                                                  | 1.5                      | 2                           | -                                                | V     |

| I <sub>MD</sub>        | Monitor diode current adjustment range                         | For stable APC loop operation in closed loop mode                                                                | 10                       | _                           | 1500                                             | μА    |

|                        | Ratio of TxPwr <sub>MON</sub> current to monitor diode current | Across range of I <sub>MD</sub>                                                                                  | 0.8                      | 1                           | 1.2                                              | A/A   |

| C <sub>MDMAX</sub>     | Maximum monitor photodiode capacitance                         | For loop stability; includes any additional parasitic capacitance                                                | -                        | 1                           | 100                                              | pF    |

| VIH_DIS                | TTL/CMOS input high voltage (DIS)                              |                                                                                                                  | 2.0                      | 1                           | -                                                | V     |

| VIL_DIS                | TTL/CMOS input low voltage (DIS)                               |                                                                                                                  | -                        | 1                           | 0.8                                              | V     |

| VIH_CFG                | Configuration logic input high voltage (Config1 - 4) (2)       |                                                                                                                  | V <sub>CC</sub> 3T - 0.5 | 1                           | -                                                | V     |

| VIL_CFG                | Configuration logic input low voltage (Config1 - 4) (2)        |                                                                                                                  | -                        | -                           | 0.5                                              | V     |

| VOH_FAIL               | Logic output high voltage (FAIL)                               | With external 10 k $\Omega$ pull-up to V $_{CC}$                                                                 | V <sub>CC</sub> - 0.6    | -                           | -                                                | V     |

| VOL_FAIL               | Logic output low voltage (FAIL)                                | I <sub>OL</sub> = 0.8 mA                                                                                         | -                        | -                           | 0.4                                              | V     |

| R <sub>IN</sub>        | Differential input resistance                                  | Transmitter Data inputs                                                                                          | -                        | 7.5                         | _                                                | kΩ    |

| V <sub>CMSELF</sub>    | Self-biased common mode input voltage                          | Data inputs floating                                                                                             | -                        | V <sub>CC</sub> 3T<br>- 1.3 | _                                                | V     |

| V <sub>INCM</sub>      | Common-mode input compliance voltage                           | Transmitter Data inputs                                                                                          | V <sub>CC</sub> 3T - 1.5 | -                           | V <sub>CC</sub> 3T<br>- V <sub>IN(Diff)</sub> /4 | V     |

| V <sub>IN(Diff)</sub>  | Differential input voltage                                     | = 2*(DINp <sub>HIGH</sub> – DINp <sub>LOW</sub> )                                                                | 200                      | -                           | 2400                                             | mV    |

#### **NOTES:**

<sup>1.</sup>  $V_{CC}3$  supply okay circuitry monitors internally regulated voltage when only the +5V supply is used ( $V_{CC} = 5V$ ).

<sup>2.</sup> Input is 3.3V tolerant logic.

## 1.3.3 DC Electrical Characteristics - Limiting Amplifier

$V_{CC}R$  = 3.05 to 3.55V or 4.7 to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V, 25°C.

Table 1-5. DC Electrical Characteristics - Limiting Amplifier

| Symbol                                | Parameter                                    | Conditions                                                               | Minimum                | Typical                | Maximum                | Units            |

|---------------------------------------|----------------------------------------------|--------------------------------------------------------------------------|------------------------|------------------------|------------------------|------------------|

| V <sub>AMP_CML</sub>                  | CML Output Amplitude                         | Single ended, $50\Omega$ load to $V_{CC}$ ; 10 m $V_{PP}$ input (M02096) | 280                    | 500                    | -                      | mV <sub>PP</sub> |

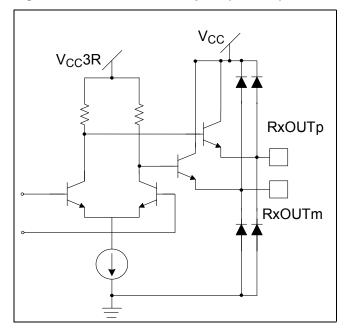

| V <sub>OUTL</sub> PECL <sup>(1)</sup> | PECL Output Low Voltage<br>(RxOUTm, RxOUTp)  | Single ended; $50\Omega$ load to $V_{CC}$ - $2V$ (M02095)                | V <sub>CC</sub> - 1.88 | V <sub>CC</sub> - 1.71 | V <sub>CC</sub> - 1.60 | V                |

| V <sub>OUTH</sub> PECL <sup>(1)</sup> | PECL Output High Voltage<br>(RxOUTm, RxOUTp) | Single ended; 50Ω load to V <sub>CC</sub> - 2V (M02095)                  | V <sub>CC</sub> - 1.09 | V <sub>CC</sub> - 0.95 | V <sub>CC</sub> - 0.88 | V                |

| V <sub>AMP_PECL</sub>                 | PECL Output Amplitude                        | Single ended; $50\Omega$ load to $V_{CC}$ - $2V$ (M02095)                | _                      | 740                    | -                      | mV <sub>PP</sub> |

| R <sub>IN</sub> _DIFF                 | Differential Input Resistance                |                                                                          | -                      | 4.5                    | _                      | kΩ               |

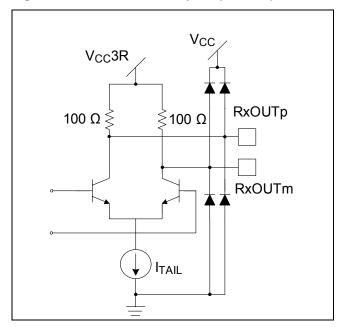

| R <sub>OUT</sub> _DIFF                | Differential Output Resistance               | CML Outputs (M02096)                                                     | 170                    | 200                    | 230                    | Ω                |

| V <sub>OUTL</sub> LOS                 | LOS Output High Voltage                      | Open collector, 4.7 - 10 k $\Omega$ pull up to V $_{CC}$                 | 2.4                    | -                      | V <sub>CC</sub>        | V                |

| V <sub>OUTH</sub> LOS                 | LOS Output Low Voltage                       | I <sub>OL</sub> = 0.8 mA                                                 | _                      | _                      | 0.4                    | V                |

#### NOTES:

# 1.4 AC Characteristics

#### 1.4.1 AC Electrical Characteristics - Laser Driver

$V_{CC}T$  = 3.05 to 3.55V or 4.7 to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $I_{BOUT}$  = 20 mA,  $I_{MOD}$  = 30 mA.

Table 1-6. AC Electrical Characteristics - Laser Driver

| Symbol                | Parameter                                                                          | Conditions                                  | Minimum | Typical               | Maximum         | Units            |

|-----------------------|------------------------------------------------------------------------------------|---------------------------------------------|---------|-----------------------|-----------------|------------------|

| I <sub>MOD</sub>      | Modulation current adjust range                                                    | To meet AC specifications <sup>(1, 2)</sup> | 8       | -                     | 85              | mA <sub>PP</sub> |

| I <sub>MOD(OFF)</sub> | Modulation current with output disabled                                            | DIS = high                                  | _       | _                     | 150             | μА               |

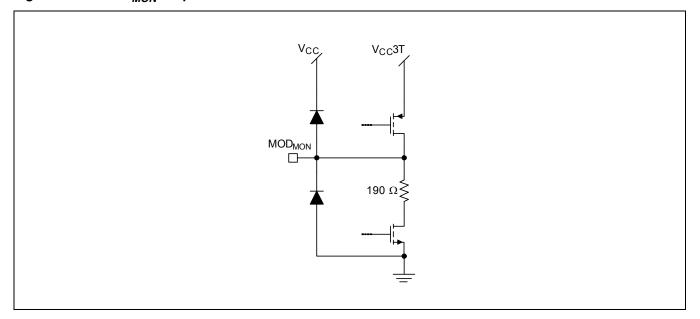

|                       | Ratio of modulation current to MOD <sub>MON</sub> current <sup>(3)</sup>           |                                             | -       | 75                    | -               | A/A              |

|                       | Ratio of modulation current to MOD <sub>SET</sub> current                          |                                             | -       | 110                   | -               | A/A              |

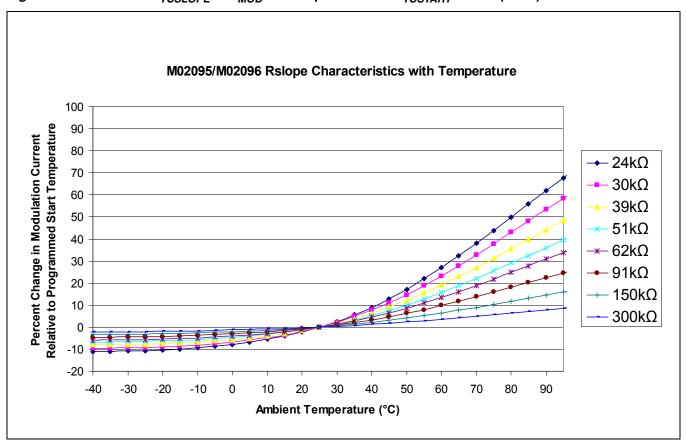

| I <sub>MOD-TC</sub>   | Programmable range for modulation current temperature coefficient                  | Adjustable using TC <sub>SLOPE</sub>        | 0       | -                     | 10 <sup>4</sup> | ppm/°C           |

| T <sub>TCSTRT</sub>   | Programmable temperature range at which modulation current TC compensation enables | Based on value set for TC <sub>START</sub>  | -       | 0 <sup>(4)</sup> - 95 | -               | °C               |

<sup>1.</sup> PECL level requirements apply from 0°C to 95°C.

Table 1-6. AC Electrical Characteristics - Laser Driver

| Symbol      | Parameter                           | Conditions                                                                                      | Minimum | Typical | Maximum | Units             |

|-------------|-------------------------------------|-------------------------------------------------------------------------------------------------|---------|---------|---------|-------------------|

|             |                                     | $20\%$ to $80\%$ into $25\Omega$ load. Measured using alternating 1111-0000 pattern at 2.5 Gbps |         |         |         |                   |

| $t_R / t_F$ | Modulation output rise / fall times | M02095; 25Ω load                                                                                | -       | 72      | 95      | ps                |

|             |                                     | M02096; 25Ω load                                                                                | _       | 65      | 85      |                   |

|             |                                     | Into 25Ω load, off direction                                                                    | -       | 3       | -       |                   |

| 0S          | Overshoot of modulation output      | Into 25Ω load, on direction                                                                     | -       | 7       | -       | %                 |

| RJ          | Random jitter                       |                                                                                                 | -       | 1.0     | -       | ps <sub>RMS</sub> |

| DJ          | Modulation output deterministic     | into $25\Omega$ load (includes pulse width distortion) K28.5 pattern at 1.25 Gbps (M02095)      | -       | 22      | 40      | ps <sub>pp</sub>  |

|             | jitter                              | 2 <sup>23</sup> - 1 PRBS at 2.7 Gbps (M02096))                                                  | _       | 15      | 30      |                   |

#### NOTES:

- 1. Minimum voltage at OUTP > 0.7 V; laser forward voltage and total series resistance must be considered if output is DC coupled to laser.

- 2. AC specifications apply across this range of mod current.

- 3. MOD<sub>MON</sub> is accessible using Special Configuration 3 (SC3), see Table 4-3.

- 4. Default if TC<sub>START</sub> is floating.

# 1.4.2 AC Electrical Characteristics - Limiting Amplifier

$V_{CC}R = 3.05$  to 3.55V or 4.7 to 5.5V,  $T_A = -40$ °C to +95°C, unless otherwise noted.

Table 1-7. AC Electrical Characteristics - Limiting Amplifier

| Symbol               | Parameter                                             | Conditions                                                                                                                                                                                           | Minimum | Typical          | Maximum | Units            |

|----------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|---------|------------------|

| .,                   | N                                                     | BER < 10 <sup>-12</sup> at 2.5 Gbps with 2 <sup>23</sup> -1 PRBS (M02096)                                                                                                                            | -       | 3.3              | 6       | .,               |

| V <sub>IN(MIN)</sub> | Minimum Differential Input<br>Sensitivity             | BER < 10 <sup>-12</sup> at 1.25 Gbps with K28.5 pattern (M02095)                                                                                                                                     | -       | 2                | 4       | mV <sub>PP</sub> |

| .,                   |                                                       | BER < 10 <sup>-12</sup> , differential input                                                                                                                                                         | 1200    | -                | _       |                  |

| V <sub>I(MAX)</sub>  | Input Overload                                        | BER < 10 <sup>-12</sup> , single-ended input                                                                                                                                                         | 600     | -                | -       | $mV_PP$          |

|                      |                                                       | M02096                                                                                                                                                                                               | -       | -                | 425     |                  |

| V <sub>N</sub>       | V <sub>N</sub> RMS Input Referred Noise               | M02095                                                                                                                                                                                               | -       | -                | 285     | $\mu V_{RMS}$    |

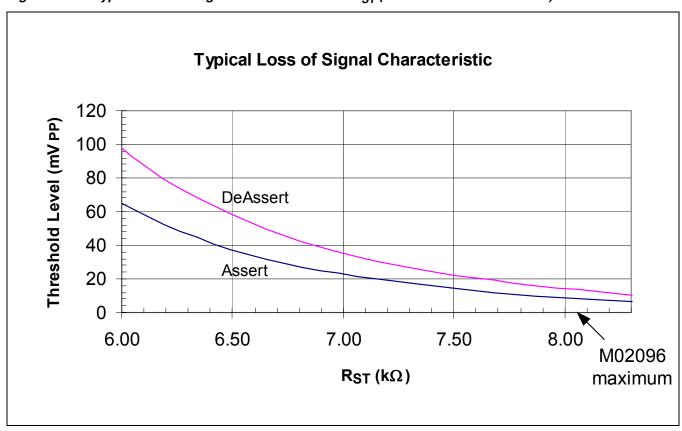

| V <sub>LOS</sub>     | LOS Programmable Range                                | Differential inputs, $6.04 \text{ k}\Omega \leq R_{\text{STSET}} \leq 8.06 \text{ k}\Omega \text{ (M02096)}$ $6.04 \text{ k}\Omega \leq R_{\text{STSET}} \leq 8.25 \text{ k}\Omega \text{ (M02095)}$ | -       | 8 - 60<br>7 - 60 | -       | mV               |

| HYS                  | Signal Detect Hysteresis                              | (electrical); signal detect level set to 20 mV <sub>PP</sub>                                                                                                                                         | 2       | 4                | 6       | dB               |

| RSSIpp               | Peak-to-peak received signal strength indicator range |                                                                                                                                                                                                      | 4       | -                | 100     | mV               |

| BW <sub>LF</sub>     | Small-Signal -3dB Low<br>Frequency Cutoff.            | Excluding AC coupling capacitors                                                                                                                                                                     | -       | 4                | _       | kHz              |

| DJ                   | Deterministic Jitter                                  | Differential, 10 mV <sub>PP</sub> input, 2 <sup>15</sup> -1 PRBS 2.5 Gbps (M02096)                                                                                                                   | -       | 20               | 48      | ps               |

|                      |                                                       | 1.25 Gbps (M02095)                                                                                                                                                                                   | _       | 20               | 70      |                  |

Table 1-7. AC Electrical Characteristics - Limiting Amplifier

| Symbol                               | Parameter                                        | Conditions                                                                                                                             | Minimum | Typical | Maximum | Units             |

|--------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------------------|

| RJ                                   | Random Jitter                                    | 10 mV <sub>PP</sub> input                                                                                                              | _       | 3.8     | -       | ps <sub>RMS</sub> |

| t <sub>r</sub> / t <sub>f2.5G</sub>  | Data Output Rise and Fall Times                  | $M02096$ 20% to 80%; outputs terminated into $50\Omega;$ 10 mV $_{PP}$ input                                                           | -       | 90      | 150     | ps                |

| t <sub>r</sub> / t <sub>f1.25G</sub> | Data Output Rise and Fall Times                  | M02095 20% to 80%; outputs terminated into 50 $\Omega$ ; 10 mV <sub>PP</sub> input                                                     | -       | 160     | 250     | ps                |

| T <sub>LOS_ON</sub>                  | Time from LOS state until LOS output is asserted | LOS assert time after 1 V <sub>PP</sub> input signal is turned off; signal detect level set to 10 mV                                   | 2.3     | -       | 80      | μS                |

| T <sub>LOS_OFF</sub>                 | Time from non-LOS state until LOS is deasserted  | LOS deassert time after input crosses signal detect level; signal detect set to 10 mV with applied input signal of 20 mV <sub>PP</sub> | 2.3     | -       | 80      | μS                |

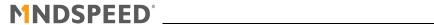

# 1.5 Safety Logic Timing

$V_{CC}$  = 3.05 to 3.55V or 4.7 to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted. Typical values are  $V_{CC}$  = 3.3V,  $IB_{OUT}$  = 20 mA,  $I_{MOD}$  = 30 mA.

Table 1-8. Safety Logic Timing

| Symbol              | Parameter                                                  | Conditions                                                                                                   | Minimum  | Typical | Maximum | Units |

|---------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------|---------|---------|-------|

| t_off               | DIS assert time                                            | Rising edge of DIS to fall of output signal below 10% of nominal <sup>(1)</sup>                              | _        | 1       | 10      | μS    |

| t_on                | DIS negate time                                            | Falling edge of DIS to rise of output signal above 90% of nominal <sup>(1)</sup>                             | _        | 0.4     | 1       | ms    |

| t_init              | Time to initialize                                         | Includes reset of FAIL; from power on after Supply_OK or from negation of DIS during reset of FAIL condition | -        | 4       | 300     | ms    |

| t_wc                | Window comparator hold-off time                            | Time during which the status of the fault detect comparators is ignored.                                     | 2        | 3       | _       | ms    |

| t_fault             | Laser fault time from fault condition to assertion of FAIL | From occurrence of fault condition or when Supply_OK is beyond specified range                               | _        | 16      | 100     | μ\$   |

| t_reset             | DIS time to start reset                                    | DIS pulse width required to initialize safety circuitry or reset a latched fault                             | _        | _       | 10      | μS    |

| t <sub>VCC-OK</sub> | Supply okay delay time                                     | Delay between supply_OK condition and when outputs are enabled                                               | _        | 900     | -       | μS    |

| NOTE:               |                                                            | 1                                                                                                            | <u>I</u> |         |         |       |

| 1. With 0           | $S_{APC} = 47 \text{ nF}.$                                 |                                                                                                              |          |         |         |       |

DIS

Fault\_OK

Voc\_OK

3.3V\_ONLY

Configuration settings are not updated while TCsLOPE is pulled high, but are updated when TCsLOPE is at normal level

\* Fault\_OK indicates that no fault is detected at any of the fault sense nodes

Figure 1-1. Safety Logic Simplified Block Diagram

Table 1-9. Circuit Response to Single-Point Fault Conditions on Driver Pins

|                     | oneutricsponse to onigical ontraditional on briver rins                                                                                                                                            |                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Name            | Circuit Response to Over-voltage Condition or Short to $V_{CC}$                                                                                                                                    | Circuit Response to Under-Voltage Condition or Short<br>to Ground                                                                                                                                  |  |  |  |  |  |  |  |

| Config1-4           | Does not affect output power (some conditions can selectively enable/disable driver output).                                                                                                       | Does not affect output power (some conditions can selectively enable/disable driver output).                                                                                                       |  |  |  |  |  |  |  |

| V <sub>CC</sub>     | Outputs are disabled if $V_{CC}$ exceeds the $V_{CC}$ -okay (high level) threshold. If so, FAIL will be asserted. (1)                                                                              | Outputs are disabled if $V_{CC}$ voltage is below the $V_{CC}$ -okay (low level) threshold. If so, FAIL will be asserted. <sup>(1)</sup>                                                           |  |  |  |  |  |  |  |

| V <sub>CC</sub> 3T  | Outputs are disabled if $V_{CC}3$ exceeds the $V_{CC}3$ _okay (high level) threshold. If so, FAIL will be asserted. $^{(1)}$                                                                       | Outputs are disabled if $V_{CC}3$ voltage is below the $V_{CC}3$ _okay (low level) threshold. If so, FAIL will be asserted. (1)                                                                    |  |  |  |  |  |  |  |

| DINp, DINm          | The APC loop will attempt to compensate for the change in output power. If the APC loop can not maintain the set average power, a fault state occurs. (2,3)                                        | The APC loop will attempt to compensate for the change in output power. If the APC loop can not maintain the set average power, a fault state occurs. (2,3)                                        |  |  |  |  |  |  |  |

| C <sub>APC</sub>    | A fault state occurs. <sup>(2)</sup>                                                                                                                                                               | Laser bias current will be shut off, then a fault state occurs. (2)                                                                                                                                |  |  |  |  |  |  |  |

| FAIL                | Does not affect laser operation.                                                                                                                                                                   | Does not affect laser operation.                                                                                                                                                                   |  |  |  |  |  |  |  |

| DIS                 | Bias and modulation outputs are disabled and $\mathrm{SV}_{\mathrm{CC}}$ is opened.                                                                                                                | Does not affect laser power (normal condition for circuit operation).                                                                                                                              |  |  |  |  |  |  |  |

| MOD <sub>SET</sub>  | No modulation current. APC loop will adjust output power if DC coupled to laser.                                                                                                                   | A fault state occurs. <sup>(2)</sup>                                                                                                                                                               |  |  |  |  |  |  |  |

| APC <sub>SET</sub>  | Laser output power is reduced (if the modulation outputs DC coupled to laser) or turned off (if the modulation outputs AC coupled to laser). A fault state may occur. (2)                          | A fault state occurs. <sup>(2)</sup>                                                                                                                                                               |  |  |  |  |  |  |  |

| TC <sub>START</sub> | Modulation current may increase depending on operating temperature and TC <sub>SLOPE</sub> setting. APC loop will adjust for change in output power if modulation outputs are DC coupled to laser. | Modulation current may decrease depending on operating temperature and TC <sub>SLOPE</sub> setting. APC loop will adjust for change in output power if modulation outputs are DC coupled to laser. |  |  |  |  |  |  |  |

| TC <sub>SLOPE</sub> | Modulation current may decrease depending on operating temperature and TC <sub>START</sub> setting. APC loop will adjust for change in output power if modulation outputs are DC coupled to laser. | Modulation current may increase depending on operating temperature and TC <sub>START</sub> setting. APC loop will adjust for change in output power if modulation outputs are DC coupled to laser. |  |  |  |  |  |  |  |

#### Table 1-9. Circuit Response to Single-Point Fault Conditions on Driver Pins

| Pin Name                                      | Circuit Response to Over-voltage Condition or Short to $$v_{\rm CC}$$                                                                                                                      | Circuit Response to Under-Voltage Condition or Short to Ground |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| BIAS <sub>MON</sub> ,<br>TxPwr <sub>MON</sub> | Does not affect laser operation.                                                                                                                                                           | Does not affect laser operation.                               |

| I <sub>PIN</sub>                              | A fault state occurs. <sup>(2,4)</sup>                                                                                                                                                     | A fault state occurs. (2,4)                                    |

| IB <sub>OUT</sub>                             | The laser is turned off and a fault state may occur. (2)                                                                                                                                   | A fault state occurs. <sup>(2)</sup>                           |

| OUTP                                          | Laser modulation is prevented; the APC loop will increase bias current to compensate for the drop in laser power. If the set output power can not be obtained, a fault state occurs. (2,3) | A fault state occurs. <sup>(2)</sup>                           |

| OUTN                                          | Does not affect laser operation.                                                                                                                                                           | Does not affect laser operation.                               |

| GNDO                                          | Laser modulation is prevented and a fault state may occur. (2)                                                                                                                             | Does not affect laser power.                                   |

| SV <sub>CC</sub>                              | Does not affect laser operation.                                                                                                                                                           | The laser is turned off and a fault state occurs. (2)          |

#### **NOTES:**

- 1. In this case a fault state will assert the FAIL output, but it is not latched. While the fault condition remains, the bias and modulation outputs are disabled and the switch at SV<sub>CC</sub> is open. No fault occurs if in Safety Circuit Bypass (SCB).

- 2. In this case a fault state will assert and latch the FAIL output, disable bias and modulation outputs and open the switch at SV<sub>CC</sub>. No fault occurs if in Safety Circuit Bypass (SCB).

- 3. Does not affect laser power when the modulation output is AC coupled to the laser.

- 4. Does not affect laser power in open loop mode or when "Ignore  $I_{PIN}$ " is selected.

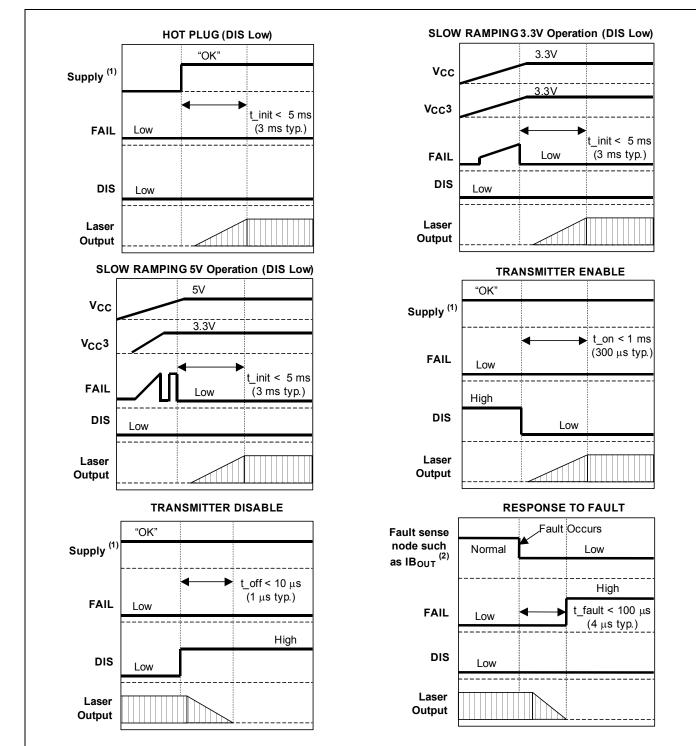

Figure 1-2. M02095/6 Safety Logic Timing Characteristics

- 1. Supply "OK" means both  $V_{CC}$  and  $V_{CC}$ 3 are within their defined operating windows.

- 2. A fault occurs when  $I_{PIN}$  goes high or low; a fault at  $I_{PIN}$  does not apply when "Ignore  $I_{PIN}$ " configuration is selected.

NOTE: "Laser Output" is equivalent to bias current plus modulation current.

Figure 1-3. M02095/6 Safety Logic Timing Characteristics (Continued)

- Supply "OK" means both  $\rm V_{\rm CC}$  and  $\rm V_{\rm CC}3$  are within their defined operating windows.

- A fault occurs when  $I_{PIN}$  goes high or low; a fault at  $I_{PIN}$  does not apply when "Ignore  $I_{PIN}$ " configuration is selected.

NOTE: "Laser Output" is equivalent to bias current plus modulation current.

# 2.0 Pin Definitions

Table 2-1. M02095/6 Pin Descriptions (1 of 2)

| Table 2-1.        | WO2093/0 I           | Fill Descriptions (1 of 2)                                                                                                                                                                                                                                                                                                                                          |

|-------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN Pin<br>Number | Pin Name             | Function                                                                                                                                                                                                                                                                                                                                                            |

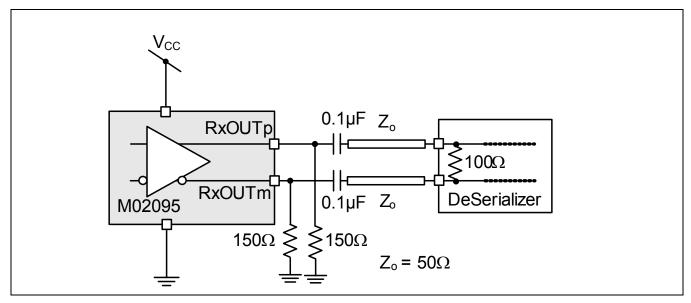

| 1                 | RxOUTm               | Limiting amplifier inverting data output (M02095 - PECL, M02096 - CML). Either output type is referenced to the Rx supply input (V <sub>CC</sub> R).                                                                                                                                                                                                                |

| 2                 | RxOUTp               | Limiting amplifier non-inverting data output (M02095 - PECL, M02096 - CML). Either output type is referenced to the Rx supply input ( $V_{CC}R$ ).                                                                                                                                                                                                                  |

| 3                 | V <sub>CC</sub> R    | Power supply input for limiting amplifier circuitry (3.3V or 5V).                                                                                                                                                                                                                                                                                                   |

| 4                 | V <sub>CC</sub> T    | Power supply input for laser driver circuitry (3.3V or 5V).                                                                                                                                                                                                                                                                                                         |

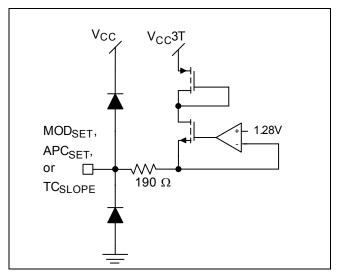

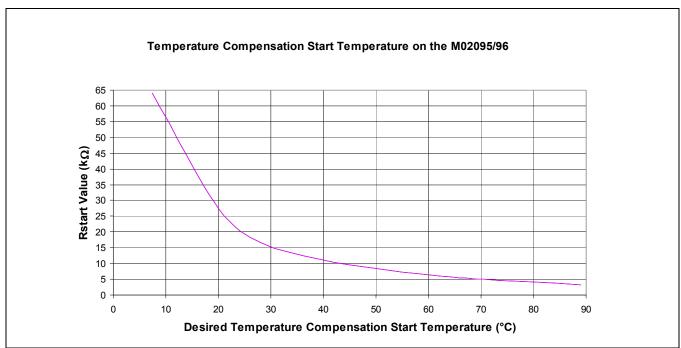

| 5                 | TC <sub>SLOPE</sub>  | Modulation temperature compensation slope. A resistor to ground sets the level of temperature compensation for the modulation current. Forcing this pin high (to 3.3V) causes the configuration logic to ignore configuration logic settings until this pin is released to its normal level (~1.25V). Temperature compensation is disabled if this pin is floating. |

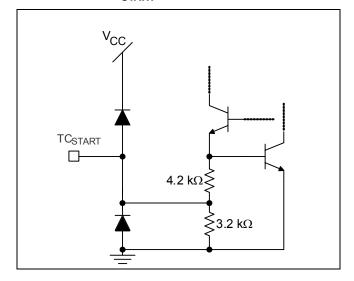

| 6                 | TC <sub>START</sub>  | A resistor to ground at this pin sets the temperature at which the modulation temperature compensation slope becomes active. Letting this pin float results in a start temperature of ~0°C. Grounding this pin disables temperature compensation.                                                                                                                   |

| 7                 | DINp                 | Transmitter positive Data Input. Internally terminated with 4 k $\Omega$ to self-bias voltage of approximately $V_{CC}3T$ - 0.65V. Can be AC coupled.                                                                                                                                                                                                               |

| 8                 | DINm                 | Transmitter negative Data Input. Internally terminated with 4 k $\Omega$ to self-bias voltage of approximately $V_{CC}3T$ - 0.65V. Can be AC coupled.                                                                                                                                                                                                               |

| 9                 | FAIL                 | Safety circuit fault indicator. Goes high when a safety logic fault is detected. The FAIL output is low when DIS is high. Open collector; $4.7~\text{k}\Omega$ to $10~\text{k}\Omega$ external pull-up required. 5V compatible when using a 5V supply.                                                                                                              |

| 10                | DIS                  | Disable control (TTL compatible). When high or left floating, the bias and modulation outputs are disabled. Set low for normal operation. 7 k $\Omega$ internal pull-up to $V_{CC}T$ .                                                                                                                                                                              |

| 11                | MOD <sub>SET</sub>   | Modulation Current Adjust. Connect a resistor between this pin and ground to set laser modulation current.                                                                                                                                                                                                                                                          |

| 12                | BIAS <sub>MON</sub>  | Bias output current monitor. Terminate with a resistor to ground to set the desired full-scale voltage at maximum bias current. Some internal functions can be muxed to this pin via the configuration logic. See configuration logic table for more detail.                                                                                                        |

| 13                | TxPwr <sub>MON</sub> | Transmit power monitor. Provides a 1:1 mirror of the monitor photodiode current. Terminate with a resistor to ground to set the desired full-scale voltage at maximum photodiode current.                                                                                                                                                                           |

| 14                | APC <sub>SET</sub>   | A resistor connected from this pin to ground sets laser output power.                                                                                                                                                                                                                                                                                               |

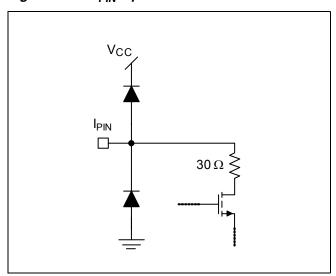

| 15                | I <sub>PIN</sub>     | Monitor photodiode input. Connect this input to the monitor photodiode anode for automatic power control. The monitor photodiode cathode should be connected to $SV_{CC}$ or $V_{CC}3T$ .                                                                                                                                                                           |

| 16                | IB <sub>OUT</sub>    | Laser bias current output. Connect to laser cathode through a ferrite.                                                                                                                                                                                                                                                                                              |

| 17                | GNDO                 | Ground for modulation output stage. Connect directly to ground or can connect to ground through an inductor.                                                                                                                                                                                                                                                        |

|                   |                      |                                                                                                                                                                                                                                                                                                                                                                     |

Table 2-1. M02095/6 Pin Descriptions (2 of 2)

| QFN Pin<br>Number | Pin Name           | Function                                                                                                                                                                                                                                                        |

|-------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18                | OUTP               | Transmitter positive modulation output. Draws current when DINp is high. Referenced to the $SV_{CC}$ (transmitter regulator output) voltage.                                                                                                                    |

| 19                | OUTN               | Transmitter negative modulation output. Draws current when DINp is low. Referenced to the SV <sub>CC</sub> (transmitter regulator output) voltage.                                                                                                              |

| 20                | SV <sub>CC</sub>   | Internal power supply switch for laser. Provides redundant shutdown during a disable or fault condition.                                                                                                                                                        |

| 21                | V <sub>CC</sub> 3T | Internally regulated voltage for laser driver circuitry in 5V applications. Connect directly to supply to allow wider power supply tolerance in 3.3V-only applications (internal regulator not in use). Do not connect to power supply if $V_{CC} = 5V$ .       |

| 22                | C <sub>APC</sub>   | A capacitor at this pin sets the dominant pole for automatic power control. Connect a capacitor between this pin and $V_{CC}3$ if automatic power control is used. Can leave floating if using open loop configuration.                                         |

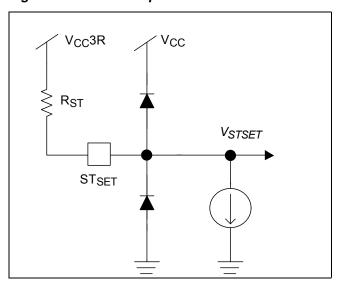

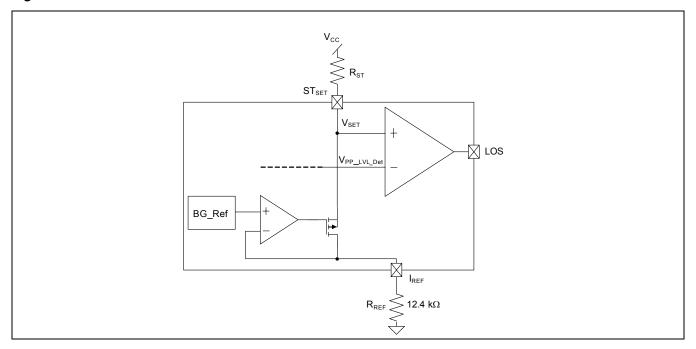

| 23                | ST <sub>SET</sub>  | Loss of signal threshold setting input. Connect a resistor between this pin and $V_{CC}3R$ to set loss of signal or signal detect threshold.                                                                                                                    |

| 24                | V <sub>CC</sub> 3R | Internally regulated voltage for limiting amplifier circuitry in 5V applications. Connect directly to supply to allow wider power supply tolerance in 3.3V-only applications (internal regulator not in use). Do not connect to power supply if $V_{CC} = 5V$ . |

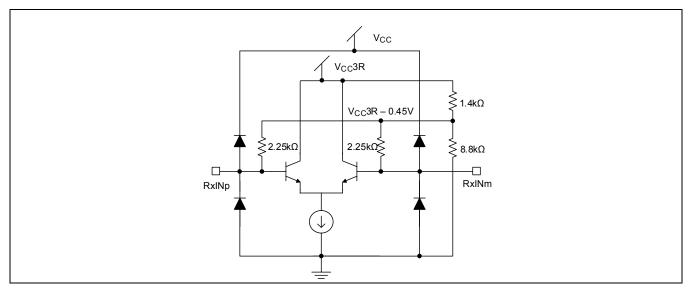

| 25                | RxINp              | Non-inverting limiting amplifier data input. Internally terminated with 2 k $\Omega$ to self-bias voltage of approximately $V_{CC}3R$ - 0.5V.                                                                                                                   |

| 26                | RxINm              | Inverting limiting amplifier data input. Internally terminated with 2 k $\Omega$ to self-bias voltage of approximately $V_{CC}3R$ - 0.5V.                                                                                                                       |

| 27                | Config1            |                                                                                                                                                                                                                                                                 |

| 28                | Config2            | Configuration logic input. These pins select laser driver and limiting amplifier configurations and test modes.  Refer to Configuration Logic table (Table 4-3) for more information. Three level logic where nominal level is mid-                             |

| 29                | Config3            | range (V <sub>CC</sub> 3T / 2) when floating.                                                                                                                                                                                                                   |

| 30                | Config4            |                                                                                                                                                                                                                                                                 |

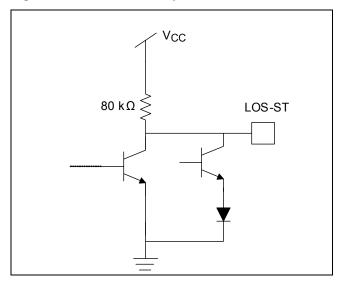

| 31                | LOS-ST             | Limiting amplifier LOS or ST (signal detect) output. Configuration logic selects whether output is to be LOS or ST. 5V compatible when using a 5V supply.                                                                                                       |

| 32                | I <sub>REF</sub>   | Internal reference current. Must be connected to ground through a 12.4 kΩ 1% resistor.                                                                                                                                                                          |

Figure 2-1. M02095/6 Package Pin-out (5x5mm MLF)

# 3.0 Functional Description

## 3.1 Overview

The M02095/6 devices are a highly integrated combined laser driver and limiting amplifier intended for applications to 2.5 Gbps, depending on device type. The parts can be operated from a single 3.3V or 5V supply.

Many features are user-adjustable, including the APC loop bias control (via a monitor photodiode), modulation current, temperature compensation control of modulation current, loss of signal threshold, using jam or not on the Rx path and the Rx and Tx polarity.

Safety circuitry is also included to provide a latched shut-down of laser bias and modulation current if a fault condition occurs. An internal  $V_{\rm CC}$  switch provides redundant shutdown of the laser current under a fault condition.

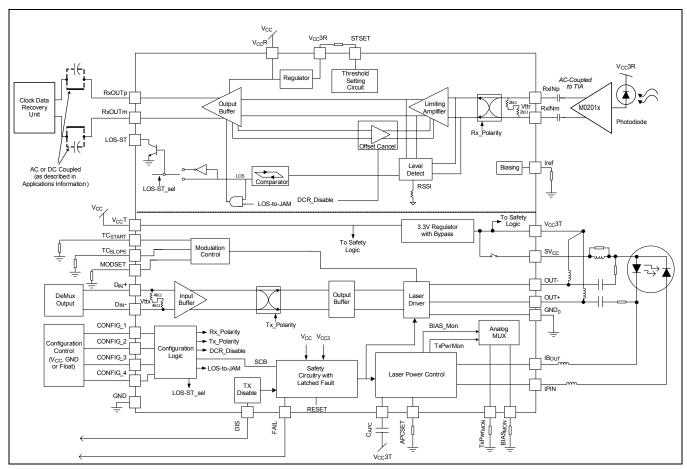

V<sub>CC</sub>3R STSET V<sub>CC</sub>R Threshold Regulato RxOUTr Limiting Output RxOUTm LOS-ST Biasing RSSI DCR\_Disable LOS-to-JAM 3.3V Regulator V<sub>CC</sub>3T TCSTART Modulation Logic TCSI OPE MODSET LOUT-D<sub>IN</sub>-Output Buffer OUT+ GND<sub>0</sub> BIAS\_Mon CONFIG\_1 V<sub>CC</sub> V<sub>CC3</sub> ► Tx\_Polarity → DCR Disable ІВоит SCB CONFIG\_3 Laser Power Control Circuitry with TX Disabl IPIN BIASMON

Figure 3-1. M02095/6 Block Diagram

# 3.2 General Description

The M02095 and M02096 integrate a laser driver and limiting amplifier in one highly configurable device for applications to 1.25 Gbps and 2.5 Gbps respectively. The Tx and Rx paths are independently operated and configurable using four three state configuration inputs allowing more than 80 user variations.

The laser driver supplies the bias and modulation current required to drive an edge emitting laser and incorporates automatic power control, a power supply switch for redundant shutdown during a fault, user settable temperature compensation of modulation current and SFP compliant safety circuitry. The limiting amplifier includes user settable input signal level detection circuit and a fully integrated DC-offset cancellation loop that does not require any external components.

Using the configuration logic, the limiting amplifier output can be jammed when loss of signal occurs and polarity control is available for both the driver and limiting amplifier data paths. Finally, using an internal self selecting regulator, the devices can operate from either a 3.3V or 5V supply with no changes to its configuration.

#### 3.2.1 Internal Regulator

The M02095/96 contain an internal 3.3V regulator so high bit rate performance can be achieved with either a 5V or 3.3V power supply.

When operating from a 5V supply ( $V_{CC}$  connected to +5V), an internal regulator provides a voltage of approximately 3.3V to the majority of the on-chip circuitry. The on-chip regulator is internally compensated, requiring no external components. When a 3.3V supply is used ( $V_{CC}$  connected to 3.3V, or both  $V_{CC}$  and  $V_{CC}$ 3 connected to 3.3V), internal logic configures the device for 3.3V operation and the regulator is switched to a low-resistance mode. The device decides whether or not the internal regulator is enabled using internal sensing logic, the sensing logic also determines whether the device safety circuitry needs to monitor for proper +5V supply voltage.

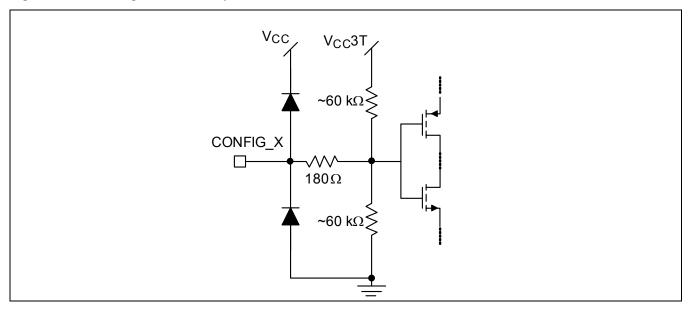

# 3.2.2 Configuration Logic

The four configuration pins allow the user to select over 80 configurations for the M02095/96. Each input has three states: tied high, tied low or floating. When floating, the respective configuration pin internally is brought to  $\sim V_{CC}3T/2$  and this is decoded separately from either a high or low state. See Figure 3-2.

Table 3-1. M02095/6 Configuration Logic Selections

| Function         | Function                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIS/EN:          | The laser driver DIS pin is either active high "Tx_Disable" or active high "Tx_Enable". Note that the DIS pin has an active high pull-up regardless of its function.                                                  |

| SCB              | Safety Circuit Bypass. If SCB is selected, a Tx Fault condition will not be latched and the safety circuitry will not disable the bias and modulation outputs. Fail will be asserted only while the fault is present. |

| LOS/ST           | Defines the limiting amplifier LOS-ST pin as either ST (goes high with signal detect) or LOS (goes high with LOS).                                                                                                    |

| LOS=JAM / NO_JAM | When "LOS=Jam" the limiting amplifier outputs are jammed when a loss of signal occurs. This is separate from whether the LOS/ST pin is defined to be either LOS or ST.                                                |

| TxP0L            | Defines the relationship between D <sub>IN</sub> + and OUT+ in the Tx path.                                                                                                                                           |

| RxP0L            | Defines the relationship between RxINp and RxOUTp in the Rx path.                                                                                                                                                     |

| Special Config   | Enables multiple specific configurations modes for the user. See Table 4-4 in Section 4.4 of this datasheet.                                                                                                          |

Figure 3-2. Configuration Pin Input

# 3.3 Laser Driver Description

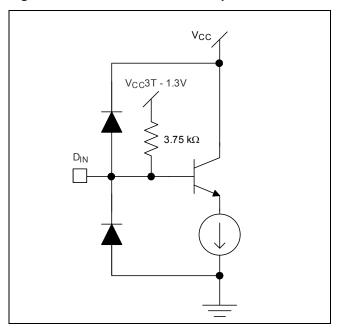

#### 3.3.1 Driver Inputs

Inputs to the laser driver data buffer are self-biased through 4  $k\Omega$  resistors to an internal reference of approximately  $V_{CC}3T$  - 1.3V (Figure 3-3). ( $V_{CC}3T$  is the internally regulated voltage for laser driver circuitry in 5V applications or is the bypassed regulator output in 3.3V applications). Both CML and PECL input signals can be AC coupled to the M02095/6.

In most applications the data inputs are AC coupled with controlled impedance pcb traces which will need to be terminated externally with a  $100\Omega$  resistor between the  $D_{IN}$ + and  $D_{IN}$ - inputs. AC coupling is recommended when using the internal regulator ( $V_{CC}$  = 5V), though external level-shifting may be used if DC coupling is desired with a 5V supply.

It is possible to invert the polarity of the driver inputs using the configuration logic (Table 4-3).

Figure 3-3. Laser Driver Data Inputs

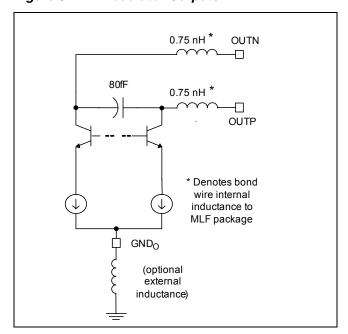

Figure 3-4. Modulator Outputs

## 3.3.2 Driver Output Stage

The laser driver output stage (Figure 3-4) incorporates feedback to maintain performance over the range of laser modulation current. The output stage is nominally configured to drive an approximate  $25\Omega$  output load. When DC coupled, OUTP should be connected through a series resistor to the laser such that the total impedance seen at the output is approximately  $25\Omega$ . This will result in the optimum pulse response while allowing the maximum modulation current to be achieved.

The output can also be AC coupled to the laser. When AC coupled the dynamic resistance seen by OUTP should still be  $25\Omega$ . In addition to a resistor in series with the laser, a capacitor is added in series and a ferrite is used to pull up the collector at OUTP to  $V_{CC}$ . When the laser is AC coupled, the OUTN pin is usually tied to the laser anode through an AC coupled series resistor which matches the impedance seen by the OUTP pad. Laser modulation current is controlled by adjusting current at MOD<sub>SET</sub> (Figure 3-5).

The output stage also has a separate current path to GND labelled GNDO. This isolates the output switching currents from the rest of the device.

#### 3.3.3 Modulation Control

The modulation current amplitude is controlled by the  $MOD_{SET}$  input pin. The modulation current can be temperature compensated by setting slope through the  $TC_{SLOPE}$  pin and  $TC_{START}$  (Figure 3-6) sets the temperature at which the temperature compensation begins to operate. The temperature compensation is independent of the modulation current setting.

Figure 3-5. APC<sub>SET</sub>, MOD<sub>SET</sub> and TC<sub>SLOPE</sub> Input

Figure 3-6. TC<sub>START</sub> Input

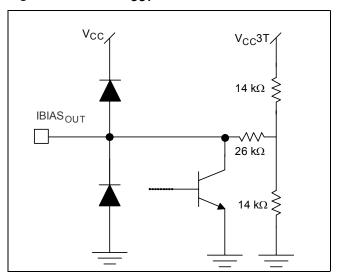

## 3.3.4 Bias Current Generator (Figure 3-7) and Automatic Power Control

The M02095/6 include circuitry to automatically maintain laser average output power with use of a monitor photodiode. The monitor photodiode cathode is connected to  $V_{CC}$ 3 (or  $SV_{CC}$ ) and the anode is connected to  $I_{PIN}$  (Figure 3-8). A feedback loop maintains the monitor photodiode current set by the current at APC<sub>SET</sub> (Figure 3-5).

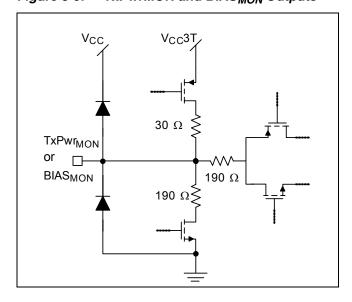

The monitor diode photo current is mirrored and an equivalent current is sourced from TxPwrMON (Figure 3-9).

Figure 3-7. IBIAS<sub>OUT</sub>

Figure 3-8. I<sub>PIN</sub> Input

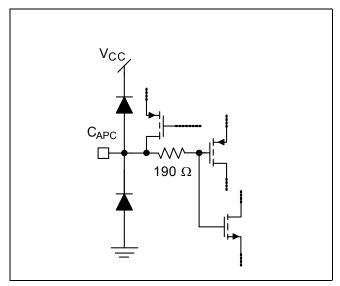

A capacitor between C<sub>APC</sub> (Figure 3-10) and V<sub>CC</sub>3 sets the dominant pole for APC loop stability.

The bias generator also includes a bias current monitor (BIAS $_{MON}$ , Figure 3-9), whose output current is typically 1/90th of the bias current.

Figure 3-9. TxPwrMON and BIAS<sub>MON</sub> Outputs

Figure 3-10. C<sub>APC</sub> Input

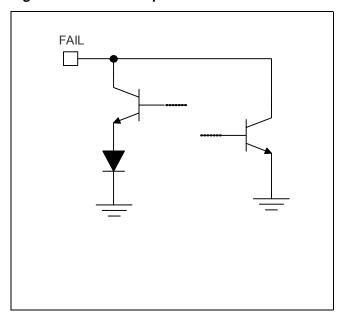

#### 3.3.5 Fail Output

The M02095/96 has an open collector FAIL alarm output (Figure 3-11) which is compatible with the TX\_FAULT signalling requirements of common plugable module standards.

The Fail output is 5V compatible whether the M02095/96 is using a 5V or 3.3V supply. It requires an external  $4.7k\Omega$  to 10  $k\Omega$  pull-up resistor so if the M02095/96 loses power the pull-up will signal a fail condition. In a simple static protection scheme used by other ICs the protection diodes would clamp the FAIL signal to ground when the chip loses power.

#### 3.3.6 Tx Disable Control

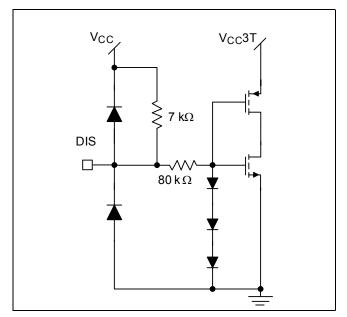

The DIS (Figure 3-12) pin is used to disable the transmit signal (both the modulation and bias current are disabled when DIS = high or is floating).

Depending on the configuration logic settings (Table 4-3), the DIS pin can redefined as an enable (EN) pin. In this case, both the modulation and bias current are enabled when EN = high or is floating).

The DIS input is compatible with TTL levels regardless of whether  $V_{CC}$  = 5V or  $V_{CC}$  = 3.3V. The external 4.7 k $\Omega$  to 10 k $\Omega$  pull-up resistor required by most interface standards is not needed because this pin has an internal 7 k $\Omega$  resistor to  $V_{CC}$ .

Figure 3-11. FAIL Output

Figure 3-12. DIS (or EN) Input

# 3.3.7 Safety Circuitry

Comparators at APC<sub>SET</sub>, MOD<sub>SET</sub>, IB<sub>OUT</sub>, I<sub>PIN</sub>, OUTP, and C<sub>APC</sub> will assert the FAIL (Figure 3-12) output, indicating that a fault condition has occurred (see Table 1-9). This condition is latched and requires DIS (Figure 3-11) to be toggled or power cycling before reset occurs.  $SV_{CC}$  is opened during a fault or disable condition.

By setting DIS high, the bias and modulation output currents are disabled. DIS will disable laser bias and modulation current if left floating. DIS must be forced to a low state to enable the outputs. When safety circuit bypass (SCB) mode is enabled, FAIL will indicate a fault condition but is not latched and the outputs will not be disabled. Only the DIS pin will shutdown the outputs when in SCB mode.

#### 3.3.8 Current Monitors

Output monitors are provided for transmit power ( $TxPwr_{MON}$ ) bias ( $BIAS_{MON}$ ) and modulation current ( $MOD_{MON}$ ).  $MOD_{MON}$  has limited availability through a configuration logic setting (Table 4-3) for the M02095/6. These monitors source current and should either feed into a current-input ADC or terminated with a resistor to ground that sets the desired full-scale voltage.

Figure 3-13. MOD<sub>MON</sub> Output

# 3.4 Limit Amp Description

#### **3.4.1** Inputs

The data inputs are internally connected to  $V_{TTR}$  via 2 k $\Omega$  resistors and generally need to be AC coupled. Referring to Figure 3-14, the nominal  $V_{TTR}$  voltage is 2.85V because of the internal resistor divider to  $V_{CC}3R$ , which means this is the DC potential on the data inputs. See the applications information section for further details on choosing the AC-coupling capacitor.

It is possible to invert the polarity of the limit amp inputs using the configuration logic (Table 4-3).

Figure 3-14. CML Data Inputs

# 3.4.2 DC Offset Compensation

The M02095/96 contains an internal DC autozero circuit that can remove the effect of DC offsets without using external components. This circuit is configured such that the feedback is effective only at frequencies well below the lowest frequency of interest. The low frequency cut off is typically 4 kHz.

It is possible to reduce the DC servo cutoff frequency using an external capacitor or to disable the servo loop completely using the configuration logic (Table 4-3). This is described in more detail in the applications section.

### 3.4.3 CML Outputs

The M02096 CML output configuration is shown in Figure 3-15. The outputs are internally terminated to  $V_{CC}3R$  through a  $100\Omega$  resistor and have a nominal amplitude of 260 mV<sub>PP</sub>

Figure 3-15. CML Data Outputs (M02096)

Figure 3-16. PECL Data Outputs (M02095)

# 3.4.4 PECL Outputs

The M02095 features 100k/300k PECL swing compatible outputs as shown in Figure 3-16 that are referenced to  $V_{CC}3R$ . The outputs may be terminated using any standard AC or DC-coupling PECL termination technique. AC-coupling is used in applications where the average DC content of the data is zero e.g. SONET. The advantage of this approach is lower power consumption, no susceptibility to DC drive and compatibility with non-PECL interfaces.

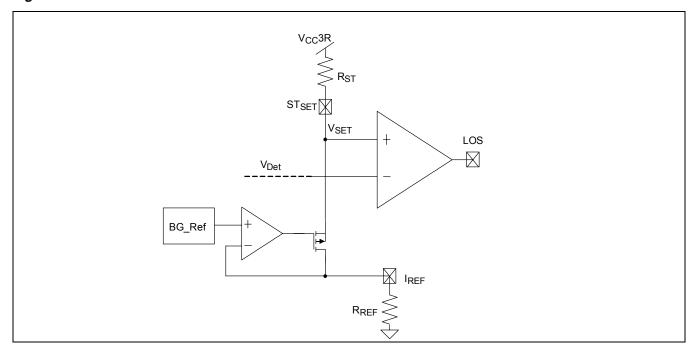

### 3.4.5 Loss of Signal/Signal Detect (LOS-ST)

The M02095/96 features input signal level detection over an extended range. Using an external resistor between pin  $ST_{SET}$  (Figure 3-18) and  $V_{CC}3R$  the user can program the input signal threshold. This function can be programmed using the configuration logic (Table 4-3) to either represent signal detect (ST) or loss of signal (LOS). For a given  $R_{ST}$  resistor setting, the difference between the ST and LOS threshold is a fixed hysteresis. The signal detect status is indicated on the LOS-ST output pin shown in Figure 3-17. LOS is active when the signal is below the threshold value, ST is active when the signal is above the threshold value. The signal detection circuitry has the equivalent of 4 dB electrical hysteresis.

Figure 3-17. LOS-ST Output

Figure 3-18. STSet Input

# 3.4.6 JAM Function ("Squelch") (Special Configuration Mode)

When enabled through the configuration logic (Table 4-3), when LOS is asserted (ST is deasserted) an internal connection between LOS and the output buffer forces the data outputs to a logic "one" state. This ensures that no data is propagated through the system. The loss of signal detection circuit can be used to automatically force the data outputs to a high state when the input signal falls below the LOS threshold. The function is normally used to allow data to propagate only when the signal is above the user's bit-error-rate requirement. It therefore inhibits the data outputs toggling due to noise when there is no signal present.

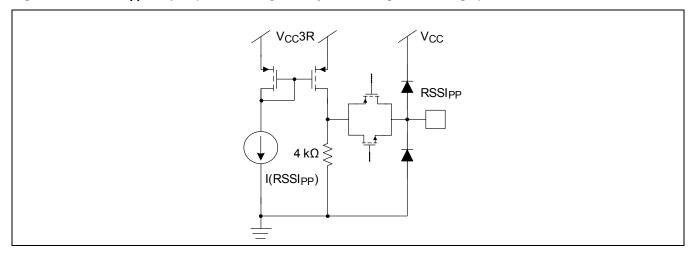

# 3.4.7 Peak to Peak Received Signal Strength Indicator (RSSI<sub>PP</sub>) (Special Configuration Mode)

When enabled through the configuration logic (Table 4-3), the RSSI<sub>PP</sub> output voltage is made available on the TxPwrMON output pin. the RSSI voltage is logarithmically proportional to the peak to peak level of the input signal. It is not necessary to connect an external capacitor to this output.

Figure 3-19. RSSI<sub>PP</sub> Output (when configured by the Configuration Logic)

#### 3.4.8 Reference Current Generation

The M095/96 contains an accurate on-chip bias circuit that requires an external 12.4 k $\Omega$  1% resistor, R<sub>REF</sub> from pin I<sub>REF</sub> to ground to set the LOS-ST threshold voltage at ST<sub>SET</sub> precisely.

Figure 3-20. Reference Current Generation

# 4.0 Applications Information

## 4.1 General