1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

### **Features and Benefits**

- WLCSP package for minimum footprint

- Ramp control circuit

- Fixed I<sup>2</sup>C logic thresholds

- 10-bit D-to-A converter

- 100  $\mu A$  resolution

- Low voltage I<sup>2</sup>C serial interface

- Low current draw sleep mode-active low

- 2.3 to 5.5 V operation

### **Applications:**

Camera focus motor

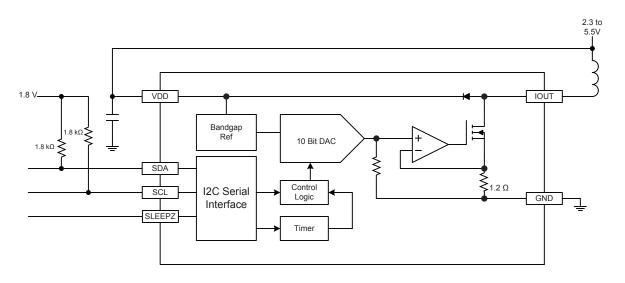

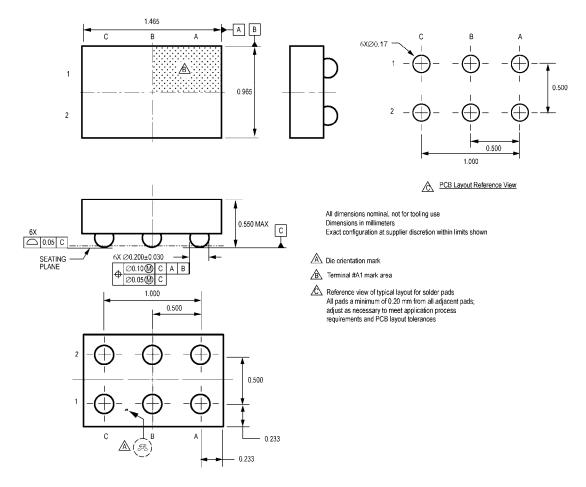

Package: 6-Bump Chip Scale Package (suffix CG)

### Description

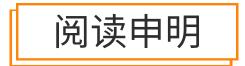

Designed for linear control of small form factor voice coil motors, the A3907 is capable of peak output currents to 102 mA and operating voltages to 5.5 V.

Internal circuit protection includes thermal shutdown with hysteresis, flyback clamp diode, and undervoltage monitoring of  $V_{\rm DD}.$

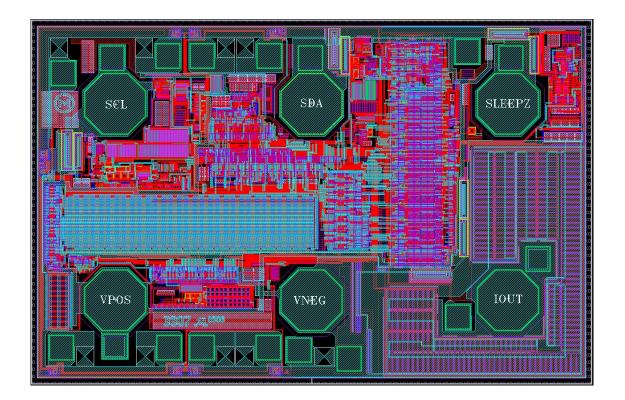

### **Functional Block Diagram**

| ABSOLUTE MAXIMUM<br>RATINGS |                 | Conditions  | Min. | Тур | Max.   | Units |

|-----------------------------|-----------------|-------------|------|-----|--------|-------|

| Supply Voltage              | V <sub>DD</sub> |             |      |     | 6      | V     |

| Logic Input Voltage Range   | Vin             |             | 3    |     | Vdd+.3 | V     |

| Junction Temperature        | Tj              |             |      |     | 150    | °C    |

| Storage Temperature Range   | Ts              |             | -40  |     | 150    | °C    |

| Operating Temperature Range |                 |             | -40  |     | 85     | °C    |

| Package Thermal Resistance  |                 |             |      |     |        |       |

| A3907ECG                    | Rja             | 4 layer PCB |      | 64  |        | °C/W  |

| Pin Name | Pin Description        |    |

|----------|------------------------|----|

| IOUT     | Sink Drive Output      | A1 |

| SLEEPZ   | Standby Mode Control   | A2 |

| GND      | Ground                 | B1 |

| SDA      | I <sup>2</sup> C data  | B2 |

| VDD      | Power Supply In        | C1 |

| SCL      | I <sup>2</sup> C clock | C2 |

#### Bump Side View

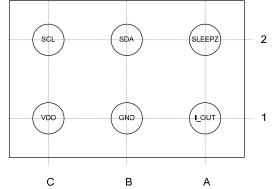

#### Top Side View

A3907

# Low Voltage Voice Coil Motor Driver

|                             |                   |                                               |      | Lir   | nits  |            |

|-----------------------------|-------------------|-----------------------------------------------|------|-------|-------|------------|

| Characteristics             | Sym               | Test Conditions                               | Min. | Тур.  | Max.  | Units      |

|                             |                   |                                               | -    | .5    | 2     | mA         |

| Supply Current              | I <sub>DD</sub>   | Sleep Mode (SLEEPZ=Low) 2.3 to 3.5V           | -    | <100  | 500   | nA         |

| UVLO Enable Threshold       | UVLOth            | Vdd Rising                                    |      | 2     | 2.295 | V          |

| UVLO Hysteresis             | UVLOhys           |                                               | 100  |       |       | mV         |

| Thermal Shutdown Temp.      | T <sub>JTSD</sub> | Temperature increasing.                       |      | 165   |       | °C         |

| Thermal Shutdown Hysteresis | $\Delta T_{J}$    | Recovery = $T_{JTSD} - \Delta T_J$            |      | 15    |       | °C         |

| Power Up Delay              |                   |                                               |      | 10    |       | uS         |

| D/A                         |                   |                                               |      |       |       |            |

| Resolution                  |                   | Target = 100uA/LSB                            |      | 10    |       | Bits       |

| Relative Accuracy           | INL               | Code = 64 to 1023, Endpoint method            |      | +/-4  |       | LSB        |

| Differential Nonlinearity   | DNL               | Guaranteed Monotonic.                         |      |       | +/-1  | LSB        |

| Max Output Current          | Imax              | Code=1023                                     |      | 102.3 |       | mA         |

| Gain Error                  |                   | Tj = 25°C, Code 64 to 1023, VDD= 2.6V to 3.0V | -10  | <3    | 10    | %FS        |

| Gain Error Drift (note 1)   |                   | $Tj = -40^{\circ}C$ to $125^{\circ}C$         |      | .2    |       | LSB/°<br>C |

| Minimum Code Error          | los1              | Code = 1                                      | 0    | 1     | 5     | mA         |

| Offset Error                | los               | Code = 64                                     |      | .5    |       | mA         |

| Output                      |                   |                                               |      |       |       |            |

| Slew Rate Timer             | Ts                | Relative to target value                      | -10  |       | 10    | %          |

| Output Voltage Range        | Vout              |                                               | .35  |       | Vdd1  | V          |

| Output Rds(on)              | Rds               | Rsense + Rsink, lout=102.3mA                  |      | 1.45  |       | ohm        |

ELECTRICAL CHARACTERISTICS at  $T_A = 25^{\circ}$ C, VDD = 2.3V to 5.5V (unless noted otherwise)

1) Assured by design and characterization, not production tested.

|                                            |                     |                           |      | Lin  | nits |       |

|--------------------------------------------|---------------------|---------------------------|------|------|------|-------|

| Characteristics                            | Symbol              | Test Conditions           | Min. | Тур. | Max. | Units |

| I <sup>2</sup> C Interface                 | -                   |                           |      |      |      | -     |

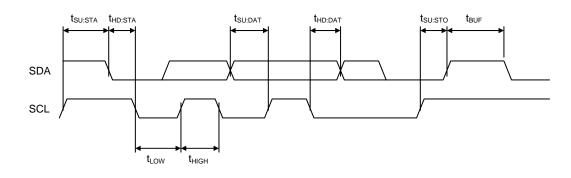

| Bus Free Time Between Stop/Start           | t <sub>BUF</sub>    |                           | 1.3  |      |      | μs    |

| Hold Time Start Condition                  | $t_{\text{HD:STA}}$ |                           | .6   |      |      | μs    |

| Setup Time for Repeated Start<br>Condition | t <sub>su:sta</sub> |                           | .6   |      |      | μs    |

| SCL Low Time                               | t <sub>LOW</sub>    |                           | 1.3  |      |      | μs    |

| SCL high Time                              | t <sub>HIGH</sub>   |                           | .6   |      |      | μs    |

| Data Setup Time                            | t <sub>su:dat</sub> |                           | 100  |      |      | ns    |

| Data Hold Time                             | t <sub>HD:DAT</sub> |                           | 0    |      | 900  | ns    |

| Setup Time for Stop Condition              | t <sub>su:sto</sub> |                           | .6   |      |      | μs    |

| Logic Input (SDA,SCL) Low Level            | V <sub>IL</sub>     |                           |      |      | 0.84 | V     |

| Logic Input (SDA,SCL) High Level           | V <sub>IH</sub>     |                           | 1.26 |      |      | V     |

| Sleep Input Low Level                      | Vinslp              |                           |      |      | .54  | V     |

| Sleep Input High Level                     | Vinslp              |                           | 1.5  |      |      | V     |

| Input Hysteresis                           | V <sub>HYS</sub>    | SDA and SCL only          |      | 100  |      | mV    |

| Logic Input Current                        | I <sub>IN</sub>     | $V_{IN} = 0V$ to Vdd      | -1   | 0    | 1    | μA    |

| Output Voltage (SDA)                       | V <sub>OL</sub>     | I <sub>LOAD</sub> = 1.5mA |      |      | 0.36 | V     |

| SCL Clock Frequency                        | f <sub>CLK</sub>    |                           |      |      | 400  | kHz   |

| SDA Output Fall Time                       | t <sub>OF</sub>     | $V_{IH}$ to $V_{IL}$      | -    |      | 250  | ns    |

### ECTRICAL CHARACTERISTICS at $T_A = 25^{\circ}$ C, VDD = 2.3V to 5.5 V (unless noted otherwise)

#### **Functional Description**

The A3907 output current is controlled by programming the DAC value via the  $I^2C$  serial port. The target output current can be calculated by

$I_out = DAC * 100uA \dots$  where DAC = 1 to 1023

Code = 0 is a disable state for the output sink drive. The DAC will be set to code = 0 upon power up or fault condition on VDD.

SLEEPZ. A logic low input will disable all of the internal circuitry and prevent the IC from draining battery power.

**Output Range.** The voltage on the IOUT pin should be over TBDmV to guarantee the accuracy and linearity on the programmed current. The output voltage is a function of the battery voltage, motor resistance, and the programmed load current.

**Clamp Diode.** When the output is turned off the load inductance will cause the output voltage to rise. A clamp diode, from IOUT to VDD, is integrated in the IC to ensure the output voltage remains at a safe level.

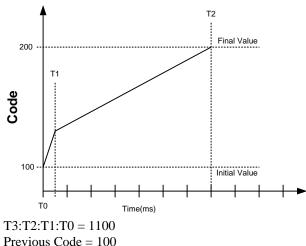

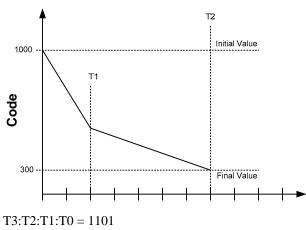

**Slew Rate Control.** To allow flexibility on the change in current with respect to time 4 serial port bits are utilized to set the timing between the change between the present current level and the next current level programmed.

When a new current level is programmed, the 3907 will move to the new value by stepping through each of the intermediate current levels until it arrives at the final programmed value. The time between each step is adjustable according to the table below.

| T3 | T2 | T1 | <b>T0</b> | Step Method             | Delay 1 <sup>st</sup> Step | Delay 2 <sup>nd</sup> Step |

|----|----|----|-----------|-------------------------|----------------------------|----------------------------|

| 0  | 0  | 0  | 0         |                         | 0 (ramp featur             | e disabled)                |

| 0  | 0  | 0  | 1         |                         | 6.25                       | 5                          |

| 0  | 0  | 1  | 0         |                         | 12.5                       | 5                          |

| 0  | 0  | 1  | 1         | Single Step             | 25                         |                            |

| 0  | 1  | 0  | 0         |                         | 50                         |                            |

| 0  | 1  | 0  | 1         |                         | 100                        |                            |

| 0  | 1  | 1  | 0         |                         | 200                        |                            |

| 0  | 1  | 1  | 1         |                         | 0 (ramp featur             | e disabled)                |

| 1  | 0  | 0  | 0         |                         | 0 (ramp featur             | e disabled)                |

| 1  | 0  | 0  | 1         |                         | 781ns                      | 6.25us                     |

| 1  | 0  | 1  | 0         |                         | 781ns                      | 12.5us                     |

| 1  | 0  | 1  | 1         | 2 Step Method           | 781ns                      | 25us                       |

| 1  | 1  | 0  | 0         | Switch over At          | 781ns                      | 50us                       |

| 1  | 1  | 0  | 1         | Code = ABS(Programmed)  | 781ns                      | 100us                      |

| 1  | 1  | 1  | 0         | Code – Previous Code)/2 | 781ns                      | 200us                      |

| 1  | 1  | 1  | 1         |                         | 0 (ramp featur             | e disabled)                |

Example 1:

Previous Code = 100 Programmed Code = 200

T1 = (200-100)/2)\*781ns = 39uS T2 -T1= 50\*50uS = 2.5mS

Previous Code = 1000Programmed Code = 300

T1 = (1000-300)/2)\*781ns = 273uS T2 -T1= 350\*100uS = 35mS

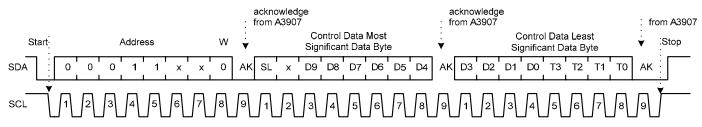

$I^2C$  Interface. This is a serial interface that uses two bus lines, SCL and SDA, to access the internal Control registers. Data is exchanged between a microcontroller (master) and the A3907 (slave). The clock input to SCL is generated by the master, while SDA functions as either an input or an open drain output, depending on the direction of the data. The I<sup>2</sup>C input thresolds do not depend on the VDD voltage of the A3907. The levels are fixed at approximately 1V. The fixed levels allow the SDA/SCL lines to be pulled up to a different logic level than the VDD supply of the 3907.

#### **Timing Considerations**

The control sequence of the communication through the  $I^2C$  interface is composed of several steps in sequence:

1. **Start Condition**. Defined by a negative edge on the SDA line, while SCL is high.

2. Address Cycle. 7 bits of address, plus 1 bit to indicate write (0) or read(1), and an acknowledge bit. The address setting is 0x18, 0x1A, 0x1C or 0x1E.

#### 3. Data Cycles.

Write - 8bits of data addressing internal control register, followed by an acknowledge bit.

4. **Stop Condition**. Defined by a positive edge on the SDA line, while SCL is high.

Except to indicate a Start or Stop condition, SDA must be stable while the clock is high. SDA can only be changed while SCL is low. It is possible for the Start or Stop condition to occur at any time during a data transfer. The A3907 always responds by resetting the data transfer sequence.

The Read/Write bit is set to low, to indicate a write cycle. Mulitple writes are allowed. If desired, the readback bit can be set to "1" to check what was last written.

The Acknowledge is used by the master to determine if the slave device is responding to its address and data. When the A3907 decodes the 7-bit address field as a valid address, it responds by pulling SDA low during the ninth clock cycle.

During a data write from the master, the A3907 pulls SDA low during the clock cycle that follows the data byte, in order to indicate that the data has been successfully received. In both cases, the master device must release the SDA line before the ninth clock cycle, in order to allow this handshaking to occur.

#### A3907 Slave Address

| Device Identifier |   |   |   |   |   | R/W |   |

|-------------------|---|---|---|---|---|-----|---|

| 0                 | 0 | 0 | 1 | 1 | Х | Х   | 0 |

#### **Control Register MSByte** (I<sup>2</sup>C Write register)

| Bit | Name  | Function                   |

|-----|-------|----------------------------|

| 0   | D4    | DAC                        |

| 1   | D5    | DAC                        |

| 2   | D6    | DAC                        |

| 3   | D7    | DAC                        |

| 4   | D8    | DAC                        |

| 5   | D9    | DAC MSB                    |

| 6   | T5    | unused                     |

| 7   | SLEEP | 1=Sleep 0=Normal Operation |

### Control Register LSByte (I<sup>2</sup>C Write register)

| Bit | Name | Function           |

|-----|------|--------------------|

| 0   | T0   | Time Setting LSB   |

| 1   | T1   | Time Setting Bit 1 |

| 2   | T2   | Time Setting Bit2  |

| 3   | Т3   | Time Setting Bit 3 |

| 4   | D0   | DAC LSB            |

| 5   | D1   | DAC                |

| 6   | D2   | DAC                |

| 7   | D3   | DAC                |

#### Write Operation

# A3907

#### Applications

**Headroom.** The current may not reach the programmed level if there is not adequate headroom in the output circuit. The IC output voltage must be over 350mV to guarantee normal linear operation. Vdd, Iload, Rload can be adjusted to ensure the device operates in the linear range. When the below equation is not satisfied the load current will be limited by the series impedance and may not reach the programmed level.

VDD(min) - Rload(max)\*Iout(max) >= 350mV

#### **Iout Errors Defined**

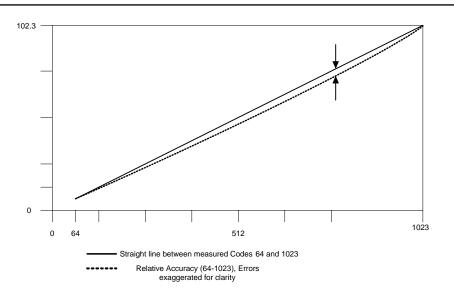

#### **Relative accuracy (INL):**

This error is calculated by measuring the worse case deviation from a straight line defined from endpoints. The straight line endpoints are defined by the actual measured values at code=63 and code= 1023. See Figure A.

#### Differential nonlinearity (DNL) :

A measure of the monotonicity of the DAC. The slope of the line must always be positive for each incremental step.

DNL = [Iout(n+1) - Iout(n)]/LSB - 1 LSB (n = 64 to 1023)

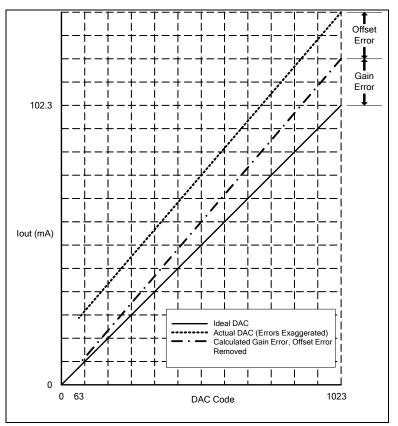

#### **Offset error:**

The measured output current at input code=64 compared to the ideal value according to the transfer function (6.4mA).

#### Gain Error:

The difference in the slopes of the ideal transfer function and the actual transfer function. The gain error is calculated by subtracting out the offset error at code 16 from the actual transfer function. This calculated value is compared to the ideal transfer function and reported as a percentage of the ideal full scale value (102.3mA). See Figure B.

#### **Gain Error Drift:**

Change in slope of the transfer function due to temperature, expressed as LSB/C.

**Figure A**

Figure B

### WLCSP Package

A3907

### Pad Location:

| Pin Name      | Pin Description      |           | Coordinates              |

|---------------|----------------------|-----------|--------------------------|

| VDD           | Power Supply In      | <u>C1</u> | <u>X = -500</u> Y = -250 |

| <u>GND</u>    | Ground               | <u>B1</u> | <u>X = 0 Y = -250</u>    |

| <u>IOUT</u>   | Sink Drive Output    | <u>A1</u> | <u>X = 500</u> Y = -250  |

| <u>SCL</u>    | I2C Clock            | <u>C2</u> | <u>X = -500 Y = 250</u>  |

| <u>SDA</u>    | I2C Data             | <u>B2</u> | <u>X = 0 Y = 250</u>     |

| <u>SLEEPZ</u> | Standby Mode Control | <u>A2</u> | <u>X = 500 Y = 250</u>   |

Copyright ©2009, Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website:

www.allegromicro.com