1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# **PWM+PFC Combi IC** TDA 16888 / TDA 16888G

High Performance Power Combi Controller

# **Power Conversion**

Never stop thinking.

#### TDA 16888/ TDA 16888G

#### Revision History: 2000-02-28

Datasheet

Previous Version:

| Page | Subjects (major changes since last revision) |

|------|----------------------------------------------|

|      |                                              |

|      |                                              |

|      |                                              |

|      |                                              |

|      |                                              |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

CoolMOS<sup>™</sup>, CoolSET<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 2000-02-28

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München © Infineon Technologies AG 1999. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

#### High Performance Power Combi Controller

TDA 16888

# 1 Overview

#### 1.1 Features

#### **PFC Section**

- IEC 1000-3 compliant

- Additional operation mode as auxiliary power supply

- Fast, soft switching totem pole gate drive (1 A)

- Dual loop control (average current and voltage sensing)

- Leading edge triggered pulse width modulation

- Peak current limitation

- Topologies of PFC preconverter are boost or flyback

- Continuous/discontinuous mode possible

- 94% maximum duty cycle

#### **PWM Section**

- Improved current mode control

- Fast, soft switching totem pole gate drive (1 A)

- Soft-start management

- Trailing edge triggered pulse width modulation

- Topologies of PWM converter are feed forward or flyback

- 50% maximum duty cycle to prevent transformer saturation

- $-f_{\text{PWM}} = f_{\text{PFC}}$

| Туре |             | Ordering Code        | Package    |  |  |

|------|-------------|----------------------|------------|--|--|

| ▼    | TDA 16888   | Q67000-A9284-X201-K5 | P-DIP-20-5 |  |  |

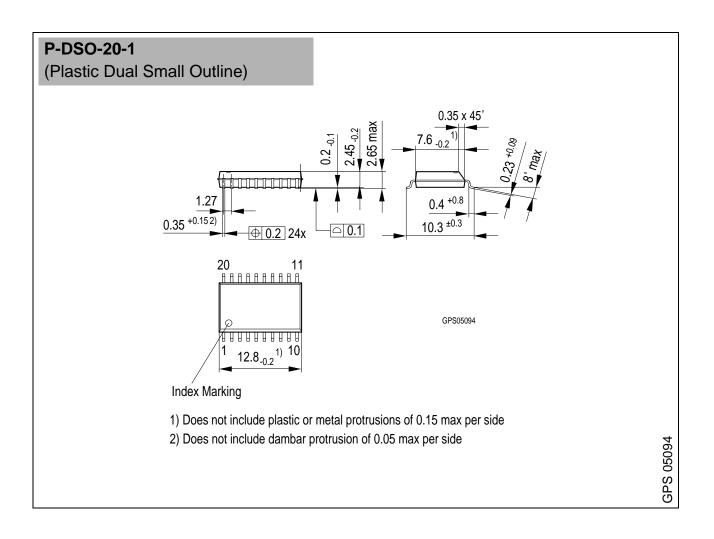

| ▼    | TDA 16888 G | Q67000-A9310-A702    | P-DSO-20-1 |  |  |

▼ New type

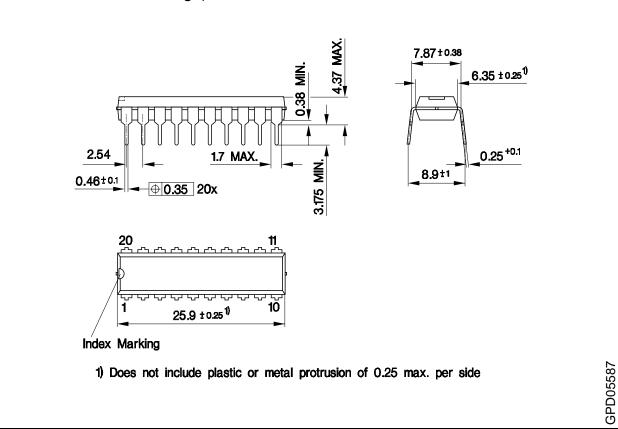

P-DIP-20-5

#### **Special Features**

- High power factor

- Typical 50 μA start-up supply current

- Low quiescent current (15 mA)

- Undervoltage lockout with internal stand-by operation

- Internally synchronized fixed operating frequency ranging from 15 kHz to 200 kHz

- External synchronization possible

- Shutdown of both outputs externally triggerable

- Peak current limitation

- Overvoltage protection

- Average current sensing by noise filtering

#### 1.2 General Remarks

The TDA 16888 comprises the complete control for power factor controlled switched mode power supplies. With its PFC and PWM section being internally synchronized, it applies for off-line converters with input voltages ranging from 90 V to 270 V.

While the preferred topologies of the PFC preconverter are boost or flyback, the PWM section can be designed as forward or flyback converter. In order to achieve minimal line current gaps the maximum duty cycle of the PFC is about 94%. The maximum duty cycle of the PWM, however, is limited to 50% to prevent transformer saturation.

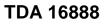

Figure 1 Pin Configuration (top view)

## 1.3 Pin Definitions and Functions

| Pin No. | Symbol           | Function                                 |

|---------|------------------|------------------------------------------|

| 1       | PFC IAC          | AC line voltage sensing input            |

| 2       | V <sub>REF</sub> | 7.5 V reference                          |

| 3       | PFC CC           | PFC current loop compensation            |

| 4       | PFC CS           | PFC current sense                        |

| 5       | GND S            | Ground sensing input                     |

| 6       | PFC CL           | Sensing input for PFC current limitation |

| 7       | GND              | Ground                                   |

| 8       | PFC OUT          | PFC driver output                        |

| 9       | V <sub>CC</sub>  | Supply voltage                           |

| 10      | PWM OUT          | PWM driver output                        |

| 11      | PWM CS           | PWM current sense                        |

| 12      | SYNC             | Oscillator synchronization input         |

| 13      | PWM SS           | PWM soft-start                           |

| 14      | PWM IN           | PWM output voltage sensing input         |

| 15      | PWM RMP          | PWM voltage ramp                         |

| 16      | ROSC             | Oscillator frequency set-up              |

| 17      | PFC FB           | PFC voltage loop feedback                |

| 18      | PFC VC           | PFC voltage loop compensation            |

| 19      | PFC VS           | PFC output voltage sensing input         |

| 20      | AUX VS           | Auxiliary power supply voltage sense     |

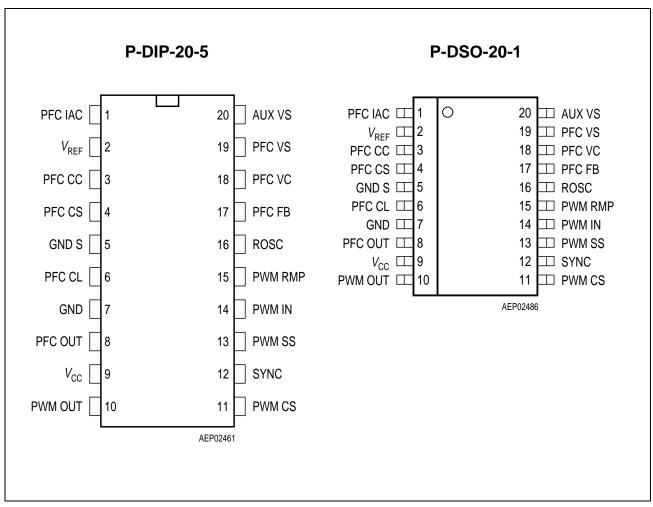

#### 1.4 Block Diagram

#### Figure 2

# 2 Functional Description

### Power Supply

The TDA 16888 is protected against overvoltages typically above 17.5 V by an internal Zener diode Z3 at pin 9 ( $V_{CC}$ ) and against electrostatic discharging at any pin by special ESD circuitry.

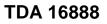

By means of its power management the TDA 16888 will switch from internal stand-by, which is characterized by negligible current consumption, to operation mode as soon as a supply voltage threshold of 14 V at pin 9 ( $V_{CC}$ ) is exceeded. To avoid uncontrolled ringing at switch-over an undervoltage lockout is implemented, which will cause the power management to switch from operation mode to internal stand-by as soon as the supply voltage falls below a threshold of 11 V. Therefore, even if the supply voltage will fall below 14 V, operation mode will be maintained as long as the supply voltage is well above 11 V.

As soon as the supply voltage has stabilized, which is determined by the TDA 16888's power management and its soft-start feature at pin 13 (PWM SS), the PWM section will be enabled by means of its internal bias control.

#### **Protection Circuitry**

Both PFC and PWM section are equipped with a fast overvoltage protection (C6) sensing at pin 19 (PFC VS), which when being activated will immediately shut down both gate drives. In addition to improve the PFC section's load regulation it uses a fast but soft overvoltage protection (OTA2) prior to the one described above, which when being activated will cause a well controlled throttling of the multiplier output  $Q_{\rm M}$ .

In case an undervoltage of the PFC output voltage is detected at pin 19 (PFC VS) by comparator C4 the gate drive of the PWM section will be shut down in order to reduce the load current and to increase the PFC output voltage. This undervoltage shutdown has to be prior to the undervoltage lockout of the internal power management and therefore has to be bound to a threshold voltage at pin 9 ( $V_{\rm CC}$ ) well above 11 V.

In order to prevent the external circuitry from destruction the PFC output PFC OUT (pin 8) will immediately be switched off by comparator C2, if the voltage at pin 19 (PFC VS) drops to ground caused by a broken wire. In a similar way measures are taken to handle a broken wire at any other pin in order to ensure a safe operation of the IC and its adjoining circuitry.

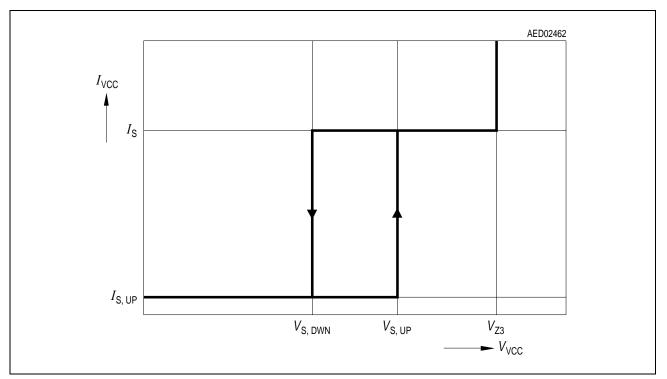

If necessary both outputs, PFC OUT (pin 8) and PWM OUT (pin 10), can be shutdown on external request. This is accomplished by shorting the external reference voltage at pin 2 ( $V_{\text{REF}}$ ) to ground. To protect the external reference, it is equipped with a foldback characteristic, which will cut down the output current when  $V_{\text{REF}}$  (pin 2) is shorted (see **Figure 4**).

Both PFC and PWM section are equipped with a peak current limitation, which is realized by the comparators C3 and C9 sensing at pin 6 (PFC CL) and pin 11 (PWM CS) respectively. When being activated this current limitation will immediately shut down the respective gate drive PFC OUT (pin 8) or PWM OUT (pin 10).

Finally each pin is protected against electrostatic discharge.

#### Oscillator/Synchronization

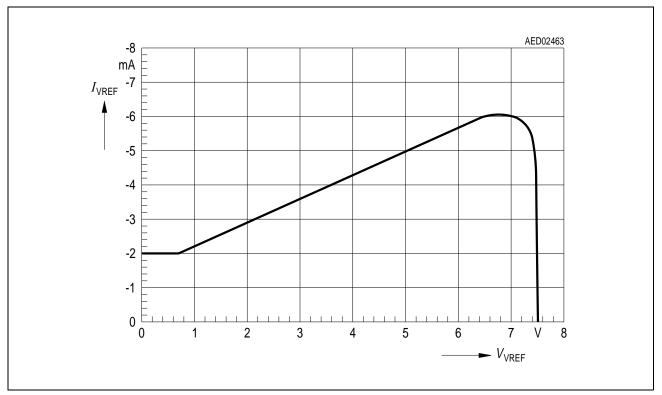

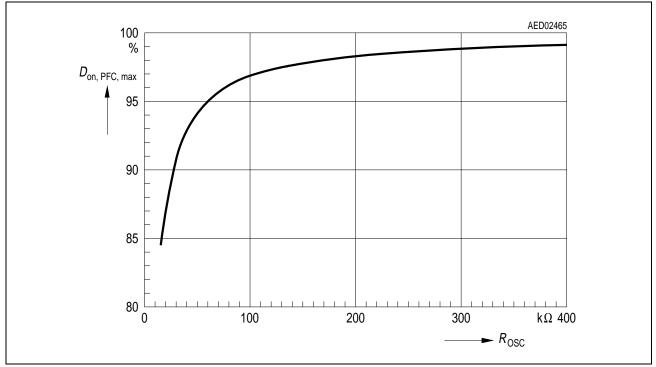

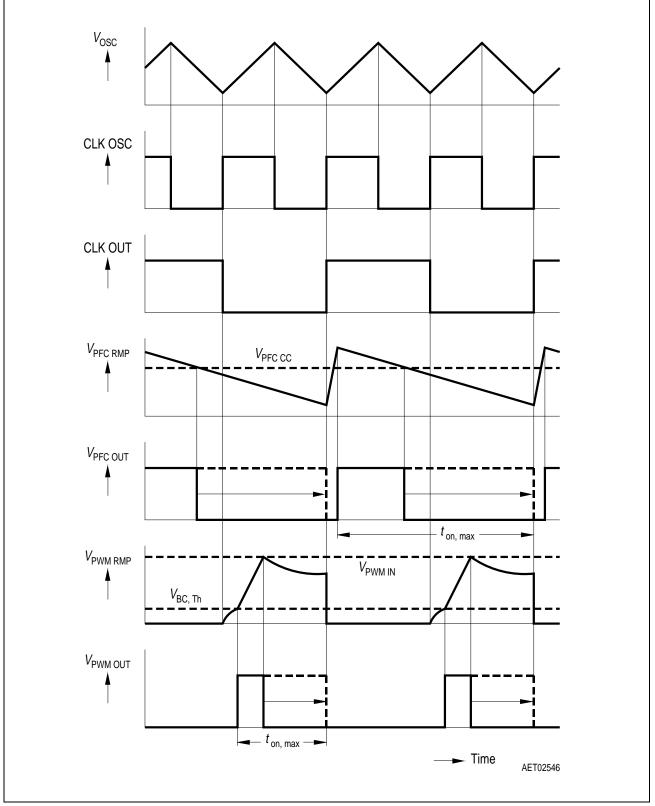

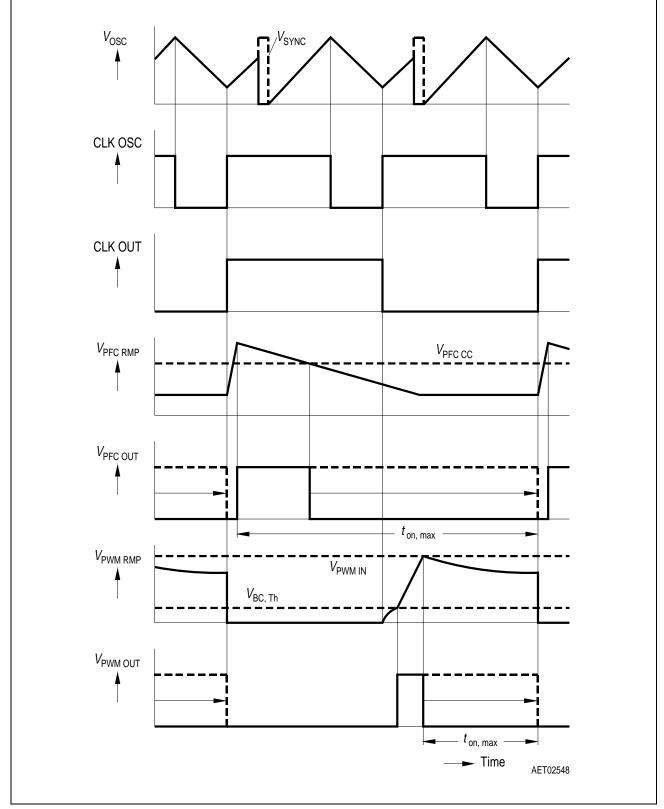

The PFC and PWM clock signals as well as the PFC voltage ramp are synchronized by the internal oscillator (see **Figure 18**). The oscillator's frequency is set by an external resistor connected to pin 16 (ROSC) and ground (see **Figure 5**). The corresponding capacitor, however, is integrated to guarantee a low current consumption and a high resistance against electromagnetic interferences. In order to ensure superior precision of the clock frequency, the clock signal CLK OSC is derived from a triangular instead of a saw-tooth signal. Furthermore to provide a clock reference CLK OUT with exactly 50% duty cycle, the frequency of the oscillator's clock signal CLK OSC is halved by a D-latch before being fed into the PFC and PWM section respectively (see **Figure 18**).

The ramp signal of the PFC section  $V_{\text{PFC RMP}}$  is composed of a slowly falling and a steeply rising edge. This ramp has been reversed in contrast to the common practice, in order to simultaneously allow for current measurement at pin 5 (GND S) and for external compensation of OP2 by means of pin 5 (GND S) and pin 3 (PFC CC).

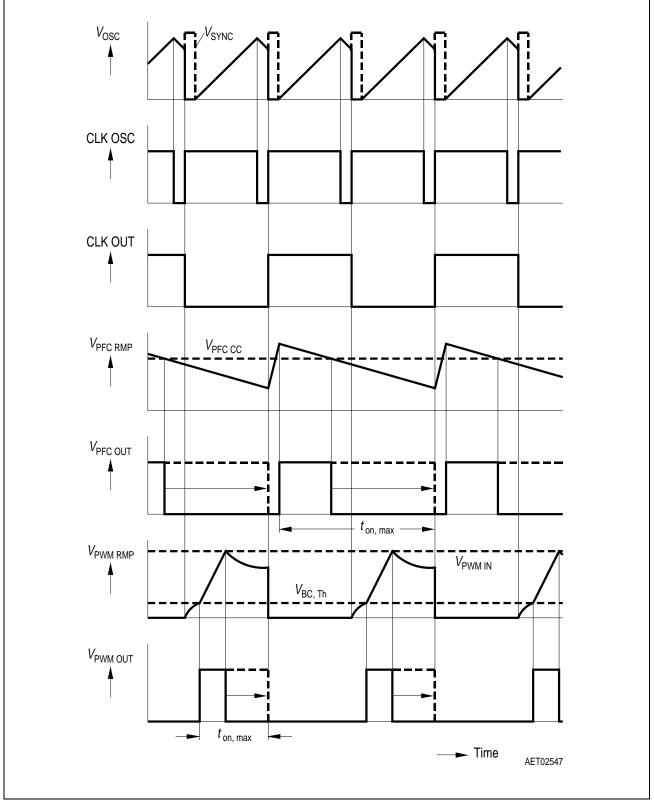

The oscillator can be synchronized with an external clock signal supplied at pin 12 (SYNC). However, since the oscillator's frequency is halved before being fed into the PFC and PWM section, a synchronization frequency being twice the operating frequency is recommended. As long as the synchronization signal is H the oscillator's triangular signal  $V_{OSC}$  is interrupted and its clock signal CLK OSC is H (see **Figure 19** and **Figure 20**). However, as soon as the external clock changes from H to L the oscillator is released. Correspondingly, by means of an external clock signal supplied at pin 12 (SYNC) the oscillator frequency  $f_{OSC}$  set by an external resistor at pin 16 (ROSC) can be varied on principle only within the range from  $0.66 f_{OSC}$  to  $2 f_{OSC}$ . If the oscillator has to be synchronized over a wider frequency range, a synchronization by means of pin 12 (SYNC). Anyhow, please note, that pin 12 (SYNC) is not meant to permanently shutdown both PFC and PWM section. It can be used to halt the oscillator freezing the prevailing state of both drivers but does not allow to automatically shut them down. A shutdown can be achieved by shorting pin 2 ( $V_{REF}$ ) to ground, instead.

Finally, In order to reduce the overall current consumption under low load conditions, the oscillator frequency itself is halved as long as the voltage at pin 13 (PWM SS) is less than 0.4 V (disabled PWM section).

#### **PFC Section**

At normal operation the PFC section operates with dual loop control. An inner loop, which includes OP2, C1, FF1 and the PFC's driver, controls the shape of the line current by average current control enabling either continuous or discontinuous operation. By the outer loop, which is supported by OP1, the multiplier, OP2, C1, FF1 and the PFC's driver, the PFC output voltage is controlled. Furthermore there is a third control loop composed of OTA1, OP2, C1, FF1 and the PFC's driver, which allows the PFC section to be operated as an auxiliary power supply even when the PWM section is disabled. With disabled PWM section, however, the PFC section is operated with half of its nominal operating frequency in order to reduce the overall current consumption.

Based on a pulse-width-modulation, which is leading edge triggered with respect to the internal clock reference CLK OUT and which is trailing edge modulated according to the PFC ramp signal  $V_{\rm PFC RMP}$  and the output voltage of OP2  $V_{\rm PFC CC}$  (see **Figure 18**), the PFC section is designed for a maximum duty cycle of ca. 94% to achieve minimal line current gaps.

#### **PWM Section**

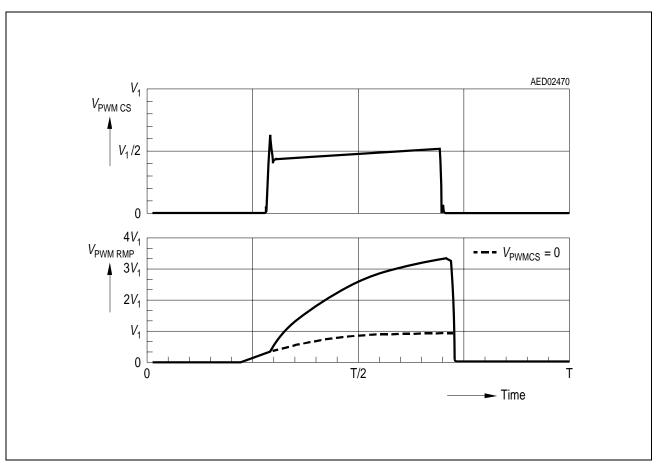

The PWM section is equipped with improved current mode control containing effective slope compensation as well as enhanced spike suppression in contrast to the commonly used leading edge current blanking. This is achieved by the chain of operational amplifier OP3, voltage source  $V_1$  and the 1st order low pass filter composed of  $R_1$  and an external capacitor, which is connected to pin 15 (PWM RMP). For crosstalk suppression between PFC and PWM section a signal-to-noise ratio comparable to voltage mode controlled PWM's is set by operational amplifier OP3 performing a fivefold amplification of the PWM load current, which is sensed by an external shunt resistor. In order to simultaneously perform effective slope compensation and to suppress leading spikes, which are due to parasitic capacitances being discharged whenever the power transistor is switched on, the resulting signal is subsequently increased by the constant voltage of  $V_1$  and finally fed into the 1st order low pass filter. The peak ramp voltage, that in this way can be reached, amounts to ca. 6.5 V. By combination of voltage source  $V_1$  and the following low pass filter a basic ramp (step response) with a leading notch is created, which will fully compensate a leading spike (see Figure 12) provided, the external capacitor at pin 15 (PWM RMP) and the external current sensing shunt resistor are scaled properly.

The pulse-width-modulation of the PWM section is trailing edge modulated according to the PWM ramp signal  $V_{\text{PWM RMP}}$  at pin 15 (PWM RMP) and the input voltage  $V_{\text{PWM IN}}$  at pin 14 (PWM IN) (see **Figure 18**). In contrast to the PFC section, however, the pulse-width-modulation of the PWM section is trailing edge triggered with respect to the internal clock reference CLK OUT in order to avoid undesirable electromagnetic interference of both sections. Moreover the maximum duty cycle of the PWM is limited to 50% to prevent transformer saturation.

By means of the above mentioned improved current mode control a stable pulse-widthmodulation from maximum load down to no load is achieved. Finally, in case of no load conditions the PWM section may as well be disabled by shorting pin 13 (PWM SS) to ground.

# 3 Functional Block Description

#### Gate Drive

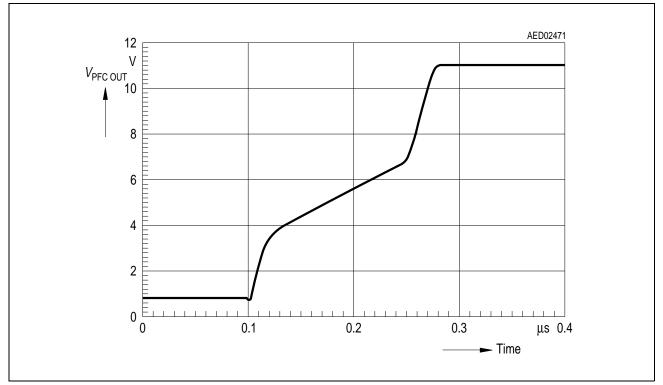

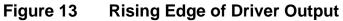

Both PFC and PWM section use fast totem pole gate drives at pin 8 (PFC OUT) and pin 10 (PWM OUT) respectively, which are designed to avoid cross conduction currents and which are equipped with Zener diodes (Z1, Z2) in order to improve the control of the attached power transistors as well as to protect them against undesirable gate overvoltages. At voltages below the undervoltage lockout threshold these gate drives are active low. In order to keep the switching losses of the involved power diodes low and to minimize electromagnetic emissions, both gate drives are optimized for soft switching operation. This is achieved by a novel slope control of the rising edge at each driver's output (see **Figure 13**).

#### Oscillator

The TDA 16888's clock signals as well as the PFC voltage ramp are provided by the internal oscillator. The oscillator's frequency is set by an external resistor connected to pin 16 (ROSC) and ground (see **Figure 5**). The corresponding capacitor, however, is integrated to guarantee a low current consumption and a high resistance against electromagnetic interferences. In order to ensure superior precision of the clock frequency, the clock signal CLK OSC is derived from the minima and maxima of a triangular instead of a saw-tooth signal (see **Figure 18**). Furthermore, to provide a clock reference CLK OUT with exactly 50% duty cycle, the frequency of the oscillator's clock signal CLK OSC is halved by a D-latch before being fed into the PFC and PWM section respectively.

The ramp signal of the PFC section  $V_{\text{PFC RMP}}$  is composed of a slowly falling and a steeply rising edge, the latter of which is triggered by the rising edge of the clock reference CLK OUT. This ramp has been reversed in contrast to the common practice, in order to simultaneously allow for current measurement at pin 5 (GND S) and for external compensation of OP2 by means of pin 5 (GND S) and pin 3 (PFC CC). The slope of the falling edge, which in conjunction with the output of OP2 controls the pulse-width-modulation of the PFC output signal  $V_{\text{PFC OUT}}$ , is derived from the current set by the external resistor at pin 16 (ROSC). In this way a constant amplitude of the ramp signal (ca. 4.5 V) is ensured. In contrast, the slope of the rising edge, which marks the minimum blanking interval and therefore limits the maximum duty cycle  $t_{\text{on,max}}$  of the PFC output signal, is determined by an internal current source.

In contrast to the PFC section the ramp signal of the PWM section is trailing edge triggered with respect to the internal clock reference CLK OUT to avoid undesirable electromagnetic interference of both sections. Moreover, the maximum duty cycle of the PWM is limited by the rising edge of the clock reference CLK OUT to 50% to prevent transformer saturation.

The oscillator can be synchronized with an external clock signal supplied at pin 12 (SYNC). As long as this clock signal is H the oscillator's triangular signal  $V_{OSC}$  is interrupted and its clock signal CLK OSC is H (see Figure 19 and Figure 20). However, as soon as the external clock changes from H to L the oscillator is released. Correspondingly, by means of an external clock signal supplied at pin 12 (SYNC) the oscillator frequency  $f_{OSC}$  set by an external resistor at pin 16 (ROSC) can be varied on principle only within the range from 0.66  $f_{OSC}$  to 2  $f_{OSC}$ . Please note, that the slope of the falling edge of the PFC ramp is not influenced by the synchronization frequency. Instead the lower voltage peak is modulated. Consequently, on the one hand at high synchronization frequencies  $f_{SYNC} > f_{OSC}$  the amplitude of the ramp signal and correspondingly its signal-to-noise ratio is decreased (see Figure 19). On the other hand at low synchronization frequencies  $f_{SYNC} < f_{OSC}$  the lower voltage peak is clamped to the minimum ramp voltage (typ. 1.1 V), that at least can be achieved (see Figure 20), which may cause undefined PFC duty cycles as the voltage  $V_{\text{PFC,CC}}$  at pin 3 (PFC CC) drops below this threshold. However, if the oscillator has to be synchronized over a wide frequency range, a synchronization by means of the sink current at pin 16 (ROSC) has to be preferred to a synchronization by means of pin 12 (SYNC).

In order to reduce the overall current consumption under low load conditions, the oscillator frequency itself is halved as long as the voltage at pin 13 (PWM SS) is less than 0.4 V (disabled PWM section).

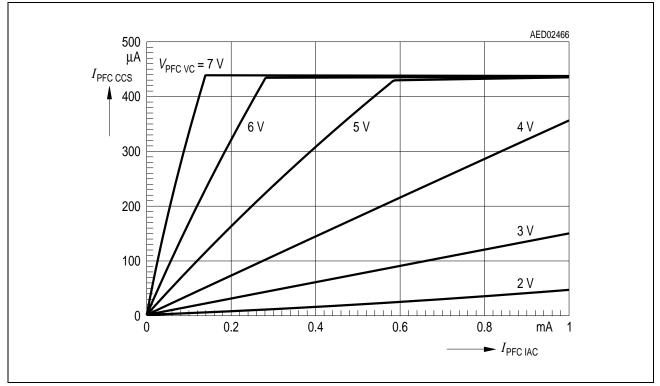

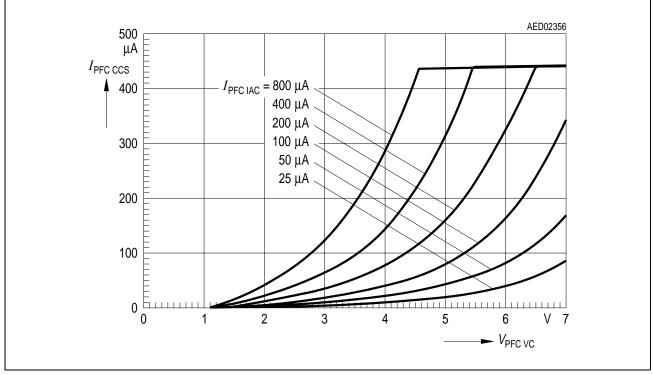

#### **Multiplier**

The multiplier serves to provide the controlled current  $I_{QM}$  by combination of the shape of the sinusoidal input current  $I_{M1}$  derived from the voltage at pin 1 (PFC IAC) by means of the 10 k $\Omega$  resistor  $R_2$ , the magnitude of the PFC output voltage  $V_{M2}$  given at pin 18 (PFC VC) and the possibility for soft overvoltage protection  $V_{M3}$  (see **Chapter Protection Circuitry**). By means of this current the required power factor as well as the magnitude of the PFC output voltage is ensured. To achieve an excellent performance over a wide range of output power and input voltage, the input voltage  $V_{M2}$  is amplified by an exponential function before being fed into the multiplier (see **Figure 8**).

#### Voltage Amplifier OP1

Being part of the outer loop the error amplifier OP1 controls the magnitude of the PFC output voltage by comparison of the PFC output voltage measured at pin 17 (PFC FB) with an internal reference voltage. The latter is fixed to 5 V in order to achieve immunity from external noise. To allow for individual feedback the output of OP1 is connected to pin 18 (PFC VC).

#### **Current Amplifier OP2**

Being part of the inner loop the error amplifier OP2 controls the shape of the line current by comparison of the controlled current  $I_{QM}$  with the measured average line current. This is achieved by setting the pulse width of the PFC gate drive in conjunction with the comparator C1. In order to limit the voltage range supplied at pin 4 (PFC CS) and at pin 5 (GND S), clamping diodes D1, D2 and D3 are connected with these pins and ground. To allow for individual feedback the output of OP2 is connected to pin 3 (PFC CC).

#### **Ramp Amplifier OP3**

For crosstalk suppression between PFC and PWM section a signal-to-noise ratio comparable to voltage mode controlled PWMs is set by operational amplifier OP3 performing a fivefold amplification of the PWM load current, which is sensed by an external shunt resistor. In order to suppress leading spikes, which are due to parasitic capacitances being discharged whenever the power transistor is switched on, the resulting signal is subsequently increased by the constant voltage of  $V_1$  and finally fed into a 1st order low pass filter. By combination of voltage source  $V_1$  and the following low pass filter a step response with a leading notch is created, which will fully compensate a leading spike (see **Figure 12**) provided, the external capacitor at pin 15 (PWM RMP) and the external current sensing shunt resistor are scaled properly.

#### **Operational Transconductance Amplifier OTA1**

The TDA 16888's auxiliary power supply mode is controlled by the fast operational transconductance amplifier OTA1. When under low load or no load conditions a voltage below 5 V is sensed at pin 20 (AUX VS), it will start to superimpose its output on the output  $Q_M$  of the multiplier and in this way will replace the error amplifier OP1 and the multiplier. At normal operation, however, when the voltage at pin 20 (AUX VS) is well above 5 V, this operational transconductance amplifier is disabled.

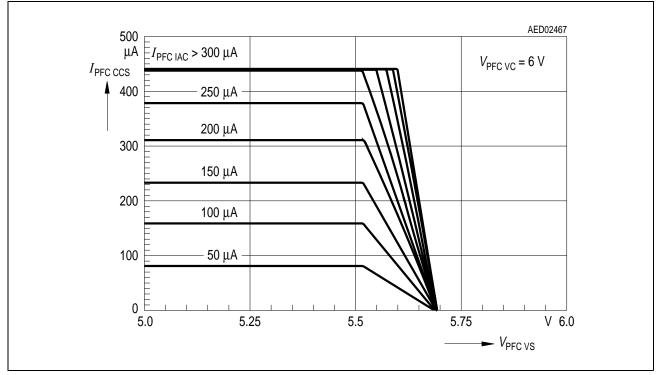

#### **Operational Transconductance Amplifier OTA2**

By means of the operational transconductance amplifier OTA2 sensing at pin 19 (PFC VS) a fast but soft overvoltage protection of the PFC output voltage is achieved, which when being activated ( $V_{PFC VS} > 5.5 V$ ) will cause a well controlled throttling of the multiplier output  $Q_M$  (see **Figure 9**).

#### **Operational Transconductance Amplifier OTA3**

In order to achieve offset compensation of error amplifier OP2 under low load conditions, that will not suffice to start OTA1, the operational transconductance amplifier OTA3 is introduced. It will start operation as soon as these conditions are reached, i.e. the voltage at pin 18 (PFC VC) falls below 1.2 V.

#### Comparator C1

The comparator C1 serves to adjust the duty cycle of the PFC gate drive. This is achieved by comparison of the output voltage of OP2 given at pin 3 (PFC CC) and the voltage ramp of the oscillator.

#### Comparator C2

The comparator C2 serves to prevent the external circuitry from destruction by immediately switching the PFC output PFC OUT (pin 8) off, if the voltage at pin 19 (PFC VS) drops below 1 V due to a broken wire.

#### Comparator C3

By means of this extremely fast comparator sensing at pin 6 (PFC CL) peak current limitation is realized. When being activated ( $V_{PFC CL} < 1 V$ ) it will immediately shut down the gate drive of the PFC section (pin 8, PFC OUT). In order to protect C3 against undervoltages at pin 6 (PFC CL) due to large inrush currents, this pin is equipped with an additional clamping diode D4.

#### Comparator C4

This comparator along with the TDA 16888's power management serves to reset the PWM section's soft start at pin 13 (PWM SS). C4 becomes active as soon as an undervoltage ( $V_{PFC VS} < 4 V$ ) of the PFC output voltage is sensed at pin 19 (PFC VS).

#### Comparator C5

Based on the status of the PWM section's soft start at pin 13 (PWM SS), the comparator C5 controls the bias of the entire PWM section. In this way the PWM section is switched off giving a very low quiescent current, until its soft start is released.

#### Comparator C6

Overvoltage protection of the PWM section's input voltage sensed at pin 19 (PFC VS) is realized by comparator C6, which when being activated will immediately shut down both gate drives PFC OUT (pin 8) and PWM OUT (pin 10).

#### Comparator C7

This comparator sensing at pin 13 (PWM SS) and at pin 15 (PWM RMP) controls the pulse width modulation of the PWM section during the soft start. This is done right after the PWM section is biased by comparator C5.

#### Comparator C8

The control of the pulse width modulation of the PWM section is taken over by comparator C8 as soon as the soft start is finished. This is achieved by comparison of the PWM output voltage at pin 14 (PWM IN) and the PWM voltage ramp at pin 15 (PWM RMP).

#### Comparator C9

By means of this extremely fast comparator sensing at pin 11 (PWM CS) peak current limitation is realized. When being activated ( $V_{PWM CS} > 1 V$ ) it will immediately shut down the gate drive of the PWM section (PWM OUT).

#### Comparator C10

By means of the threshold of 0.4 V the comparator C10 allows the PWM duty cycle to be continuously controlled from 0 to 50%. As long as the ramp voltage at pin 15 (PWM RMP) is below this threshold the gate drive of the PWM section (pin 10, PWM OUT) is turned off.

# 4 Electrical Characteristics

#### 4.1

Absolute Maximum Ratings  $T_A = -25$  to 85 °C

| Parameter#                           | Symbol               | Limit Values |                 | Unit | Remarks                          |  |

|--------------------------------------|----------------------|--------------|-----------------|------|----------------------------------|--|

|                                      |                      | min.         | max.            |      |                                  |  |

| $V_{\rm CC}$ supply voltage          | Vs                   | - 0.3        | V <sub>Z3</sub> | V    | $V_{Z3}$ = Zener voltage of Z3   |  |

| Zener current of Z3                  | I <sub>Z3</sub>      | _            | 50              | mA   | -                                |  |

| $V_{REF}$ voltage                    | $V_{VREF}$           | - 0.3        | 8               | V    | $V_{\rm VREF} < V_{\rm S}$       |  |

| ROSC voltage                         | V <sub>ROSC</sub>    | - 0.3        | 8               | V    | $V_{\rm ROSC} < V_{\rm S}$       |  |

| SYNC voltage                         | V <sub>SYNC</sub>    | - 0.3        | 8               | V    | -                                |  |

| PFC FB voltage                       | $V_{\rm PFCFB}$      | - 0.3        | 8               | V    | -                                |  |

| PFC IAC voltage                      | V <sub>PFC IAC</sub> | - 0.3        | 15              | V    | -                                |  |

| AUX VS voltage                       | V <sub>AUX VS</sub>  | - 0.3        | 8               | V    | -                                |  |

| PFC VS voltage                       | $V_{\rm PFCVS}$      | - 0.3        | 8               | V    | $ I_{\rm PFC VS}  < 1  \rm mA$   |  |

| PFC CL voltage                       | $V_{\rm PFCCL}$      | - 1          | 3               | V    | $ I_{\rm PFC  CL}  < 1  \rm mA$  |  |

| PWM SS voltage                       | V <sub>PWM SS</sub>  | - 0.3        | 8               | V    | $V_{\rm PWM SS} < V_{\rm VREF}$  |  |

| PWM IN voltage                       | $V_{\rm PWM  IN}$    | - 0.3        | 8               | V    | -                                |  |

| PWM RMP voltage                      | $V_{\rm PWM RMP}$    | - 0.3        | 8               | V    | $V_{\rm PWM RMP} < V_{\rm VREF}$ |  |

| PWM CS voltage                       | $V_{\rm PWMCS}$      | - 0.3        | 3               | V    | -                                |  |

| PFC VC voltage                       | $V_{\rm PFC VC}$     | - 0.3        | 8               | V    | -                                |  |

| PFC VC current                       | I <sub>PFC VC</sub>  | - 20         | 20              | mA   | -                                |  |

| PFC CS current                       | I <sub>PFC CS</sub>  | - 5          | 5               | mA   | -                                |  |

| GND S current                        | I <sub>GND S</sub>   | - 5          | 5               | mA   | -                                |  |

| PFC CC voltage                       | $V_{\rm PFCCC}$      | - 0.3        | 8               | V    | -                                |  |

| PFC CC current                       | I <sub>PFC CC</sub>  | - 20         | 20              | mA   | -                                |  |

| PFC/PWM OUT DC current               | I <sub>OUT</sub>     | - 100        | 100             | mA   | -                                |  |

| PFC/PWM OUT peak<br>clamping current | I <sub>OUT</sub>     | _            | 200             | mA   | $V_{\rm OUT}$ = High             |  |

| PFC/PWM OUT peak clamping current    | I <sub>OUT</sub>     | - 500        | _               | mA   | $V_{\sf OUT}$ = Low              |  |

| Junction temperature                 | TJ                   | - 40         | 150             | °C   | -                                |  |

#### 4.1 Absolute Maximum Ratings (cont'd)

| $T_{\Delta} = -25$ | to | 85 | °C |

|--------------------|----|----|----|

|--------------------|----|----|----|

| Parameter#          | Symbol            | Limit Values |      | Unit | Remarks    |  |  |

|---------------------|-------------------|--------------|------|------|------------|--|--|

|                     |                   | min.         | max. |      |            |  |  |

| Storage temperature | T <sub>S</sub>    | - 65         | 150  | °C   | -          |  |  |

| Thermal resistance  | R <sub>thJA</sub> | -            | 60   | K/W  | P-DIP-20-5 |  |  |

| Thermal resistance  | R <sub>thJA</sub> | -            | 70   | K/W  | P-DSO-20-1 |  |  |

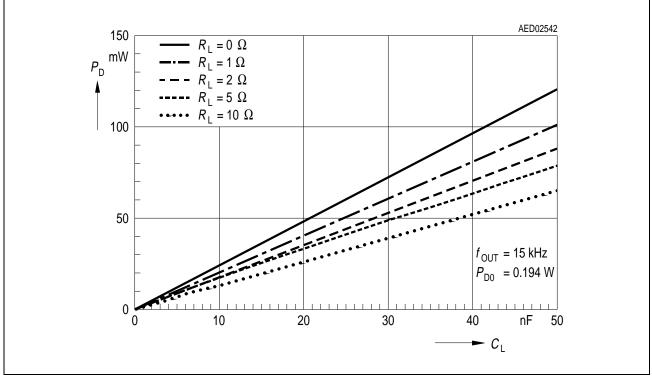

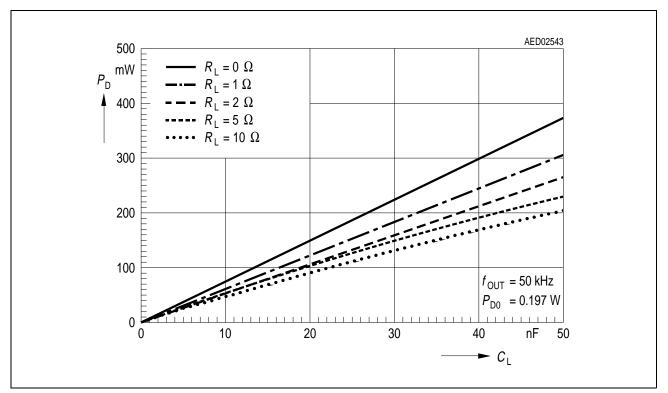

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. To avoid destruction make sure, that for any pin except for pins PFC OUT and PWM OUT the currents caused by transient processes stay well below 100 mA. For the same reason make sure, that any capacitor that will be connected to pin 9 (V<sub>CC</sub>) is discharged before assembling the application circuit. In order to characterize the gate driver's output performance **Figure 14**, **Figure 15**, **Figure 16** and **Figure 17** are provided, instead of referring just to a single parameter like the maximum gate charge or the maximum output energy.

| Parameter                   | Symbol               | Limit Values |          | Unit | Remarks                        |  |  |

|-----------------------------|----------------------|--------------|----------|------|--------------------------------|--|--|

|                             |                      | min.         | max.     |      |                                |  |  |

| $V_{\rm CC}$ supply voltage | Vs                   | 0            | $V_{Z3}$ | V    | $V_{Z3}$ = Zener voltage of Z3 |  |  |

| Zener current               | I <sub>Z3</sub>      | 0            | 50       | mA   | Limited by $T_{J,max}$         |  |  |

| PFC/PWM OUT current         | I <sub>OUT</sub>     | - 1          | 1.5      | А    | -                              |  |  |

| PFC IAC input current       | I <sub>PFC IAC</sub> | 0            | 1        | mA   | -                              |  |  |

| PFC/PWM frequency           | $f_{\rm OUT}$        | 15           | 200      | kHz  | -                              |  |  |

| Junction temperature        | TJ                   | - 25         | 125      | °C   | -                              |  |  |

#### 4.2 Operating Range

Note: Within the operating range the IC operates as described in the functional description. In order to characterize the gate driver's output performance **Figure 14**, **Figure 15**, **Figure 16** and **Figure 17** are provided, instead of referring just to a single parameter like the maximum gate charge or the maximum output energy.

#### 4.3 Characteristics

#### **Supply Section**

| Parameter                   | Symbol          | Limit Values |      |      | Unit | Test Condition                                                                                                                            |

|-----------------------------|-----------------|--------------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                             |                 | min.         | typ. | max. | 1    |                                                                                                                                           |

| Zener voltage <sup>1)</sup> | V <sub>Z3</sub> | 16.0         | 17.5 | 19.0 | V    | <i>I</i> <sub>Z3</sub> = 30 mA                                                                                                            |

| Zener current               | I <sub>Z3</sub> | -            | -    | 500  | μA   | $V_{\rm S} \le 15.5 \ { m V}^{2)}$                                                                                                        |

| Quiescent supply current    | I <sub>S</sub>  | -            | -    | 12   | mA   | $V_{\text{PWM SS}} = 0 \text{ V}$ $R_{\text{ROSC}} = 51 \text{ k}\Omega$ $C_{\text{L}} = 0 \text{ V}$ PFC enabled<br>PWM disabled         |

|                             |                 | _            | -    | 15   | mA   | $V_{\text{PWM SS}} = 6 \text{ V}$<br>$R_{\text{ROSC}} = 51 \text{ k}\Omega$<br>$C_{\text{L}} = 0 \text{ F}$<br>PFC enabled<br>PWM enabled |

| Supply current              | I <sub>S</sub>  | -            | -    | 40   | mA   | $V_{\rm PWM SS} = 6 V$<br>$R_{\rm ROSC} = 51 k\Omega$<br>$C_{\rm L} = 4.7 nF$<br>PFC enabled<br>PWM enabled                               |

<sup>1)</sup> See **Figure 3**

<sup>2)</sup> Design characteristics (not meant for production testing)

Note: The electrical characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range  $T_A$  from – 25 °C to 85 °C Typical values represent the median values, which are related to production processes. If not otherwise stated, a supply voltage of  $V_S = 15$  V is assumed.

#### Undervoltage Lockout

| Parameter                                                 | Symbol            | Li   | mit Valu | les  | Unit | Test Condition                                                                                   |

|-----------------------------------------------------------|-------------------|------|----------|------|------|--------------------------------------------------------------------------------------------------|

|                                                           |                   | min. | typ.     | max. |      |                                                                                                  |

| Power up,<br>rising voltage<br>threshold <sup>1)</sup>    | V <sub>S,UP</sub> | 13.0 | 14.0     | 14.5 | V    | -                                                                                                |

| Power down,<br>falling voltage<br>threshold <sup>1)</sup> | $V_{\rm S,DWN}$   | 10.5 | 11.0     | 11.5 | V    | -                                                                                                |

| Power up,<br>threshold current                            | I <sub>S,UP</sub> | _    | 23       | 100  | μA   | $V_{\rm S} = V_{\rm S,UP} - 0.1 \text{ V}$ $V_{\rm PFC \ CL} < 0.3 \text{ V}^{2)}$ Stand-by mode |

<sup>1)</sup> See Figure 3

$^{2)}\,$  To ensure the voltage fallback of pin PFC CL is disabled.

#### Internal Voltage Reference

| Parameter                 | Symbol           | Limit Values |      |      | Unit | Test Condition                   |

|---------------------------|------------------|--------------|------|------|------|----------------------------------|

|                           |                  | min.         | typ. | max. |      |                                  |

| Trimmed reference voltage | V <sub>REF</sub> | 4.9          | 5.0  | 5.1  | V    | Measured at pin PFC VC           |

| Line regulation           | $\Delta V_{REF}$ | -            | _    | 40   | mV   | $\Delta V_{\rm S} = 3 \text{ V}$ |

#### External Voltage Reference

| Parameter                                      | Symbol                | Symbol Limit Values |      |      | Unit | <b>Test Condition</b>                                                                                                      |

|------------------------------------------------|-----------------------|---------------------|------|------|------|----------------------------------------------------------------------------------------------------------------------------|

|                                                |                       | min.                | typ. | max. |      |                                                                                                                            |

| Buffered output voltage                        | $V_{VREF}$            | 7.2                 | 7.5  | 7.8  | V    | $-3 \text{ mA} \le I_{\text{VREF}} \le 0$                                                                                  |

| Line regulation                                | $\Delta V_{\rm VREF}$ | -                   | -    | 50   | mV   | $\Delta V_{\rm S} = 3 \text{ V}$                                                                                           |

| Load regulation                                | $\Delta V_{VREF}$     | 0                   | 40   | 100  | mV   | $\Delta I_{\text{VREF}} = 2 \text{ mA}$                                                                                    |

| Maximum output current <sup>1)</sup>           | I <sub>VREF</sub>     | - 10                | - 6  | - 4  | mA   | $V_{\rm VREF}$ = 6.5 V                                                                                                     |

| Short circuit current <sup>1)</sup>            | I <sub>VREF</sub>     | -                   | -2   | _    | mA   | $V_{\text{VREF}} = 0 \text{ V}$                                                                                            |

| Shutdown hysteresis, rising voltage threshold  | $V_{VREF}$            | -                   | 6.6  | -    | V    | _                                                                                                                          |

| Shutdown hysteresis, falling voltage threshold | $V_{VREF}$            | -                   | 6.2  | -    | V    | -                                                                                                                          |

| Shutdown delay                                 | t <sub>d,VREF</sub>   | -                   | 500  | -    | ns   | $V_{\text{VREF}} = 5 \text{ V}^{2(3)}$ $V_{\text{PFC OUT}} = 3 \text{ V}^{2(3)}$ $V_{\text{PWM OUT}} = 3 \text{ V}^{2(3)}$ |

<sup>1)</sup> See Figure 4

<sup>2)</sup> Design characteristics (not meant for production testing)

<sup>3)</sup> Transient reference value

#### Oscillator

| Parameter                             | Symbol              | Limit Values |      |            | Unit | <b>Test Condition</b>                                                   |

|---------------------------------------|---------------------|--------------|------|------------|------|-------------------------------------------------------------------------|

|                                       |                     | min.         | typ. | max.       |      |                                                                         |

| PFC/PWM frequency <sup>1)</sup>       | $f_{\rm OUT50}$     | 43           | 50   | 57         | kHz  | $R_{\rm ROSC} = 110 \ \rm k\Omega$                                      |

| PFC/PWM frequency <sup>1)</sup>       | $f_{\rm OUT100}$    | 87           | 100  | 113        | kHz  | $R_{\rm ROSC} = 51 \ \rm k\Omega$                                       |

| PFC/PWM frequency,<br>line regulation | $\Delta f_{OUT}$    | _            | _    | 1          | %    | $\Delta V_{\rm S} = 3 \text{ V}$<br>$R_{\rm ROSC} = 51 \text{ k}\Omega$ |

| Maximum ramp voltage                  | $V_{\rm PFC \ RMP}$ | 5.0          | 5.4  | 5.6        | V    | -                                                                       |

| Minimum ramp voltage                  | $V_{\rm PFC \ RMP}$ | 0.8          | 1.1  | 1.4        | V    | -                                                                       |

| SYNC, low level voltage               | $V_{\rm SYNC}$      | -            | -    | 0.4        | V    | -                                                                       |

| SYNC, high level voltage              | V <sub>SYNC</sub>   | 3.5          | -    | $V_{VREF}$ | V    | -                                                                       |

| SYNC, input current                   | I <sub>SYNC</sub>   | -            | -    | 20         | μA   | $V_{\rm SYNC}$ < 0.4 V                                                  |

|                                       |                     | -            | -    | 150        | μA   | $V_{\rm SYNC}$ = 3.5 V                                                  |

<sup>1)</sup> See Figure 5

#### **PFC Section**

| Parameter                                                           | Symbol              | Li    | mit Va | lues  | Unit | Test Condition                                                                                   |

|---------------------------------------------------------------------|---------------------|-------|--------|-------|------|--------------------------------------------------------------------------------------------------|

|                                                                     |                     | min.  | typ.   | max.  |      |                                                                                                  |

| Max duty cycle <sup>1)</sup>                                        | D <sub>on,PFC</sub> | 91    | 94     | 98    | %    | $V_{\rm PFC \ OUT} = 2 \ V^{3)}$ $R_{\rm ROSC} = 51 \ k\Omega$ $C_{\rm L} = 4.7 \ \rm nF$        |

| Multiplier throttling<br>(OTA2), threshold<br>voltage <sup>2)</sup> | V <sub>PFC VS</sub> | 5.2   | 5.5    | 5.8   | V    | 0.9 $I_{PFC CS}$<br>$I_{PFC IAC} = 100 \mu A$<br>$V_{PFC VC} = 6 V$<br>OTA1 disabled             |

| Overvoltage protection<br>(C6), rising voltage<br>threshold         | V <sub>PFC VS</sub> | 5.8   | 6      | 6.2   | V    | _                                                                                                |

| Overvoltage protection<br>(C6), falling voltage<br>threshold        | V <sub>PFC VS</sub> | 5.3   | 5.5    | 5.7   | V    | _                                                                                                |

| Overvoltage protection (C6), turn-off delay                         | t <sub>d,OV</sub>   | -     | 2      | -     | μs   | $V_{\rm PFC \ VS} = 6.5 \ V^{3)4)} V_{\rm PFC \ OUT} = 3 \ V^{3)4)}$                             |

| Broken wire detection (C2), threshold voltage                       | $V_{\rm PFC  VS}$   | 0.93  | 1      | 1.07  | V    | _                                                                                                |

| Voltage sense, input current                                        | I <sub>PFC VS</sub> | 0.2   | 0.45   | 0.7   | μA   | $V_{\rm PFC VS}$ = 1 V                                                                           |

| Current limitation (C3), threshold voltage                          | V <sub>PFC CL</sub> | 0.93  | 1      | 1.07  | V    | _                                                                                                |

| Current limitation (C3), input current                              | I <sub>PFC CL</sub> | 1     | -      | 10    | μA   | $V_{\rm PFC \ CL} = 1 \ V$                                                                       |

| Current limitation (C3, D4), clamping voltage                       | $V_{\rm PFC\ CL}$   | - 0.9 | -      | - 0.1 | V    | $I_{\rm PFC \ CL} = -500 \ \mu A$                                                                |

| Current limitation (C3),<br>turn-off delay                          | t <sub>d,CL</sub>   | 30    | -      | 150   | ns   | $V_{\rm PFC \ CL} = 0.75 \ V^{3)} \\ V_{\rm PFC \ OUT} = 3 \ V^{3)} \\ C_{\rm L} = 4.7 \ \rm nF$ |

<sup>1)</sup> See Figure 6

<sup>2)</sup> See Figure 9

<sup>3)</sup> Transient reference value

<sup>4)</sup> Design characteristics (not meant for production testing)

#### Multiplier

| Parameter                               | Symbol               | Li    | mit Valu | les   | Unit | Test Condition                                                                         |

|-----------------------------------------|----------------------|-------|----------|-------|------|----------------------------------------------------------------------------------------|

|                                         |                      | min.  | typ.     | max.  |      |                                                                                        |

| Input current                           | I <sub>PFC IAC</sub> | 0     | -        | 1     | mA   | -                                                                                      |

| Input voltage                           | $V_{\rm PFC \ VC}$   | 0     | -        | 6.7   | V    | -                                                                                      |

| Exponential function, threshold voltage | $V_{\rm PFC \ VC}$   | _     | 1.1      | -     | V    | 1)2)                                                                                   |

| Maximum output current                  | I <sub>PFC CS</sub>  | - 320 | - 420    | - 550 | μA   | OTA1 disabled                                                                          |

| Output current <sup>3)</sup>            | I <sub>PFC CS</sub>  | -     | - 100    | - 500 | nA   | $I_{\rm PFC \ IAC} = 0 \ {\rm A}$<br>$V_{\rm PFC \ VC} = 2 \ {\rm V}$<br>OTA1 disabled |

|                                         |                      | -     | - 1.2    | -     | μA   | $I_{\rm PFC \ IAC} = 25 \ \mu A$<br>$V_{\rm PFC \ VC} = 2 \ V$<br>OTA1 disabled        |

|                                         |                      | _     | - 10     | _     | μA   | $I_{\rm PFC \ IAC} = 25 \ \mu A$<br>$V_{\rm PFC \ VC} = 4 \ V$<br>OTA1 disabled        |

|                                         |                      | -     | - 40     | -     | μA   | $I_{\rm PFC \ IAC} = 100 \ \mu A$<br>$V_{\rm PFC \ VC} = 4 \ V$<br>OTA1 disabled       |

|                                         |                      | _     | - 150    | -     | μA   | $I_{\rm PFC \ IAC} = 400 \ \mu A$<br>$V_{\rm PFC \ VC} = 4 \ V$<br>OTA1 disabled       |

|                                         |                      | _     | - 170    | _     | μA   | $I_{\rm PFC \ IAC}$ = 100 µA<br>$V_{\rm PFC \ VC}$ = 6 V<br>OTA1 disabled              |

<sup>1)</sup> Design characteristics (not meant for production testing)

<sup>2)</sup> For input voltages below this threshold the multiplier output current remains constant. For input voltages above this threshold the output rises exponentially (see **Figure 8**).

<sup>3)</sup> See Figure 7

#### **Operational Transconductance Amplifier (OTA1)**

| Parameter                                               | Symbol Limit Values |      |      | ues  | Unit | Test Condition                                       |

|---------------------------------------------------------|---------------------|------|------|------|------|------------------------------------------------------|

|                                                         |                     | min. | typ. | max. |      |                                                      |

| Auxiliary power supply, threshold voltage <sup>1)</sup> | V <sub>AUX VS</sub> | 4.8  | 5.0  | 5.2  | V    | $I_{\rm PFC CS} = -1 \ \mu A$<br>Multiplier disabled |

| Input current                                           | I <sub>AUX VS</sub> | -    | _    | 15   | μA   | V <sub>AUX VS</sub> > 5.2 V                          |

|                                                         |                     | - 20 | -    | -    | μA   | $V_{\rm AUX VS}$ < 4.8 V                             |

| Output current                                          | I <sub>PFC CS</sub> | -    | 0    | -    | μA   | $V_{\rm AUX  VS} > 5.2  \rm V^{1)}$                  |

|                                                         |                     | -    | - 30 | —    | μA   | $V_{\rm AUX VS}$ < 4.8 V                             |

<sup>1)</sup> For input voltages below this threshold the output current is linearly increasing until at ca. 4.8 V the maximum output current is reached.

#### **Operational Transconductance Amplifier (OTA3)**

| Parameter                              | Symbol              | Li   | mit Valu | les  | Unit | Test Condition              |

|----------------------------------------|---------------------|------|----------|------|------|-----------------------------|

|                                        |                     | min. | typ.     | max. |      |                             |

| Offset compensation, threshold voltage | V <sub>PFC VC</sub> | 1.1  | 1.2      | -    | V    | -                           |

| Input current                          | I <sub>PFC VC</sub> | - 1  | -        | -    | μA   | 1)                          |

| Output current                         | I <sub>GND S</sub>  | -    | 0        | -    | μA   | V <sub>PFC VC</sub> > 1.2 V |

|                                        |                     | _    | - 10     | -    | μA   | V <sub>PFC VC</sub> < 1.1 V |

<sup>1)</sup> Design characteristics (not meant for production testing)

### Voltage Amplifier (OP1)

| Parameter                            | Symbol Limit Values |      |      |            | Unit | Test Condition                                            |

|--------------------------------------|---------------------|------|------|------------|------|-----------------------------------------------------------|

|                                      |                     | min. | typ. | max.       |      |                                                           |

| Offset voltage                       | V <sub>Off</sub>    | - 4  | _    | 4          | mV   | 1)                                                        |

| Input current                        | I <sub>PFC FB</sub> | - 1  | -    | 1          | μA   | $V_{\rm PFC FB} = 4 V$                                    |

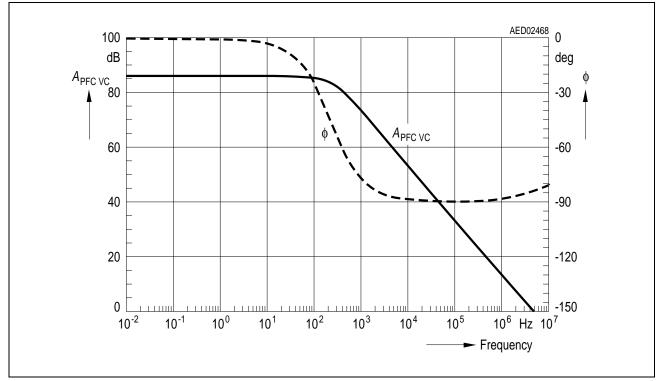

| Open loop gain                       | $A_{\rm PFC VC}$    | _    | 85   | _          | dB   | 2)                                                        |

| Input voltage range                  | $V_{\rm PFC  FB}$   | 0    | -    | 6          | V    | -                                                         |

| Voltage sense,<br>threshold voltage  | V <sub>PFC FB</sub> | 4.9  | 5    | 5.1        | V    | -                                                         |

| Output, maximum<br>voltage           | $V_{\rm PFC VC}$    | 6.3  | -    | $V_{VREF}$ | V    | $I_{\rm PFC VC} = -500 \mu$ A                             |

| Output, minimum<br>voltage           | V <sub>PFC VC</sub> | 0.5  | -    | 1.1        | V    | $I_{\rm PFC VC} = 500 \mu {\rm A}$                        |

| Output, short circuit source current | I <sub>PFC VC</sub> | -    | - 10 | -          | mA   | $V_{\rm PFC \ VC} = 0 \ V$ $V_{\rm PFC \ FB} = 4.9 \ V$   |

| Output, short circuit sink current   | I <sub>PFC VC</sub> | -    | 10   | -          | mA   | $V_{\rm PFC \ VC} = 6.4 \ V$ $V_{\rm PFC \ FB} = 5.1 \ V$ |

<sup>1)</sup> Guaranteed by wafer test

<sup>2)</sup> Design characteristics (not meant for production testing)

### Current Amplifier (OP2)

| Parameter                                             | Symbol                            | Li    | mit Val | ues        | Unit | Test Condition                                                                                     |

|-------------------------------------------------------|-----------------------------------|-------|---------|------------|------|----------------------------------------------------------------------------------------------------|

|                                                       |                                   | min.  | typ.    | max.       | 1    |                                                                                                    |

| Offset voltage                                        | V <sub>Off</sub>                  | - 5   | - 1     | 3          | mV   | -                                                                                                  |

| Input current                                         | $I_{\rm PFCCS}$<br>$I_{\rm GNDS}$ | - 500 | -       | 500        | nA   | -                                                                                                  |

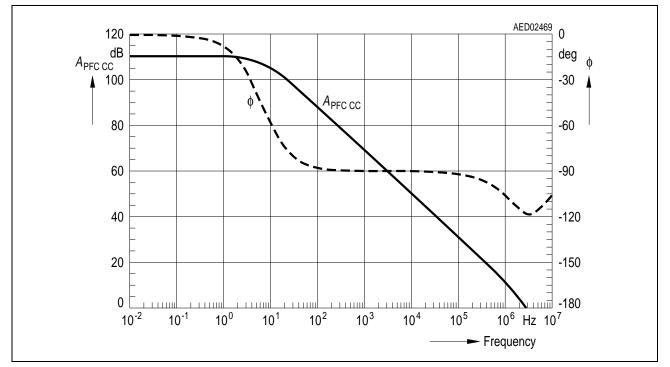

| Open loop gain                                        | $A_{\rm PFC \ CC}$                | -     | 110     | -          | dB   | -                                                                                                  |

| Gain bandwidth product                                | $f_{T}$                           | -     | 2.5     | -          | MHz  | 1)                                                                                                 |

| Phase margin                                          | φ                                 | -     | 60      | -          | 0    | 1)                                                                                                 |

| Common mode voltage range                             | V <sub>CMVR</sub>                 | - 0.2 | -       | 0.5        | V    | 1)                                                                                                 |

| Clamped input voltage,<br>upper threshold<br>(D2, D3) | $V_{ m PFCCS}$ $V_{ m GNDS}$      | 0.4   | -       | 1.0        | V    | $I_{\rm PFC \ CS}$ = 500 µA<br>$I_{\rm GND \ S}$ = 500 µA<br>Multiplier, OTA1<br>and OTA3 disabled |

| Clamped input voltage,<br>lower threshold (D1)        | V <sub>PFC CS</sub>               | - 0.9 | -       | - 0.1      | V    | $I_{\rm PFC \ CS} = -500 \ \mu A$<br>Multiplier and OTA1<br>disabled                               |

| Output, maximum voltage                               | $V_{\rm PFCCC}$                   | 6.3   | -       | $V_{VREF}$ | V    | $I_{\rm PFC \ CC} = -500 \ \mu A$                                                                  |

| Output, minimum voltage                               | V <sub>PFC CC</sub>               | 0.5   | -       | 1.1        | V    | $I_{\rm PFC \ CC} = 500 \ \mu A$                                                                   |

| Output, short circuit source current                  | I <sub>PFC CC</sub>               | -     | - 10    | -          | mA   | $V_{\rm PFC\ CC} = 0\ V$<br>$V_{\rm PFC\ CS} = 0\ V$<br>$V_{\rm GND\ S} = 0.5\ V$                  |

| Output, short circuit sink current                    | I <sub>PFC CC</sub>               | -     | 10      | -          | mA   | $V_{\rm PFC\ CC} = 6.5\ V$<br>$V_{\rm PFC\ CS} = 0.5\ V$<br>$V_{\rm GND\ S} = 0\ V$                |

<sup>1)</sup> Design characteristics (not meant for production testing)

#### **PWM Section**

| Parameter                                       | Symbol                 | Li   | mit Val | ues  | Unit | <b>Test Condition</b>                                                                                             |

|-------------------------------------------------|------------------------|------|---------|------|------|-------------------------------------------------------------------------------------------------------------------|

|                                                 |                        | min. | typ.    | max. |      |                                                                                                                   |

| Undervoltage protection (C4), threshold voltage | $V_{\rm PFC  VS}$      | 3.8  | 4.0     | 4.2  | V    | _                                                                                                                 |

| Bias control (C5),<br>rising voltage threshold  | $V_{\rm BC,Th}$        | _    | 0.45    | -    | V    | _                                                                                                                 |

| Bias control (C5),<br>falling voltage threshold | $V_{\rm BC,Th}$        | _    | 0.4     | -    | V    | _                                                                                                                 |

| Softstart ( $I_1$ ), charging current           | <i>I</i> <sub>11</sub> | 20   | 30      | 40   | μA   | _                                                                                                                 |

| Softstart, maximum voltage                      | $V_{\rm PWMSS}$        | -    | 6.7     | -    | V    | -                                                                                                                 |

| Input voltage                                   | $V_{\rm PWM  IN}$      | 0.4  | -       | 7.4  | V    | -                                                                                                                 |

| PWM IN – GND resistance                         | <i>R</i> <sub>3</sub>  | 75   | 100     | 150  | kΩ   | -                                                                                                                 |

| Ramp (OP3), voltage gain                        | A <sub>OP3</sub>       | _    | 5       | -    | V/V  | -                                                                                                                 |

| Ramp (C10), pulse start threshold voltage       | $V_{RMP}$              | 0.36 | 0.4     | 0.5  | V    | _                                                                                                                 |

| Ramp, maximum voltage                           | $V_{RMP}$              | -    | 6.5     | -    | V    | -                                                                                                                 |

| Ramp ( $V_1$ ), voltage offset                  | $V_{V1}$               | -    | 1.5     | -    | V    | -                                                                                                                 |

| Ramp ( $R_1$ ), output impedance                | $Z_{RMP}$              | _    | 10      | -    | kΩ   | _                                                                                                                 |

| Maximum duty cycle                              | $D_{ m on,PWM}$        | 41   | _       | 50   | %    | $V_{\rm PWM \; OUT} = 2 \; {\rm V}^{1)}$<br>$R_{\rm ROSC} = 51 \; {\rm k}\Omega$<br>$C_{\rm L} = 4.7 \; {\rm nF}$ |

| Current sense (C9), voltage threshold           | $V_{\rm CS,Th}$        | 0.9  | 1.0     | 1.1  | V    | _                                                                                                                 |

| Current sense (C9),<br>overload turn-off delay  | t <sub>d,CS</sub>      | 30   | -       | 250  | ns   | $V_{\rm PWM  CS} = 1.25  {\rm V}^{1)}$<br>$V_{\rm PWM  OUT} = 3  {\rm V}^{1)}$<br>$C_{\rm L} = 4.7  {\rm nF}$     |

<sup>1)</sup> Transient reference value

#### Gate Drive (PWM and PFC Section)

| Parameter                                  | Symbol           | Lin   | nit Val | ues  | Unit | Test Condition                                                                                               |

|--------------------------------------------|------------------|-------|---------|------|------|--------------------------------------------------------------------------------------------------------------|

|                                            |                  | min.  | typ.    | max. |      |                                                                                                              |

| Output, minimum voltage                    | V <sub>OUT</sub> | -     | -       | 1.2  | V    | V <sub>S</sub> = 5 V<br>I <sub>OUT</sub> = 5 mA                                                              |

|                                            |                  | _     | _       | 1.5  | V    | $V_{\rm S}$ = 5 V<br>$I_{\rm OUT}$ = 20 mA                                                                   |

|                                            |                  | _     | 0.8     | _    | V    | $I_{OUT} = 0 \text{ A}$                                                                                      |

|                                            |                  | _     | 1.6     | 2.0  | V    | I <sub>OUT</sub> = 50 mA                                                                                     |

|                                            |                  | - 0.2 | 0.2     | _    | V    | I <sub>OUT</sub> = – 50 mA                                                                                   |

| Output, maximum voltage                    | V <sub>OUT</sub> | 10    | 11      | 12   | V    | $V_{\rm S}$ = 16 V<br>$t_{\rm H}$ = 10 µs<br>$C_{\rm L}$ = 4.7 nF                                            |

|                                            |                  | 10.0  | 10.5    | _    | V    | $V_{\rm S}$ = 12 V<br>$t_{\rm H}$ = 10 µs<br>$C_{\rm L}$ = 4.7 nF                                            |

|                                            |                  | 8.8   | -       | _    | V    | $V_{\rm S} = V_{\rm S,DWN} + 0.2 \text{ V}$<br>$t_{\rm H} = 10 \mu \text{s}$<br>$C_{\rm L} = 4.7 \text{ nF}$ |

| Rise time <sup>1)</sup>                    | t <sub>r</sub>   | -     | 150     | _    | ns   | $V_{OUT} = 2 \text{ V} \dots 8 \text{ V}^{2)}$<br>$C_{L} = 4.7 \text{ nF}$                                   |

|                                            |                  | _     | 100     | _    | ns   | $V_{OUT} = 3 \text{ V} \dots 6 \text{ V}^{2)}$<br>$C_{L} = 4.7 \text{ nF}$                                   |

| Fall time                                  | t <sub>f</sub>   | -     | 30      | _    | ns   | $V_{OUT} = 9 \text{ V} \dots 3 \text{ V}^{2)}$<br>$C_{L} = 4.7 \text{ nF}$                                   |

|                                            |                  | _     | 40      | _    | ns   | $V_{OUT} = 9 \text{ V} \dots 2 \text{ V}^{2)}$<br>$C_{L} = 4.7 \text{ nF}$                                   |

| Output current, rising edge <sup>3)</sup>  | I <sub>OUT</sub> | - 1   | —       | _    | А    | $C_{\rm L} = 4.7 \ {\rm nF}^{4)}$                                                                            |

| Output current, falling edge <sup>3)</sup> | I <sub>OUT</sub> | _     | _       | 1.5  | А    | $C_{\rm L} = 4.7 \ {\rm nF}^{4)}$                                                                            |

<sup>1)</sup> See Figure 13

<sup>2)</sup> Transient reference value

<sup>3)</sup> The gate driver's output performance is characterized in **Figure 14**, **Figure 15**, **Figure 16** and **Figure 17**.

<sup>4)</sup> Design characteristics (not meant for production testing)

Note: If not otherwise stated the figures shown in this section represent typical performance characteristics.

# Figure 3 Undervoltage Lockout Hysteresis and Zener Diode Overvoltage Protection

#### Figure 4 Foldback Characteristic of Pin 2 ( $V_{\text{REF}}$ )

Figure 6 Maximum PFC Duty Cycle

Figure 8 Multiplier Dynamic

Figure 10 Open Loop Gain and Phase Characteristic of Voltage Amplifier OP1

Figure 11 Open Loop Gain and Phase Characteristic of Current Amplifier OP2

Figure 12 PWM Ramp Composition Scheme

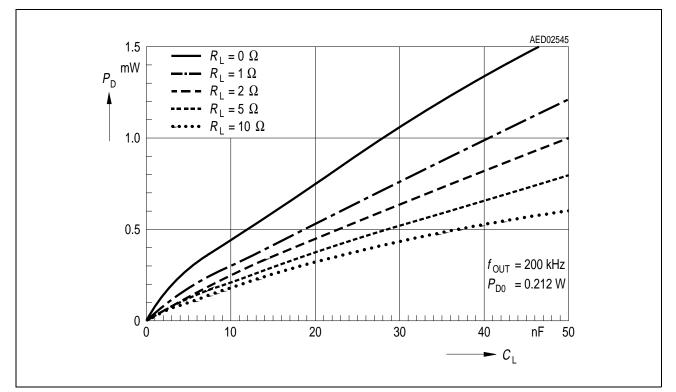

Figure 14 Power Dissipation of Single Gate Driver at  $f_{OUT}$  = 15 kHz

Figure 15 Power Dissipation of Single Gate Driver at  $f_{OUT}$  = 50 kHz

Figure 16 Power Dissipation of Single Gate Driver at  $f_{OUT}$  = 100 kHz

Figure 17 Power Dissipation of Single Gate Driver at  $f_{OUT}$  = 200 kHz

Figure 18 Timing Diagram without Synchronization

**Figure 19** Timing Diagram with Synchronization ( $f_{SYNC} > f_{OSC}$ )

**Figure 20** Timing Diagram with Synchronization ( $f_{SYNC} < f_{OSC}$ )

# 5 Package Outlines

(Plastic Dual In-line Package)

#### Sorts of Packing

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

Dimensions in mm

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

41

Dimensions in mm

# **Total Quality Management**

Qualität hat für uns eine umfassende Bedeutung. Wir wollen allen Ihren Ansprüchen in der bestmöglichen Weise gerecht werden. Es geht uns also nicht nur um die Produktqualität – unsere Anstrengungen gelten gleichermaßen der Lieferqualität und Logistik, dem Service und Support sowie allen sonstigen Beratungs- und Betreuungsleistungen.

Dazu gehört eine bestimmte Geisteshaltung unserer Mitarbeiter. Total Quality im Denken und Handeln gegenüber Kollegen, Lieferanten und Ihnen, unserem Kunden. Unsere Leitlinie ist jede Aufgabe mit "Null Fehlern" zu lösen – in offener Sichtweise auch über den eigenen Arbeitsplatz hinaus – und uns ständig zu verbessern.

Unternehmensweit orientieren wir uns dabei auch an "top" (Time Optimized Processes), um Ihnen durch größere Schnelligkeit den entscheidenden Wettbewerbsvorsprung zu verschaffen.

Geben Sie uns die Chance, hohe Leistung durch umfassende Qualität zu beweisen. Quality takes on an all encompassing significance at Semiconductor Group. For us it means living up to each and every one of your demands in the best possible way. So we are not only concerned with product quality. We direct our efforts equally at quality of supply and logistics, service and support, as well as all the other ways in which we advise and attend to you.

Part of this is the very special attitude of our staff. Total Quality in thought and deed, towards co-workers, suppliers and you, our customer. Our guideline is "do everything with zero defects", in an open manner that is demonstrated beyond your immediate workplace, and to constantly improve.

Throughout the corporation we also think in terms of Time Optimized Processes (top), greater speed on our part to give you that decisive competitive edge.

Give us the chance to prove the best of performance through the best of quality – you will be convinced.

Wir werden Sie überzeugen.

http://www.infineon.com