## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

#### **Features and Benefits**

- 3.3 to 5 V logic supply range

- Power-on reset (POR)

- To 10 MHz data input rate

- CMOS, TTL compatible inputs

- -40°C operation available

- Low-power CMOS logic and latches

- Schmitt trigger inputs for improved noise immunity

- High-voltage current-sink outputs

- Internal pull-up/pull-down resistors

- Output transient-protection diodes

- Single or split supply operation

#### Packages:

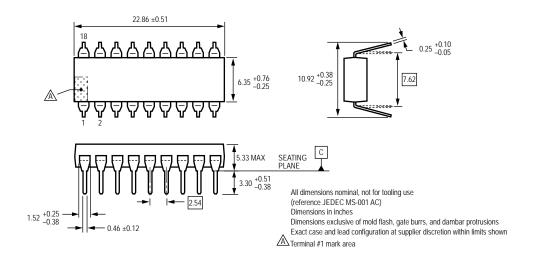

Not to scale

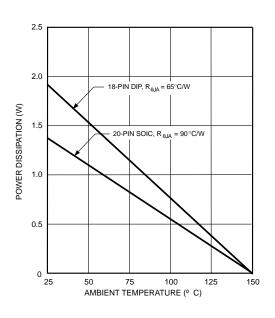

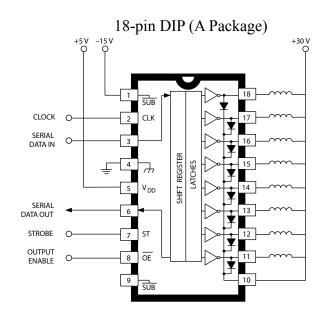

18-pin DIP (Package A)

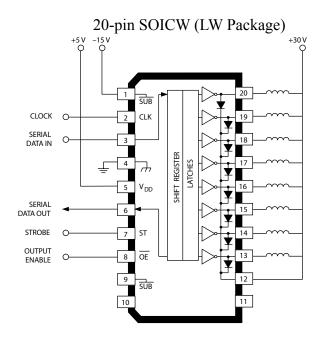

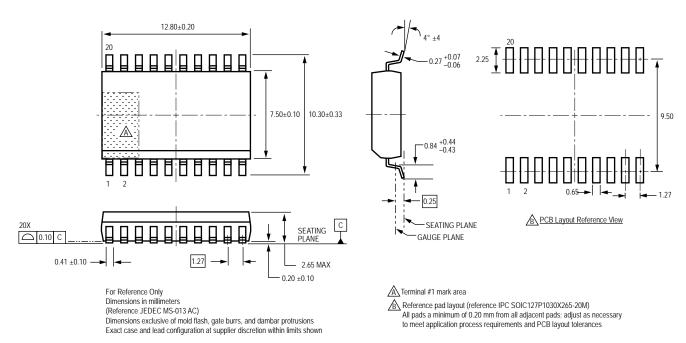

20-pin SOICW (package LW) (drop-in replacement for discontinued 18-pin SOIC variants)

#### Description

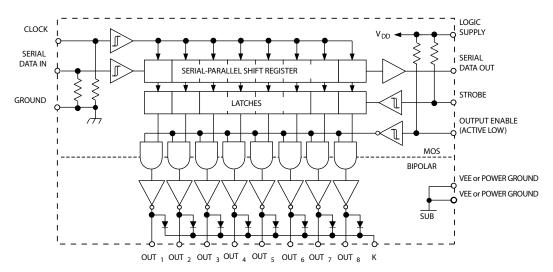

The merging of low-power CMOS logic and bipolar output power drivers using the proprietary DABiC-5 fabrication process permit the A6841 integrated circuits to be used in a wide variety of peripheral power driver applications. Each device has an eight-bit CMOS shift register and CMOS control circuitry, eight CMOS data latches, and eight bipolar current-sinking Darlington output drivers. The 500 mA, NPN Darlington outputs, with integral transient-suppression diodes, are suitable for use with relays, solenoids, and other inductive loads.

All package variations of the A6841 offer premium performance with a minimum output-breakdown voltage rating of  $50 \, \text{V} (35 \, \text{V})$  sustaining). All drivers can be operated with a split supply where the negative supply is up to  $-20 \, \text{V}$ .

The CMOS inputs are compatible with standard CMOS logic levels. TTL circuits may require the use of appropriate pull-up resistors. By using the serial data output, drivers can be cascaded for interface applications requiring additional drive lines.

The A6841 is provided in an 18-pin plastic DIP (suffix A), and a 20-pin wide-body SOIC (suffix LW) with improved thermal characteristics compared to the 18-pin SOIC version it replaces (100% pin-compatible electrically). These devices are lead (Pb) free, with 100% matte tin plated leadframes.

Applications include:

- Relays

- Solenoids

- Inductive loads

#### **Functional Block Diagram**

#### **Selection Guide**

| Part Number     | Package               | Packing              | Ambient       |

|-----------------|-----------------------|----------------------|---------------|

| A6841EA-T       | 18-pin DIP            | 21 pieces per tube   |               |

| A6841ELW-20-T   | 20-pin wide body SOIC | 37 pieces per tube   | –40°C to 85°C |

| A6841ELWTR-20-T | 20-pin wide body SOIC | 1000 pieces per reel |               |

| A6841SA-T       | 18-pin DIP            | 21 pieces per tube   |               |

| A6841SLW-20-T   | 20-pin wide body SOIC | 37 pieces per tube   | –20°C to 85°C |

| A6841SLWTR-20-T | 20-pin wide body SOIC | 1000 pieces per reel |               |

#### **Absolute Maximum Ratings\***

| Characteristic                | Symbol               | Notes                           | Rating                       | Units |

|-------------------------------|----------------------|---------------------------------|------------------------------|-------|

| Logic Supply Voltage          | $V_{DD}$             |                                 | 7                            | V     |

| Emitter Supply Voltage        | V <sub>EE</sub>      |                                 | -20                          | V     |

| Input Voltage Range           | V <sub>IN</sub>      |                                 | -0.3 to V <sub>DD</sub> +0.3 | V     |

| Outrot Valtage                | V <sub>CE</sub>      |                                 | 50                           | V     |

| Output Voltage                | V <sub>CE(SUS)</sub> | For inductive load applications | 35                           | V     |

| Continuous Output Current     | I <sub>OUT</sub>     | Each output                     | 500                          | mA    |

| Operation Ambient Temperature | т                    | Range E                         | -40 to 85                    | °C    |

| Operating Ambient Temperature | T <sub>A</sub>       | Range S                         | -20 to 85                    | °C    |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                                 | 150                          | °C    |

| Storage Temperature           | T <sub>stg</sub>     |                                 | -55 to 150                   | °C    |

Caution: CMOS devices have input-static protection, but are susceptible to damage when exposed to extremely high static-electrical charges.

#### Allowable Package Power Dissipation, PD

## **ELECTRICAL CHARACTERISTICS**<sup>1</sup> Unless otherwise noted: $T_A = 25$ °C, $V_{EE} = 0$ V, logic supply operating voltage $V_{DD} = 3.0$ to 5.5 V

|                                      |                        |                                                       | V <sub>dd</sub> = 3.3 V |      | V <sub>dd</sub> = 5 V |      |      |      |       |

|--------------------------------------|------------------------|-------------------------------------------------------|-------------------------|------|-----------------------|------|------|------|-------|

| Characteristic                       | Symbol                 | Test Conditions                                       | Min.                    | Тур. | Max.                  | Min. | Тур. | Max. | Units |

| Output Leakage Current               | I <sub>CEX</sub>       | V <sub>OUT</sub> = 50 V                               | _                       | _    | 10                    | -    | -    | 10   | μΑ    |

| Output Sustaining Voltage            | V <sub>CE(SUS)</sub>   | I <sub>OUT</sub> = 350 mA, L = 3 mH                   | 35                      | _    | -                     | 35   | _    | -    | V     |

| Oallantar Freitter Oatswelfer        | V <sub>CE(SAT)</sub>   | I <sub>OUT</sub> = 100 mA                             | -                       | _    | 1.1                   | -    | _    | 1.1  | V     |

| Collector–Emitter Saturation Voltage |                        | I <sub>OUT</sub> = 200 mA                             | _                       | _    | 1.3                   | _    | _    | 1.3  | V     |

| Voltage                              |                        | I <sub>OUT</sub> = 350 mA                             | _                       | _    | 1.6                   | -    | _    | 1.6  | V     |

| Input Voltage                        | V <sub>IN(1)</sub>     |                                                       | 2.2                     | _    | -                     | 3.3  | _    | -    | V     |

| Imput voltage                        | V <sub>IN(0)</sub>     |                                                       | _                       | _    | 1.1                   | _    | _    | 1.7  | V     |

| Input Resistance                     | R <sub>IN</sub>        |                                                       | 50                      | _    | -                     | 50   | _    | -    | kΩ    |

| Serial Data Output Voltage           | V <sub>OUT(1)</sub>    | I <sub>OUT</sub> = -200 μA                            | 2.8                     | 3.05 | -                     | 4.5  | 4.75 | -    | V     |

| Serial Data Output Voltage           | V <sub>OUT(0)</sub>    | I <sub>OUT</sub> = 200 μA                             | _                       | 0.15 | 0.3                   | _    | 0.15 | 0.3  | V     |

| Maximum Clock Frequency <sup>2</sup> | f <sub>c</sub>         |                                                       | 10                      | _    | _                     | 10   | _    | -    | MHz   |

|                                      | I <sub>DD(1)</sub>     | One output on, OE = L, ST = H                         | -                       | _    | 2.0                   | -    | _    | 2.0  | mA    |

| Logic Supply Current                 | I <sub>DD(0)</sub>     | All outputs off, OE = H, ST = H,<br>P1 through P8 = L | -                       | _    | 100                   | _    | _    | 100  | μΑ    |

| Clamp Diode Leakage Current          | I <sub>r</sub>         | V <sub>r</sub> = 50 V                                 | -                       | _    | 50                    | -    | _    | 50   | μA    |

| Clamp Diode Forward Voltage          | V <sub>f</sub>         | I <sub>f</sub> = 350 mA                               | _                       | _    | 2                     | -    | _    | 2    | V     |

| Output Enable-to-Output Delay        | t <sub>dis(BQ)</sub>   | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | -                       | _    | 1.0                   | -    | _    | 1.0  | μs    |

| Output Enable-to-Output Delay        | t <sub>en(BQ)</sub>    | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | _                       | _    | 1.0                   | -    | _    | 1.0  | μs    |

| Strobe-to-Output Delay               | t <sub>p(STH-QL)</sub> | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | -                       | _    | 1.0                   | -    | _    | 1.0  | μs    |

| Strobe-to-Output Delay               | t <sub>p(STH-QH)</sub> | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | _                       | _    | 1.0                   | _    | _    | 1.0  | μs    |

| Output Fall Time                     | t <sub>f</sub>         | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | -                       | _    | 1.0                   | _    | _    | 1.0  | μs    |

| Output Rise Time                     | t <sub>r</sub>         | V <sub>CC</sub> = 50 V, R1 = 500 Ω, C1≤30 pF          | -                       | _    | 1.0                   | _    | _    | 1.0  | μs    |

| Clock-to-Serial Data Out Delay       | t <sub>p(CH-SQX)</sub> | I <sub>OUT</sub> = ±200 μA                            | -                       | 50   | -                     | _    | 50   | -    | ns    |

<sup>&</sup>lt;sup>1</sup>Positive (negative) current is defined as conventional current going into (coming out of) the specified device pin.

#### Truth Table

| Serial |       | Shift Register Contents                                     | Serial         |        | Latch Contents                                              | Output | Output Contents                                             |

|--------|-------|-------------------------------------------------------------|----------------|--------|-------------------------------------------------------------|--------|-------------------------------------------------------------|

| Data   | Clock |                                                             | Data           | Strobe |                                                             | Enable |                                                             |

| Input  | Input | l <sub>1</sub> l <sub>2</sub> l <sub>3</sub> l <sub>8</sub> | Output         | Input  | l <sub>1</sub> l <sub>2</sub> l <sub>3</sub> l <sub>8</sub> | Input  | l <sub>1</sub> l <sub>2</sub> l <sub>3</sub> l <sub>8</sub> |

| Н      | Т     | H R <sub>1</sub> R <sub>2</sub> R <sub>7</sub>              | R <sub>7</sub> |        |                                                             |        |                                                             |

| L      | 7     | L R <sub>1</sub> R <sub>2</sub> R <sub>7</sub>              | R <sub>7</sub> |        |                                                             |        |                                                             |

| Х      | l     | R <sub>1</sub> R <sub>2</sub> R <sub>3</sub> R <sub>8</sub> | R <sub>8</sub> |        |                                                             |        |                                                             |

|        |       | X X X X                                                     | Х              | L      | R <sub>1</sub> R <sub>2</sub> R <sub>3</sub> R <sub>8</sub> |        |                                                             |

|        |       | P <sub>1</sub> P <sub>2</sub> P <sub>3</sub> P <sub>8</sub> | P <sub>8</sub> | Н      | P <sub>1</sub> P <sub>2</sub> P <sub>3</sub> P <sub>8</sub> | L      | P <sub>1</sub> P <sub>2</sub> P <sub>3</sub> P <sub>8</sub> |

|        |       |                                                             |                |        | X X X X                                                     | Н      | ннн н                                                       |

L = Low Logic Level H = High Logic Level P = Present State R = Previous State

X = Irrelevant

<sup>&</sup>lt;sup>2</sup>Operation at a clock frequency greater than the specified minimum value is possible but not warranteed.

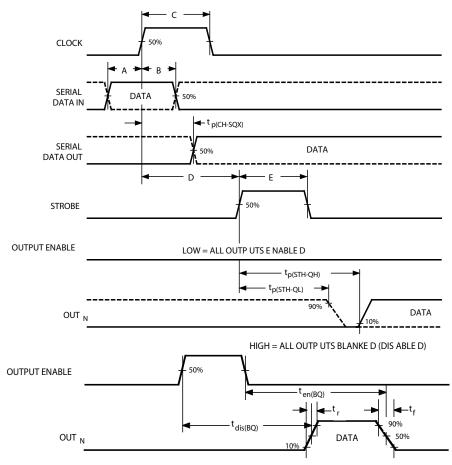

#### Timing Requirements and Specifications (Logic Levels are V<sub>DD</sub> and Ground)

| Key | Description                                            | Symbol              | Time (ns) |

|-----|--------------------------------------------------------|---------------------|-----------|

| Α   | Data Active Time Before Clock Pulse (Data Set-Up Time) | t <sub>su(D)</sub>  | 25        |

| В   | Data Active Time After Clock Pulse (Data Hold Time)    | t <sub>h(D)</sub>   | 25        |

| С   | Clock Pulse Width                                      | t <sub>w(CH)</sub>  | 50        |

| D   | Time Between Clock Activation and Strobe               | t <sub>su(C)</sub>  | 100       |

| Е   | Strobe Pulse Width                                     | t <sub>w(STH)</sub> | 50        |

NOTE: Timing is representative of a 10 MHz clock. Higher speeds may be attainable; operation at high temperatures will reduce the specified maximum clock frequency.

Powering-on with the inputs in the low state ensures that the registers and latches power-on in the low state (POR).

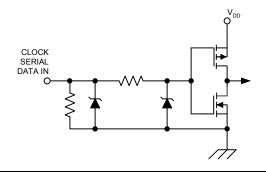

Serial Data present at the input is transferred to the shift register on the logical 0 to logical 1 transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUT-PUT. The serial data must appear at the input prior to the rising edge of the CLOCK input waveform.

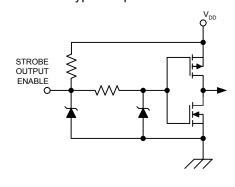

Information present at any register is transferred to the respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be high during serial data entry.

When the OUTPUT ENABLE input is high, all of the output buffers are disabled (OFF). The information stored in the latches or shift register is not affected by the OUTPUT ENABLE input. With the OUTPUT ENABLE input low, the outputs are controlled by the state of their respective latches.

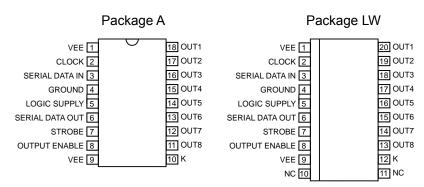

#### Pin-out Diagrams

(NC pins, 10 and 11, not present on discontinued 18-pin LW package)

#### Terminal List Table

| Name            | Description                                     | Number    |            |  |  |

|-----------------|-------------------------------------------------|-----------|------------|--|--|

| Name            | Description                                     | Package A | Package LW |  |  |

| VEE             | Power Ground to substrate                       | 1, 9      | 1, 9       |  |  |

| CLOCK           | Clock                                           | 2         | 2          |  |  |

| SERIAL DATA IN  | Serial Data In                                  | 3         | 3          |  |  |

| GROUND          | Logic Ground                                    | 4         | 4          |  |  |

| VDD             | Logic Supply                                    | 5         | 5          |  |  |

| SERIAL DATA OUT | Serial Data Out, for cascading devices          | 6         | 6          |  |  |

| STROBE          | Strobe                                          | 7         | 7          |  |  |

| OUTPUT ENABLE   | Output Enable (active low)                      | 8         | 8          |  |  |

| К               | Common to +V <sub>L</sub> , for inductive loads | 10        | 12         |  |  |

| NC              | Not internally connected                        | _         | 10, 11     |  |  |

| OUT8            | Sink Output 8                                   | 11        | 13         |  |  |

| OUT7            | Sink Output 7                                   | 12        | 14         |  |  |

| OUT6            | Sink Output 6                                   | 13        | 15         |  |  |

| OUT5            | Sink Output 5                                   | 14        | 16         |  |  |

| OUT4            | Sink Output 4                                   | 15        | 17         |  |  |

| OUT3            | Sink Output 3                                   | 16        | 18         |  |  |

| OUT2            | Sink Output 2                                   | 17        | 19         |  |  |

| OUT1            | Sink Output 1                                   | 18        | 20         |  |  |

## Typical Application Relay/solenoid driver using split supply

Pins 10 and 11 can float; other pins match discontinued 18-pin SOIC: 1 to 9 same, pins 12 to 20 match pins 10 to 18

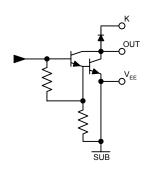

**Typical Input Circuits**

Typical Output Driver

#### Package A, 18-Pin DIP

### Package LW, 20-Pin SOICW

### A6841

### DABiC-5 8-Bit Serial Input Latched Sink Drivers

Copyright ©2004-2008 Allegro MicroSystems, Inc.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

> For the latest version of this document, visit our website: www.allegromicro.com

8