# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

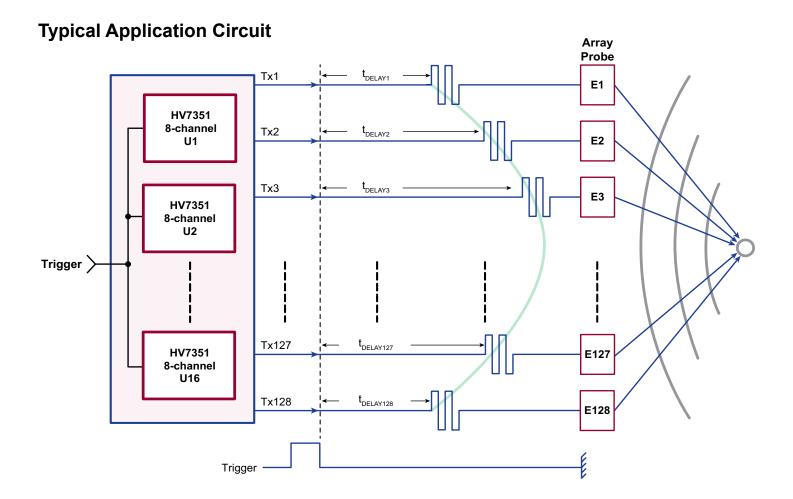

# Eight Channel Programmable High Voltage Ultrasound Transmit Beamformer

### **Features**

- ► Eight channels with return to zero

- Up to ±70V output voltage

- ±3.0A output current

- Store up to four different patterns

- ▶ Independent programmable delays

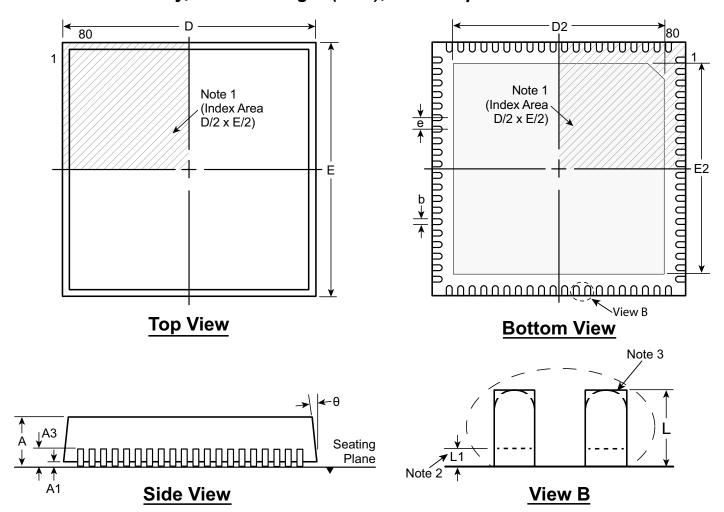

- Single 11x11 QFN-80 package

### **Application**

- Medical ultrasound imaging

- NDT, non-destructive testing

- Arbitrary pattern generator

- High speed PIN diode driver

### **General Description**

The Supertex HV7351 is an 8-channel programmable high voltage ultrasound transmit beamformer. Each channel is capable of swinging up to ±70V with an active discharge back to 0V. The outputs can source and sink more than 3.0A to achieve fast output rise and fall times. The active discharge is also capable of sourcing and sinking 3.0A for a fast return to ground. The topology of the HV7351 will significantly reduce the number of I/O logic control lines needed.

Each pulser has four associated 64-bit shift registers for storing pre-determined transmit patterns and a 10-bit delay counter for controlling the transmit time. One of four arbitrary patterns can be transmitted with adjustable delay, depending on the data loaded into these shift registers and the delay counter. The delay counter can be clocked up to 200MHz, allowing incremental delays down to 5ns.

## **Ordering Information**

| Part Number | Package Option      | Packing  |

|-------------|---------------------|----------|

| HV7351K6-G  | 80-Lead QFN (11x11) | 176/Tray |

<sup>-</sup>G denotes a lead (Pb)-free / RoHS compliant package

## **Absolute Maximum Ratings**

| Parameter                                                   | Value                       |

|-------------------------------------------------------------|-----------------------------|

| V <sub>LL</sub> , Positive logic supply                     | -0.5V to 5.5V               |

| DV <sub>DD</sub> , Positive logic supply voltage            | -0.5V to 5.5V               |

| PV <sub>DD</sub> , Positive gate drive supply voltage       | -0.5V to 5.5V               |

| AV <sub>DD</sub> , Positive analog supply voltage           | -0.5V to 5.5V               |

| PV <sub>SS</sub> , Negative gate drive supply voltage       | +0.5V to -5.5V              |

| V <sub>pp</sub> , High voltage positive supply voltage      | -0.5V to +80V               |

| $V_{_{\mathrm{NN}}}$ , High voltage negative supply voltage | +0.5V to -80V               |

| $(V_{PP} - V_{NN})$ , Differential high voltage supply      | +160V                       |

| V <sub>PF</sub> , Positive floating supply voltage          | $V_{PP}$ - 6.0V to $V_{PP}$ |

| V <sub>NF</sub> , Negative floating supply voltage          | $V_{NN}$ to $V_{NN}$ +6.0V  |

| $V_{\rm RP}$ , Positive supply for $V_{\rm NF}$ regulator   | 0V to 15V                   |

| $V_{\rm RN}$ , Negative supply for $V_{\rm PF}$ regulator   | 0V to -15V                  |

| Operating temperature                                       | -40°C to +125°C             |

| Storage temperature                                         | -65°C to +150°C             |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

## **Pin Configuration**

80-Lead QFN (top view)

## **Package Marking**

Package may or may not include the following marks: Si or 🚯

## **Typical Thermal Resistance**

| Package     | $oldsymbol{	heta}_{j_{oldsymbol{a}}}$ |

|-------------|---------------------------------------|

| 80-Lead QFN | 14°C/W                                |

## **Operating Supply Voltages**

(T<sub>1</sub> = 25°C unless otherwise specified)

| Sym              | Parameter                                      | Min   | Тур   | Max   | Units | Conditions |

|------------------|------------------------------------------------|-------|-------|-------|-------|------------|

| V <sub>PP</sub>  | Positive high voltage supply                   | 3.0   | -     | 70    | V     |            |

| V <sub>NN</sub>  | Negative high voltage supply                   | -70   | -     | -3.0  | V     |            |

| V <sub>LL</sub>  | Logic interface voltage                        | 2.85  | 3.30  | 3.6   | V     |            |

| AV <sub>DD</sub> | Low voltage positive analog supply voltage     | 4.75  | 5.00  | 5.25  | V     |            |

| DV <sub>DD</sub> | Low voltage positive digital supply voltage    | 4.75  | 5.00  | 5.25  | V     |            |

| PV <sub>DD</sub> | Low voltage positive gate drive supply voltage | 4.75  | 5.00  | 5.25  | V     |            |

| PV <sub>SS</sub> | Low voltage negative gate drive supply voltage | -5.25 | -5.00 | -4.75 | V     |            |

# Operating Supply Voltages (cont.) $(T_j = 25^{\circ}\text{C unless otherwise specified})$

| Sym              | Parameter                                      | Min                | Тур                | Max                | Units | Conditions                                  |

|------------------|------------------------------------------------|--------------------|--------------------|--------------------|-------|---------------------------------------------|

| V <sub>RP</sub>  | Low voltage positive supply for VNF regulator  | 4.75               | -                  | 12                 | V     |                                             |

| V <sub>RN</sub>  | Low voltage negative supply for VPF regulator  | -12                | -                  | -4.75              | V     |                                             |

| TCK              | Reference voltage logic trip point for TCK pin | 0.4V <sub>LL</sub> | 0.5V <sub>LL</sub> | 0.6V <sub>LL</sub> | V     |                                             |

| I <sub>TCK</sub> | TCK input current                              | -                  | -                  | ±10                | μA    | $V_{\overline{TCK}} = 0 \text{ to } V_{LL}$ |

**Regulator Outputs** (Operating conditions unless otherwise specified,  $V_{LL} = 3.3V$ ,  $AV_{DD} = DV_{DD} = PV_{DD} = V_{RP} = 5.0V$ ,  $PV_{SS} = V_{RN} = -5.0V$ ,  $V_{PP} = +70V$ ,  $V_{NN} = -70V$ ,  $T_{J} = 25^{\circ}$ C)

| S | ym              | Parameter                            | Min                   | Тур                   | Max                   | Units | Conditions                                                 |

|---|-----------------|--------------------------------------|-----------------------|-----------------------|-----------------------|-------|------------------------------------------------------------|

| \ | / <sub>PF</sub> | Positive floating gate drive voltage | V <sub>PP</sub> -5.25 | V <sub>PP</sub> -5.00 | V <sub>PP</sub> -4.00 | V     | 4.0 $\mu$ F ceramic capacitor across $V_{PF}$ and $V_{PP}$ |

| V | / <sub>NF</sub> | Negative floating gate drive voltage | V <sub>NN</sub> +4.00 | V <sub>NN</sub> +5.00 | V <sub>NN</sub> +5.25 | V     | 4.0 $\mu$ F ceramic capacitor across $V_{NF}$ and $V_{NN}$ |

## **Electrical Characteristics**

(Operating conditions unless otherwise specified  $V = 3.3V \text{ AV} = DV = PV = V = 5.0V \text{ PV} = V = -5.0V \text{ V} = +70V \text{ V} = -70V \text{ T} = 25^{\circ}\text{C}$ )

|                     | g conditions unless otherwise specified, V |      |       |     | 100 7.11 | 1                                      |

|---------------------|--------------------------------------------|------|-------|-----|----------|----------------------------------------|

| Sym                 | Parameter                                  | Min  | Тур   | Max | Units    | Conditions                             |

| I <sub>VLLQ</sub>   | V <sub>LL</sub> quiescent current          | -    | 384   | 500 | μA       | EN = Low, all inputs are static        |

| I <sub>AVDDQ</sub>  | AV <sub>DD</sub> quiescent current         | -    | 12    | 30  |          |                                        |

| I <sub>DVDDQ</sub>  | DV <sub>DD</sub> quiescent current         | -    | 12    | 30  | μA       | EN = Low, all inputs are static        |

| I <sub>PVDDQ</sub>  | PV <sub>DD</sub> quiescent current         | -    | 70    | 100 |          |                                        |

| I <sub>VRPQ</sub>   | V <sub>RP</sub> quiescent current          | -    | 0.3   | 6.0 |          | [N = Low all inputs are static         |

| I <sub>VRNQ</sub>   | V <sub>RN</sub> quiescent current          | -    | -0.01 | 6.0 | μA       | EN = Low, all inputs are static        |

| I <sub>PVSSQ</sub>  | PV <sub>ss</sub> quiescent current         | -85  | -45   | -   | μA       | EN = Low, all inputs are static        |

| l <sub>VPPQ</sub>   | V <sub>PP</sub> quiescent current          | -    | 2.6   | 6.0 |          | EN = Low, all inputs are static        |

| I <sub>VNNQ</sub>   | V <sub>NN</sub> quiescent current          | -    | -1.6  | 6.0 | μA       |                                        |

| I <sub>VLLEN</sub>  | V <sub>LL</sub> enabled quiescent current  | -    | 390   | 500 | μA       | EN = High, all inputs are static       |

| AVDDEN              | AV <sub>DD</sub> enabled quiescent current | -    | 600   | 800 |          |                                        |

| I <sub>DVDDEN</sub> | DV <sub>DD</sub> enabled quiescent current | -    | 22    | 55  | μA       | EN = High, all inputs are static       |

| I <sub>PVDDEN</sub> | PV <sub>DD</sub> enabled quiescent current | -    | 44    | 100 | μA       | EN = High, all inputs are static       |

| I <sub>VRPEN</sub>  | V <sub>RP</sub> enabled quiescent current  | -    | 450   | 650 |          | EN Illiah allianata ana atatia         |

| I <sub>VRNEN</sub>  | V <sub>RN</sub> enabled quiescent current  | -650 | -350  | -   | μA       | EN = High, all inputs are static       |

| I <sub>PVSSEN</sub> | PV <sub>ss</sub> enabled quiescent current | -100 | -44   | -   | μA       | EN = High, all inputs are static       |

| I <sub>VPPEN</sub>  | V <sub>PP</sub> enabled quiescent current  | -    | 370   | 620 |          | ENI - I link all investo and at - fire |

| I <sub>VNNEN</sub>  | V <sub>NN</sub> enabled quiescent current  | -620 | -420  | -   | μA       | EN = High, all inputs are static       |

Electrical Characteristics (cont.) (Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $PV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $T_{J}$  = 25°C)

| Sym                 | Parameter                              | Min | Тур | Max | Units | Conditions                                                                      |

|---------------------|----------------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------|

| I <sub>VLLCW</sub>  | V <sub>LL</sub> current at TCK = 80MHz | -   | 500 | -   | μA    | \                                                                               |

| I <sub>DVDDCW</sub> | DV <sub>DD</sub> current at CW = 5MHz  | -   | 25  | -   | mA    | $V_{PP} = +5.0V, V_{NN} = -5.0V, EN = High, CW = High, 80MHz on TCK, 0.5V_{11}$ |

| I <sub>VPPCW</sub>  | V <sub>PP</sub> current at CW = 5MHz   | -   | 141 | -   | mA    | on TCK, all 8 channels active at                                                |

| I <sub>VNNCW</sub>  | V <sub>NN</sub> current at CW = 5MHz   | -   | 98  | -   | mA    | 5.0MHz, No load                                                                 |

**AC Electrical Characteristics**(Operating conditions unless otherwise specified,  $V_{LV} = 3.3V$ ,  $AV_{DD} = DV_{DD} = PV_{DD} = V_{RD} = 5.0V$ ,  $PV_{SD} = V_{RD} = -5.0V$ ,  $V_{RD} = +70V$ ,  $V_{RD} = -70V$ ,  $T_{LP} = 25^{\circ}$ C)

| Sym                  | Parameter                               | Min                     | Тур | Max | Units  | Conditions                                      |

|----------------------|-----------------------------------------|-------------------------|-----|-----|--------|-------------------------------------------------|

| f <sub>TCK</sub>     | Transmit clock frequency                | 0                       | -   | 200 | MHz    |                                                 |

| f.                   | Serial clock frequency                  | 0                       | -   | 80  | MHz    | No daisy chain                                  |

| f <sub>sck</sub>     | Serial clock frequency                  | 0                       | -   | 70  | IVITIZ | Daisy chained                                   |

| t <sub>SU-DIN</sub>  | Set-up time data in to SCK              | 2.0                     | 1.0 | -   | ns     |                                                 |

| t <sub>H-DIN</sub>   | Hold time SCK to data in                | 2.0                     | 1.0 | -   | ns     |                                                 |

| t <sub>SU-CS1</sub>  | Set-up time CS1 low to SCK              | 2.0                     | -   | -   | ns     |                                                 |

| t <sub>SU-CS2</sub>  | Set-up time CS2 low to SCK              | 2.0                     | -   | -   | ns     |                                                 |

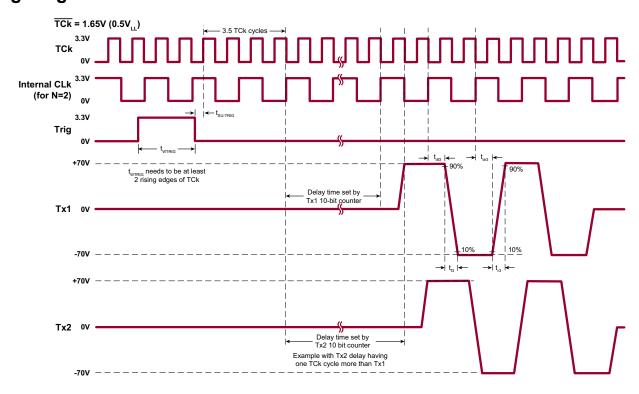

| t <sub>SU-TRIG</sub> | Set-up time TRIG low to TCK             | 2.0                     | -   | -   | ns     |                                                 |

| t <sub>w-TRIG</sub>  | TRIG pulse width                        | 2TCK                    | -   | -   | -      |                                                 |

|                      | SCK to data out low to high             | 3.0                     | 9.0 | 12  |        | For D <sub>OUT</sub> 1                          |

| t <sub>LHDO</sub>    | delay time                              | 3.0                     | 9.0 | 10  | ns     | For D <sub>OUT</sub> 2                          |

|                      | SCK to data out high to low             | 3.0                     | 9.0 | 12  |        | For D <sub>OUT</sub> 1                          |

| HLDO                 | delay time                              | 3.0                     | 9.0 | 10  | ns     | For D <sub>OUT</sub> 2                          |

| t <sub>wa1A0</sub>   | A1A0 pulse width                        | t <sub>W-TRIG</sub> +40 | -   | -   |        |                                                 |

| t <sub>SUA1A0</sub>  | Set-up time A1A0 to TRIG rising edge    | -                       | 20  | -   | ns     |                                                 |

| t <sub>HA1A0</sub>   | Hold time A1A0 to TRIG falling edge     | -                       | 20  | -   |        |                                                 |

| t <sub>EN-ON</sub>   | Device enable time                      | ı                       | 1.0 | -   | ms     | 1.0 $\mu$ F capacitor on every VPF and VNF pin. |

| t <sub>EN-OFF</sub>  | Device disable time                     | -                       | -   | 100 | ns     |                                                 |

| t <sub>r1</sub>      | Output rise time from 0V to +HV         | -                       | 9.0 | 13  |        |                                                 |

| t <sub>f1</sub>      | Output fall time from 0V to -HV         | -                       | 9.0 | 13  |        |                                                 |

| t <sub>r2</sub>      | Damping output rise time from -HV to 0V | -                       | 9.0 | 13  |        | Lood = 220nF//2 5kO                             |

| t <sub>f2</sub>      | Damping output fall time from +HV to 0V | -                       | 9.0 | 13  | ns     | Load = 330pF//2.5kΩ                             |

| t <sub>r3</sub>      | Output rise time from -HV to +HV        | -                       | 17  | 23  |        |                                                 |

| t <sub>f3</sub>      | Output fall time from +HV to -HV        | -                       | 17  | 23  |        |                                                 |

| t <sub>rcw</sub>     | CW output rise time                     | -                       | 9.0 | 16  |        | $V_{PP} = +5.0V, V_{NN} = -5.0V,$               |

| t <sub>fcw</sub>     | CW output fall time                     | -                       | 9.0 | 16  | ns     | Load = $330pF//2.5k\Omega$                      |

### **AC Electrical Characteristics** (cont.)

(Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $V_{J}$  = 25°C)

| Sym                   | Parameter                                         | Min    | Тур    | Max    | Units | Conditions                                             |

|-----------------------|---------------------------------------------------|--------|--------|--------|-------|--------------------------------------------------------|

| t <sub>dr1</sub>      | Output propagation delay rise time 1              | 10.85  | 13.35  | 15.85  |       |                                                        |

| t <sub>df1</sub>      | Output propagation delay fall time 1              | 11.35  | 13.85  | 16.35  |       |                                                        |

| t <sub>dr2</sub>      | Output propagation delay rise time 2              | 11.25  | 13.75  | 16.25  | ne    | No Load.                                               |

| t <sub>df2</sub>      | Output propagation delay fall time 2              | 11.75  | 14.25  | 16.75  | ns    | NO LOAU.                                               |

| t <sub>dr3</sub>      | Output propagation delay rise time 3              | 11.35  | 13.85  | 16.35  |       |                                                        |

| t <sub>df3</sub>      | Output propagation delay fall time 3              | 11.45  | 13.95  | 16.45  |       |                                                        |

| t <sub>dcwlh</sub>    | CW output propagation delay time from low to high | 10.45  | 12.95  | 15.45  | ns    | $V_{PP} = +5.0V, V_{NN} = -5.0V,$                      |

| t <sub>dcwhl</sub>    | CW output propagation delay time from high to low | 10.35  | 12.85  | 15.35  | 115   | No Load                                                |

| $\Delta t_{ m dcwhl}$ | Delay time matching                               | -      | ±0.7   | -      | ns    | P to N, channel-to-channel matching                    |

| t <sub>JCW</sub>      | Delay jitter on rise or fall                      | -      | 13     | -      | ps    | $V_{pp}$ = +5.0V, $V_{NN}$ = -5.0V, Load = 50 $\Omega$ |

| LAT                   | Latency                                           | 3.5TCK | 3.5TCK | 3.5TCK | -     |                                                        |

## Output P-channel MOSFET to $V_{pp}$ , CW = 0

| I <sub>OUT</sub> | Output saturation current | 2.2 | 3.2 | - | Α  |                                                      |

|------------------|---------------------------|-----|-----|---|----|------------------------------------------------------|

| R <sub>on</sub>  | Output ON-resistance      | -   | 4.2 | - | Ω  | I <sub>OUT</sub> = 100mA                             |

| Coss             | Output capacitance        | -   | 62  | ı | pF | V <sub>PP</sub> - V <sub>OUT</sub> = 25V, f = 1.0MHz |

## Output N-channel MOSFET to $V_{NN}$ , CW = 0

| I <sub>OUT</sub> | Output saturation current | - | -3.2 | -2.2 | Α  |                                       |

|------------------|---------------------------|---|------|------|----|---------------------------------------|

| $R_{on}$         | Output ON-resistance      | - | 2.4  | -    | Ω  | I <sub>OUT</sub> = -100mA             |

| C <sub>oss</sub> | Output capacitance        | - | 50   | -    | pF | $V_{NN} - V_{OUT} = -25V, f = 1.0MHz$ |

## Output P-channel MOSFET to $V_{pp}$ , CW = 1

| I <sub>OUT</sub> | Output saturation current | 1.2 | 1.5 | - | Α  |                                                      |

|------------------|---------------------------|-----|-----|---|----|------------------------------------------------------|

| R <sub>on</sub>  | Output ON-resistance      | -   | 8.0 | - | Ω  | I <sub>OUT</sub> = 100mA                             |

| C <sub>oss</sub> | Output capacitance        | -   | 62  | - | pF | V <sub>PP</sub> - V <sub>OUT</sub> = 25V, f = 1.0MHz |

## Output N-channel MOSFET to $V_{NN}$ , CW = 1

| I <sub>OUT</sub> | Output saturation current | - | -1.5 | -1.2 | Α  |                                                       |

|------------------|---------------------------|---|------|------|----|-------------------------------------------------------|

| R <sub>on</sub>  | Output ON-resistance      | - | 6.6  | -    | Ω  | I <sub>OUT</sub> = -100mA                             |

| C <sub>oss</sub> | Output capacitance        | - | 50   | -    | pF | V <sub>NN</sub> - V <sub>OUT</sub> = -25V, f = 1.0MHz |

AC Electrical Characteristics (cont.) (Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $PV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $V_{J}$  = 25°C)

| Sym              | Parameter                        | Min     | Тур  | Max  | Units | Conditions                                            |  |  |  |  |  |  |

|------------------|----------------------------------|---------|------|------|-------|-------------------------------------------------------|--|--|--|--|--|--|

| Damp             | Damping P-channel MOSFET to PGND |         |      |      |       |                                                       |  |  |  |  |  |  |

| l <sub>out</sub> | Output saturation current        | 2.2     | 3.2  | -    | Α     |                                                       |  |  |  |  |  |  |

| R <sub>on</sub>  | Output ON-resistance             | -       | 4.0  | -    | Ω     | I <sub>OUT</sub> = 100mA                              |  |  |  |  |  |  |

| C <sub>oss</sub> | Output capacitance               | -       | 62   | -    | pF    | V <sub>PP</sub> - V <sub>OUT</sub> = 25V, f = 1.0MHz  |  |  |  |  |  |  |

| Damp             | oing N-channel MOSFE             | T to PG | ND   |      |       |                                                       |  |  |  |  |  |  |

| I <sub>OUT</sub> | Output saturation current        | -       | -3.2 | -2.2 | Α     |                                                       |  |  |  |  |  |  |

| R <sub>on</sub>  | Output ON-resistance             | -       | 2.3  | -    | Ω     | I <sub>OUT</sub> = -100mA                             |  |  |  |  |  |  |

| C <sub>oss</sub> | Output capacitance               | -       | 50   | -    | pF    | V <sub>NN</sub> - V <sub>OUT</sub> = -25V, f = 1.0MHz |  |  |  |  |  |  |

### **Logic Inputs**

| = 0.5V <sub>LL</sub> |

|----------------------|

|                      |

| : 0.5\/              |

| U.UV <sub>LL</sub>   |

| TCK                  |

| TCK                  |

|                      |

|                      |

|                      |

|                      |

|                      |

|                      |

## **Logic Truth Table**

|                                                     |    |    | Input             | S   |     |     | (          | Output     | 5   |                                                                                                                     |

|-----------------------------------------------------|----|----|-------------------|-----|-----|-----|------------|------------|-----|---------------------------------------------------------------------------------------------------------------------|

| Mode                                                | EN | cw | 10-bit<br>Counter | INV | NIN | PIN | N-ch       | P-ch       | RTZ | Comments                                                                                                            |

|                                                     | 1  | 0  | Х                 | х   | 0   | 0   | OFF        | OFF        | ON  | RTZ (return-to-zero) is activated when NIN and PIN are both low. Output is pulled to ground through a series diode. |

| Non-CW mode. Outputs not inverted. Outputs are con- | 1  | 0  | х                 | 0   | 0   | 1   | OFF        | ON         | OFF | Not inverted. Logic 1 in the P-channel register turns on the output P-channel MOSFET.                               |

| trolled by data in the shift registers              | 1  | 0  | X                 | 0   | 1   | 0   | ON         | OFF        | OFF | Not inverted. Logic 1 in the N-channel register turns on the output N-channel MOSFET.                               |

|                                                     | 1  | 0  | Х                 | x   | 1   | 1   | OFF        | OFF        | OFF | Avoids cross over current. A logic 1 in both P- and N-channel registers will put the output in a Hi-Z state.        |

| Non-CW mode. Outputs are inverted. Outputs are con- | 1  | 0  | x                 | 1   | 0   | 1   | ON         | OFF        | OFF | Inverted, for harmonic imaging                                                                                      |

| trolled by data in the shift registers              | 1  | 0  | X                 | 1   | 1   | 0   | OFF        | ON         | OFF | Inverted, for harmonic imaging                                                                                      |

| CW mode.                                            | 1  | X  | All 1             | Х   | Х   | Х   | OFF        | OFF        | OFF | Off channels are the ones with all 1's in their respective 10-bit counters. Output follows the f <sub>cw</sub>      |

| Output follows fcw                                  | 1  | 1  | Not all 1         | X   | X   | Х   | OFF/<br>ON | ON/<br>OFF | OFF | signal. Shift registers for NIN and PIN should remain static to save power.                                         |

| Device Disabled                                     | 0  | Х  | Х                 | Х   | Х   | Х   | OFF        | OFF        | OFF | Hi-Z state                                                                                                          |

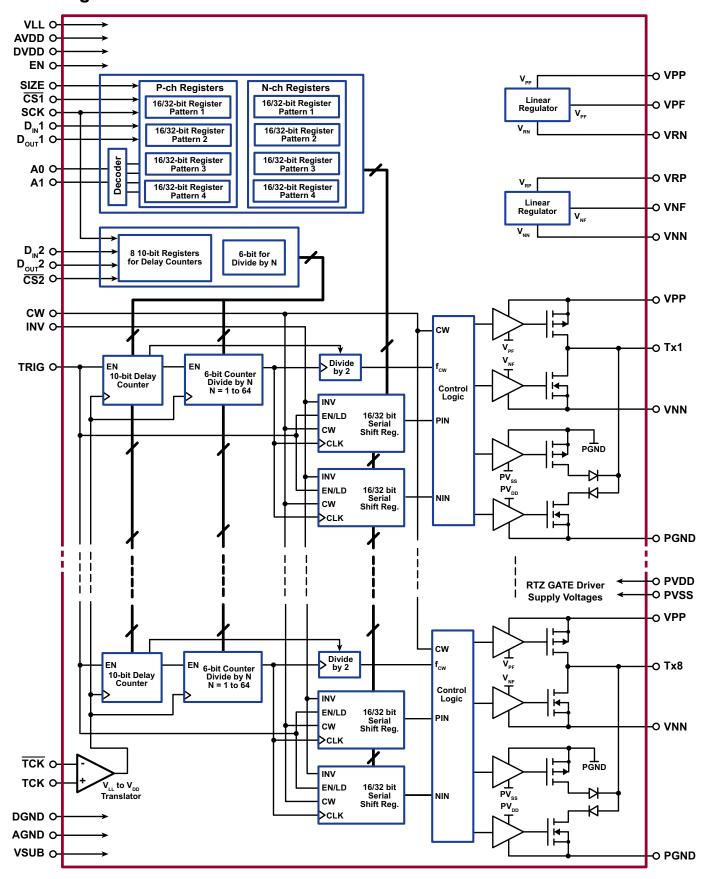

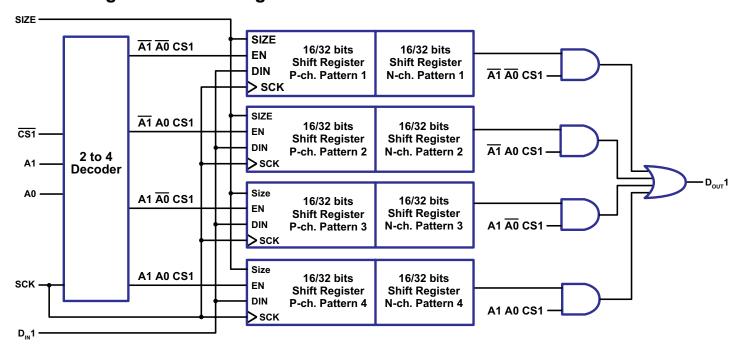

## **Block Diagram**

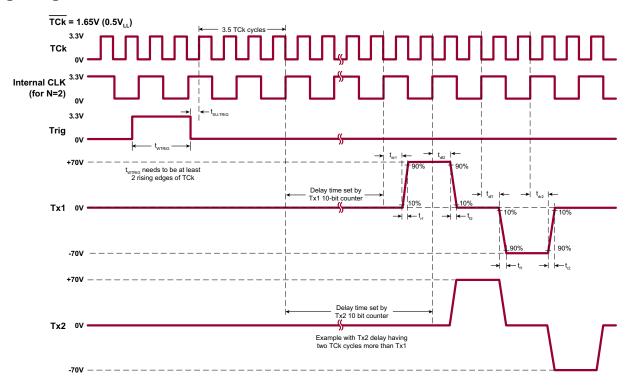

## **Timing Diagram 1**

## **Timing Diagram 2**

### **Pattern Register Circuit Diagram**

### Loading Data into the Four 16/32 bit Pattern Registers

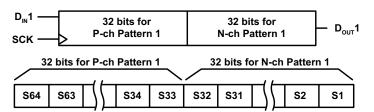

A detailed circuit diagram of the pattern registers is shown above. There are 4 programmable patterns that can be stored. One of four patterns can be selected via the two input logic decoder pins, A1 and A0. Data can be loaded on the selected pattern. Each pattern can be either 16 or 32 bits wide. The SIZE pin determines whether they are 16 or 32 bits wide. SIZE = H will set the pattern to be 32 bits wide while SIZE = L will set it to 16 bits wide.  $D_{IN}$ 1 is the input data for the register. When  $\overline{CS1}$  is high, data will not be shifted in. Data is shifted in only when  $\overline{CS1}$  is low.

With SIZE = H, the circuit is effectively a 64-bit serial shift register. The data first enters into the P-channel register and continues to be shifted though to the N-channel register. Data is clocked in during the rising edge of the clock. There is no activity during the falling edge of the clock. The data,  $D_{IN}1$ , enters from the P-channel register and exits from the N-channel register from  $D_{OUT}1$ .

For size = High, 32 bits wide (size = Low, 16-bits wide)

A1 = A0 = Low, Pattern 1 selected

CS1 = Low, data can be shifted in

64-bit serial shift register: 32 bits for the P-channel and

32 bits for the N-channel

Data is shifted in during the rising edge of the clock. S1 is the first bit shifted in, entering the P-channel register. After 64 clock cycles, S1 will be located in the N-channel register as shown below. It will also be clocked out to D<sub>OUT</sub>1.

A 2-to-4 decoder is provided to select which of the four patterns is to be used for all of the outputs. Logic inputs A1 and A0 determine which patterns are selected per the decoder truth table shown below. Once A1 and A0 are set, a rising edge on the trigger logic input pin will automatically load the selected pattern to all of the outputs.

### **Decoder Truth Table**

| Logic Dec | Logic Decoder Input |   |  |  |  |  |  |  |

|-----------|---------------------|---|--|--|--|--|--|--|

| A1        | A1 A0               |   |  |  |  |  |  |  |

| 0         | 0                   | 1 |  |  |  |  |  |  |

| 0         | 1                   | 2 |  |  |  |  |  |  |

| 1         | 0                   | 3 |  |  |  |  |  |  |

| 1         | 1                   | 4 |  |  |  |  |  |  |

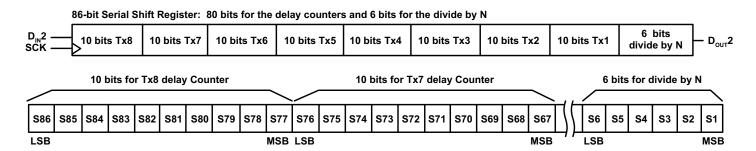

# Loading Data into the Delay Counters and the Divide-by-N Counter

Each output channel, TX, has its own programmable 10-bit delay counter. For 8 channels, 80 bits are needed. A 6-bit divide-by-N counter is also provided to program the desired TX frequency. To program all the individual delay counters and the divide-by-N counter, an 86-bit serial shift register is provided. It uses the same clock input that the pattern registers uses. DIN2 is the input data for this register. When CS2 is high, data will not be shifted in. Data is shifted in only when CS2 is low.

As shown below, the data first enters into the 10-bit register for the TX8 delay counter and continues to be shifted

though to the 6-bit register for the divide by N counter. Data is clocked in during the rising edge of the clock. There is no activity during the falling edge of the clock. The MSB bit in the 6-bit divide-by-N register is clocked out into DOUT2 for cascading multiple devices if desired.

### **10-Bit Delay Counter**

The input clock for the 10-bit delay counter is the TCK pin. The TCK pin is the only pin that is capable of high frequency, 200MHz. This helps maximum delay time resolution. The counter counts upward. Please refer to the table below.

### **Delay Counter Table**

| MSB |   |   |   |   |   |   |   |   | LSB | Delay Time      |

|-----|---|---|---|---|---|---|---|---|-----|-----------------|

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 1023 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1   | 1022 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0   | 1021 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1   | 1020 TCK cycles |

| I   | I | I | I | I | I | I | ı | I | I   |                 |

| ı   | I | I | I | I | I | I | I | I | I   | I               |

| I   | I | I | I | I | I | I | I | I | I   | I               |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0   | 3 TCK cycles    |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1   | 2 TCK cycles    |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0   | 1 TCK cycle     |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1   | No trigger      |

## 6-Bit Divide-by-N Counter

The input clock for the 6-bit divide-by-N counter is the TCK pin. It generates the clock frequency for the 16/32 bit serial shift register for the output P- and N-channel patterns. Each

clock cycle will set the TX output to be either at  $V_{PP}$ ,  $V_{NN}$ , ground, or high impedance depending on what was preprogrammed in their corresponding registers.

| MSB |   |   |   |   | LSB | Output Shift Register<br>Clock Frequency |

|-----|---|---|---|---|-----|------------------------------------------|

| 0   | 0 | 0 | 0 | 0 | 0   | f <sub>τcκ</sub> ÷ 64                    |

| 0   | 0 | 0 | 0 | 0 | 1   | f <sub>TCK</sub> ÷ 63                    |

| 0   | 0 | 0 | 0 | 1 | 0   | f <sub>TCK</sub> ÷ 62                    |

| 0   | 0 | 0 | 0 | 1 | 1   | f <sub>TCK</sub> ÷ 61                    |

| I   | I | I | I | I | I   | I                                        |

| I   | I | I | I | I | I   | l                                        |

| I   | I | I | I | I | I   | I                                        |

| 1   | 1 | 1 | 1 | 0 | 0   | f <sub>τcκ</sub> ÷4                      |

| 1   | 1 | 1 | 1 | 0 | 1   | f <sub>TCK</sub> ÷3                      |

| 1   | 1 | 1 | 1 | 1 | 0   | f <sub>TCK</sub> ÷ 2                     |

| 1   | 1 | 1 | 1 | 1 | 1   | f <sub>TCK</sub> ÷ 1                     |

## **Pin Description**

| Pin | Name  | Description                                                                                                                                                                                                                  |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AVDD  | Positive analog supply voltage (+5.0V).                                                                                                                                                                                      |

| 2   | DIN2  | Serial data in for delay counters and frequency divider.                                                                                                                                                                     |

| 3   | CS2   | Activates DIN2. Input logic high = off, input logic low = on.                                                                                                                                                                |

| 4   | SIZE  | Sets pattern width to either 16-bits or 32-bits. Logic low = 16-bits, logic high = 32-bits.                                                                                                                                  |

| 5   | INV   | Inverts the TX output waveform. See logic truth table for details.                                                                                                                                                           |

| 6   | CW    | Activates CW mode. Logic low = non-CW mode, logic high = CW mode. See logic truth table for details.                                                                                                                         |

| 7   | DOUT2 | Data out for delay counters and frequency divider.                                                                                                                                                                           |

| 8   | EN    | Enables and disables device. Logic low = off, logic high = on.                                                                                                                                                               |

| 9   | SCK   | Serial clock input for serial shift registers.                                                                                                                                                                               |

| 10  | DVDD  | Positive digital supply voltage (+5.0V).                                                                                                                                                                                     |

| 11  | DGND  | Digital ground.                                                                                                                                                                                                              |

| 12  | TRIG  | Toggles all TX outputs to transmit. Needs to be high for 2 rising edges of TCK. Delay counters will start on the rising edge of the TCK pin right after the falling edge of the TRIG signal. See timing diagram for details. |

| 13  | TCK   | Transmitter clock for the delay counters and input frequency for the divide by N. Can be CMOS, LVDS, or SSTL.                                                                                                                |

| 14  | TCK   | Logic trip point TCK. Can be set to a DC value from 0.4V <sub>LL</sub> to 0.6V <sub>LL</sub> or driven differentially with TCK.                                                                                              |

| 15  | VLL   | Logic interface supply voltage (3.0V or 3.3V).                                                                                                                                                                               |

| 16  | CS1   | Activates DIN1. Input logic high = off, input logic low = on.                                                                                                                                                                |

| 17  | DOUT1 | Data out for P-channel and N-channel pattern registers.                                                                                                                                                                      |

## Pin Description (cont.)

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin | Name | Description                                                            |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------------------------------------------------------------------------|--|--|--|--|--|--|

| Decoded to select 1 of 4 patterns to be loaded.  Decoded to select 1 of 4 patterns to be loaded.  Decoded to select 1 of 4 patterns to be loaded.  POND Serial data in for P-channel and N-channel pattern registers.  PVRN Negative supply for VPF regulator (-5.0V).  Positive gate drive supply voltage for RTZ output transistors (+5.0V).  Power ground path for RTZ output transistors (-5.0V).  Power ground path for RTZ output transistors.  Negative gate drive supply voltage for RTZ output transistors (-5.0V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  No connection.  Positive high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  Positive high voltage supply (+3.0V to +70V).  Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 3.  Positive high voltage supply (+3.0V to +70V).  Positive high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  Dendo Digital ground.  Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                     | 18  | A0   |                                                                        |  |  |  |  |  |  |

| 21 VRN Negative supply for VPF regulator (-5.0V).  22 PVDD Positive gate drive supply voltage for RTZ output transistors (+5.0V).  23 PGND 24 PGND 25 PVSS Negative gate drive supply voltage for RTZ output transistors (-5.0V).  26 VPF Linear regulator output gate drive voltage for RTZ output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  27 NC No connection.  28 VNF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF and VPP pin. There are four in total.  29 VNN Negative high voltage supply (-3.0V to -70V).  30 TX1 Transmit pulser outputs for channel 1.  31 VPP 32 VPP 33 TX2 Transmit pulser outputs for channel 2.  34 VNN Negative high voltage supply (-3.0V to -70V).  35 VNN Negative high voltage supply (-3.0V to -70V).  36 TX3 Transmit pulser outputs for channel 3.  37 VPP 38 VPP 39 TX4 Transmit pulser outputs for channel 4.  40 VNN Negative high voltage supply (+3.0V to +70V).  41 VNN Negative high voltage supply (-3.0V to -70V).  42 VNF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  44 VPP Positive high voltage supply (+3.0V to +70V).  45 VPF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  46 PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                           |     |      | Decoded to select 1 of 4 patterns to be loaded.                        |  |  |  |  |  |  |

| PVDD Positive gate drive supply voltage for RTZ output transistors (+5.0V).  PGND Power ground path for RTZ output transistors.  Power ground path for RTZ output transistors.  Power ground path for RTZ output transistors.  Power ground path for RTZ output transistors (-5.0V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  VNF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  VPP Positive high voltage supply (+3.0V to +70V).  Negative high voltage supply (-3.0V to -70V).  Negative high voltage supply (+3.0V to -70V).  Positive high voltage supply (+3.0V to +70V).  Positive high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  DGND Digital ground.  VPP Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                                                                                                                                                                                                                                                                                                                      | 20  | DIN1 | Serial data in for P-channel and N-channel pattern registers.          |  |  |  |  |  |  |

| PGND Power ground path for RTZ output transistors.  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  No connection.  Regative high voltage supply (-3.0V to -70V).  No connection.  Positive high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  Negative high voltage supply (+3.0V to -70V).  Transmit pulser outputs for channel 3.  VPP Rositive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 3.  VPP Rositive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 4.  VNN Negative high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Dositive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total. | 21  | VRN  | Negative supply for VPF regulator (-5.0V).                             |  |  |  |  |  |  |

| Power ground path for RTZ output transistors.  Power ground path for RTZ output transistors.  Power ground path for RTZ output transistors (-5.0V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  NC No connection.  NC No connection.  NN No linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  NN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  Negative high voltage supply (-3.0V to -70V).  Negative high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 3.  Transmit pulser outputs for channel 3.  Transmit pulser outputs for channel 3.  Transmit pulser outputs for channel 4.  Negative high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 4.  Negative high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  Negative high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                                                                                                                | 22  | PVDD | Positive gate drive supply voltage for RTZ output transistors (+5.0V). |  |  |  |  |  |  |

| PGND  Negative gate drive supply voltage for RTZ output transistors (-5.0V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  NC No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  VPP  VNN  Negative high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  Negative high voltage supply (-3.0V to -70V).  Negative high voltage supply (-3.0V to -70V).  Positive high voltage supply (-3.0V to +70V).  Transmit pulser outputs for channel 3.  VPP  Negative high voltage supply (+3.0V to +70V).  Positive high voltage supply (-3.0V to -70V).  Negative high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP  Doshib positive high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                                                                                                                                                                                                                                                                                                    | 23  | PGND | D                                                                      |  |  |  |  |  |  |

| VPF Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  NC No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VNF Regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  VNN Negative high voltage supply (+3.0V to +70V).  Negative high voltage supply (-3.0V to -70V).  Negative high voltage supply (+3.0V to +70V).  Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 4.  VNN Negative high voltage supply (-3.0V to -70V).  VNN Negative high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  VPF Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                                                                                                                                                                                                                                                                           | 24  | PGND | Power ground path for R12 output transistors.                          |  |  |  |  |  |  |

| ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.  NC No connection.  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  Transmit pulser outputs for channel 2.  VNP Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  Transmit pulser outputs for channel 3.  TX3 Transmit pulser outputs for channel 3.  TX4 Transmit pulser outputs for channel 3.  Positive high voltage supply (+3.0V to +70V).  TX4 Transmit pulser outputs for channel 4.  VPP Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25  | PVSS | Negative gate drive supply voltage for RTZ output transistors (-5.0V). |  |  |  |  |  |  |

| UNF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF cramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  VPP Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 3.  VNN Negative high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 3.  VPP Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 4.  VNN Negative high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Positive high voltage supply (+3.0V to +70V).  Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF and VPP pin. There are four in total.  PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26  | VPF  |                                                                        |  |  |  |  |  |  |

| ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 1.  VPP Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 2.  VNN Negative high voltage supply (-3.0V to -70V).  Transmit pulser outputs for channel 3.  VNN Negative high voltage supply (+3.0V to -70V).  Transmit pulser outputs for channel 3.  VPP Positive high voltage supply (+3.0V to +70V).  Transmit pulser outputs for channel 4.  VNN Negative high voltage supply (-3.0V to -70V).  VNN Negative high voltage supply (-3.0V to -70V).  Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  VPP Positive high voltage supply (+3.0V to +70V).  VPP Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF and VPP pin. There are four in total.  PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27  | NC   | No connection.                                                         |  |  |  |  |  |  |

| 30 TX1 Transmit pulser outputs for channel 1.  31 VPP 32 VPP 33 TX2 Transmit pulser outputs for channel 2.  34 VNN 35 VNN 36 TX3 Transmit pulser outputs for channel 3.  37 VPP 38 VPP 39 TX4 Transmit pulser outputs for channel 4.  40 VNN 41 VNN 41 VNN 42 VNF 42 UNF 43 DGND 44 VPP 45 Desitive high voltage supply (+3.0V to +70V).  45 VPF 46 Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  46 PGND 47 Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28  | VNF  |                                                                        |  |  |  |  |  |  |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29  | VNN  | Negative high voltage supply (-3.0V to -70V).                          |  |  |  |  |  |  |

| Solution   Positive high voltage supply (+3.0V to +70V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30  | TX1  | Transmit pulser outputs for channel 1.                                 |  |  |  |  |  |  |

| 32 VPP 33 TX2 Transmit pulser outputs for channel 2.  34 VNN 35 VNN 36 TX3 Transmit pulser outputs for channel 3.  37 VPP 38 VPP 39 TX4 Transmit pulser outputs for channel 4.  40 VNN 41 VNN 41 VNN 42 VNF 42 Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  43 DGND Digital ground.  44 VPP Positive high voltage supply (+3.0V to +70V).  45 VPF 46 PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31  | VPP  | Desitive high veltage eventy (12.0)/ to 170\/\                         |  |  |  |  |  |  |

| 34 VNN 35 VNN Negative high voltage supply (-3.0V to -70V).  36 TX3 Transmit pulser outputs for channel 3.  37 VPP 38 VPP 39 TX4 Transmit pulser outputs for channel 4.  40 VNN 41 VNN VNN Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  43 DGND Digital ground.  44 VPP Positive high voltage supply (+3.0V to +70V).  45 VPF Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  46 PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32  | VPP  | τ ositive riigit voitage supply (±3.0 v t0 ±70 v).                     |  |  |  |  |  |  |

| Negative high voltage supply (-3.0V to -70V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33  | TX2  | Transmit pulser outputs for channel 2.                                 |  |  |  |  |  |  |

| 35 VNN 36 TX3 Transmit pulser outputs for channel 3.  37 VPP 38 VPP 39 TX4 Transmit pulser outputs for channel 4.  40 VNN 41 VNN 41 VNN 42 VNF Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  43 DGND Digital ground.  44 VPP Positive high voltage supply (+3.0V to +70V).  45 VPF Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0μF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.  46 PGND Power ground path for RTZ output transistors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 34  | VNN  | Negative high veltage cumply ( 3.0V to70V)                             |  |  |  |  |  |  |