# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

#### **Features**

- Digital Self-supervising Watchdog with Hysteresis

- One 150-mA Output Driver for Relay

- One High-side Driver for N-channel Power FET

- Positive and Negative Enable Output

- Positive and Negative Reset Output

- Over/Under-voltage Detection

- Relay and Power FET Outputs Protected Against Standard Transients and 55-V Load Dump

### **Description**

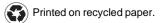

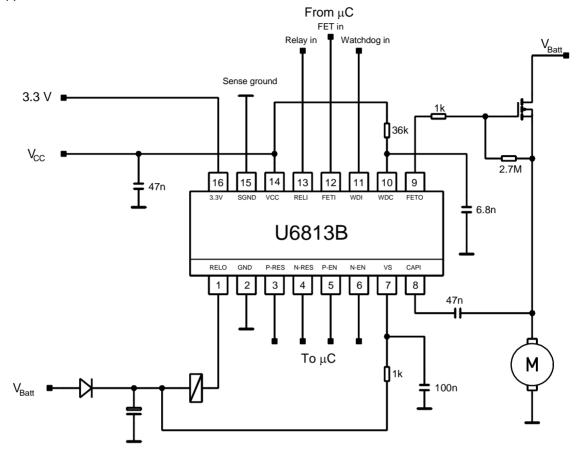

The function of microcontrollers in safety-critical applications (e.g., anti-lock systems) needs to be monitored permanently. Usually, this task is accomplished by an independent watchdog timer. The monolithic IC U6813B, designed in bipolar technology and qualified according to the needs of the automotive industry, includes such a watchdog timer and provides additional features for added value. With the help of integrated driver stages, it is easy to control safety-related functions of a relay and of an N-channel power MOSFET in high-side applications. In case of a microcontroller malfunction or supply-voltage anomalies, the U6813B provides positive and negative reset and enable output signals. This flexibility guarantees a broad range of applications. The U6813B is based on of Atmel's fail-safe ICs U6808B and U6809B.

Figure 1. Block Diagram

# Fail-safe IC with High-side and Relay Driver

U6813B

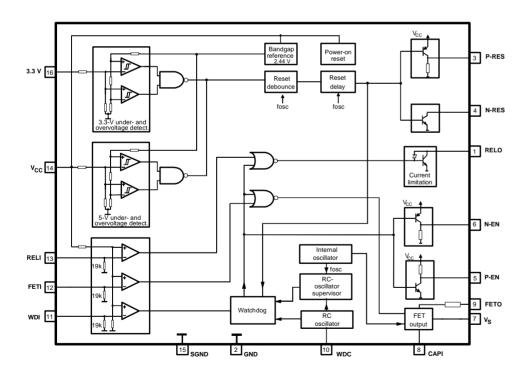

## **Pin Configuration**

Figure 2. Pinning SO16

## **Pin Description**

| Pin | Symbol          | Description                  | Function                                              | Туре           |

|-----|-----------------|------------------------------|-------------------------------------------------------|----------------|

| 1   | RELO            | Open-collector output driver | Fail-safe relay driver                                | Driver on: L   |

| 2   | GND             | Supply                       | General ground                                        |                |

| 3   | P-RES           | Digital output               | Positive reset signal                                 | Reset: H       |

| 4   | N-RES           | Digital output               | Negative reset signal                                 | Reset: L       |

| 5   | P-EN            | Digital output               | Positive enable signal                                | Enable: H      |

| 6   | N-EN            | Digital output               | Negative enable signal                                | Enable: L      |

| 7   | V <sub>S</sub>  | Battery supply               | Voltage for charge pump                               |                |

| 8   | CAPI            | Analog input                 | Input bootstrap capacitor                             |                |

| 9   | FETO            | Power FET output             | High voltage for N-channel FET                        |                |

| 10  | WDC             | Analog input                 | External RC for watchdog timer                        |                |

| 11  | WDI             | Digital input                | Watchdog trigger signal                               | Pulse sequence |

| 12  | FETI            | Digital input                | Activation of power FET                               | FET on: H      |

| 13  | RELI            | Digital input                | Activation of relay driver                            | Driver on: H   |

| 14  | V <sub>CC</sub> | Supply                       | 5-V supply                                            |                |

| 15  | SGND            | Supply                       | Sense ground, reference for V <sub>CC</sub> and 3.3 V |                |

| 16  | 3.3V            | Analog input                 | 3.3-V supply                                          |                |

### **Fail-safe Functions**

A fail-safe IC has to maintain its monitoring function even if there is a fault condition at one of the pins (e.g., short circuit), ensuring that a microcontroller system does not reach a "critical status". A critical status means, for example, if the system is not able to switch off the relay or disable the power MOSFET, or if the system is not able to provide a signal to the microcontroller via ENABLE- and RESET-outputs in the case of a fault condition. The U6813B is designed to handle those fault conditions according to Table 1 for a maximum of system safety.

Table 1. Truth Table

| VCC   | 3.3V  | WDI   | RELI             | FETI             | RELO | FETO | N-RES | P-RES | P-EN (2) | N-EN (3) |

|-------|-------|-------|------------------|------------------|------|------|-------|-------|----------|----------|

| ok    | ok    | ok    | Н                | Х                | on   | Х    | Н     | L     | Н        | L        |

| ok    | ok    | ok    | L <sup>(1)</sup> | Х                | off  | Х    | Н     | L     | Н        | L        |

| ok    | ok    | ok    | Х                | Н                | х    | on   | Н     | L     | Н        | L        |

| ok    | ok    | ok    | Х                | L <sup>(1)</sup> | х    | off  | Н     | L     | Н        | L        |

| ok    | ok    | wrong | Х                | Х                | off  | off  | Н     | L     | L        | Н        |

| Х     | wrong | Х     | Х                | Х                | off  | off  | L     | Н     | L        | Н        |

| wrong | Х     | Х     | Х                | Х                | off  | off  | L     | Н     | L        | Н        |

Notes: 1. default state at open input

P-EN disable: low

N-EN disable: high

### **Watchdog Description**

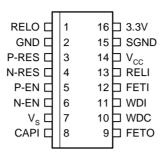

Figure 3. Watchdog Block Diagram

The microcontroller is monitored by a digital window watchdog which accepts an incomming trigger signal of a constant frequency for correct operation. The frequency of the trigger signal can be varied in a broad range as the watchdog's time window is determined by external R/C components. The following description refers to the watchdog timing diagram with tolerances (see Figure 4).

### **WDI Input (Pin 11)**

The microcontroller has to provide a trigger signal with the frequency  $f_{WDI}$  which is fed to the WDI input. A positive edge of  $f_{WDI}$  detected by a slope detector resets the binary counter and clocks the up/down counter. The latter one counts only from 0 to 3 or reverse. Each correct trigger increments the up/down counter by 1, each wrong trigger decrements it by 1. As soon as the counter reaches status 3, the RS flip-flop is set; see Figure 5 (Watchdog state diagram). A missing incoming trigger signal is detected after 250 clocks of the internal watchdog frequency  $f_{RC}$  (see WD\_OK output) and resets the up/down counter directly.

### **WDC Input (Pin 10)**

It is to be equiped by external R/C components. By means of an external R/C circuitry, the IC generates a time base (frequency  $f_{WDC}$ ) independent from the microcontroller. The watchdog's time window refers to a frequency of  $f_{WDC} = 100 \times f_{WDI}$ .

### **OSCERR Input**

A smart watchdog has to ensure that internal problems with its own time base are detected and do not lead to an undesired status of the complete system. If the RC oscillator stops oscillating, a signal is fed to the OSCERR input after a timeout delay. It resets the up/down counter and disables the WD-OK output. Without this reset function, the watchdog would freeze its current status when  $f_{\rm RC}$  stops.

### **RESET Input**

During power-on and under/overvoltage detection, a reset signal is fed to this pin. It resets the watchdog timer and sets the initial state.

#### **WD-OK Output**

After the up/down counter has reached to status 3 (see Figure 5, Watchdog State Diagram), the RS flip-flop is set and the WD-OK output becomes logic "1". As WD-OK is directly connected to the enable pins, the open-collector output P-EN provides also logic "1" while a logic "0" is available at N-EN output. If on the other hand the up/down counter is decremented to "0", the RS flip-flop is reset, the WD-OK output and the P-EN output are logic "0" and N-EN output is logic "1". The WD-OK output also controls a dual MUX stage which shifts the time window by one clock after a successful trigger, thus forming a hysteresis to provide stable conditions for the evaluation of the trigger signal "good or false". The WD-OK signal is also reset in case the watchdog counter is not reset after 250 clocks (missing trigger signal).

Figure 4. Watchdog Timing Diagram with Tolerances

| Time/s 79/              | f <sub>WDC</sub> 80/                         | f <sub>WDC</sub> 169                | / f <sub>WDC</sub> 170                       | / f <sub>WDC</sub>      | 250/ f <sub>WDC</sub>                                   | 251/ f <sub>WDC</sub> |

|-------------------------|----------------------------------------------|-------------------------------------|----------------------------------------------|-------------------------|---------------------------------------------------------|-----------------------|

|                         |                                              | Watchdog Window update rate is good |                                              |                         |                                                         |                       |

| Update rate is too fast | Update rate is<br>either too fast or<br>good |                                     | Update rate is<br>either too slow<br>or good | Update rate is too slow | Update rate is either too slow or pulse has dropped out | Pulse has dropped out |

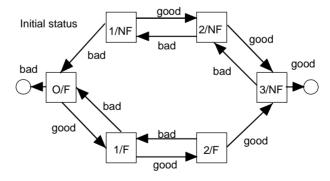

Figure 5. Watchdog State Diagram

### **Explanation**

In each block, the first character represents the state of the counter. The second notation indicates the fault status of the counter. A fault status is indicated by an "F" and a no-fault status is indicated by an "NF". When the watchdog is powered up initially, the counter starts at the 0/F block (initial state). "Good" indicates that a pulse has been received whose width resides within the timing window. "Bad" indicates that a pulse has been received whose width is either too short or too long.

# Watchdog Window Calculation

### **Example with recommended values**

$C_{osc} = 6.8 \text{ nF}$  (should be preferably 10%, NPO)

$R_{osc}$  = 36 k $\Omega$  (can be 5%,  $R_{osc}$  < 200 k $\Omega$  due to leakage current and humidity)

#### **RC** oscillator

$$t_{WDC}(s) = 10^{-3} [C_{osc}(nF) [(0.00078 R_{osc}(k\Omega)) + 0.0005]]$$

$f_{WDC}(Hz) = 1 / (t_{WDC})$

#### Watchdog WDI

$$\begin{split} f_{WDI} & (Hz) = 0.01 \; f_{WDC} \\ t_{WDC} = 200 \; \mu s \rightarrow f_{WDC} = 5 \; kHz \\ f_{WDI} = 50 \; Hz \quad \rightarrow t_{WDI} = 20 \; ms \end{split}$$

### WDI pulse width for fault detection after 3 pulses:

### Upper watchdog window

Minimum: 169/

$$f_{WDC}$$

= 33.8 ms ->  $f_{WDC}$ / 169 = 29.55 Hz

Maximum: 170/  $f_{WDC}$  = 34 ms ->  $f_{WDC}$ / 170 = 29.4 Hz

#### Lower watchdog window

Minimum:

$$79/f_{WDC} = 15.8 \text{ ms} -> f_{WDC} / 79 = 63.3 \text{ Hz}$$

Maximum:  $80/f_{WDC} = 16 \text{ ms} -> f_{WDC} / 80 = 62.5 \text{ Hz}$

#### WDI dropouts for immediate fault detection:

Minimum:  $250/ f_{WDC} = 50.0 \text{ ms}$ Maximum:  $251/ f_{WDC} = 50.2 \text{ ms}$

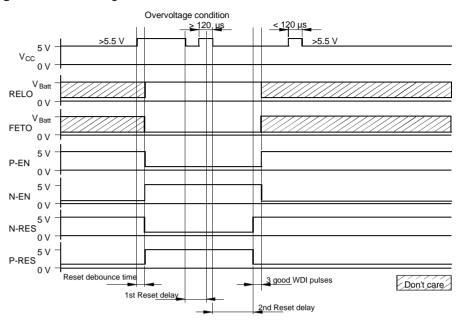

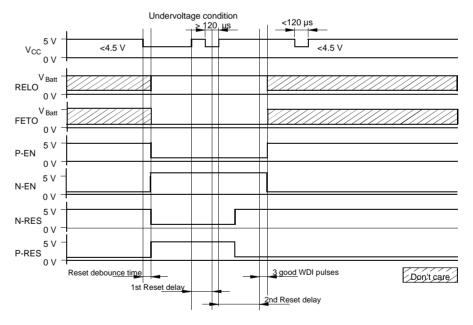

#### Remarks to reset relay

The duration of the over- or undervoltage pulses determines the enable- and reset outputs. A pulse duration shorter than the debounce time has no effect on the outputs. A pulse longer than the debounce time results in the first reset delay. If a pulse appears during this delay, a second delay time is triggered. Therefore, the total reset delay time can be longer than specified in the data sheet.

## **Absolute Maximum Ratings**

| Parameters                                                           | Symbol           | Value        | Unit |

|----------------------------------------------------------------------|------------------|--------------|------|

| Supply voltage range                                                 | V <sub>S</sub>   | - 0.2 to +26 | V    |

| Power dissipation $V_S = 5 \text{ V}; T_{amb} = -40^{\circ}\text{C}$ | P <sub>tot</sub> | 250          | mW   |

| $V_S = 5 \text{ V}; T_{amb} = 125^{\circ}\text{C}$                   | P <sub>tot</sub> | 150          | mW   |

| Junction temperature                                                 | T <sub>j</sub>   | 150          | °C   |

| Ambient temperature range                                            | T <sub>amb</sub> | -40 to +125  | O°   |

| Storage temperature range                                            | T <sub>stg</sub> | -55 to +155  | O°   |

### **Thermal Resistance**

| Parameters       | Symbol     | Value | Unit |

|------------------|------------|-------|------|

| Junction ambient | $R_{thJA}$ | 110   | K/W  |

### **Electrical Characteristics**

$V_{CC} = 5 \text{ V}, T_{amb} = -40 \text{ to } +125 ^{\circ}\text{C}; \text{ reference pin is GND or SGND (over- and under-voltage detection)}; \\ \underline{f}_{intern} = 200 \text{ kHz } +50\%/-45\%, f_{WDC} = 5 \text{ kHz } \pm 10\%; f_{WDI} = 50 \text{ Hz, bootstrap capacitor } C_{Boot} = 47 \text{ nF at Pin CAPI}$

| No. | Parameters                               | Test Conditions                                                                                  | Pin | Symbol             | Min.                     | Тур. | Max.                       | Unit     | Type* |

|-----|------------------------------------------|--------------------------------------------------------------------------------------------------|-----|--------------------|--------------------------|------|----------------------------|----------|-------|

| 1   | Supply                                   |                                                                                                  | +   | -                  | +                        | !    | +                          |          | +     |

| 1.1 | Operation-voltage range                  |                                                                                                  | 14  | V <sub>CC</sub>    | 4.5                      |      | 5.5                        | V        | D     |

| 1.2 | Operation-voltage range of RESET outputs |                                                                                                  | 14  | V <sub>cc</sub>    | 1.1                      |      | 18.0                       | V        | А     |

| 1.3 | Current consumption                      | $V = 5.25 \text{ V}$ , Relay on $T_{amb} = -40^{\circ}\text{C}$ $T_{amb} = +125^{\circ}\text{C}$ | 14  | I <sub>CC</sub>    |                          |      | 15<br>10                   | mA<br>mA | А     |

| 2   | Digital Input WDI                        |                                                                                                  |     |                    |                          | 11   |                            |          | 1     |

| 2.1 | Detection low                            |                                                                                                  | 11  | $V_{WDI}$          | -0.2                     |      | 0.3 × V <sub>CC</sub>      | V        | D     |

| 2.2 | Detection high                           |                                                                                                  | 11  | $V_{WDI}$          | 0.7 ×<br>V <sub>CC</sub> |      | V <sub>CC</sub><br>+ 0.2 V | V        | D     |

| 2.3 | Internal pull-down resistor              |                                                                                                  | 11  | R <sub>INT11</sub> | 10                       |      | 40                         | kΩ       | А     |

| 2.4 | Input current low                        | Input voltage = 0 V                                                                              | 11  | I <sub>WDI</sub>   | -5                       |      | 5                          | μA       | Α     |

| 2.5 | Input current high                       | Input voltage = 5 V                                                                              | 11  | I <sub>WDI</sub>   | 100                      |      | 550                        | μA       | Α     |

| 3   | Digital Input RELI                       |                                                                                                  |     |                    |                          |      |                            |          |       |

| 3.1 | Detection low                            |                                                                                                  | 13  | V <sub>RELI</sub>  | -0.2                     |      | 0.3 ×<br>V <sub>CC</sub>   | V        | D     |

| 3.2 | Detection high                           |                                                                                                  | 13  | $V_{RELI}$         | 0.7 × V <sub>CC</sub>    |      | V <sub>CC</sub><br>+ 0.2 V | V        | D     |

| 3.3 | Internal pull-down resistor              |                                                                                                  | 13  | R <sub>INT13</sub> | 10                       |      | 40                         | kΩ       | А     |

| 3.4 | Input current low                        | Input voltage = 0 V                                                                              | 13  | I <sub>RELI</sub>  | -5                       |      | 5                          | μA       | Α     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter Note:

1. If V<sub>S</sub> > 26 V the current has to be limited at 5 mA by an external resistor.

$V_{CC} = 5$  V,  $T_{amb} = -40$  to +125°C; reference pin is GND or SGND (over- and under-voltage detection);  $f_{intern} = 200$  kHz +50%/-45%,  $f_{WDC} = 5$  kHz  $\pm 10$ %;  $f_{WDI} = 50$  Hz, bootstrap capacitor  $C_{Boot} = 47$  nF at Pin CAPI

| IIIICIII | · V                                  | , MDI                       |          | <u> </u>           | <u> </u>                   | DOOL |                            |      |       |

|----------|--------------------------------------|-----------------------------|----------|--------------------|----------------------------|------|----------------------------|------|-------|

| No.      | Parameters                           | Test Conditions             | Pin      | Symbol             | Min.                       | Тур. | Max.                       | Unit | Type* |

| 3.5      | Input current high                   | Input voltage = 5 V         | 13       | I <sub>RELI</sub>  | 100                        |      | 550                        | μA   | Α     |

| 4        | Digital Input FETI                   |                             |          |                    |                            |      |                            |      |       |

| 4.1      | Detection low                        |                             | 12       | V <sub>FETI</sub>  | -0.2                       |      | 0.3 ×<br>V <sub>CC</sub>   | V    | А     |

| 4.2      | Detection high                       |                             | 12       | V <sub>FETI</sub>  | 0.7 × V <sub>CC</sub>      |      | V <sub>CC</sub><br>+ 0.2 V | V    | А     |

| 4.3      | Internal pull-down resistor          |                             | 12       | R <sub>INT12</sub> | 10                         |      | 40                         | kΩ   | А     |

| 4.4      | Input current low                    | Input voltage = 0 V         | 12       | I <sub>FETI</sub>  | -5                         |      | 5                          | μA   | Α     |

| 4.5      | Input current high                   | Input voltage = 5 V         | 12       | I <sub>FETI</sub>  | 100                        |      | 550                        | μA   | Α     |

| 5        | Digital Output N-RES                 | (Open Collector)            |          |                    | 1                          | 1    |                            |      | -1    |

| 5.1      | Saturation voltage low               | I <sub>reset</sub> ≤ 2.5 mA | 4        | V <sub>SAT4</sub>  |                            |      | 0.5                        | V    | А     |

| 5.2      | Leakage current                      | at 5 V, high state          | 4        | I <sub>LEAK4</sub> |                            |      | 0.5                        | μA   | Α     |

| 5.3      | Reset debounce time (switch to low)  | Over- or undervoltage       | 4        | t <sub>DEB4</sub>  | 120                        | 320  | 500                        | μs   | Α     |

| 5.4      | Reset delay (switch back to high)    | Over- or undervoltage       | 4        | t <sub>DEL4</sub>  |                            | 50   |                            | ms   | А     |

| 6        | Digital Output P-RES                 | (Internal Pull-down Res     | istor)   | l                  |                            | 1    |                            |      | II.   |

| 6.1      | Saturation voltage high              | I <sub>reset</sub> ≤ 0.3 mA | 3        | V <sub>SAT3</sub>  | V <sub>CC</sub> -<br>0.5 V |      | V <sub>CC</sub>            | V    | А     |

| 6.2      | Leakage current                      | at 0 V, low state           | 3        | I <sub>LEAK3</sub> |                            |      | 0.5                        | μA   | Α     |

| 6.3      | Internal pull-down resistor          | at 5 V                      | 3        | R <sub>INT3</sub>  | 25                         |      | 100                        | kΩ   | Α     |

| 6.4      | Reset debounce time (switch to low)  | Over- or undervoltage       | 3        | t <sub>DEB3</sub>  | 120                        | 320  | 500                        | μs   | А     |

| 6.5      | Reset delay (switch back to high)    | Over- or undervoltage       | 3        | t <sub>DEL3</sub>  |                            | 50   |                            | ms   | А     |

| 7        | Digital Output N-EN (                | with Open Collector and     | Internal | Pull-down Re       | esistor)                   |      |                            |      | +     |

| 7.1      | Saturation voltage high              | I ≤ 1 mA                    | 6        | V <sub>SAT6</sub>  | V <sub>CC</sub> -<br>0.5V  |      | V <sub>CC</sub>            | V    | А     |

| 7.2      | Leakage current                      | at 0 V, low state           | 6        | I <sub>LEAK6</sub> |                            |      | 0.5                        | μA   | Α     |

| 7.3      | Internal pull-down resistor          | at 5 V                      | 6        | R <sub>INT6</sub>  | 25                         |      | 100                        | kΩ   | Α     |

| 7.4      | Enable debounce time (switch to low) | Over- or undervoltage       | 6        | t <sub>DEB6</sub>  | 120                        | 320  | 500                        | μs   | А     |

| 7.5      | Enable delay (switch back to high)   | Over- or undervoltage       | 6        | t <sub>DEL6</sub>  |                            | 85   |                            | ms   | А     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. If  $V_S > 26$  V the current has to be limited at 5 mA by an external resistor.

$V_{CC}=5$  V,  $T_{amb}=-40$  to +125°C; reference pin is GND or SGND (over- and under-voltage detection);  $f_{intern}=200$  kHz +50%/-45%,  $f_{WDC}=5$  kHz  $\pm10\%$ ;  $f_{WDI}=50$  Hz, bootstrap capacitor  $C_{Boot}=47$  nF at Pin CAPI

| No.  | Parameters                            | Test Conditions                                              | Pin      | Symbol              | Min.                  | Тур.    | Max.                  | Unit                     | Type*  |

|------|---------------------------------------|--------------------------------------------------------------|----------|---------------------|-----------------------|---------|-----------------------|--------------------------|--------|

| 8    | Digital Output P-EN (                 | nternal Pull-up Resistor                                     | )        | li .                | -11-                  |         | -11-                  | -11-                     | -11-   |

| 8.1  | Saturation voltage high               | I ≤ 3 mA                                                     | 5        | V <sub>SAT5</sub>   |                       |         | 0.5                   | V                        | А      |

| 8.2  | Leakage current                       | at 5 V, high state                                           | 5        | I <sub>LEAK5</sub>  |                       |         | 0.5                   | μΑ                       | А      |

| 8.3  | Internal pull-up resistor             | at 0 V                                                       | 5        | R <sub>INT5</sub>   | 12.5                  |         | 50                    | kΩ                       | А      |

| 8.4  | Enable debounce time (switch to high) | Over- or undervoltage                                        | 5        | t <sub>DEB5</sub>   | 120                   | 320     | 500                   | μS                       | А      |

| 8.5  | Enable delay (switch back to low)     | Over- or undervoltage                                        | 5        | t <sub>DEL5</sub>   |                       | 85      |                       | ms                       | А      |

| 9    | Relay Driver (RELO)                   | -                                                            |          | +                   | +                     |         | +                     | +                        | +      |

| 9.1  | Saturation voltage                    | I ≤ 150 mA                                                   | 1        | V <sub>SAT1</sub>   | 0.1                   |         | 0.5                   | V                        | Α      |

| 9.2  | Current limitation                    |                                                              | 1        | I <sub>LIM</sub>    | 150                   |         | 300                   | mA                       | Α      |

| 9.3  | Internal clamping voltage             |                                                              | 1        | V <sub>CL</sub>     | 26                    |         | 30                    | V                        | А      |

| 9.4  | Turn-off energy                       |                                                              | 1        |                     | 30                    |         |                       | mJ                       | С      |

| 9.5  | Leakage current                       | V <sub>Batt</sub> = 16 V<br>V <sub>Batt</sub> = 26 V at 25°C | 1        | I <sub>LEAK1</sub>  |                       |         | 20<br>200             | μ <b>Α</b><br>μ <b>Α</b> | А      |

| 10   | Power-FET Output FE                   | TO (Maximum Load Cap                                         | acitor a | FET Gate 47         | 0 pF, Char            | ge-pump | Frequency             | 110 to 30                | 0 kHz) |

| 10.1 | Output voltage                        | V <sub>S</sub> = 9 V to 15 V                                 | 9        | V <sub>OUT9</sub>   | V <sub>S</sub> + 10 V |         | V <sub>S</sub> + 15 V | V                        | Α      |

| 10.2 | Operation range                       |                                                              | 7        | Vs                  | 9                     |         | 20                    | V                        | Α      |

| 10.3 | Overvoltage shut-<br>down             |                                                              | 7        | V <sub>S</sub>      | 20                    |         | 24                    | V                        | А      |

| 10.4 | Internal clamping voltage             |                                                              | 9        | V <sub>CL</sub>     | 26                    |         | 30                    | V                        | А      |

| 10.5 | On/off frequency                      |                                                              | 9        | f                   |                       |         | 200                   | Hz                       | Α      |

| 10.6 | Maximum current                       | FETO                                                         | 9        | I <sub>FETO</sub>   | 10                    |         |                       | μΑ                       | А      |

| 11   | Battery Supply                        |                                                              |          |                     |                       |         |                       |                          |        |

| 11.1 | Internal clamping voltage             |                                                              | 7        | V <sub>CL</sub>     | 26                    |         | 30                    | V                        | А      |

| 11.2 | Clamping current capability (1)       |                                                              | 7        | I <sub>VS</sub>     | 5                     |         |                       | mA                       | А      |

| 11.3 | Leakage current                       | at FETI = low                                                | 7        | I <sub>LEAVS</sub>  |                       |         | 100                   | μА                       | Α      |

| 12   | Reset and V <sub>CC</sub> Contro      | ol                                                           |          | 1                   |                       | '       |                       |                          |        |

| 12.1 | Lower reset level                     | Reference SGND                                               | 14       | V <sub>CC</sub>     | 4.5                   |         | 4.75                  | V                        | Α      |

| 12.2 | Upper reset level                     | Reference SGND                                               | 14       | V <sub>CC</sub>     | 5.25                  |         | 5.5                   | V                        | Α      |

| 12.3 | Hysteresis                            |                                                              | 14       | V <sub>HYST14</sub> | 25                    |         | 100                   | mV                       | Α      |

| 12.4 | Reset debounce time                   |                                                              | 14       | t <sub>DEB</sub>    | 120                   | 320     | 500                   | μS                       | Α      |

| 12.5 | Reset delay                           |                                                              | 14       | t <sub>DEL</sub>    | 20                    | 50      | 80                    | ms                       | Α      |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. If  $V_S > 26$  V the current has to be limited at 5 mA by an external resistor.

$V_{CC}=5$  V,  $T_{amb}=-40$  to +125°C; reference pin is GND or SGND (over- and under-voltage detection);  $f_{intern}=200$  kHz +50%/-45%,  $f_{WDC}=5$  kHz  $\pm10\%$ ;  $f_{WDI}=50$  Hz, bootstrap capacitor  $C_{Boot}=47$  nF at Pin CAPI

| No.   | Parameters                                                                 | Test Conditions                                              | Pin | Symbol                | Min.  | Тур. | Max.  | Unit | Type* |

|-------|----------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----------------------|-------|------|-------|------|-------|

| 13    | Reset and 3.3 V Conti                                                      | rol                                                          | I.  |                       |       |      |       |      | l     |

| 13.1  | Lower reset level                                                          | Reference SGND                                               | 16  | V <sub>3.3V</sub>     | 2.97  |      | 3.13  | V    | Α     |

| 13.2  | Upper reset level                                                          | Reference SGND                                               | 16  | V <sub>3.3V</sub>     | 3.47  |      | 3.63  | V    | Α     |

| 13.3  | Hysteresis                                                                 |                                                              | 16  | V <sub>HYST16</sub>   | 15    |      | 70    | mV   | Α     |

| 13.4  | Reset debounce time                                                        |                                                              | 16  | t <sub>DEB16</sub>    | 120   | 320  | 500   | μS   | Α     |

| 13.5  | Reset delay                                                                |                                                              | 16  | t <sub>DEL16</sub>    | 20    | 50   | 80    | ms   | Α     |

| 13.6  | Current                                                                    |                                                              | 16  | I <sub>3.3V</sub>     |       |      | 0.5   | mA   | С     |

| 14    | RC Oscillator WDC                                                          |                                                              |     |                       |       |      |       | 1    |       |

| 14.1  | Oscillator frequency                                                       | $R_{OSC} = 36 \text{ k}\Omega$<br>$C_{OSC} = 6.8 \text{ nF}$ | 10  | f <sub>WDC</sub>      | 4.5   | 5    | 5.5   | kHz  | Α     |

| 15    | Watchdog Timing                                                            | 1                                                            |     |                       | *     |      | •     |      |       |

| 15.1  | Power-on-reset prolongation time                                           |                                                              |     | t <sub>POR</sub>      | 34.3  |      | 103.1 | ms   | Α     |

| 15.2  | Detection time for RC-oscillator fault                                     | V <sub>CR</sub> = constant                                   |     | t <sub>RCerror</sub>  | 81.9  |      | 246   | ms   | Α     |

| 15.3  | Time interval for over/under-voltage detection                             |                                                              |     | t <sub>D,OUV</sub>    | 0.16  |      | 0.64  | ms   | A     |

| 15.4  | Reaction time of reset output at over/under voltage                        |                                                              |     | t <sub>R,OUV</sub>    | 0.187 |      | 0.72  | ms   | A     |

| 15.5  | Nominal frequency for WDI                                                  | f <sub>RC</sub> = 100 f <sub>WDI</sub>                       |     | $f_{WDI}$             | 10    |      | 65    | Hz   | D     |

| 15.6  | Nominal frequency for WDC                                                  | $f_{WDI} = 1/100 f_{WDC}$                                    |     | $f_{WDC}$             | 1     |      | 6.5   | kHz  | D     |

| 15.7  | Minimum pulse<br>duration for a<br>guaranteed WDI<br>input-pulse detection | f <sub>WDC</sub> = 5 kHz                                     |     | t <sub>P,WDI</sub>    | 364   |      |       | μs   | А     |

| 15.8  | Frequency range for a correct WDI signal                                   | f <sub>WDC</sub> = 5 kHz                                     |     | $f_{WDI}$             | 32.35 |      | 56.25 | Hz   | D     |

| 15.9  | Number of incorrect<br>WDI trigger counts for<br>locking the outputs       |                                                              |     | n <sub>lock</sub>     |       | 3    |       |      | А     |

| 15.10 | Number of correct<br>WDI trigger counts for<br>releasing the outputs       |                                                              |     | n <sub>release</sub>  |       | 3    |       |      | А     |

| 15.11 | Detection time for a stucked WDI signal                                    | $V_{WDI}$ = constant<br>$f_{WDC}$ = 5 kHz                    |     | t <sub>WDIerror</sub> | 49    |      | 51    | ms   | Α     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. If  $V_S > 26$  V the current has to be limited at 5 mA by an external resistor.

$V_{CC}=5$  V,  $T_{amb}=-40$  to +125°C; reference pin is GND or SGND (over- and under-voltage detection);  $f_{intern}=200$  kHz +50%/-45%,  $f_{WDC}=5$  kHz  $\pm10\%$ ;  $f_{WDI}=50$  Hz, bootstrap capacitor  $C_{Boot}=47$  nF at Pin CAPI

| No.  | Parameters                                                                 | Test Conditions                              | Pin | Symbol | Min. | Тур. | Max. | Unit   | Type* |

|------|----------------------------------------------------------------------------|----------------------------------------------|-----|--------|------|------|------|--------|-------|

| 16   | Watchdog Timing Rel                                                        | Natchdog Timing Relative to f <sub>WDC</sub> |     |        |      |      |      |        |       |

| 16.1 | Minimum pulse<br>duration for a<br>guaranteed WDI<br>input-pulse detection |                                              |     |        |      | 2    |      | cycles | A     |

| 16.2 | Frequency range for a correct WDI signal                                   |                                              |     |        | 80   |      | 170  | cycles | D     |

| 16.3 | Hysteresis range at the WDI ok margins                                     |                                              |     |        |      | 1    |      | cycle  | А     |

| 16.4 | Detection time for a stucked WDI signal (WDI dropout)                      | V <sub>WDI</sub> = constant                  |     |        | 250  |      | 251  | cycles | А     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. If  $V_S > 26$  V the current has to be limited at 5 mA by an external resistor.

Table 2. Protection Versus Transient Voltages According to ISO TR 7637-1 Level 4 (Except Pulse 5)

| Pulse | Voltage | Source Resistance (1) | Rise Time | Duration | Amount |

|-------|---------|-----------------------|-----------|----------|--------|

| 1     | - 110 V | 10 Ω                  | 100 V/s   | 2 ms     | 15.000 |

| 2     | + 110 V | 10 Ω                  | 100 V/s   | 0.05 ms  | 15.000 |

| 3a    | - 160 V | 50 Ω                  | 30 V/ns   | 0.1 μs   | 1 h    |

| 3b    | + 150 V | 50 Ω                  | 20 V/ns   | 0.1 μs   | 1 h    |

| 5     | 55 V    | 2 Ω                   | 10 V/ms   | 250 ms   | 20     |

Note: 1. In the case of the relay driver, the coil resistance of  $R_{min}$  = 150  $\Omega$  has to be added to the source resistance.

# **Timing Diagrams**

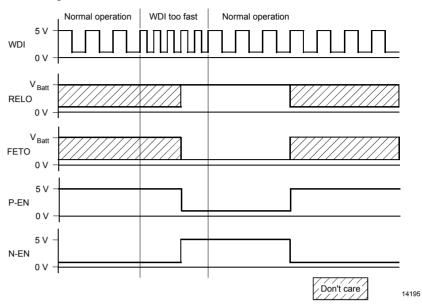

Figure 6. Watchdog in Too-fast Condition

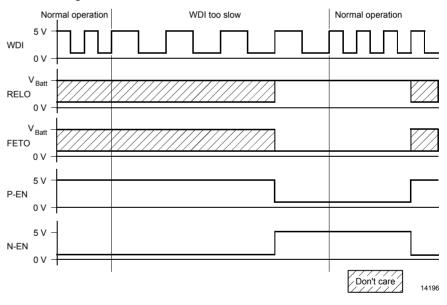

Figure 7. Watchdog in Too-slow Condition

Figure 8. Overvoltage Condition

Figure 9. Undervoltage Condition

Figure 10. Application Circuit

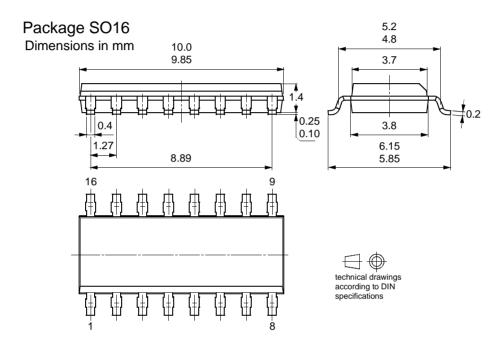

# **Ordering Information**

| Extended Type Number | Package | Remarks          |

|----------------------|---------|------------------|

| U6813B-MFPG3         | SO16    | Taped and reeled |

# **Package Information**

### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80

e-mail literature@atmel.com

Web Site http://www.atmel.com

#### © Atmel Corporation 2002.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Atmel® is the registered trademark of Atmel.

Other terms and product names may be the trademarks of others.