1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# HCPL - 800J PLC Powerline DAA IC

# **Data Sheet**

# Description

The HCPL-800J is a galvanically isolated Powerline Data Access Arrangement IC. It provides the key features of isolation, Tx line driver and Rx amplifier as required in a powerline modem application.

Used together with a simple LC coupling circuit, the HCPL-800J offers a highly integrated, cost effective Analogue Front End (AFE) solution. Optical coupling technology provides very high isolation mode rejection, facilitating excellent EMI and EMC performance. Application robustness is enhanced by the inherent properties of opto-isolation devices, to effectively block the transfer of damaging surge transients.

Excellent transmitter performance is achieved with the use of a high efficiency, low distortion line driver stage. Transmitter robustness is further enhanced with integrated load detection and over-temperature protection functions.

The HCPL-800J is designed to work with various transceiver ICs and significantly simplify the implementation of a powerline modem.

# Features

- -60 dB Overall Tx Distortion

- 25 nV/ Typical Input Referred Noise

- Load Detection Function

- Under-Voltage Detection

- Over-Temperature Shutdown

- Highly Efficient Tx Line Driver

- Built-in Rx Amplifier

- Temperature Range: -40°C to +85°C

- Regulatory Approvals (pending): UL, CSA, IEC/EN/DIN EN 60747-5-2

- Suitable for FCC Part 15 and EN50065-1 Compliant Design

#### **Applications**

- Automatic Meter Reading (AMR)

- Powerline Modem

- Home Automation/Control

- Security and Surveillance

- General Purpose Isolated Transceiver

- Internet Appliances

CAUTION: It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

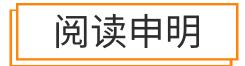

#### **Connection Diagram**

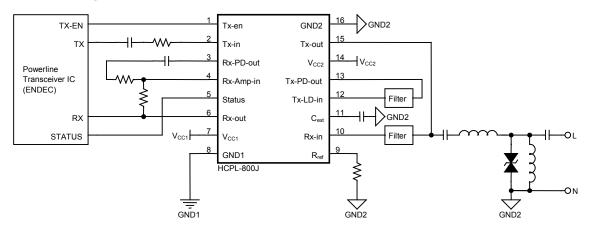

#### **Block Diagram**

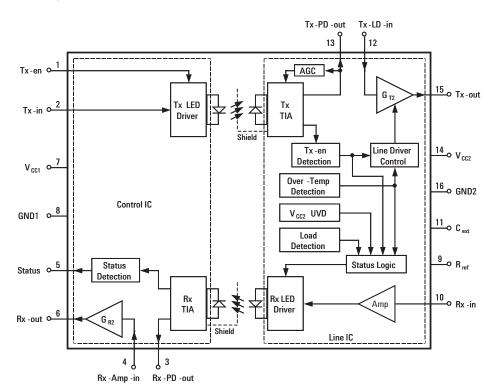

#### Package Pin Out

#### **Pin Descriptions**

| Pin No. | Symbol           | Description                                               |

|---------|------------------|-----------------------------------------------------------|

| 1       | Tx-en            | Transmit Enable Input                                     |

| 2       | Tx-in            | Transmit Input Signal                                     |

| 3       | Rx-PD-out        | Rx Photodetector Output                                   |

| 4       | Rx-Amp-in        | Receiver Output Amplifier Input                           |

| 5       | Status           | Signal indicating Line Condition                          |

| 6       | Rx-out           | Receiving Signal Output                                   |

| 7       | V <sub>cc1</sub> | 5 V Power Supply                                          |

| 8       | GND1             | VCC1 Power Supply Ground                                  |

| 9       | $R_{ref}$        | Sets Line Driver biasing current, typically 24 k $\Omega$ |

| 10      | Rx-in            | Receiving Signal Input from Powerline                     |

| 11      | C <sub>ext</sub> | External Capacitor                                        |

| 12      | Tx-LD-in         | Tx Line Driver Input                                      |

| 13      | Tx-PD-out        | Tx Photodetector Output                                   |

| 14      | V <sub>CC2</sub> | 5 V Power Supply                                          |

| 15      | Tx-out           | Transmit Signal Output to Powerline                       |

| 16      | GND2             | VCC2 Power Supply Ground                                  |

#### **Ordering Information**

|             | Option                | _         |               |             | IEC/EN/DIN EN |              |

|-------------|-----------------------|-----------|---------------|-------------|---------------|--------------|

| Part number | <b>RoHS</b> Compliant | Packaging | Surface Mount | Tape & Reel | 60747-5-2     | Quantity     |

| HCPL-800J   | -000E                 | SO-16     | Х             |             | Х             | 45 per tube  |

|             | -500E                 | SO-16     | Х             | Х           | Х             | 850 per reel |

HCPL-800J are UL Recognized with 3750 Vrms for 1 minute per UL1577.

To order, choose a part number from the part number column and combine with the desired option from the option column to form an order entry.

Example 1:

ACPL-800J-500E to order product of SO-16 package in Tape and Reel packaging packaging with IEC/EN/DIN EN 60747-5-2 Safety Approval in RoHS compliant..

Option datasheets are available. Contact your Avago sales representative or authorized distributor for information.

Remarks: The notation '#XXX' is used for existing products, while (new) products launched since 15th July 2001 and RoHS compliant option will use '-XXXE'.

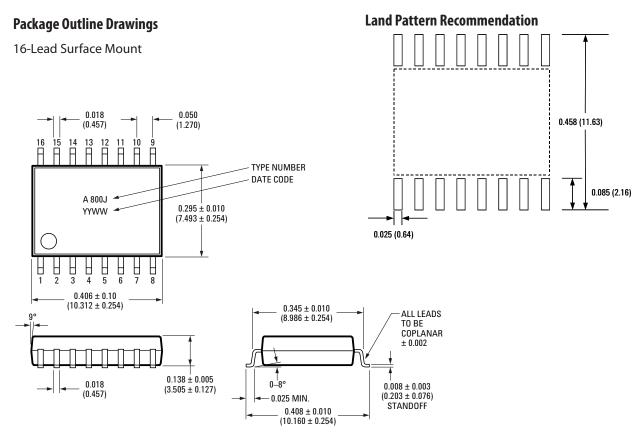

DIMENSIONS IN INCHES (MILLIMETERS).

NOTES:

- 1. INITIAL AND CONTINUED VARIATION IN THE COLOR OF THE HCPL-800J'S WHITE MOLD COMPOUND IS NORMAL AND DOES NOT AFFECT DEVICE PERFORMANCE OR RELIABILITY.

- 2. FLOATING LEAD PROTRUSION IS 0.006 (0.15) MAX.

#### **Package Characteristics**

All specifications and figures are at the nominal (typical) operating conditions of  $V_{cc1} = 5 \text{ V}$ , GND1 = 0 V,  $V_{cc2} = 5 \text{ V}$ , GND2 = 0 V and  $T_{a} = +25^{\circ}\text{C}$ .

| Parameter                                           | Symbol           | Min. | Тур. | Max. | Units            | Test Conditions                                              | Note    |

|-----------------------------------------------------|------------------|------|------|------|------------------|--------------------------------------------------------------|---------|

| Control IC - Line IC Momentary<br>Withstand Voltage | V <sub>ISO</sub> | 3750 |      | ·    | V <sub>rms</sub> | RH< 50%, t = 1 min.,<br>T <sub>A</sub> = 25°C                | 1, 2, 3 |

| Resistance (Control IC - Line IC)                   | R <sub>I-O</sub> |      | >109 |      | Ω                | V <sub>I-0</sub> = 500 Vdc                                   | 3       |

| Capacitance (Control IC - Line IC)                  | C <sub>I-O</sub> |      | 1.4  |      | pF               | f = 1 MHz                                                    |         |

| Control IC to Ambient Thermal<br>Resistance         | $\theta_{IA}$    |      | 83   | ·    | °C/W             | 1 oz. trace, 2-layer PCB<br>Still air, T <sub>A</sub> = 25°C | 4       |

| Line IC to Ambient Thermal<br>Resistance            | $\theta_{_{OA}}$ |      | 85   |      | _                |                                                              |         |

Notes:

1. In accordance with UL1577, each optocoupler is proof tested by applying an insulation test voltage  $\geq$  4500 Vrms for 1 second (leakage detection current limit, I<sub>L0</sub>  $\leq$  5 µA). This test is performed before the 100% production test for partial discharge (method b) shown in IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table, if applicable.

2. The Control IC-Line IC Momentary Withstand Voltage is a dielectric voltage rating that should not be interpreted as a Control IC-Line IC continuous voltage rating. For the continuous voltage rating refer to your equipment level safety specification or IEC/EN/DIN EN 60747-5-2 Insulation Characteristics Table.

3. Device is considered as a two terminal device: pins 1 - 8 shorted together and pins 9 - 16 shorted together.

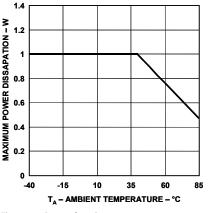

4. Maximum power dissipation in Control side and Line side IC's needs to be limited to ensure that their respective junction temperature is less than 125°C. The maximum permissible power dissipation is dependent on the thermal impedance and the ambient temperature. Details on the typical thermal impedances are given in the Package Characteristics. Further details on applying this to an actual application can be found in the Application Information section under Thermal Considerations.

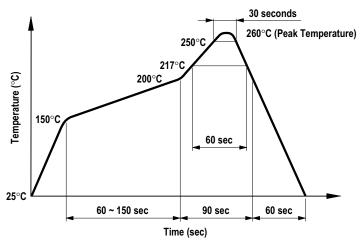

#### **Recommended PB-free IR Profile**

Note: Non-halide flux should be used

#### **Regulatory Information**

The HCPL-800J is pending for approval by the following organizations:

#### **IEC/EN/DIN EN 60747-5-2**

UL

Approved under: IEC 60747-5-2:1997 + A1:2002 EN 60747-5-2:2001 + A1:2002 DIN EN 60747-5-2 (VDE 0884 Teil 2):2003-01 with VIORM = 891 Vpeak. Recognized under UL 1577, component recognition program, File E55361.

#### CSA

Approved under CSA Acceptance Notice #5, File CA 88324.

#### IEC/EN/DIN EN 60747-5-2 Insulation Characteristics (1)

| Description                                                                                                                                                                                 | Symbol                                                            | Characteristic            | Unit              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------|-------------------|

| Installation classification per DIN VDE 0110/1.89, Table 1<br>For rated mains voltage $\leq$ 150 Vrms<br>For rated mains voltage $\leq$ 300 Vrms<br>For rated mains voltage $\leq$ 600 Vrms |                                                                   | – IV<br>  – III<br>  – II |                   |

| Climatic Classification                                                                                                                                                                     |                                                                   | 55/100/21                 |                   |

| Pollution Degree (DIN VDE 0110/1.89)                                                                                                                                                        |                                                                   | 2                         |                   |

| Maximum Working Insulation Voltage                                                                                                                                                          | V                                                                 | 891                       | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method b $^{\scriptscriptstyle (2)}$ $V_{_{\rm IORM}}$ x 1.875 = $V_{_{\rm PR}}$ , 100% Production Test with $t_{_{\rm m}}$ = 1 sec, Partial Discharge < 5 pC | V <sub>PR</sub>                                                   | 1670                      | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method a $^{(2)}$ $V_{\rm IORM}$ x 1.5 = $V_{\rm PR}$ , Type and Sample Test, $t_{\rm m}$ = 60 sec, Partial Discharge < 5 pC                                  | V <sub>PR</sub>                                                   | 1336                      | V <sub>PEAK</sub> |

| Highest Allowable Over-voltage <sup>(2)</sup><br>(Transient Over-voltage tini = 10 sec)                                                                                                     | V <sub>IOTM</sub>                                                 | 6000                      | V <sub>PEAK</sub> |

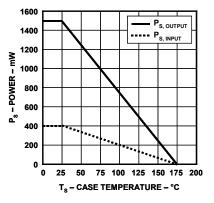

| Safety-limiting values - maximum values allowed in the event of a failure<br>Case Temperature<br>Control Side Power <sup>(3)</sup><br>Line Side Power <sup>(3)</sup>                        | T <sub>s</sub><br>P <sub>s, input</sub><br>P <sub>s, output</sub> | 175<br>400<br>1500        | °C<br>mW<br>mW    |

| Insulation Resistance at $T_{s'} V_{IO} = 500 V$                                                                                                                                            | R <sub>s</sub>                                                    | >109                      | Ω                 |

#### Notes:

- 1. Isolation characteristics are guaranteed only within the safety maximum ratings that must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCO0802.

- Refer to the optocoupler section of the Isolation and Control Component Designer's Catalog, under Product Safety Regulations section, (IEC/EN/DIN EN 60747-5-2) for a detailed description of Method a and Method b partial discharge test profiles.

- 3. Refer to the following figure for dependence of PS, INPUT and PS, OUTPUT on case temperature.

# **Insulation and Safety Related Specifications**

| Parameter                                            | Symbol | Value | Unit  | Condition                                                                                                                   |

|------------------------------------------------------|--------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------|

| Minimum External Air Gap<br>(Clearance)              | L(101) | 8.3   | mm    | Measured from input terminals to output terminals, short-<br>est distance through air.                                      |

| Minimum External Tracking<br>(Creepage)              | L(102) | 8.3   | mm    | Measured from input terminals to output terminals, short-<br>est distance path along body.                                  |

| Minimum Internal Plastic Gap<br>(Internal Clearance) |        | 0.5   | mm    | Through insulation distance of conductor to conductor, usually the straight-line distance between the emitter and detector. |

| Tracking Resistance<br>(Comparative Tracking Index)  | CTI    | >175  | Volts | DIN IEC 112/VDE 0303 Part 1                                                                                                 |

| Isolation Group                                      |        | Illa  |       | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                |

#### **Absolute Maximum Ratings**

| Parameter                         | Symbol              | Minimum                       | Maximum          | Unit | Note |

|-----------------------------------|---------------------|-------------------------------|------------------|------|------|

| Storage Temperature               | T <sub>s</sub>      | -55                           | 125              | °C   |      |

| Ambient Operating Temperature     | T <sub>A</sub>      | -40                           | 85               | °C   |      |

| Junction Temperature              | T                   |                               | 125              | °C   |      |

| Supply Voltage 1                  | V <sub>cc1</sub>    | -0.5                          | 5.5              | V    |      |

| Supply Voltage 2                  | V <sub>cc2</sub>    | -0.5                          | 5.5              | V    |      |

| Transmit Output Voltage           | V <sub>Tx-out</sub> | -0.5                          | V <sub>cc2</sub> | V    |      |

| Transmit Input Signal Voltage     | V <sub>Tx-in</sub>  | -0.5                          | V <sub>cc1</sub> | V    | 1    |

| Transmit Enable Voltage           | V <sub>Tx-en</sub>  | -0.5                          | V <sub>cc1</sub> | V    |      |

| Receiving Input Signal Voltage    | V <sub>Rx-in</sub>  | -0.5                          | V <sub>cc2</sub> | V    |      |

| Control-Side Power Dissipation    | P                   |                               | 200              | mW   | 1    |

| Line-Side Power Dissipation       | Po                  |                               | 1000             | mW   |      |

| Solder Reflow Temperature Profile | (See Solder Reflow  | v Temperature Profile Section | on)              |      |      |

#### Notes:

1. Maximum power dissipation in Control side and Line side IC's needs to be limited to ensure that their respective junction temperature is less than 125°C. The maximum permissible power dissipation is dependent on the thermal impedance and the ambient temperature. Details on the typical thermal impedances are given in the Package Characteristics. Further details on applying this to an actual application can be found in the Application Information section under Thermal Considerations.

#### **Recommended Operating Conditions**

| Parameter                     | Symbol           | Minimum | Typical | Maximum | Unit            | Note |

|-------------------------------|------------------|---------|---------|---------|-----------------|------|

| Ambient Operating Temperature | T <sub>A</sub>   | -40     |         | 85      | °C              |      |

| Input Supply Voltage          | V <sub>cc1</sub> | 4.75    | 5       | 5.25    | V               |      |

| Output Supply Voltage         | V <sub>cc2</sub> | 4.75    | 5       | 5.25    | V               |      |

| Tx-in Signal Current          | I                |         | 250     |         | $\mu A_{_{PP}}$ | 1    |

Notes:

1. The transmitter input impedance is very low, this is meant for signal current input. Transmitter performance is optimized at 250  $\mu$ APP input signal, an external series resistor with nominal value of 2 k $\Omega$  would be required if the input signal is 0.5 V<sub>pp</sub>.

## **Electrical Specifications**

Unless otherwise noted, for sinusoidal waveform input and reference resistor  $R_{ref} = 24 \text{ k}\Omega$ , all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC1} = 5 \text{ V}$ ,  $V_{CC2} = 5 \text{ V}$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

#### General

| Parameter                                   | Symbol           | Min.                 | Тур. | Max. | Unit            | Test Condition                                           | Fig.    | Note |

|---------------------------------------------|------------------|----------------------|------|------|-----------------|----------------------------------------------------------|---------|------|

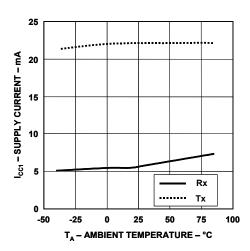

| V <sub>cc1</sub> Supply Current             | I <sub>CC1</sub> |                      | 6    | 15   | mA              | $V_{Tx-en} = 0 V$                                        | 1       |      |

|                                             |                  |                      | 20   | 28   | mA              | $V_{Tx-en} = 5 V$                                        |         |      |

| V <sub>cc2</sub> Supply Current             | I <sub>CC2</sub> |                      | 22   | 28   | mA              | $V_{Tx-en} = 0 V$                                        | 2       |      |

|                                             |                  |                      | 40   | 56   | mA              | $V_{Tx-en} = 5 V$                                        | 2, 3, 4 |      |

| Status Logic High Output                    | V <sub>OH</sub>  | V <sub>cc1</sub> - 1 |      |      | V               | I <sub>он</sub> = - 4 mA                                 |         |      |

| Status Logic Low Output                     | V <sub>OL</sub>  |                      |      | 1    | V               | $V_{cc2} = 3.5 \text{ V}, \text{ I}_{OL} = 4 \text{ mA}$ |         |      |

| V <sub>cc2</sub> Under Voltage<br>Detection | $V_{\rm UVD}$    | 3.8                  | 4    | 4.3  | V               |                                                          |         | 1    |

| Junction Over-Temperature<br>Threshold      | T <sub>th</sub>  |                      | 130  |      | °C              |                                                          |         | 2    |

| Load Detection Threshold                    |                  |                      | 0.6  |      | A <sub>PP</sub> | $V_{Tx-en} = 5 V, f = 132 kHz$                           | 5, 19   |      |

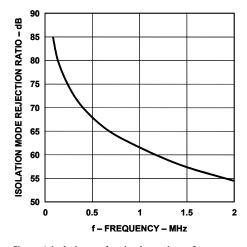

| Isolation Mode Rejection Ratio              | IMRR             |                      | 80   |      | dB              | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                   | 6, 20   | 3    |

Notes:

1. Threshold of falling  $\rm V_{\rm cc2}$  with hysteresis of 0.15 V (typ.).

2. Threshold of rising junction temperature with hysteresis of 15°C (typ.).

3. IMRR is defined as the ratio of the signal gain (measured at Rx-PD-out with signal applied to Rx-in) to the isolation mode gain (measured at Rx-PD-out with Rx-in connected to GND2 and the isolation mode voltage, V<sub>IM</sub> applied between GND1 and GND2), expressed in dB.

# **Electrical Specifications (Cont.)**

Unless otherwise noted, for sinusoidal waveform input and reference resistor  $R_{ref} = 24 \text{ k}\Omega$ , all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC1} = 5 \text{ V}$ ,  $V_{CC2} = 5 \text{ V}$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

# Transmitter

| Parameter                                           | Symbol                          | Min. | Тур. | Max. | Unit            | Test Condition                                                                                                                              | Fig.               | Note |

|-----------------------------------------------------|---------------------------------|------|------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| Transmit Enable Threshold<br>Voltage                | $V_{th}, T_{x-en}$              | 0.8  |      | 2.4  | V               |                                                                                                                                             |                    |      |

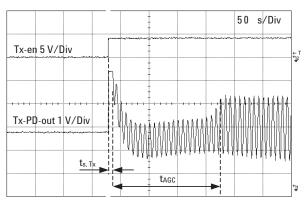

| Set-up Time (Tx-PD-out)                             | t <sub>s</sub> , T <sub>x</sub> |      | 10   |      | μs              | $V_{Tx-en} = 5 \text{ V}, \text{ I}_{Tx-in} = 250 \ \mu\text{A}_{pp'} \text{ f}$                                                            | 21                 | 1    |

| AGC Settling Time                                   | t <sub>AGC</sub>                |      | 180  |      | μs              | <ul> <li>= 132 kHz,</li> <li>Tx-PD-out no load</li> </ul>                                                                                   |                    | 2    |

| Tx Photodetector Output<br>Voltage (Tx-PD-out)      |                                 | 2.8  | 3.3  | 3.6  | V               | $V_{Tx-en} = 5 V, I_{Tx-in} = 250 \mu A_{PP'} f$<br>= 132 kHz, $T_A = 25^{\circ}C$                                                          | 7, 8, 9            |      |

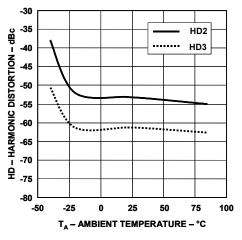

| 2nd Harmonic Distortion<br>Tx-PD-out)               | HD2 <sub>TxPD</sub>             |      | -50  |      | dB              | $V_{Tx-en} = 5 V, I_{Tx-in} = 250 \mu A_{pp}, f$<br>= 132 kHz, Tx-PD-out load                                                               | 10, 22             |      |

| 3rd Harmonic Distortion<br>(Tx-PD-out)              | HD3 <sub>TxPD</sub>             |      | -62  |      | dB              | - 1 kΩ                                                                                                                                      |                    |      |

| Bandwidth (Tx-PD-out)                               | BW                              |      | 1    |      | MHz             | $V_{Tx-en} = 5 \text{ V}, \text{ I}_{Tx-in} = 250 \mu \text{A}_{PP}$                                                                        |                    |      |

| Tx Photodetector Output<br>Impedance (Tx-PD-out)    | Z <sub>O' TxPD</sub>            |      | 1    |      | Ω               | $V_{Tx-en} = 5 V, f = 132 \text{ kHz}$                                                                                                      |                    |      |

| Line Driver (LD)                                    |                                 |      |      |      |                 |                                                                                                                                             |                    |      |

| Power Supply (V <sub>cc2</sub> )<br>Rejection Ratio | PSRR                            |      | 55   |      | dB              | 50 Hz ripple,<br>V <sub>ripple</sub> = 200 mV <sub>PP</sub>                                                                                 |                    |      |

| Input Impedance                                     | Z <sub>I, LD</sub>              |      | 10   |      | kΩ              | $V_{Tx-en} = 5 V, f = 132 \text{ kHz}$                                                                                                      |                    |      |

| DC Biased Voltage                                   | V <sub>Bias</sub> , LD          |      | 2.27 |      | V               | $V_{\text{Tx-en}} = 5 \text{ V}$                                                                                                            |                    |      |

| Gain                                                | G <sub>T2</sub>                 | 1.8  | 2    | 2.2  | V/V             | $V_{Tx-en} = 5 V, f = 132 \text{ kHz}, Tx-out no load$                                                                                      | 11                 |      |

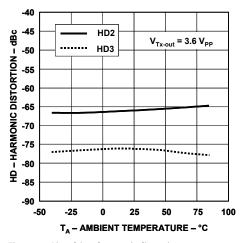

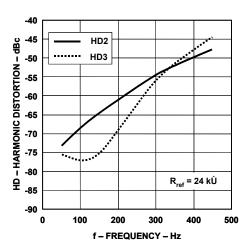

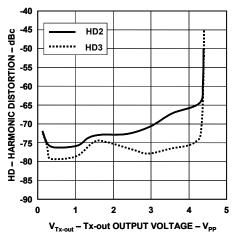

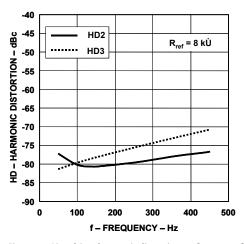

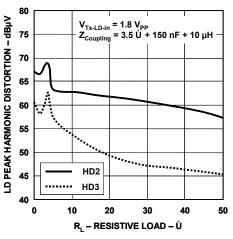

| 2nd Harmonic Distortion<br>(Tx-out)                 | HD2 <sub>LD</sub>               |      | -65  | -60  | dB              | $V_{\text{Tx-en}} = 5 \text{ V}, V_{\text{Tx-out}} = 3.6 \text{ V}_{\text{PP}}$<br>f = 132 kHz, Tx-out load 50                              | 12, 13,<br>14, 15, |      |

| 3rd Harmonic Distortion<br>(Tx-out)                 | HD3 <sub>LD</sub>               |      | -75  | -65  | dB              | $- \Omega, T_A = 25^{\circ}C$                                                                                                               | 16, 23             |      |

| Output Impedance (Tx-out)                           | Z <sub>o, LD</sub>              |      | 0.5  |      | Ω               | $V_{Tx-en} = 5 V, f = 132 \text{ kHz}$                                                                                                      |                    |      |

|                                                     |                                 |      | 7.5  |      | kΩ              | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                                                                                                      |                    |      |

| Short-Circuit Output Current                        | I <sub>os</sub>                 |      | 2    |      | A <sub>PP</sub> | $\begin{array}{l} V_{_{Tx-en}}=5 \text{ V},\\ V_{_{Tx-LD-in}}=1.8 V_{_{PP'}}\\ f=132 \text{ kHz}, t_{_{P}} \leq 50 \mu\text{s} \end{array}$ |                    | 3, 4 |

#### Notes:

1. Time from transmit is enabled (V<sub>Tx-en</sub> is set to logic high) until output (Tx-PD-out) is available. See Figure 26 in the Application Information section.

2. Time from output (Tx-PD-out) is available until Tx-PD-out signal reaches 66% of its steady state level. See Figure 26 in the Application Information section.

3. To keep the junction temperature as close to the ambient temperature as possible, pulse testing method is used. The device is transmitenabled within the pulse duration time, t<sub>r</sub>. Thermal effects must be considered separately.

4. Maximum power dissipation in Control side and Line side IC's needs to be limited to ensure that their respective junction temperature is less than 125°C. The maximum permissible power dissipation is dependent on the thermal impedance and the ambient temperature. Details on the typical thermal impedances are given in the Package Characteristics. Further details on applying this to an actual application can be found in the Application Information section under Thermal Considerations.

# **Electrical Specifications (Cont.)**

Unless otherwise noted, for sinusoidal waveform input and reference resistor  $R_{ref} = 24 \text{ k}\Omega$ , all typical values are at  $T_A = 25^{\circ}$ C,  $V_{CC1} = 5 \text{ V}$ ,  $V_{CC2} = 5 \text{ V}$ ; all Minimum/Maximum specifications are at Recommended Operating Conditions.

# Receiver

| Parameter                                | Symbol               | Min. | Тур. | Max. | Unit  | Test Condition                                                                                                                                                                                                                   | Fig. | Note |

|------------------------------------------|----------------------|------|------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

| Input Impedance                          | Z <sub>I, Rx</sub>   |      | 4    |      | kΩ    | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                                                                                                                                                                                           |      |      |

| Output Impedance (Rx-PD-out)             | Z <sub>O, RxPD</sub> |      | 30   |      | W √Hz | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                                                                                                                                                                                           |      |      |

| Input Referred Noise                     | V <sub>nr</sub>      |      | 25   |      | nV/   | $V_{Tx-en} = 0 V, V_{Rx-in} = 0 VPP$                                                                                                                                                                                             |      |      |

| Bandwidth (Rx-PD-out)                    | BW                   |      | 500  |      | kHz   | $V_{Tx-en} = 0 V$                                                                                                                                                                                                                |      |      |

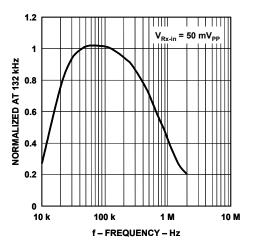

| Gain                                     | G <sub>R1</sub>      |      | 20   |      | dB    | $V_{Tx-en} = 0 V, V_{Rx-in} = 0.05 V_{PP'} f$<br>= 132 kHz                                                                                                                                                                       | 17   |      |

| Set-up Time (Rx-PD-out)                  | t <sub>s, Rx</sub>   |      | 10   |      | ms    | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                                                                                                                                                                                           |      |      |

| Total Harmonic Distortion<br>(Rx-PD-out) | THD <sub>RxPD</sub>  |      | -38  |      | dB    | $V_{Tx-en} = 0 V, V_{Rx-in} = 0.01 V_{PP'} f$<br>= 132 kHz                                                                                                                                                                       |      |      |

| Receiver Output Amplifier (RxAMP)        |                      |      |      |      |       |                                                                                                                                                                                                                                  |      |      |

| DC Biased Voltage                        | $V_{_{Bias,Rx}}$     |      | 2.27 |      | V     |                                                                                                                                                                                                                                  |      |      |

| Output Impedance                         | Z <sub>O, RxA</sub>  |      | 20   |      | W     | $V_{Tx-en} = 0 V, f = 132 \text{ kHz}$                                                                                                                                                                                           |      |      |

| Total Harmonic Distortion<br>(Rx-out)    | THD <sub>rx</sub>    |      | -60  |      | dB    | $\begin{split} V_{\text{Tx-en}} &= 0 \text{ V, } f = 132 \text{ kHz,} \\ V_{\text{Rx-Amp-in}} &= 0.5 \text{ V}_{\text{pp}} \text{ ,} \\ \text{Gain} &= -4 \text{ ,} \\ \text{feedback resistor } 20 \text{ k}\Omega \end{split}$ |      |      |

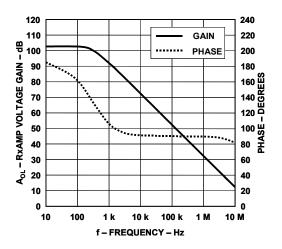

| Gain Bandwidth Product                   | GBW <sub>RxA</sub>   |      | 28   |      | MHz   | $\begin{split} V_{_{Tx\text{-}en}} &= 0 \text{ V, } f = 132 \text{ kHz,} \\ V_{_{Rx\text{-}in}} &= 0.1 \text{ V}_{_{PP}} \text{ G}_{_{R2}} = -20, \\ \text{feedback resistor } 20 \text{ k}\Omega \end{split}$                   | 18   |      |

#### **Typical Performance Plots**

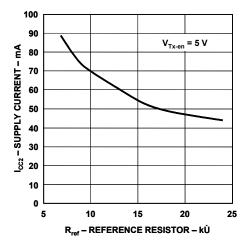

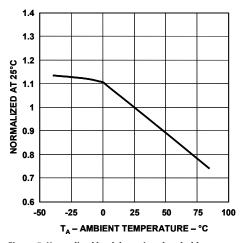

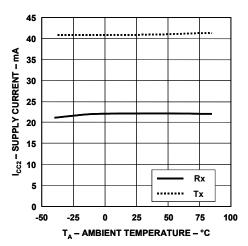

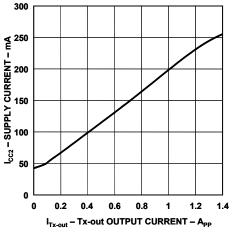

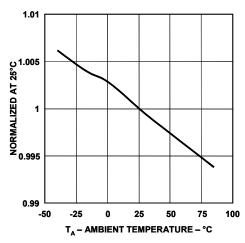

Unless otherwise noted, all typical plots are at  $T_A = 25^{\circ}$ C,  $V_{_{CC1}} = 5$  V,  $V_{_{CC2}} = 5$  V, sinusoidal waveform input, signal frequency f = 132 kHz,  $I_{_{Tx-in}} = 250 \mu A_{_{PP}}$  and  $R_{_{ref}} = 24 \text{ k}\Omega$ .

Figure 1.  $V_{\text{cc1}}$  supply current vs. temperature

Figure 3.  $V_{cc2}$  supply current vs. reference resistor

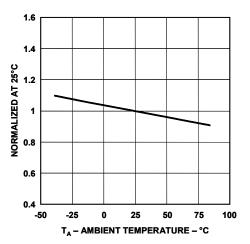

Figure 5. Normalized load detection threshold vs. temperature

Figure 2.  $V_{cc2}$  supply current vs. temperature

Figure 4.  $\rm V_{cc2}$  supply current vs. Tx output current

Figure 6. Isolation mode rejection ratio vs. frequency

#### **Typical Performance Plots (Cont.)**

Unless otherwise noted, all typical plots are at  $T_A = 25^{\circ}$ C,  $V_{_{CC1}} = 5$  V,  $V_{_{CC2}} = 5$  V, sinusoidal waveform input, signal frequency f = 132 kHz,  $I_{_{Tx-in}} = 250 \ \mu A_{_{PP'}}$  and  $R_{_{ref}} = 24 \ k\Omega$ .

Figure 7. Normalized Tx-PD-out output voltage vs. temperature

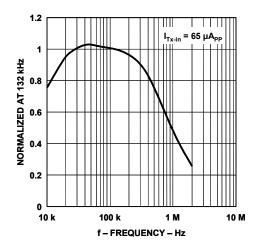

Figure 9. Normalized Tx-PD-out output voltage vs. frequency

Figure 11. Normalized line driver gain vs. temperature

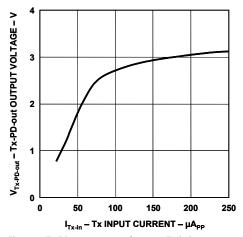

Figure 8. Tx-PD-out output voltage vs. Tx-in input current

Figure 10. Tx-PD-out harmonic distortion vs. temperature

Figure 12. Line driver harmonic distortion vs. temperature

#### **Typical Performance Plots (Cont.)**

Unless otherwise noted, all typical plots are at  $T_A = 25^{\circ}$ C,  $V_{_{CC1}} = 5$  V,  $V_{_{CC2}} = 5$  V, sinusoidal waveform input, signal frequency f = 132 kHz,  $I_{_{Tx-in}} = 250 \ \mu A_{_{PP'}}$  and  $R_{_{ref}} = 24 \ k\Omega$ .

Figure 13. Line driver harmonic distortion vs. frequency for  $R_{ref} = 24 \text{ k}\Omega$

Figure 15. Line driver harmonic distortion vs. Tx-out output voltage

Figure 17. Normalized Rx-PD-out output voltage vs. frequency

Figure 14. Line driver harmonic distortion vs. frequency for  $R_{ref} = 8 \text{ k}\Omega$

Figure 16. Line driver peak harmonic distortion vs. load

Figure 18. RxAMP gain and phase xs. frequency

#### **Test Circuit Diagrams**

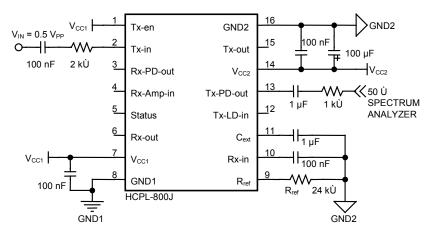

Unless otherwise noted, all test circuits are at  $T_A = 25^{\circ}$ C,  $V_{CC1} = 5$  V,  $V_{CC2} = 5$  V, sinusoidal waveform input, and signal frequency f = 132 kHz.

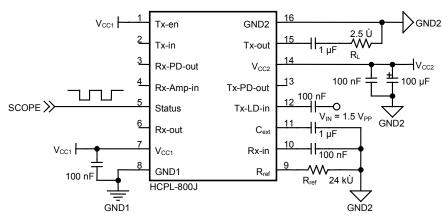

Figure 19. Load detection test circuit

Figure 20. Isolation mode rejection ratio test circuit

Figure 21. Tx-PD-out enable/ disable time test circuit

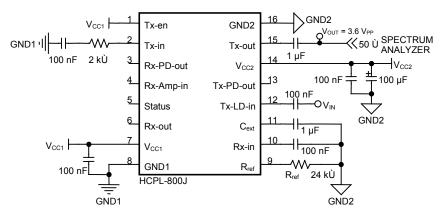

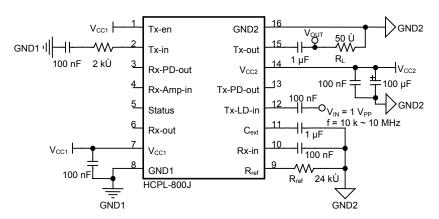

#### Test Circuit Diagrams (Cont.)

Unless otherwise noted, all test circuits are at  $T_A = 25$  °C,  $V_{CC1} = 5$  V,  $V_{CC2} = 5$  V, sinusoidal waveform input, and signal frequency f = 132 kHz.

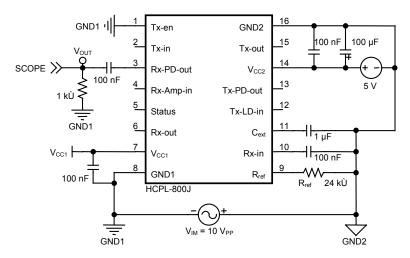

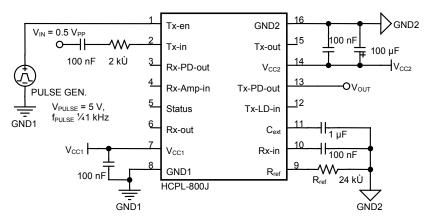

Figure 22. Tx-PD-out harmonic distortion test circuit

Figure 23. Line driver harmonic distortion test circuit

Figure 24. Line driver bandwidth test circuit

## **Applications Information**

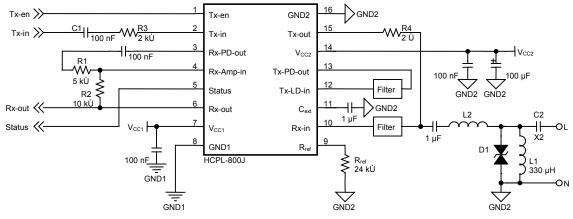

Figure 25. Schematic of HCPL - 800J application for FSK modulation scheme

#### Typical application for FSK modulation scheme

The HCPL-800J is designed to work with various transceivers and can be used with a variety of modulation methods including ASK, FSK and BPSK. Figure 25 shows a typical application in a powerline modem using Frequency Shift Keying (FSK) modulation scheme.

#### Transmitter

The analogue Tx input pin is connected to the modulator via an external coupling capacitor C1 and a series resistor R3 (see Figure 25). Optimal performance is obtained with an input signal of 250  $\mu$ A<sub>pp</sub> E.g., for a modulator with an output signal of 0.5 V<sub>pp</sub> using a coupling capacitor of 100 nF, the optimal series resistor R3 would be 2 k $\Omega$ .

# TX AGC

To ensure a stable and constant output voltage at Tx-PDout, the HCPL-800J includes an Automatic Gain Control (AGC) circuit in the isolated transmit signal path.

This AGC circuit compensates for variations in the input signal level presented at Tx-in and variations in the optical channel over temperature and time. The Tx-PD-out output signal is effectively stabilized for input Tx-in signals of between 150  $\mu$ A<sub>pp</sub> and 250  $\mu$ A<sub>pp</sub> (see Figure 8). The AGC circuit starts to function 10  $\mu$ s after the Tx-en signal is set to logic high. After a period of 180  $\mu$ s the Tx-PD-out signal typically reaches 66% of its steady state level (see Figure 26). To ensure correct operation of the internal circuitry, an external 1  $\mu$ F capacitor needs to be connected from pin 11 to GND2.

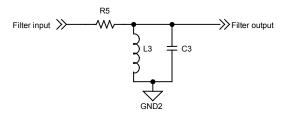

The optical signal coupling technology used in the HCPL-800J transmit path achieves very good harmonic distortion typically HD2 < -50 dB and HD3 < -62 dB, which is usually significantly better than the distortion performance of the modulated input signal. However to meet the requirements of some international EMC regulations it is often necessary to filter the modulated input signal. The optimal position for such a filter is between pins 13 and 12 as shown in Figure 25. A possible band-pass filter topology is shown in Figure 27, some typical values of the components in this filter are listed in Table 1.

Figure 26. Tx-PD-out AGC response time

Figure 27. An example of a band-pass filter for transmit

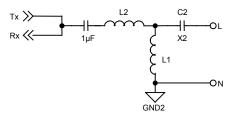

Figure 28. LC coupling network

Table 1. Typical component values for band-pass filter and LC coupling network.

| Carrier         | Band-Pas | s Filter | LC Coupli | LC Coupling |  |  |

|-----------------|----------|----------|-----------|-------------|--|--|

| Frequency (kHz) | L3 (µH)  | C3 (nF)  | L2 (µH)   | C2 (nF)     |  |  |

| 110             | 680      | 3.3      | 15        | 150         |  |  |

| 120             | 680      | 2.7      | 10        | 220         |  |  |

| 132             | 680      | 2.2      | 6.8       | 220         |  |  |

| 150             | 680      | 1.8      | 6.8       | 220         |  |  |

To compensate for the attenuation in the filter, the line driver stage has 6 dB gain. To prevent the line driver output from saturating, it is therefore important to achieve 6 dB of attenuation between Tx-PD-out (pin 13) and Tx-LD-in (pin 12) either by the inherent filter attenuation or by other means.

#### **Transmitter Line Driver**

The line driver is capable of driving powerline load impedances with output signals up to 4  $V_{pp}$ . The internal biasing of the line driver is controlled externally via a resistor  $R_{ref}$  connected from pin 9 to GND2. The optimum biasing point value for modulation frequencies up to 150 kHz is 24 k $\Omega$ . For higher frequency operation with certain modulation schemes, it may be necessary to reduce the resistor value to enable compliance with international regulations.

The output of the line driver is coupled onto the powerline using a simple LC coupling circuit as shown in Figure 28. Refer to Table 1 for some typical component values. Capacitor C2 and inductor L1 attenuate the 50/60 Hz powerline transmission frequency. A suitable value for L1 can range in value from 200  $\mu$ H to 1 mH. To reduce the series coupling impedance at the modulation frequency, L2 is included to compensate the reactive impedance of C2. This inductor should be a low resistive type capable of meeting the peak current requirements. To meet many regulatory requirements, capacitor C2 needs to be an X2 type. Since these types of capacitors typically have a very wide tolerance range of 20%, it is recommended to use as low O factor as possible for the L2/C2 combination. Using a high Q coupling circuit will result in a wide tolerance on the overall coupling impedance, causing potential communication difficulties with low powerline impedances. Occasionally with other circuit configurations, a high Q coupling arrangement is recommend, e.g., C2 less than 100 nF. In this case it is normally used as a compromise to filter out of band harmonics originating from the line driver. This is not required with the HCPL-800J.

Although the series coupling impedance is minimized to reduce insertion loss, it has to be sufficiently large to limit the peak current to the desired level in the worst expected powerline load condition. The peak output current is effectively limited by the total series coupling resistance, which is made up of the series resistance of L2, the series resistance of the fuse and any other resistive element connected in the coupling network.

To reduce power dissipation when not operating in transmit mode the line driver stage is shut down to a low power high impedance state by pulling the Tx-en input (pin 1) to logic low state. The high impedance condition helps minimize attenuation on received signals.

#### Receiver

The received signal from the powerline is often heavily attenuated and also includes high level out of band noise. Receiver performance can be improved by positioning a suitable filter prior to the Rx-in input (pin 10). To counter the inevitable attenuation on the powerline, the HCPL-800J receiver circuit includes a fixed 20 dB front-end gain stage. If desired, this fixed gain can be reduced to unity gain by inserting an impedance of 33 k $\Omega$  in the receiver signal path. It is however recommended to maintain the fixed gain of 20 dB at this position and reduce the overall signal gain elsewhere if required. This configuration will result in the best SNR and IMRR.

The optical isolated Rx signal appears at Rx-PD-out (pin 3). This signal is subsequently AC coupled to the final gain stage via a capacitor.

The final gain stage consists of an op-amp configured in an inverting configuration and DC biased at 2.27 V. The actual gain of this gain stage is user programmable with external resistors R1 and R2 as shown in Figure 25. The signal output at Rx-out (pin 6) is buffered and may be directly connected to the demodulator or ADC, using AC coupling if required.

#### **Internal Protection and Sensing**

The HCPL-800J includes several sensing and protection functions to ensure robust operation under wide ranging environmental conditions.

The first feature is the  $V_{_{CC2}}$  Under Voltage Detection (UVD). In the event of  $V_{_{CC2}}$  dropping to a voltage less than 4 V, the output status pin is switched to a logic low state.

The next feature is the over-temperature shutdown. This particular feature protects the line driver stage from over-temperature stress. Should the IC junction temperature reach a level above 130°C, the line driver circuit is shut down, simultaneously the output of Status (pin 5) is pulled to the logic low state.

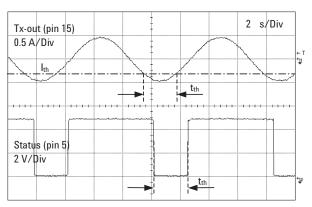

The final feature is load detection function. The powerline impedance is quite unpredictable and varies not just at

different connection points but is also time variant. The HCPL-800J includes a current sense feature, which may be utilized to feedback information on the instantaneous powerline load condition. Should the peak current reach a level greater than 0.6  $A_{pp}$  the output of Status pin is pulled to a logic low state for the entire period the peak current exceeds -0.3 A, as shown in Figure 29. Using the period of the pulse together with the known coupling impedance, the actual powerline load can be calculated. Table 2 shows the logic output of the Status pin.

#### **External Transient Voltage Protection**

To protect the HCPL-800J from high voltage transients caused by power surges and disconnecting/connecting the modem, it is necessary to add an external 6.8 V bidirectional transient voltage protector (as component D1 shown in Figure 25).

Additional protection from powerline voltage surges can be achieved by adding an appropriate Metal Oxide Varistor (MOV) across the powerline terminals after the fuse.

|                  | Normal | $V_{cc2} < 4 V$ | Over-Temperature | I <sub>Tx-out</sub> < -0.3 A |

|------------------|--------|-----------------|------------------|------------------------------|

| Receiver Mode    | High   | Low             | -                | -                            |

| Transmitter Mode | High   | Low             | Low              | Low (pulsed)                 |

Figure 30. A simple low cost non-isolated power supply

#### VCC2 Power Supply Requirements

The recommended voltage regulator to supply  $V_{cc2}$  is a low cost 78L05 or equivalent. To minimize harmonic distortion, it is recommended to connect a tantalum decoupling capacitor of at least 10  $\mu$ F together with a 100 nF ceramic capacitor in parallel. The capacitors should be positioned as close as possible to the supply input pin. The supply voltage for the regulator can be supplied from the system level power supply transformer (powerline side winding). Alternatively, the supply can be derived directly from the powerline via a simple low cost circuit as shown in Figure 30.

#### **Thermal Considerations**

The high efficiency line driver used in the HCPL-800J ensures minimum internal power dissipation, even for high peak output currents. Despite this, operating the line driver continuously with high output currents at elevated ambient temperatures can cause the peak junction temperature to exceed 125°C and/or resulting in the triggering of the thermal protection.

To prevent this from happening, when operating the line driver continuously with high output currents, an ambient temperature derating factor needs to be applied. A typical derating curve is shown in Figure 31.

In this case the assumption is that the transmitter is operating continuously in still air with a typical 2-layer Printed-Circuit Board (PCB). However, it should be noted that operating the transmitter discontinuously for short periods of time will allow lower derating or even no derating at all. Conversely operating the line driver continuously with a poor PCB layout and/or with restricted air convection could result in the requirement for a larger derating factor.

Figure 31. Power derating vs. temperature

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2009 Avago Technologies. All rights reserved. Obsoletes 5989-0402EN AV02-0413EN - August 28, 2009