## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# **ST-NXP Wireless**

#### **IMPORTANT NOTICE**

Dear customer,

As from August 2<sup>nd</sup> 2008, the wireless operations of NXP have moved to a new company, ST-NXP Wireless.

As a result, the following changes are applicable to the attached document.

- Company name Philips Semiconductors is replaced with ST-NXP Wireless.

- Copyright the copyright notice at the bottom of each page "© Koninklijke Philips Electronics N.V. 200x. All rights reserved", shall now read: "© ST-NXP Wireless 200x All rights reserved".

- Web site <a href="http://www.semiconductors.philips.com">http://www.semiconductors.philips.com</a> is replaced with <a href="http://www.stnwireless.com">http://www.stnwireless.com</a>

- Contact information the list of sales offices previously obtained by sending an email to <u>sales.addresses@www.semiconductors.philips.com</u>, is now found at <a href="http://www.stnwireless.com">http://www.stnwireless.com</a> under Contacts.

If you have any questions related to the document, please contact our nearest sales office. Thank you for your cooperation and understanding.

ST-NXP Wireless

### **TEA5764UK**

FM radio + RDS

Rev. 02 — 9 August 2005

**Product data sheet**

The TEA5764UK is a single chip electronically tuned FM stereo radio with Radio Data System (RDS) and Radio Broadcast Data System (RBDS) demodulator and RDS/RBDS decoder for portable application with fully integrated IF selectivity and demodulation.

The radio is completely adjustment free and only requires a minimum of small and low cost external components.

The radio can tune to the European, US and Japanese FM bands. It has a low power consumption and can operate at a low supply voltage.

#### 2. Features

- Chip scale package

- High sensitivity due to integrated low noise RF input amplifier

- FM mixer for conversion of the US/Europe (87.5 MHz to 108 MHz) and Japanese FM band (76 MHz to 90 MHz) to IF

- Preset tuning to receive Japanese TV audio up to 108 MHz

- Auto search tuning, raster 100 kHz

- RF automatic gain control circuit

- LC tuner oscillator operating with low cost fixed chip inductors

- Fully integrated FM IF selectivity

- Fully integrated FM demodulator; no external discriminator

- Crystal oscillator at 32768 Hz, or external reference frequency at 32768 Hz

- PLL synthesizer tuning system

- IF counter; 7-bit output via the I<sup>2</sup>C-bus

- Level detector: 4-bit level information output via the I<sup>2</sup>C-bus

- Soft mute: signal dependent mute function

- Mono/stereo blend: gradual change from mono to stereo, depending on signal

- Adjustment-free stereo decoder

- Autonomous search tuning function

- Standby mode

- MPX output

- One software programmable port

- Fully integrated RDS/RBDS demodulator in accordance with EN50067

- RDS/RBDS decoder with memory for two RDS data blocks provides block synchronization and error correction; block data and status information are available via the I<sup>2</sup>C-bus

- Audio pause detector

#### 3. Applications

FM stereo radio

#### 4. Quick reference data

#### Table 1: Electrical parameters general

The listed parameters are valid when a crystal is used that meets the requirements as stated in <u>Table 46</u>; All RF input values are defined in potential difference, except when EMF is explicitly stated.

| Symbol                  | Parameter                                                    | r Conditions                                                                                                                                                                    |            | Тур  | Max       | Unit |

|-------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----------|------|

| Supplies                |                                                              |                                                                                                                                                                                 |            |      |           |      |

| V <sub>CCA</sub>        | analog supply voltage                                        |                                                                                                                                                                                 | 2.5        | 2.7  | 3.3       | V    |

| I <sub>CCA</sub>        | analog supply current                                        | $V_{CCA} = 2.5 \text{ V to } 3.3 \text{ V}$                                                                                                                                     |            |      |           |      |

|                         |                                                              | operating mode                                                                                                                                                                  | 12         | 13.7 | 16        | mA   |

|                         |                                                              | Standby mode                                                                                                                                                                    | 0          | 0.1  | 1         | μΑ   |

| V <sub>CCD</sub>        | digital supply voltage                                       |                                                                                                                                                                                 | 2.5        | 2.7  | 3.3       | V    |

| I <sub>CCD</sub>        | digital supply current                                       | V <sub>CCD</sub> = 2.5 V to 3.3 V                                                                                                                                               |            |      |           |      |

|                         |                                                              | operating mode                                                                                                                                                                  | 0.3        | 0.7  | 1.5       | mA   |

|                         |                                                              | Standby mode                                                                                                                                                                    | 1          | 15   | 22.5      | μΑ   |

| Reference               | voltage                                                      |                                                                                                                                                                                 |            |      |           |      |

| $V_{VREFDIG}$           | digital reference voltage for I <sup>2</sup> C-bus interface |                                                                                                                                                                                 | 1.65       | 1.8  | $V_{CCD}$ | V    |

| I <sub>VREFDIG</sub>    | digital reference supply current                             | operating mode; $V_{VREFDIG} = 1.65 \text{ V to } V_{CCD}$                                                                                                                      | 0          | 0.5  | 1         | μΑ   |

| General                 |                                                              |                                                                                                                                                                                 |            |      |           |      |

| f <sub>i(FM)</sub>      | FM input frequency                                           |                                                                                                                                                                                 | 76         | -    | 108       | MHz  |

| T <sub>amb</sub>        | ambient temperature                                          |                                                                                                                                                                                 | -40        | -    | +85       | °C   |

| FM and RD               | S overall system paramete                                    | ers                                                                                                                                                                             |            |      |           |      |

| V <sub>sens</sub> (EMF) | sensitivity EMF value voltage                                | $f_{RF}$ = 76 MHz to 108 MHz;<br>$\Delta f$ = 22.5 kHz; $f_{mod}$ = 1 kHz;<br>(S+N)/N = 26 dB; $TC_{deem}$ = 75 $\mu$ s;<br>A-weighting filter;<br>$B_{aud}$ = 300 Hz to 15 kHz |            | 2.9  | 4.4       | μV   |

| IP3 <sub>in</sub>       | in-band 3rd-order intercept point                            | $\Delta f_1$ = 200 kHz; $\Delta f_2$ = 400 kHz;<br>$f_{tune}$ = 76 MHz to 108 MHz;<br>$RF_{agc}$ = off                                                                          | 78         | 87   | -         | dΒμV |

| IP3 <sub>out</sub>      | out-of-band 3rd-order intercept point                        | $\Delta f_1 = 4$ MHz; $\Delta f_2 = 8$ MHz;<br>$f_{tune} = 76$ MHz to 108 MHz;<br>$RF_{agc} = off$                                                                              | 87         | 93   | -         | dBμV |

| S                       | selectivity                                                  | f <sub>tune</sub> = 76 MHz to 108 MHz                                                                                                                                           | <u>[1]</u> |      |           |      |

|                         |                                                              | high-side; $\Delta f = +200 \text{ kHz}$                                                                                                                                        | 39         | 43   | -         | dB   |

|                         |                                                              | low-side; $\Delta f = -200 \text{ kHz}$                                                                                                                                         | 32         | 36   | -         | dB   |

| $V_{VAFL}$              | left audio output voltage on pin VAFL                        | $V_{RF}$ = 1 mV; L = R; $\Delta f$ = 22.5 kHz; $f_{mod}$ = 1 kHz; no pre-emphasis; $TC_{deem}$ = 75 $\mu s$                                                                     | 55         | 66   | 75        | mV   |

TEA5764UK\_2

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

The listed parameters are valid when a crystal is used that meets the requirements as stated in <u>Table 46</u>; All RF input values are defined in potential difference, except when EMF is explicitly stated.

| Symbol            | Parameter                                 | Conditions                                                                                                                                                                          | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $V_{VAFR}$        | right audio output voltage<br>on pin VAFR | $V_{RF}$ = 1 mV; L = R; $\Delta f$ = 22.5 kHz;<br>$f_{mod}$ = 1 kHz; no pre-emphasis;<br>$TC_{deem}$ = 75 $\mu$ s                                                                   | 55  | 66  | 75  | mV   |

| (S+N)/N(m)        | maximum signal-to-noise ratio, mono       | $V_{RF}$ = 1 mV; $\Delta f$ = 22.5 kHz; L = R;<br>$f_{mod}$ = 1 kHz; de-emphasis = 75 $\mu$ s;<br>$B_{AF}$ = 300 Hz to 15 kHz; A-weighting<br>filter                                | 54  | 57  | -   | dB   |

| (S+N)/N(s)        | maximum signal-to-noise ratio, stereo     | $V_{RF}$ = 1 mV; $\Delta f$ = 67.5 kHz; L = R;<br>$f_{mod}$ = 1 kHz; $\Delta f_{pilot}$ = 6.75 kHz;<br>de-emphasis = 75 $\mu$ s; $B_{AF}$ = 300 Hz<br>to 15 kHz; A-weighting filter | 50  | 54  | -   | dB   |

| $\alpha_{	t cs}$  | channel separation                        | MST = 0; R = 1 and L = 0 or R = 0 and L = 1; $V_{RF}$ = 30 $\mu$ V; increasing RF input level                                                                                       | 27  | 33  | -   | dB   |

| THD               | total harmonic distortion                 | $V_{RF}$ = 1 mV; $\Delta f$ = 75 kHz;<br>$f_{mod}$ = 1 kHz; DTC = 0; $B_{aud}$ = 300 Hz<br>to 15 kHz; A-weighting filter; mono;<br>L = R; no pilot deviation                        | -   | 0.4 | 0.9 | %    |

| V <sub>sens</sub> | RDS sensitivity EMF value                 | $\Delta f$ = 22.5 kHz; $f_{AF}$ = 1 kHz; L = R;<br>SYM1 = 0 and SYM0 = 0; average<br>over 2000 blocks; block quality<br>rate $\geq$ 95 %; $\Delta f_{RDS}$ = 2 kHz                  | -   | 17  | 30  | μV   |

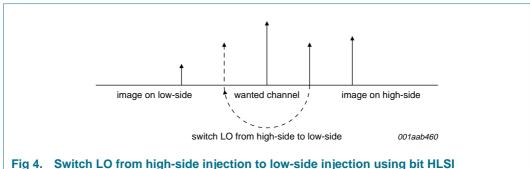

<sup>[1]</sup> Low-side and high-side selectivity can be measured by changing the mixer LO injection from high-side to low-side.

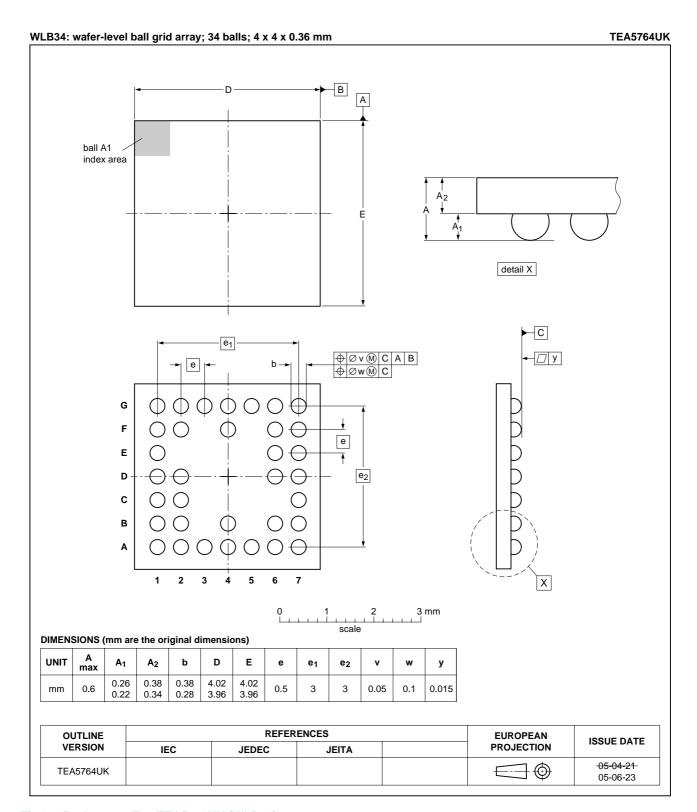

#### 5. Ordering information

**Table 2: Ordering information**

| Type number | Package | Package                                                            |           |  |  |  |  |  |  |  |

|-------------|---------|--------------------------------------------------------------------|-----------|--|--|--|--|--|--|--|

|             | Name    | ame Description Version                                            |           |  |  |  |  |  |  |  |

| TEA5764UK   | WLB34   | wafer-level ball grid array; 34 balls; $4 \times 4 \times 0.36$ mm | TEA5764UK |  |  |  |  |  |  |  |

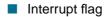

# **Block diagram**

9

Fig 1. Block diagram

Product data sheet

**Rev. 02**

9 August 2005

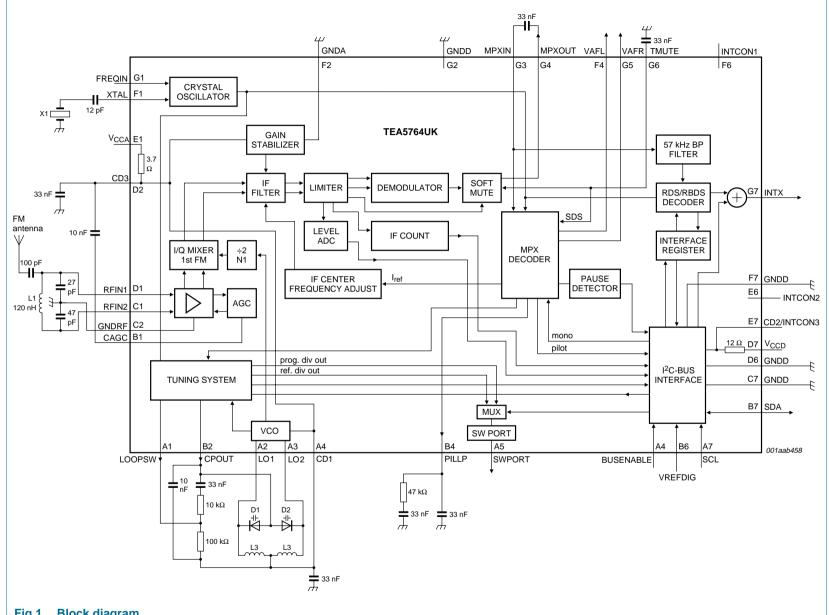

#### 7.1 Pinning

#### 7.2 Pin description

Table 3: Pin description

| Symbol           | Ball | Description                                                |

|------------------|------|------------------------------------------------------------|

| LOOPSW           | A1   | synthesizer PLL loop filter switch output                  |

| CPOUT            | B2   | charge pump output of synthesizer PLL                      |

| LO1              | A2   | local oscillator coil connection 1                         |

| LO2              | A3   | local oscillator coil connection 2                         |

| CD1              | A4   | VCO supply decoupling capacitor                            |

| PILLP            | B4   | pilot PLL loop filter                                      |

| SWPORT           | A5   | software programmable port output                          |

| BUSENABLE        | A6   | I <sup>2</sup> C-bus enable input                          |

| VREFDIG          | B6   | digital reference voltage for I <sup>2</sup> C-bus signals |

| SCL              | A7   | I <sup>2</sup> C-bus clock line input                      |

| SDA              | B7   | I <sup>2</sup> C-bus data line input and output            |

| n.c.             | -    | not connected                                              |

| GNDD             | C7   | digital ground                                             |

| GNDD             | D6   | digital ground                                             |

| V <sub>CCD</sub> | D7   | digital supply voltage                                     |

| CD2/INTCON3      | E7   | internally connected                                       |

| n.c.             | -    | not connected                                              |

| INTCON2          | E6   | internally connected; leave open                           |

| GNDD             | F7   | digital ground                                             |

| INTX             | G7   | interrupt flag output                                      |

| n.c.             | -    | not connected                                              |

| INTCON1          | F6   | internally connected; leave open                           |

| Symbol           | Ball | Description                                                                                  |

|------------------|------|----------------------------------------------------------------------------------------------|

| TMUTE            | G6   | soft mute time-constant capacitor                                                            |

| VAFR             | G5   | right audio output                                                                           |

| VAFL             | F4   | left audio output                                                                            |

| MPXOUT           | G4   | FM demodulator MPX output                                                                    |

| MPXIN            | G3   | MPX decoder and RDS decoder MPX input                                                        |

| GNDD             | G2   | digital ground; this pin has an internal pull-down resistor of 10 $\text{k}\Omega$ to ground |

| n.c.             | -    | not connected                                                                                |

| GNDA             | F2   | analog ground                                                                                |

| n.c.             | -    | not connected                                                                                |

| FREQIN           | G1   | 32.768 kHz reference frequency input                                                         |

| XTAL             | F1   | crystal oscillator input                                                                     |

| V <sub>CCA</sub> | E1   | analog supply voltage                                                                        |

| CD3              | D2   | V <sub>CCA</sub> decoupling capacitor                                                        |

| RFIN1            | D1   | RF input 1                                                                                   |

| RFIN2            | C1   | RF input 2                                                                                   |

| GNDRF            | C2   | RF ground                                                                                    |

| CAGC             | B1   | RF AGC time-constant capacitor                                                               |

| n.c.             | -    | not connected                                                                                |

#### 8. Functional description

#### 8.1 Low noise RF amplifier

The LNA input impedance together with the LC RF input circuit defines an FM band filter. The gain of the LNA is controlled by the RF AGC circuit.

#### 8.2 FM I/Q mixer

FM quadrature mixer converts FM RF (76 MHz to 108 MHz) to IF.

#### 8.3 VCO

The varactor tuned LC VCO provides the Local Oscillator (LO) signal for the FM quadrature mixer. The VCO frequency range is 150 MHz to 217 MHz.

#### 8.4 Crystal oscillator

The crystal oscillator can operate with a 32.768 kHz clock crystal. The oscillator can be overridden via the FREFIN pin. When the FREFIN pin is used the oscillator is clocked externally by a 32.768 kHz signal. Selection between a reference clock or a reference crystal can be done via the I<sup>2</sup>C-bus. When a crystal is connected the FREFIN pin must be left open-circuit, and when pin FREFIN is used a crystal may not be connected. It is not possible to connect a crystal and apply a frequency via the FREFIN pin in the same application.

The crystal oscillator generates the reference frequency for the following:

- Reference frequency divider for synthesizer PLL

- Timing for the IF counter

- Timing for the pause detector

- Free running frequency adjustment of the stereo decoder VCO

- Centre frequency for adjustment of the IF filters

- Clock frequency of the RDS/RBDS decoder

#### 8.5 PLL tuning system

The PLL synthesizer tuning system is suitable to operate with a 32.768 kHz reference frequency generated by the crystal oscillator or a reference clock of 32.768 kHz fed into the TEA5764UK. To tune the radio to the required frequency requires the PLL word to be calculated and then programmed to the register. The PLL word is 14 bits long; see Table 20 and Table 21. Calculation of this 14-bit word can be done as follows.

Formula for high-side injection:

$$N_{DEC} = \frac{4 \times (f_{RF} + f_{IF})}{f_{ref}} \tag{1}$$

Formula for low-side injection:

$$N_{DEC} = \frac{4 \times (f_{RF} - f_{IF})}{f_{ref}} \tag{2}$$

where:

N<sub>DEC</sub> = decimal value of PLL word

f<sub>RF</sub> = wanted tuning frequency (Hz)

f<sub>IF</sub> = intermediate frequency of 225 kHz

f<sub>REFS</sub> = the reference frequency of 32.768 kHz

Example for receiving a channel at 100.1 MHz:

$$N_{DEC} = \frac{4 \times (100.1 \times 10^6 + 225 \times 10^3)}{32768} = 12246.704$$

(3)

The result found using <u>Equation 1</u> or <u>Equation 2</u> must always be rounded to the lowest integer value. If rounded down to the lowest integer value of  $N_{DEC} = 12246$ , the PLL word becomes 2FD6h.

This value can be written to register FRQSETLSB or FRQSETMSB via the I<sup>2</sup>C-bus and the IC will then either start an autonomous search at this frequency or go to a preset channel at this frequency. When the application is built according to the block diagram shown in <a href="Figure 1">Figure 1</a>, and with the preferred components, the PLL will settle to the new frequency within 5 ms. The most accurate tuning is accomplished when a search is followed by a preset to the same frequency.

The PLL is triggered by writing to any one of the bytes FRQSETMSB, FRQSETLSB, TNCTRL1, TNCTRL2, TESTBITS, TESTMODE.

Accurate validation of the PLL locking on the new frequency can take 2 ms to 10 ms. When a lock is detected, bit LD is set.

#### 8.6 Band limits

The TEA5764UK can be switched either to the Japanese FM band or to the US/Europe FM band. Setting bit BLIM to logic 0 the band range is 87.5 MHz to 108 MHz; setting bit BLIM to logic 1 selects the Japanese band range of 76 MHz to 90 MHz.

#### 8.7 RF AGC

The RF AGC (or wideband AGC) prevents overloading and limits the amount of intermodulation products created by strong adjacent channels. The RF AGC is on by default and can be turned off via the I<sup>2</sup>C-bus.

The TEA5764UK also has an in-band AGC to prevent overloading by the wanted channel. The in-band AGC is always turned on.

#### 8.8 Local or long distance receive

If bit LDX = 1, the LNA gain is reduced by 6 dB to prevent distortion when a transmitter is very near. If bit LDX = 0, the LNA gain is normal to receive long distance (DX) stations.

#### 8.9 IF filter

A fully integrated IF filter is built-in.

#### 8.10 FM demodulator

The FM quadrature demodulator has an integrated resonator to perform the phase shift of the IF signal.

#### 8.11 IF counter

The received signal is mixed to produce an IF of 225 kHz. The result of the mixing is counted. A good IF count result indicates that the radio is tuned to a valid channel instead of an image or a channel with much interference. The IF counter outputs a 7-bit count result via the I<sup>2</sup>C-bus. The IF counter is continuously active and can be read at any time via the I<sup>2</sup>C-bus. It also activates a flag when the IF count result is outside the IF count valid result window; see Section 9.1.4.4.

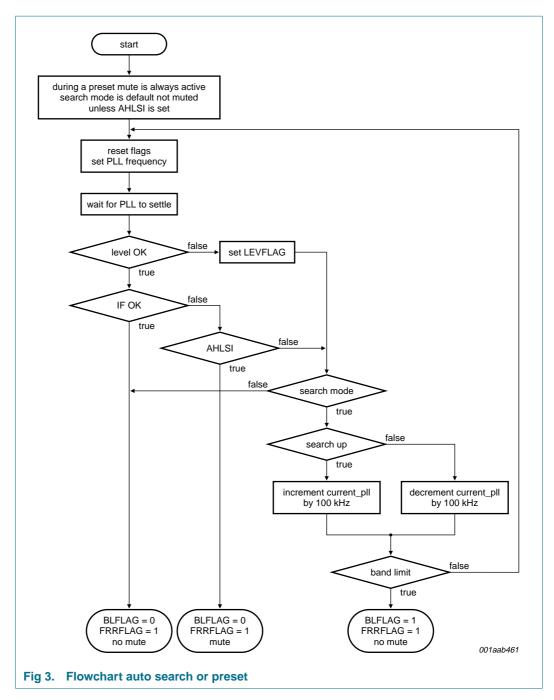

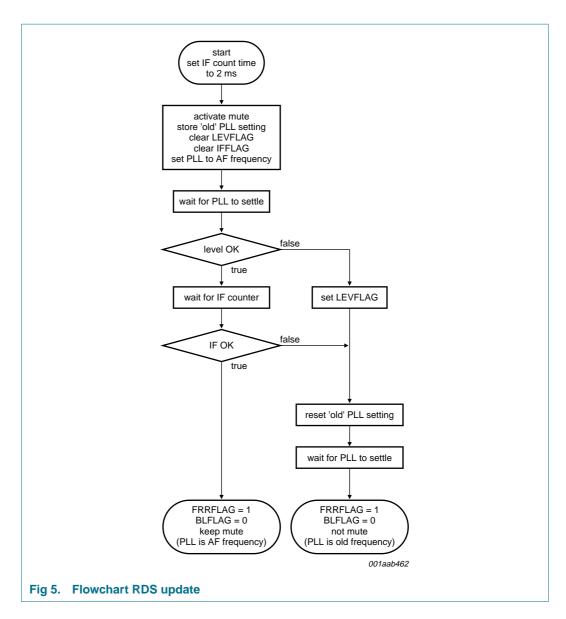

Before a tuning cycle is initiated the IF count period can be set to 2 ms or to 15.6 ms by bit IFCTC. When the IF count period is set to 2 ms, initiating the tuning algorithm with a preset (bit SM = 0) will always give an RDS update as shown in Section 8.22.1. In case the IF count time is set to 15.6 ms, the tuning flowchart illustrated in Figure 3 is used. Once tuned, the IF count period is always 15.6 ms.

#### 8.12 Voltage level generator and analog-to-digital converter

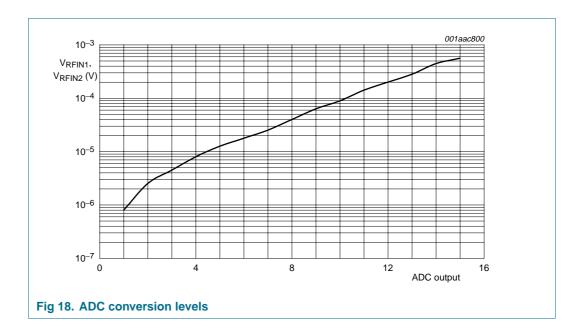

The voltage level indicates the field strength received by the antenna. The voltage level is analog-to-digital converted to a 4-bit word and output via the I<sup>2</sup>C-bus. The ADC level is continuously active and can be read at any time via the I<sup>2</sup>C-bus. It also activates a flag when the voltage level falls below a predefined selectable threshold. Bit LHSW allows either large or small hysteresis steps to be chosen; see Table 24 and Section 9.1.4.5.

When the ADC level is set to 3, its minimum value, the search algorithm will only stop at channels having a RF level higher than, or equal to, ADC level 3. After completing the search algorithm and being tuned to a station, due to hysteresis the effective limit will be set to 0. This means that the continuous ADC level check will never set the LEVFLAG.

#### 8.13 Mute

#### 8.13.1 Soft mute

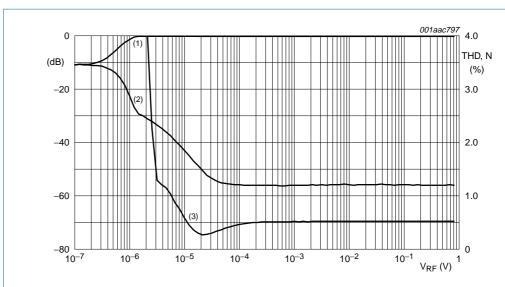

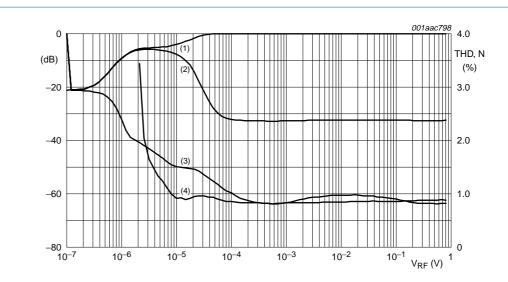

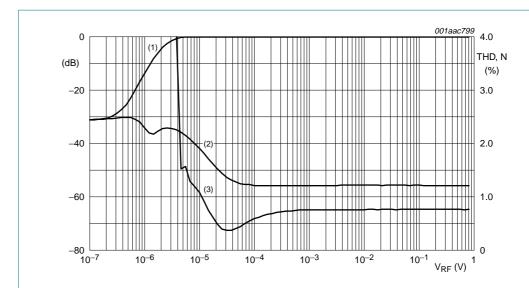

The low-pass filtered voltage level drives the soft mute attenuator at low RF input levels: the audio output is faded and hence also the noise (see graphs referenced 1 in <u>Figure 15</u> and <u>Figure 17</u>).

The soft mute function can also be switched off via the I<sup>2</sup>C-bus, using bit SMUTE.

#### **8.13.2** Hard mute

The audio outputs VAFL and VAFR can be hard-muted by bit MU in byte TNCTRL2, which means that they are put into 3-state. This can also be done by setting bits Left Hard Mute (LHM) or Right Hard Mute (RHM) in byte TESTBITS, which allows either one or both channels to be muted and forces the TEA5764UK to mono mode. When the TEA5764UK is in Standby mode the audio outputs are hard-muted.

#### 8.13.3 Audio frequency mute

The audio signal is muted by setting bit AFM of the TNCTRL1 register to logic 1. In the soft mute attenuator the audio signal is blocked and so pins VAFL and VAFR will be at their DC biasing point with no signal.

The audio is automatically muted during an RDS update as shown in the flowchart of <u>Figure 3</u>. When the audio must be muted during Search mode, it is done by setting bit AFM to logic 1 before the search action and resetting it to logic 0 afterwards.

Setting bit AFM to logic 0 stops the RDS data.

#### 8.14 MPX decoder

The PLL stereo decoder is adjustment free. It can be switched to mono via the I<sup>2</sup>C-bus.

#### 8.15 Signal dependent mono/stereo blend (stereo noise cancellation)

If the RF input level decreases, the MPX decoder blends from stereo to mono to limit the output noise. The continuous mono-to-stereo blend can also be programmed via the  $I^2C$ -bus to an RF level dependent switched mono-to-stereo transition. Stereo noise cancellation can be switched off via the  $I^2C$ -bus by bit SNC.

#### 8.16 Software programmable port

One software programmable port (CMOS output) can be addressed via the I<sup>2</sup>C-bus:

Bit SWPM = 1, the software port functions as the output for the FRRFLAG.

Bit SWPM = 0, the software port outputs bit SWP of the registers.

In Test mode the software port outputs signals according to <u>Table 27</u>. Test mode is selected, setting bit TM of byte TESTMODE to logic 1.

The software port cannot be disabled by the PUPD bits; see Section 8.17.

#### 8.17 Standby mode

The radio can be put into Standby mode by the Power-Up / Power-Down (PUPD) bits. The RDS part can be turned off separately or both the RDS and the FM part can be turned off. The TEA5764UK is still accessible via the I<sup>2</sup>C-bus but takes only a low power from the supply, in Standby mode, the audio outputs are hard-muted.

#### 8.18 Power-on reset

After startup of  $V_{CCA}$  and  $V_{CCD}$  a power-on reset circuit will generate a reset pulse and the registers will be set to their default values. The power-on reset is effectively generated by  $V_{CCD}$ .

After a power-on reset the TEA5764UK is in Standby mode and the PUPD bits are set to logic 0. After a power-on reset the registers are reset to their default value, except for byte12R to byte19R and flags DAVFLG, LSYNCFLG and PDFLAG. To reset these, the RDS part must be turned on by setting PUPD. After setting PUPD to logic 1, it will take 0.9 ms to start-up the TEA5764UK and set these registers to their default value.

The power supplies can be switched on in any order.

When the supply voltage  $V_{CCA}$  and  $V_{CCD}$  are at 0 V, all I/Os, the audio outputs and the reference clock input are high-ohmic.

#### **8.19 RDS/RBDS**

#### 8.19.1 RDS/RBDS demodulator

A fully integrated RDS/RBDS demodulator which uses the reference frequency (32.678 Hz) of the PLL synthesizer tuning system. The RDS demodulator recovers and regenerates the continuously transmitted RDS or RBDS data stream of the multiplex signal (MPXRDS) and provides the signals clock (RDCL), data (RDDA) for further processing by the integrated RDS decoder.

#### 8.19.2 RDS data and clock direct

The RDS demodulator retrieves the RDS data and clock signals, this data can be put directly onto pins VAFL and VAFR by setting bit RDSCDA to logic 1.

10 of 64

#### 8.19.2.1 RDS/RBDS decoder

The RDS decoder provides block synchronization, error correction and flywheel function for reliable extraction of RDS or RBDS block data. Different modes of operation can be selected to fit different application requirements. Availability of new data is signalled by bit DAVFLG and output pin INTX which generates an interrupt. Up to two blocks of data and status information are available via the  $I^2C$ -bus in a single transmission.

The behavior of the DAVFLG is described in Section 10.

#### 8.20 Audio pause detector

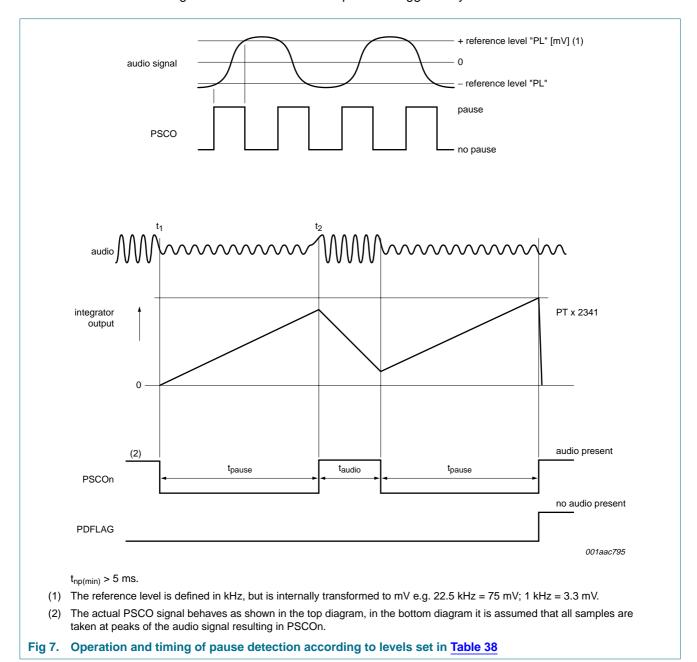

The audio pause detector monitors the audio modulation for pauses and responds to low levels. The modulation threshold can be adjusted in 4 steps of 4 dB by control bits PL[1:0]. The minimum time for detecting a pause can be adjusted by control bits PT[1:0] as shown in <u>Table 38</u>. When a pause occurs, flag PDFLAG is set to logic 1 and a hardware interrupt is generated; see <u>Section 9.1.4.6</u>.

#### 8.21 Auto search and Preset mode

In Search mode the TEA5764UK can search channels automatically (see Figure 3).

Before starting a search or a preset, the INTMSK register must be reset and only the FRRMSK must be set. This allows the microprocessor to be interrupted only when the search or preset algorithm is ready.

#### 8.21.1 Search mode

Search mode is initiated by setting bit SM in byte FRQSETMSB to logic 1. The search direction is set by bit SUD; SUD = 0 (search down), bit SUD = 1 (search up). The tuner starts searching at the frequency set in bytes FRQSETLSB and FRQSETMSB. The Search Stop Level (SSL) bits define the field strength level at which a desired channel is detected. The tuner will stop on a channel with a field strength equal to or higher than this reference level and then checks the IF frequency; when both are valid, the search stops (Note that this depends on bit AHLSI described in <a href="Figure 3">Figure 3</a>). If the level check or the IF-count fails, the search continues. If no channels are found, the TEA5764UK stops searching when it has reached the band limit, setting the BLFLAG HIGH. A search always stops when the FRRFLAG is set and on the occurrence of a hardware interrupt, this procedure is shown in <a href="Figure 3">Figure 3</a>.

The search algorithm can stop at a frequency that is offset from the IF by up to a maximum of 12 kHz. The maximum offset can be limited to 8 kHz by applying a preset. For optimum tuning, it is recommended that a preset is applied after a search and when the found frequency has an offset that is above 8 kHz.

After this interrupt the TEA5764UK will not update the tuner registers for a period of 15 ms. The state of the TEA5764UK can be checked by reading the bytes of INTFLAG, FRQCHKMSB, FRQCHKLSB, TNCTRL1 and TNCTRL2. <u>Table 4</u> shows the possible states of these registers after an auto search.

Table 4: Tuner truth table [1]

| IFFLAG | BLFLAG | FRRFLAG | Comment                                                                                                                                                                                                     |

|--------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0       | if pin INTX has gone LOW and only IFMSK, FRRMSK and BLMSK were set then this cannot occur                                                                                                                   |

| 0      | 0      | 1       | channel found during search / preset; FRRMSK set                                                                                                                                                            |

| 0      | 1      | 0       | not a valid state                                                                                                                                                                                           |

| 0      | 1      | 1       | a valid channel found and the band limit has been reached during a search; BLMSK or FRRMSK set                                                                                                              |

| 1      | 0      | 0       | not a valid state                                                                                                                                                                                           |

| 1      | 0      | 1       | a preset or search has occurred but the wanted channel has a valid RSSI level but fails the IF count when AHLSI was set to logic 1; HLSI must be toggled and a new PLL value must be programmed; FRRMSK set |

| 1      | 1      | 0       | not a valid state                                                                                                                                                                                           |

| 1      | 1      | 1       | band limit is reached during search; no valid channel found;<br>BLMSK or FRRMSK set                                                                                                                         |

<sup>[1]</sup> This table is valid until 30.6 ms after the tuning cycle has completed. It shows the outcome of the flag register when a read is done after pin INTX goes LOW on condition that no mask bit other than FRRMSK is set.

#### 8.21.2 Preset mode

A preset occurs by setting bit SM to logic 0 and writing a frequency to byte FRQSETMSB. The tuner jumps to the selected frequency and sets the FRRFLAG when it is ready.

After this interrupt the TEA5764UK will not update the tuner registers for a period of 15 ms. The state of the TEA5764UK can be checked by reading registers: INTFLAG, FRQCHKLSB, FRQCHKMSB, TNCTRL1 and TNCTRL2. Table 4 shows the possible states after a preset.

#### 8.21.3 Auto high-side and low-side injection stop switch

When a channel is searched or a preset is done, reception can sometimes improve when injection is done at the other side of the wanted channel.

The TEA5764UK has bit HLSI which toggles the injection of the local oscillator from high-side (bit HLSI = 1) to low-side (bit HLSI = 0). When bit HLSI is toggled, a new PLL setting must be sent to the TEA5764UK.

When bit AHLSI is set to logic 1, the search / preset algorithm will stop after a channel has a valid RSSI level check but fails the IF count. The microprocessor can now respond by toggling the HLSI switch and sending a new PLL value to the tuner.

#### 8.21.4 Muting during search or preset

During a preset the tuner is always muted and this is implemented by the algorithm.

A search is not muted by default unless bit AFM = 1 or bit AHLSI = 1.

When bit AHLSI = 1 and the tuner stopped during a preset or a search because of a wrong IF count, the tuner stays muted; this allows the microprocessor to switch from the high to low setting quietly and wait for the new result.

The tuner is always muted if bit AFM = 1 and is independent of a search or a preset. A search can be muted by setting bit AFM to logic 1 before a search is initiated and resetting it to logic 0 when the tuner is ready (only set bit FRRMSK when initiating a search or preset).

All these mute actions are done by blocking the audio signal inside the soft mute attenuator, the audio output will keep its DC level and stay low-ohmic i.e. 50  $\Omega$  (a hard mute set by bit MU will cause a plop).

#### 8.22 RDS update/alternative frequency jump

A channel which transmits RDS data can have alternative channels which have the same information. These alternative channel frequencies are in the RDS data, so the microprocessor can read the alternative frequencies and store them in a memory.

The tuner can perform an RDS update. This is very similar to a preset, but with a 2 ms IF count time. The tuner will jump to the alternative frequency and check the level and the IF count using a 2 ms count time. When the RSSI level check is above the specified level and the IF count result is within the limits, then the tuner will stay at the alternative frequency and stay muted, the microprocessor can now decide what to do. If the alternative frequency is not valid it will jump back to the frequency it came from.

The algorithm will finish with the FRRFLAG being set and an interrupt is generated. After this interrupt the TEA5764UK will not measure the IF count for a period of 15 ms. 15 ms after completing a RDS jump, a measurement of the IF count will start and hence the IF count result and the IFFLAG will be updated 30.6 ms after completing the algorithm. The level measurement will start immediately after the tuning algorithm, so the LEVFLAG will be updated 500  $\mu$ s after the algorithm. The state of the TEA5764UK can be checked by reading registers INTFLAG, FRQCHKLSB, FRQCHKMSB, IFCHK and LEVCHK. Table 5 shows the possible states after an auto search, Figure 5 is a flowchart showing how the RDS is updated.

#### 8.22.1 Muting during RDS update

An RDS update (AF jump) is always muted. There are two possibilities for leaving the algorithm:

- The tuner jumps to an alternative frequency which is not valid (according to the specified SSL limit and fixed IF counter limits) and jumps back, then it will automatically unmute.

- Or the tuner jumps to a valid alternative frequency and stays there. Now it does not

unmute. The microprocessor can unmute or it keeps the tuner muted and can check

for the presence of RDS data. The valid way to unmute is to apply a preset to the

current frequency (an IF count time of 15.6 ms is used at preset, which gives a more

accurate IF count result than the result obtained by the AF jump, where 2 ms is used).

Table 5: RDS update truth table [1]

| IFFLAG | BLFLAG | FRRFLAG | Comment                                                                                                   |

|--------|--------|---------|-----------------------------------------------------------------------------------------------------------|

| 0      | 0      | 0       | if pin INTX is LOW and only IFMSK, FRRMSK and BLMSK were set then this cannot occur                       |

| 0      | 0      | 1       | alternative frequency jump successful; radio is tuned to the alternative frequency and stays muted        |

| 0      | 1      | 0       | not a valid state                                                                                         |

| 0      | 1      | 1       | not a valid state                                                                                         |

| 1      | 0      | 0       | not a valid state                                                                                         |

| 1      | 0      | 1       | AF jump has occurred but the wanted channel fails the IF count; the PLL will be set back to the old value |

| 1      | 1      | 0       | not a valid state                                                                                         |

| 1      | 1      | 1       | if pin INTX is LOW and only IFMSK, FRRMSK and BLMSK were set then this cannot occur                       |

<sup>[1]</sup> This table is valid until 30.6 ms after an RDS update has completed. It shows the outcome of the flag register when a read is done after pin INTX has gone LOW and on condition that only mask bit FRRMSK is set.

#### 9. Interrupt handling

#### 9.1 Interrupt register

The first two bytes of the  $I^2C$ -bus register contain the interrupt masks and the interrupt flags. A flag is set when it is a logic 1.

Table 6: INTFLAG - byte0R

| Bit      | 7 6                   |              | 5        | 4              | 3 | 2      | 1       | 0      |

|----------|-----------------------|--------------|----------|----------------|---|--------|---------|--------|

| Symbol   | Symbol DAVFLG TESTBIT |              | LSYNCFLG | IFFLAG LEVFLAG |   | PDFLAG | FRRFLAG | BLFLAG |

| Table 7: | INTMSK - byte         | e0W / byte1R |          |                |   |        |         |        |

|        |        | ,,, |          |       |        |       |        |       |

|--------|--------|-----|----------|-------|--------|-------|--------|-------|

| Bit    | 7      | 6   | 5        | 4     | 3      | 2     | 1      | 0     |

| Symbol | DAVMSK | -   | LSYNCMSK | IFMSK | LEVMSK | PDMSK | FRRMSK | BLMSK |

TEA5764UK\_2

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

The interrupt flag register contains the flags set according to the behavior outlined in Section 9.1.4. When these flags are set they can also cause the INTX to go active (hardware interrupt line) depending on the status of the corresponding mask bit in Table 7. A logic 1 in the mask register enables the hardware interrupt for that flag.

Hence, it is conceivable that, with all the mask bits cleared, the software could operate in a continuous polling mode that reads the interrupt flag register for any bits that maybe set.

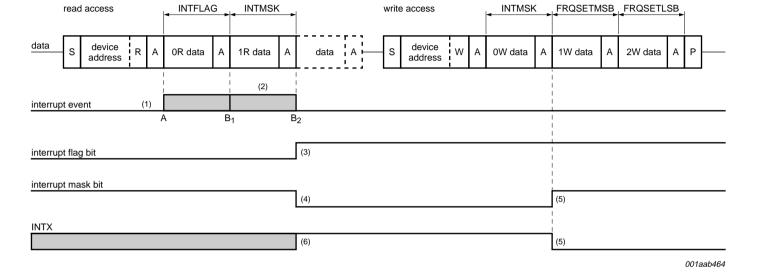

Interrupt mask bits are always cleared after reading the first two bytes of the interrupt register. This is to control multiple hardware interrupts (see <u>Figure 6</u>). Bit LSYNCMSK has a different function and is not cleared after reading the interrupt register bytes, see also <u>Section 9.1.4.3</u>.

#### 9.1.1 Interrupt clearing

The interrupt flag and mask bits are always cleared after:

- They have been read via the I2C-bus

- A power-on reset

#### **9.1.2 Timing**

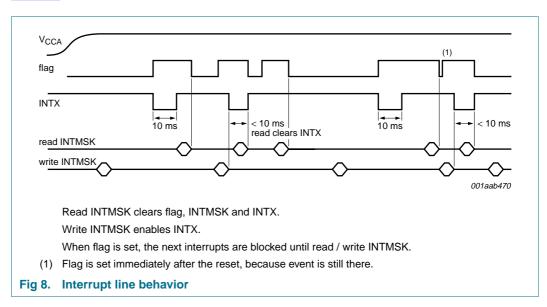

The timing sequence for the general operation interrupts is shown in <a href="Figure 6">Figure 6</a> and shows a read access of the interrupt bytes INTFLAG and INTMSK and a subsequent (though not necessarily immediate) write to the mask register. It also indicates the two key timing points A and B.

If an interrupt event occurs while the register is being accessed (after point A) it must be held until after the mask register is cleared at the end of the read operation (point B).

Point A is after the R/W bit has been decoded and point B is where the acknowledge has been received from the master after the first two bytes have been sent.

The LOW time for the INTX line ( $t_{LOW}$ ) has a maximum value specified in <u>Section 14</u>. However it can be shorter if the read of the INTMSK and INTFLAG bytes occurs within  $t_{LOW}$ .

#### 9.1.3 Reset

A reset can be performed at any time by a simple read of the interrupt bytes, byte0R and byte0W, which automatically clears the interrupt flags and masks.

- (1) Interrupt events that occur outside of the region A-B set their respective flag bits in the normal way immediately and can thus trigger a hardware interrupt if the mask bits are set.

- (2) The blocking of interrupts is marked by the region A-B<sub>1</sub> / B<sub>2</sub> depending on the actual read cycle.

- B<sub>1</sub> is when only the INTFLAG is read and a stop condition is received (only INTFLAG is read so only this will be cleared).

- B<sub>2</sub> is when both registers are read and hence cleared and this is terminated by either an acknowledge or stop bit.

- (3) Interrupt events that occur between A and B set their respective flags after the mask bits are cleared. Which means that in this diagram an interrupt event occurred in period A-B, so after A-B the flag goes to logic 1.

- (4) All interrupt mask bits are cleared after the interrupt flag and mask bytes are read.

- Software writes to the mask byte and enables the required mask bits. Any flags currently set will then trigger a hardware interrupt.

- INTX is set HIGH (inactive) after the interrupt mask bytes are read.

- Fig 6. I<sup>2</sup>C-bus interrupt sequence, read and write operation

#### 9.1.4 Interrupt flags and behavior

#### 9.1.4.1 Multiple interrupt events

If the interrupt mask register bit is set then the setting of an interrupt flag for that bit causes a hardware interrupt (pin INTX goes LOW). If the event occurs again, before the flag is cleared, then this does not trigger any further hardware interrupts until that specific flag is cleared. However, two different events can occur in sequence and generate a sequence of hardware interrupts. A second interrupt can be generated only after the INTMSK byte is read, followed by a write as the first interrupt blocks the input of the INTX one-shot generator.

If subsequent interrupts occur within the INTX LOW period then these do not cause the INTX period to extend beyond its specified maximum period (see Section 9.2).

#### 9.1.4.2 Data available flag

The DAVFLG is set when a new block of data is received according to the diagrams shown in <u>Section 10</u> where the different DAV modes are described. Once synchronized, this continues for all subsequent received blocks (dependent on DAV mode) and in the following situations:

- During sync search, in any DAV mode: two valid blocks in the correct sequence received with BBC < BBL (synchronized).</li>

- During synchronization search in DAVB mode if a valid A(C')-block has been detected. This mode can be used for fast search tuning (detection and comparison of the PI code contained in the A or C' block.

- If the pre-processor is synchronized and in mode DAVA and DAVB a new block has been processed. This mode is the standard data processing mode if the decoder is synchronized.

- If the pre-processor is synchronized and in DAVC mode, two new blocks have been processed.

- If the decoder is synchronized and in any DAV mode, with LSYNCMSK = 0, loss of synchronization is detected (flywheel loss of synchronization, resulting in a restart of synchronization search).

The DAVFLG is reset by a read of RDSLBLSB (byte15R) or RDSPBLSB (byte17R). An interrupt is asserted each time a new block of data is decoded and when bit DAVMSK is set; for details see Section 10.

#### 9.1.4.3 RDS synchronization flag

Bit SYNC, <u>Table 29</u>, shows the status of the RDS decoder. If it is a logic 1 then the decoder is synchronized, if it is a logic 0 it is not.

The action of the TEA5764UK depends on the status of bit LSYNCMSK in <u>Table 7</u>. If this is set then the loss of synchronization causes bit LSYNCFL to go to logic 1 when synchronization is lost, and a hardware interrupt is asserted. The RDS part of the TEA5764UK is set to idle and waits for the microprocessor to initiate a new synchronization search by setting bit NWSY as described in <u>Table 36</u>.

If bit LSYNCMSK is 0 and synchronization is lost, the ASIC automatically starts a new synchronization search. It will not generate a hardware interrupt. The microprocessor can wait until the RDS decoder is synchronized again, this will be indicated by the DAVFLG and the SYNC status bit (this requires bit DAVMSK being set).

Bit LSYNCFL is reset by a read of the INTMSK byte1R.

Bit LSYNCMSK is not reset by a read of byte INTMSK, it must be set or reset by the microprocessor. Resetting it automatically would change the status of the ASIC and cause an automatic synchronization search as described above.

How the synchronization is defined is explained in brief in Section 10.

#### 9.1.4.4 IF frequency flag

During an automatic frequency search, preset or AF update, the FM part of the TEA5764UK performs a check of the received IF frequency as a measure of the level of interference in the channel received. If an incorrect IF frequency is received, it indicates the presence of either strong interferers or tuning to an image which sets bit IFFLAG in the INTFLAG register. Also a preset to a channel with no signal will result in a wrong IF count value and hence the setting of bit IFFLAG.

When a search, preset or AF update is finished, bit FRRFLAG will be set to indicate this and will generate an interrupt. The microprocessor can now read the outcome of the registers which will contain the IF count value and the IFFLAG status of the channel it is tuned to. In the case of an AF update, the IF count value of the alternative frequency will be in the registers and also when it jumps back, because it will then not start a new IF count.

15 ms after the tuning algorithm has completed the IF counter will start a new count. So 30.6 ms after a failed AF update the IF count result will be equal again to that of the channel from where the jump was initiated.

15 ms after the FRRFLAG has been set the IF counter will start to run continuously on the tuned frequency and if the conditions for correct frequency are not met then this sets bit IFFLAG in the interrupt register. When bit IFMSK is set this will also cause an interrupt.

Bit IFFLAG is cleared by a read of byte1R, or by starting the tuning algorithm.

#### 9.1.4.5 RSSI threshold flag

The voltage level reflects the field strength received by the antenna. The voltage level is analog to digital converted to a 4-bit value and output via the l<sup>2</sup>C-bus, this 4-bit level value can be compared to a threshold level set by the SSL bits in <u>Table 19</u> or the LH bits in <u>Table 26</u>.

The ADC level (which converts the analog value to digital) can be triggered to convert in either of two ways:

During a tuning step, a search, a preset or an AF update, it is triggered by these algorithms and compares the level with the threshold set by bits SSL[1:0]. Bit LEVFLAG is set if the RSSI level drops below the threshold level set by bits SSL[1:0] (see <u>Table 19</u>). The hardware interrupt is only generated if the corresponding mask bit is set. 2. After a search, a preset or an AF update, the threshold for comparison is switched to the hysteresis level. The hysteresis level is set by the combination of bits SSL[1:0] and bit LHSW; see <u>Table 24</u>. The result is a hysteresis as shown in <u>Table 26</u>. Then the ADC level starts to run automatically and compares the level every 500 μs with the hysteresis level. Bit LEVFLAG is set if the RSSI level drops below the threshold level set by bits SSL[1:0] in combination with bit LHSW (see <u>Table 26</u>); the hardware interrupt is only generated if the corresponding mask bit is set. Bit LHSW allows either a small or a large hysteresis to be selected which results in the levels of the left RSSI hysteresis threshold column for bit LHSW = 0 and the right RSSI hysteresis threshold column; see <u>Table 26</u>. When a search or preset is done with the ADC level set to 3 then when the algorithm has finished, the threshold level is set to 0. Hence the LEVFLAG will never be set.

Bit LEVFLAG is cleared by a read of the INTMSK byte1R, or by starting the tuning algorithm.

#### 9.1.4.6 Pause detection flag

The pause detector monitors the amplitude of the audio signal and starts counting if it drops below the reference level. When the counter reaches the specified count time, a pause is detected and the PDFLAG is set and will generate an interrupt if bit PDMSK is set to logic 1. The PDFLAG operates independently of bit PDMSK and is only active when the RDS decoder is switched on when bit PUPD is set to logic 1 and when the RDS decoder is not idle if synchronization is lost.

See Figure 7. When the peak audio level of the (L+R) drops below the threshold level at  $t_1$  it counts the duration of the pause. If the pause lasts longer than the value set by the PT bits, bit PDFLAG is set which in turn generates a hardware interrupt (bit PDMSK set to logic 1). The threshold level at  $t_1$  is set by the PL bits shown in Table 38.

Bit PDFLAG is cleared by a read of byte1R on condition that the read action occurs more than  $500 \, \mu s$  after receiving the pause interrupt on the INTX line.

The circuit should ignore short transients where the audio level momentarily rises above the threshold (at t<sub>2</sub>).

A pause is detected by comparing the amplitude of the audio signal with the reference level selected by the PL bits. The resultant signal PSCO produced by this comparison is sampled at a frequency of 2341 Hz resulting in signal PSCOn. A pause is detected under the conditions given by Equation 4 and Equation 5.

$$\{SUM(0toN-1)[PSCOn = 0] - 8 \times SUM(0toN-1)[PSCOn = 1]\} > PT \times 2341 \tag{4}$$

$$t_{pause} - 8 \times t_{audio} > PT \tag{5}$$

where N is the number of samples taken over time and PT is the pause time selected by bus bits PT. When a pause is detected, the integrator will be reset. The integrator value cannot be less than zero; therefore if in <a href="Equation 4">Equation 4</a>, the value of the second SUM becomes larger than the first SUM, the output of the integrator remains at zero.

Suppose that PT = 20 ms,  $t_{pause}$  = 16 ms and  $t_{audio}$  = 1.5 ms. The pause detector will count according to Equation 5 as shown in Equation 6:

$$2 \times t_{pause} - 8 \times t_{audio} = 20 \text{ ms} \ge 2 \times 16 \text{ ms} - 8 \times 1.5 \text{ ms} = 20 \text{ ms}$$

(6)

TEA5764UK\_2

In Equation 6, the pause detector has measured  $1 \times 16$  ms 'pause',  $8 \times 1.5$  ms 'no pause' and  $1 \times 16$  ms pause. Therefore on average the pause detector has measured 16 ms -12 ms + 16 ms = 20 ms pause time and hence a pause will be detected.

The PSCOn signal goes directly to the software port. The PDFLAG is set by the integrator and goes to the bus. The interrupt line is triggered by the PDFLAG.

#### 9.1.4.7 Frequency ready flag

The frequency ready flag bit is set to logic 1 when the automatic tuning has finished a search, a preset or an RDS AF update. This bit is described in <u>Table 4</u> and <u>Table 5</u>. The FRRFLAG is cleared by a read of byte1R.

#### 9.1.4.8 Band limit flag

The band limit bit BLFLAG is set to logic 1 when the automatic tuning has detected the end of the tuning band or when the PLL cannot lock on a certain frequency. This bit is described in Table 4 and Table 5. This bit is cleared by reading byte1R.

#### 9.2 Interrupt output

The interrupt line driver is a MOS transistor with a nominal sink current of 680  $\mu$ A, it is pulled HIGH by an 18 k $\Omega$  resistor connected to pin VREFDIG. The interrupt line can be connected to one other similar device with an interrupt output and an 18 k $\Omega$  pull-up resistor providing a wired OR function. This allows any of the drivers to pull the line LOW by sinking the current. When a flag is set and not masked it generates an interrupt; see Figure 8.

#### 10. RDS data processing

The RDS demodulator and decoder perform the following operations:

- Demodulation of the RDS/RDBS data stream from the MPX signal

- Symbol decoding

- Block and group synchronization

- Error detection and correction

- Store last and previous data block received with associated ID and error status

- Set the DAVFLG when new data is received

- Set the SYNC status bit according to the current synchronization state

- Set the LSYNCFL flag when synchronization is lost

The RDS decoder can be set to different modes, each meant to look for specific information.

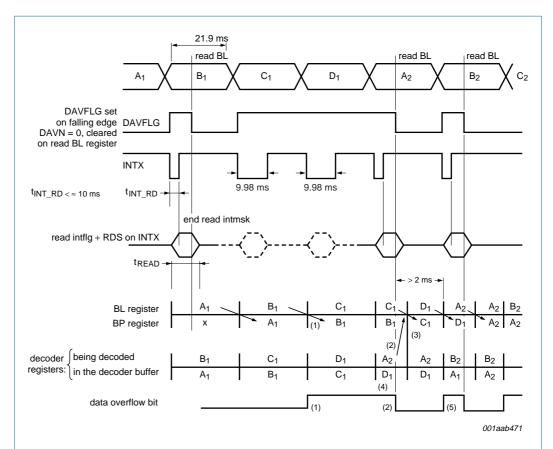

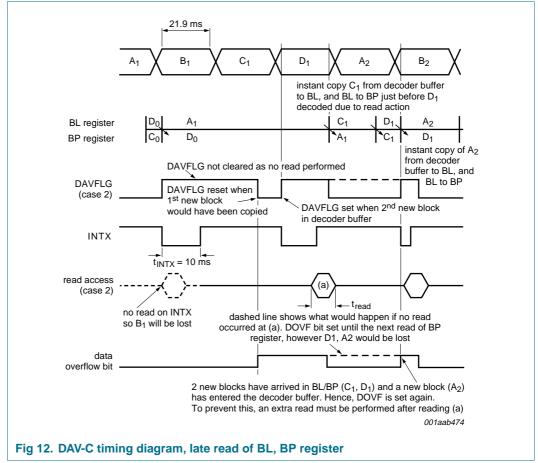

#### 10.1 DAV-A processing mode

The DAV-A processing mode is the standard processing mode used. In this mode, when a data block has been decoded, it is transferred to the I<sup>2</sup>C-bus registers. It generates interrupts on the INTX line after every new block of RDS data that has been processed and also sets the DAVFLG; see <u>Figure 9</u>. The DAVFLG is reset by a read of the I<sup>2</sup>C-bus registers.

If a data block is decoded and a new one arrives, pin INTX goes LOW again, the DAVFLG will be set and the last block will be shifted to the previous block and the last decoded block will be put in the last block. This means that all RDS data is still available in the BL and BP registers.

When the I<sup>2</sup>C-bus registers are not read the DAVFLG will not be reset. If a data block is decoded and a new one arrives, pin INTX goes LOW and the last block will be shifted to the previous block and the last decoded block will be put in the last block. This means that all RDS data is still available in the BL and BP registers but must be read. This is indicated by the setting of bit DOVF.

If the I<sup>2</sup>C-bus registers are still not read, data will be lost, except when this read is done within 20 ms after the INTX line has gone LOW and 2 ms before the arrival of a new block. If this read is done at least 2 ms before the arrival of a new block, then BL and BP are read and the data in the decoder buffer is then instantaneously shifted to the BL register. All data is now read and bit DOVF will be reset.

Bit DOVF set when 2 new blocks received in BL and BP registers

- (1) If there is no read cycle,  $B_1$  is placed in the BP register and the new block  $C_1$  is now in the BL register. Bit DOVF is set to indicate two blocks available.

- (2) Data is not transferred to BL register at the end of the read period/clear DOVF,  $D_1$  is missed.

- (3) In order not to lose D<sub>1</sub> a read must be performed before D<sub>1</sub> enters decoder buffer, thus read finishes within 21 ms after DOVF set to logic 1.

- (4) DOVF is cleared when the BL register is read. To be of use, DOVF has to be read before BL and BP registers.

- (5) To prevent DOVF being set again, an extra read of BL must be performed before A2 has been decoded.

Fig 9. DAV-A timing diagram, DAV-A/B: normal

<u>Figure 9</u> assumes that block synchronization has been achieved and that no other interrupt flags are being set.

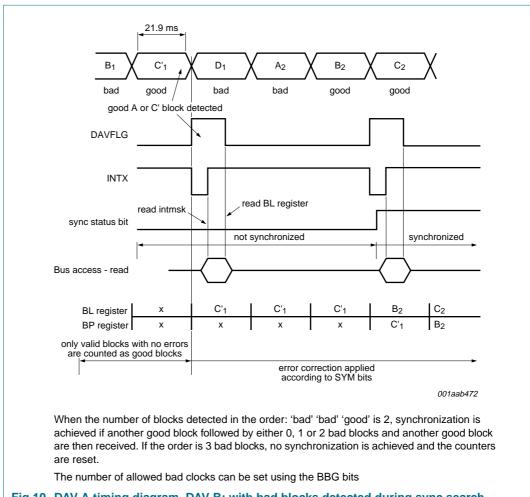

#### 10.2 DAV-B processing mode / fast PI search mode

This mode is used, for example, when the receiver has been re-tuned to a new station, and a fast search of the PI code, always contained in the A or C' block, is required. The diagram shown in <a href="Figure 10">Figure 10</a>, assumes that the RDS decoder is unsynchronized initially and is performing a synchronization search.

During synchronization search the decoder does not set the DAVFLG until a valid A or C' block is detected. If a valid B block is detected immediately, then the decoder is now synchronized and bit SYNC is set to logic 1. In fact, if any 2 good blocks in a valid order are detected, the RDS decoder will synchronize and give an interrupt.

If for some reason a valid B block was not received then the next valid A or C' block is decoded and the DAVFLG set. The BP and BL registers record the A block history.

When the decoder is synchronized, each decoded block will set the DAVFLG (assuming it was reset by a read action) and generate an interrupt.

Fig 10. DAV-A timing diagram, DAV B: with bad blocks detected during sync search

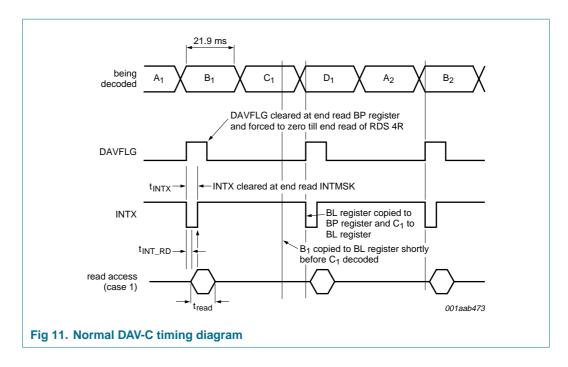

#### 10.3 DAV-C reduced processing mode

The DAV-C processing mode is very similar to DAV-A mode with the main exception that a data flag is set only after two new blocks are received. Hence the update rate is reduced by half.

#### 10.4 Synchronization

#### 10.4.1 Conditions for synchronization

When the RDS decoder is turned on it must be synchronized to extract valid data from the MPX signal. To do so the decoder automatically initiates a search for synchronization. The conditions to meet synchronization and the status of this synchronization can be set and checked by the following bits:

- BBL (Bad Blocks Lose): these bits can be set via the I<sup>2</sup>C-bus and have a value between 0 to 63

- GBL (Good Blocks Lose): these bits can be set via the I<sup>2</sup>C-bus and have a value between 0 to 63

- BBG (Bad Blocks Gain): these bits can be set via the I<sup>2</sup>C-bus and have a value between 0 to 32

- GBC (Good Block Count): these bits can be read via the I<sup>2</sup>C-bus and have a value between 0 to 63

- BBC (Bad Block Count): these bits can be read via the I<sup>2</sup>C-bus and have a value between 0 to 63

When the decoder is not synchronized it will initiate a synchronization search. This involves calculation of the syndrome for each block of 26 received bits on a bit-by-bit basis. When a correct syndrome (and hence block ID) is received the decoder clocks the next 26 bits into the internal registers and performs a second syndrome check. Synchronization is found when a certain number of blocks have been decoded and two good blocks have been found, this number of blocks is defined by the BBG bits. If the first block needed for synchronization has been found and the expected second block (after 26 bits) is an invalid block, then the decoder module internal bad\_blocks\_counter is incremented and the next expected block is calculated; exception: if RBDS mode is selected and the first block is E, then the next expected block is always block A, until synchronization is found or the maximum bad\_blocks\_counter value is reached. If the decoder module internal bad\_blocks\_counter reaches the value of BBG[4:0], then a new synchronization search (bit-by-bit) is started immediately to find a new first block.

The synchronization is monitored by two flywheel counters, GBC and BBC. These are 6-bit counters that can be preset by bits GBL and BBL to values between 0 and 63. Each time a block is decoded and recognized as a bad block the Bad Block Counter value, BBC, is incremented by 1. When the BBC value is equal to the BBL value, synchronization is lost. Bit SYNC will become 0 and bit LSYNCFL is set to indicate the loss of synchronization. The TEA5764UK will now automatically initiate a new synchronization search.

Each time a good block is decoded, the GBC value is incremented. When the GBC value is equal to the GBL value, both counters, BBC and GBC, are set to 0 and a new count starts. The GBC counter is only incremented when the decoder is synchronized.

#### 10.4.2 Data overflow

During synchronization, after RDS data is read from the registers, new available blocks are shifted to the registers as described in <u>Section 10.1</u> to <u>Section 10.3</u>. If the registers are not read in time, the decoder cannot shift any new available block to the registers and hence a data overflow will occur, this is indicated by bit DOVF which is set to 1. Bit DOVF is reset by a read of the registers or if bit NWSY = 1 which results in the start of a new synchronization search.

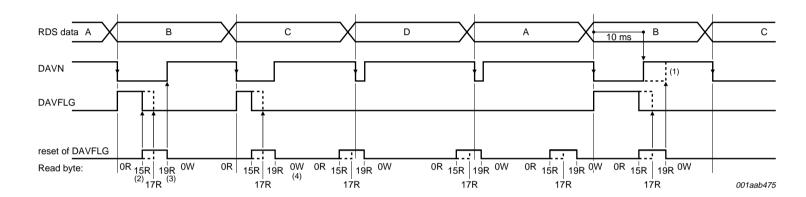

Each time when a RDS data block is decoded, bit DAVN goes to logic 0 to indicate the presence of a new data block. Bit DAVN also triggers the interrupt output INTX. In principle the microprocessor must now start reading and must have read all RDS data (byte12R to byte19R) before the arrival of a new RDS data block. In the application it is possible that there is too large a delay between the arrival of a new block and reading this block. This can have various causes such as a microprocessor that has to start-up from Sleep mode or when polling is used instead of interrupt based read actions. Figure 13 shows the behavior of bit DAVFLG and bit DAVN when polling, where reading can occur at any time. Note: Bit DAVN sets the INTX oneshot generator when DAVMSK = 1. Unlike INTX, bit DAVN is not cleared by a read of the mask register.

#### 10.5 RDS flag behavior during read action

Blocking DAVFLG: at end of reading byte15R or byte17R (DAV-A, B/C) DAVFLG is forced to zero. Only after reading byte19R DAVFLG is released again.

If synchronous reading is performed using ASIC generated interrupts, this problem does not occur.

To prevent undefined situations, byte12R to byte19R should always be read in one action immediately after each other. Signal DAVN ≠ INTX.

- (1) Normally reading byte19R would reset bit DAVN, but now it is reset after 10 ms, the maximal LOW time of bit DAVN.

- (2) Read of byte15R in DAV-A and DAV-B mode clears DAVFLG. In DAV-C mode two consecutive RDS data blocks are read and hence DAVFLG is reset after reading byte17R instead of byte15R (dotted line).

- (3) Read of byte19R clears bit DAVN.

- (4) Write byte0W (interrupt register).

#### Fig 13. RDS flag behavior

**Philips**

Semiconductors

#### 10.6 Error detection and reporting

The TDA5764UK must report information on the number of errors corrected in the last and previously decoded blocks. This is reported in bits ELB and EPB as shown in Table 29.

During synchronization search the error correction is disabled for detection of the first block and is enabled for processing of the second block according to the mode set by the SYM bits as described in Table 36.

#### 10.7 RDS test modes

In Test mode the raw RDS clock and RDS data can be recovered directly from pins VAFL and VAFR when bit RDSCDA = 1.

#### 10.8 Reading RDS data from the registers

To read RDS data the microprocessor must read byte12R to byte19R. All 8 bytes must be read to reset the status bytes 12R and 13R, i.e. effectively the status bits can be updated by the decoder after reading the last bit of byte19R. Bit DOVF is cleared after reading the last bit of byte19R and the status of bit SYNC does not depend on reading the register, bit SYNC indicates if the decoder is synchronized or not. When starting a read action from byte12R, the decoder blocks updates from the RDS bytes until byte19R has been read. RDS byte12R to byte19R must be read in one read action.

#### 11. I<sup>2</sup>C-bus interface

The  $I^2C$ -bus interface is based on "The  $I^2C$ -bus specification", version 2.1 January 2000, expanded by the following definitions.

#### 11.1 Write and read mode

#### Table 8: I<sup>2</sup>C-bus FM write mode

| S     | Byte 1       |                  | As  | Byte 2    | As  | Byte n | As  | Byte 8    | As  | Р    |

|-------|--------------|------------------|-----|-----------|-----|--------|-----|-----------|-----|------|

| START | chip address | $R/\overline{W}$ | ACK | byte0W    | ACK |        | ACK | byte6W    | ACK | STOP |

|       | 0010 000     | 0                |     | XXXX XXXX |     |        |     | XXXX XXXX |     |      |

#### Table 9: I<sup>2</sup>C-bus RDS write mode

| S     | Byte 1       | As     | Byte 2    | Am  | Byte n | As  | Byte 8    | As         | Р    |

|-------|--------------|--------|-----------|-----|--------|-----|-----------|------------|------|

| START | chip address | R/W AC | C byte7W  | ACK |        | ACK | byte10W   | non<br>ACK | STOP |

|       | 0010 001     | 0      | xxxx xxxx |     |        |     | xxxx xxxx |            |      |

When writing all bytes, byte0W to byte10W can be written with one write action.

#### Table 10: I<sup>2</sup>C-bus FM read mode

| S     | Byte 1       |     | As  | Byte 2    | Am  | Byte n | Am  | Byte 17   | NAm        | Р    |

|-------|--------------|-----|-----|-----------|-----|--------|-----|-----------|------------|------|

| START | chip address | R/W | ACK | byte0R    | ACK |        | ACK | byte15R   | non<br>ACK | STOP |

|       | 0010 000     | 1   |     | XXXX XXXX |     |        |     | xxxx xxxx |            |      |

| S     | Byte 1       |     | As  | Byte 2    | Am  | Byte n | Am  | Byte 17   | NAm        | Р    |

|-------|--------------|-----|-----|-----------|-----|--------|-----|-----------|------------|------|

| START | chip address | R/W | ACK | byte12R   | ACK |        | ACK | byte27R   | non<br>ACK | STOP |

|       | 0010 001     | 1   |     | XXXX XXXX |     |        |     | XXXX XXXX |            |      |

Table 12: I<sup>2</sup>C-bus transfer description

| Label        | Definition                                                                     |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|--|--|--|--|

| S            | START condition                                                                |  |  |  |  |

| Byte 1       | I <sup>2</sup> C-bus chip address (7 bits)                                     |  |  |  |  |

|              | $R/\overline{W} = 0$ for write action and $R/\overline{W} = 1$ for read action |  |  |  |  |

| As           | acknowledge from slave TEA5764UK (SDA is LOW)                                  |  |  |  |  |

| Byte 2, etc. | data byte (8 bits)                                                             |  |  |  |  |

| Р            | STOP condition                                                                 |  |  |  |  |

| Am           | acknowledge from master microcontroller (SDA is LOW)                           |  |  |  |  |

| NAm          | non acknowledge from master microcontroller (SDA is HIGH)                      |  |  |  |  |

| NA           | non acknowledge (SDA is HIGH)                                                  |  |  |  |  |

When the TEA5764UK is addressed by the FM radio address, the RDS part (byte12R to byte27R) can be read in one read action. A read does not have to stop at byte11R.

Therefore, by effectively only using the RDS part of the address, ignores some bytes which reduces I<sup>2</sup>C-bus access.

#### 11.2 Data transfer

Structure of the I2C-bus:

- Slave transceiver

- · Subaddresses not used

- Maximum LOW-level input voltage: V<sub>IL</sub> = 0.3 × V<sub>VREFDIG</sub>

- Minimum HIGH-level input voltage: V<sub>IH</sub> = 0.7 × V<sub>VREFDIG</sub>

**Remark:** The I<sup>2</sup>C-bus operates at a maximum clock rate of 400 kHz. It is not allowed to connect the TEA5764UK to a I<sup>2</sup>C-bus operating at a higher clock rate.

Data transfer to the IC:

- Bit 7 of each byte is considered the MSB and has to be transferred as the first bit of the byte

- The LSB indicates the write or read action

- The data becomes valid byte-wise at the appropriate falling edge of the SCL clock

- A STOP condition after any byte can shorten transmission times. When writing to the transceiver by using the STOP condition before completion of the whole transfer:

- The remaining bytes will contain the old information

- If the transfer of a byte is not completed the new bits will be used, but a new tuning cycle will not be started

TEA5764UK\_2

To speed up RDS traffic it is possible to read all the RDS data and then only write back byte INTMSK to set the appropriate mask(s) again.

#### I<sup>2</sup>C-bus activity:

- With bits PUPD the TEA5764UK can be switched in a low current Standby mode. The I<sup>2</sup>C-bus is then still active

- When the I<sup>2</sup>C-bus interface is deactivated, by making pin BUSENABLE LOW and without programmed Standby mode, the TEA5764UK keeps its normal operation, but is isolated from the I<sup>2</sup>C-bus lines

- It is possible to operate the TEA5764UK with BUSENABLE hard wired to pin VREFDIG, and have the bus interface always active.

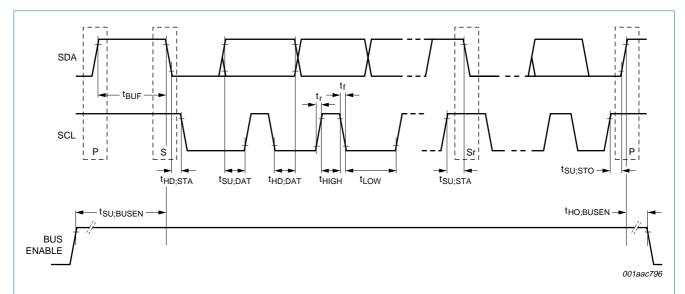

$t_f$  = fall time of both SDA and SCL signals: 20 + 0.1  $C_b$  <  $t_f$  < 300 ns, where  $C_b$  = total capacitance on bus line in pF.  $t_f$  = rise time of both SDA and SCL signals: 20 + 0.1  $C_b$  <  $t_f$  < 300 ns, where  $C_b$  = total capacitance on bus line in pF.

t<sub>HD:STA</sub> = hold time (repeated) START condition. After this period, the first clock pulse is generated: > 600 ns.

$t_{HIGH}$  = HIGH period of the SCL clock: > 600 ns.

$t_{SU;STA}$  = setup time for a repeated START condition: > 600 ns.

$t_{HD;DAT}$  = data hold time: 300 <  $t_{HD;DAT}$  < 900 ns.

Remark: 300 ns lower limit is added because the ASIC has no internal hold time for the SDA signal.

$t_{SU;DAT} = data \ setup \ time: \ t_{SU;DAT} > 100 \ ns. \ If \ ASIC \ is \ used \ in \ a \ standard \ mode \ I^2C-bus \ system, \ t_{SU;DAT} > 250 \ ns.$

$t_{SU;STO}$  = setup time for STOP condition: > 600 ns.

$t_{BUF}$  = bus free time between a STOP and a START condition: > 600 ns.

$C_b$  = capacitive load of one bus line: < 400 pF.

$t_{\text{SU;BUSEN}}$  = bus enable setup time:  $t_{\text{SU;BUSEN}}$  > 10  $\mu s.$

$t_{HO;BUSEN}$  = bus enable hold time:  $t_{HO:BUSEN}$  > 10  $\mu s.$

Fig 14. Bus timing diagram

#### 11.3 Register map

Table 13: Register overview

| Table 13: | Register overvie | W         |        |             |           |

|-----------|------------------|-----------|--------|-------------|-----------|

| Byte      |                  | Byte name | Access | Reset value | Reference |

| Read      | Write            |           |        |             |           |

| 0R        |                  | INTFLAG   | R      | 00          | Table 14  |

| 1R        | 0W               | INTMSK    | R/W    | 00          | Table 15  |

| 2R        | 1W               | FRQSETMSB | R/W    | 80          | Table 16  |

| 3R        | 2W               | FRQSETLSB | R/W    | 00          | Table 17  |

| 4R        | 3W               | TNCTRL1   | R/W    | 08          | Table 18  |

| 5R        | 4W               | TNCTRL2   | R/W    | D2          | Table 19  |

| 6R        |                  | FRQCHKMSB | R      | -           | Table 20  |

| 7R        |                  | FRQCHKLSB | R      | -           | Table 21  |

| 8R        |                  | IFCHK     | R      | -           | Table 22  |

| 9R        |                  | LEVCHK    | R      | -           | Table 23  |

| 10R       | 5W               | TESTBITS  | R/W    | 00          | Table 24  |

| 11R       | 6W               | TESTMODE  | R/W    | 00          | Table 25  |

| 12R       |                  | RDSSTAT1  | R      | -           | Table 28  |

| 13R       |                  | RDSSTAT2  | R      | -           | Table 29  |

| 14R       |                  | RDSLBMSB  | R      | -           | Table 30  |

| 15R       |                  | RDSLBLSB  | R      | -           | Table 31  |

| 16R       |                  | RDSPBMSB  | R      | -           | Table 32  |

| 17R       |                  | RDSPBLSB  | R      | -           | Table 33  |

| 18R       |                  | RDSBBC    | R      | -           | Table 34  |

| 19R       |                  | RDSGBC    | R      | -           | Table 35  |

| 20R       | 7W               | RDSCTRL1  | R/W    | 00          | Table 36  |

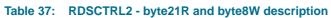

| 21R       | 8W               | RDSCTRL2  | R/W    | 10          | Table 37  |

| 22R       | 9W               | PAUSEDET  | R/W    | 00          | Table 38  |

| 23R       | 10W              | RDSBBL    | R/W    | 00          | Table 39  |

| 24R       |                  | MANID1    | R      | 50          | Table 40  |

| 25R       |                  | MANID2    | R      | 2B          | Table 41  |

| 26R       |                  | CHIPID1   | R      | 57          | Table 42  |

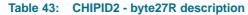

| 27R       |                  | CHPID2    | R      | 64          | Table 43  |

|           |                  |           |        |             |           |

#### 11.4 Byte description

Table 14: INTFLAG - byte0R description

| Bit | Symbol  | Access | Reset | Functional description      |

|-----|---------|--------|-------|-----------------------------|