1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

Solutions for a Real Time World

**NEMO Bluetooth Radio Module**

Datasheet

## **Unigen Corp. Wireless Module Products**

## NEMO Bluetooth Radio Modules UGWC621RSMA133

Issue Date: 18-Aug-09 Revision: 1.1

Solutions for a Real Time World

### Datasheet

## **Revision History**

| Rev. No. | History  | Issue Date    | Remarks                                         |

|----------|----------|---------------|-------------------------------------------------|

| 1.0      | Draft    | Dec. 5, 2008  | Advanced information; Author: Allen B. Cabreros |

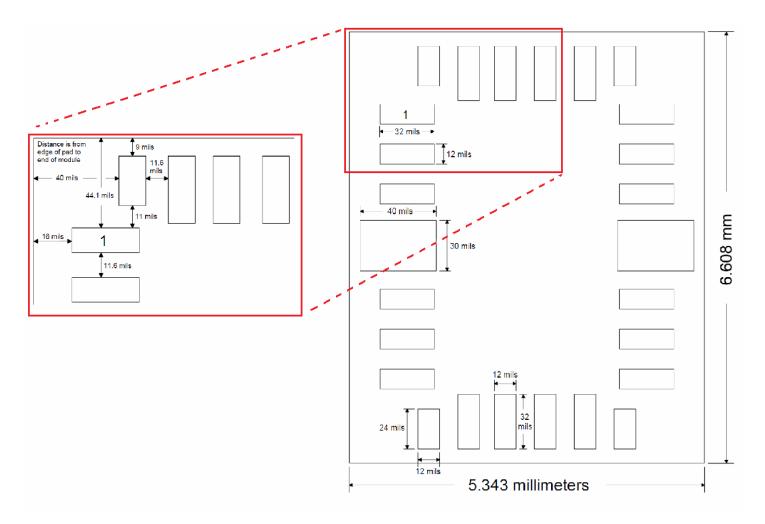

| 1.1      | Revision | Aug. 18, 2009 | Added dimensional drawings.                     |

|          |          |               |                                                 |

|          |          |               |                                                 |

|          |          |               |                                                 |

|          |          |               |                                                 |

|          |          |               |                                                 |

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Unigen Corporation disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this document. No license, expressed or implied, by estoppel or otherwise, to any intellectual property rights is granted herein.

\*Third-party brands, names, and trademarks are the property of their respective owners.

Solutions for a Real Time World

Datasheet

## TABLE OF CONTENTS

| LIST OF FIGURES       4         LIST OF TABLES       5         PRODUCT INTRODUCTION       6         PRODUCT INTRODUCTION       6         FATURES AND BENEFITS       6         PRODUCT DESCRIPTION       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RECOMMENDED OPERATING CONDITIONS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Firmware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         BlueCore Serial Protocol (BCSP)       22         BlueCore Serial Protocol (BCSP)       22                                                                                            | TABLE OF CONTENTS                                                 |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----|

| LIST OF TABLES       5         PRODUCT INTRODUCTION       6         PRODUCT INTRODUCTION       6         FEATURES AND BENEFITS       6         PRODUCT DESCRIPTION       8         NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RECOMMENDED OPERATING CONDITIONS       13         RECOMMENDED OPERATING CONDITIONS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Yey Features of the HCI Stack: Extra Functionality       22         BlueCore Serial Protocol (BCSP)       22         BlueCore ComMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Long Frame Sync       27         PCM Interface Mast                                                                                   | LIST OF FIGURES                                                   | 4  |

| PRODUCT INTRODUCTION       6         PRODUCT INTRODUCTION       6         FEATURES AND BENEFITS       6         PRODUCT DESCRIPTION       8         NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Lo                                                                                   | LIST OF TABLES                                                    | 5  |

| PRODUCT INTRODUCTION       6         FEATURES AND BENEFITS       6         PRODUCT DESCRIPTION       8         NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Extra Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync                                                                                         | PRODUCT INTRODUCTION                                              | 6  |

| FEATURES AND BENEFITS       6         PRODUCT DESCRIPTION       8         NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RECOMMENDE OPERATING CONDITIONS       13         RECOMENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Firmware Functional Description       17         CSR                                                                                    |                                                                   |    |

| PRODUCT DESCRIPTION       8         NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RECOMMENDED OPERATING CONDITIONS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       16         NEMO Hardware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       28         Multi-slot Operation       30                                       | FEATURES AND BENEFITS                                             | 6  |

| NEMO Module       8         CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Long Frame Sync       28         Multi-slot Operation       30         PCM Stots and Sample                                                 |                                                                   |    |

| CSR BlueCore 6 ROM Transceiver IC       8         Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN ASSIGNMENT       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         FUNCTIONAL OVERVIEW       16         NEGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       30                                                                             | NEMO Module                                                       | 8  |

| Functional Block Diagrams       9         PIN ASSIGNMENT       11         PIN FUNCTIONS       12         PIN FUNCTIONS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       31         PCM Configuration       32         PCM Configuration       32         PCM Configuration       33         PCM Configuration                                                                                        | CSR BlueCore 6 ROM Transceiver IC                                 | 8  |

| PIN ASSIGNMENT       11         PIN FUNCTIONS       12         ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       30         PCM Slots and Sample Formats       31         PCM Slots and Sample Formats <td< td=""><td>Functional Block Diagrams</td><td>9</td></td<> | Functional Block Diagrams                                         | 9  |

| ABSOLUTE MAXIMUM RATINGS       13         RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Standard Bluetooth Functionality       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Interface Master/Slave       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Configuration       35         Digital Audio Interface (I²S)       38                                     |                                                                   |    |

| RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Configuration       32         PCM Configuration       35         Digital Audio Interface (I²S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                    | PIN FUNCTIONS                                                     | 12 |

| RECOMMENDED OPERATING CONDITIONS       13         RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Configuration       32         PCM Configuration       35         Digital Audio Interface (I²S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                    | ABSOLUTE MAXIMUM RATINGS                                          | 13 |

| RF CHARACTERISTICS       14         EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS       14         AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Configuration       32         PCM Configuration       35         Digital Audio Interface (I²S)       38         Figure 20: Digital Audio Interface Master Timing       41 </td <td>RECOMMENDED OPERATING CONDITIONS</td> <td>13</td>          | RECOMMENDED OPERATING CONDITIONS                                  | 13 |

| AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       21         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM COnfiguration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                                                                                                                                                                | RF CHARACTERISTICS                                                | 14 |

| AGENCY CERTIFICATIONS (PRE-SCAN)       15         REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       21         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM COnfiguration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                                                                                                                                                                | EXTERNAL SLOW CLOCK SOURCE CHARACTERISTICS                        | 14 |

| REGULATORY COMPLIANCE STATEMENT       15         FUNCTIONAL OVERVIEW       16         NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       32         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                                 | AGENCY CERTIFICATIONS (PRE-SCAN)                                  | 15 |

| NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                                                                                                                                                                                                                         | REGULATORY COMPLIANCE STATEMENT                                   | 15 |

| NEMO Hardware Functional Description       16         NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                      | FUNCTIONAL OVERVIEW                                               | 16 |

| NEMO Firmware Functional Description       17         CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                           | NEMO Hardware Functional Description                              | 16 |

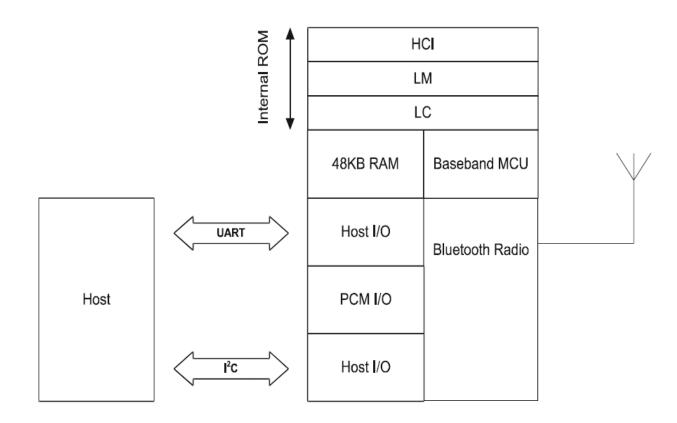

| CSR BLUETOOTH SOFTWARE STACK       18         Key Features of the HCI Stack: Standard Bluetooth Functionality       19         Key Features of the HCI Stack: Extra Functionality       21         DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and 12S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                                                                                 | NEMO Firmware Functional Description                              | 17 |

| Key Features of the HCI Stack: Extra Functionality21         DIGITAL INTERFACES22         High Speed UART Interface22         BlueCore Serial Protocol (BCSP)22         BLUECORE COMMAND (BCCMD) PROTOCOL24         Audio PCM and I2S Interfaces25         PCM Interface Master/Slave25         PCM Long Frame Sync27         Short Frame Sync28         Multi-slot Operation29         GCI Interface30         PCM Slots and Sample Formats31         PCM CLK and PCM SYNC Generation32         PCM Configuration35         Digital Audio Interface (I²S)38         Figure 20: Digital Audio Interface Master Timing41         POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                   |    |

| DIGITAL INTERFACES       22         High Speed UART Interface       22         BlueCore Serial Protocol (BCSP)       22         BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       27         Short Frame Sync       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Timing Information       32         PCM Configuration       35         Digital Audio Interface (1 <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Key Features of the HCI Stack: Standard Bluetooth Functionality _ | 19 |

| High Speed UART Interface22BlueCore Serial Protocol (BCSP)22BLUECORE COMMAND (BCCMD) PROTOCOL24Audio PCM and I2S Interfaces25PCM Interface Master/Slave25PCM Long Frame Sync27Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Key Features of the HCI Stack: Extra Functionality                | 21 |

| High Speed UART Interface22BlueCore Serial Protocol (BCSP)22BLUECORE COMMAND (BCCMD) PROTOCOL24Audio PCM and I2S Interfaces25PCM Interface Master/Slave25PCM Long Frame Sync27Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DIGITAL INTERFACES                                                | 22 |

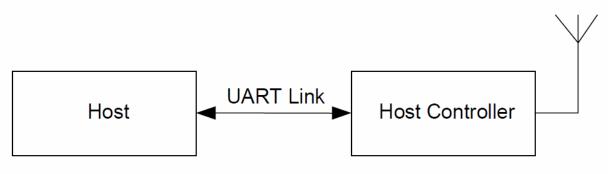

| BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Timing Information       32         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I²S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | High Speed UART Interface                                         | 22 |

| BLUECORE COMMAND (BCCMD) PROTOCOL       24         Audio PCM and I2S Interfaces       25         PCM Interface Master/Slave       25         PCM Long Frame Sync       27         Short Frame Sync       28         Multi-slot Operation       29         GCI Interface       30         PCM Slots and Sample Formats       31         PCM Timing Information       32         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I²S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BlueCore Serial Protocol (BCSP)                                   | 22 |

| PCM Interface Master/Slave25PCM Long Frame Sync27Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | BLUECORE COMMAND (BCCMD) PROTOCOL                                 | 24 |

| PCM Long Frame Sync27Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Audio PCM and I2S Interfaces                                      | 25 |

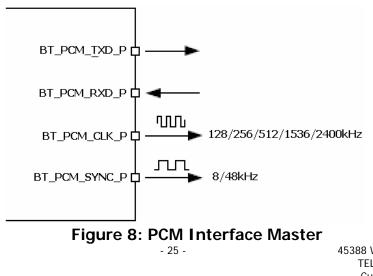

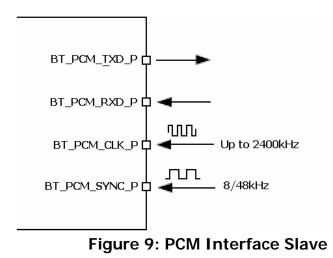

| Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCM Interface Master/Slave                                        | 25 |

| Short Frame Sync28Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PCM Long Frame Sync                                               | 27 |

| Multi-slot Operation29GCI Interface30PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                   |    |

| PCM Slots and Sample Formats31PCM Timing Information32PCM CLK and PCM SYNC Generation34PCM Configuration35Digital Audio Interface (I²S)38Figure 20: Digital Audio Interface Master Timing41POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                   | 29 |

| PCM Timing Information       32         PCM CLK and PCM SYNC Generation       34         PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GCI Interface                                                     | 30 |

| PCM CLK and PCM SYNC Generation34         PCM Configuration35         Digital Audio Interface (I <sup>2</sup> S)38         Figure 20: Digital Audio Interface Master Timing41         POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PCM Slots and Sample Formats                                      | 31 |

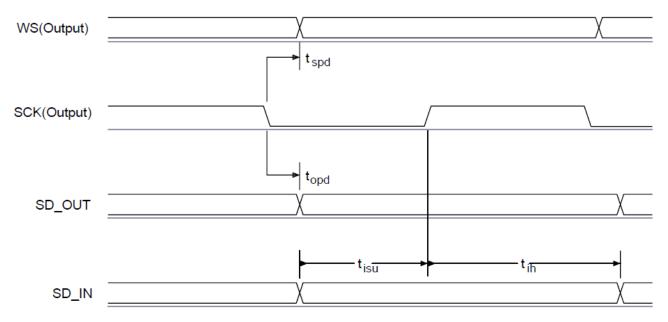

| PCM Configuration       35         Digital Audio Interface (I <sup>2</sup> S)       38         Figure 20: Digital Audio Interface Master Timing       41         POWER CONSUMPTION       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCM Timing Information                                            | 32 |

| Figure 20: Digital Audio Interface Master Timing41      POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                   |    |

| Figure 20: Digital Audio Interface Master Timing41      POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PCM Configuration                                                 | 35 |

| Figure 20: Digital Audio Interface Master Timing41      POWER CONSUMPTION42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Digital Audio Interface (I <sup>2</sup> S)                        | 38 |

| POWER CONSUMPTION    42      BOOTING NEMO ROM    44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 20: Digital Audio Interface Master Timing                  | 41 |

| BOOTING NEMO ROM44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | POWER CONSUMPTION                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BOOTING NEMO ROM                                                  |    |

Datasheet

Solutions for a Real Time World

| UART Auto Baud Rate                             | 44 |

|-------------------------------------------------|----|

| Persistent Store Keys (PSKEYS)                  | 45 |

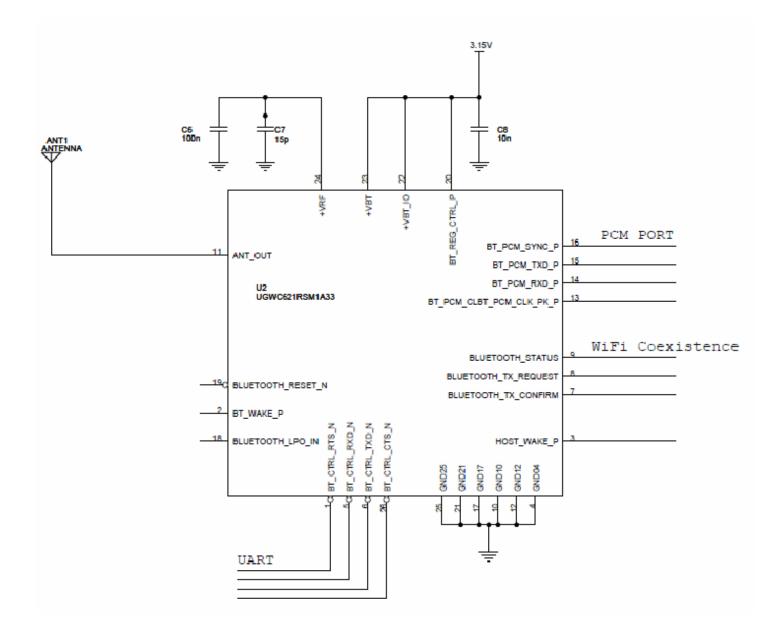

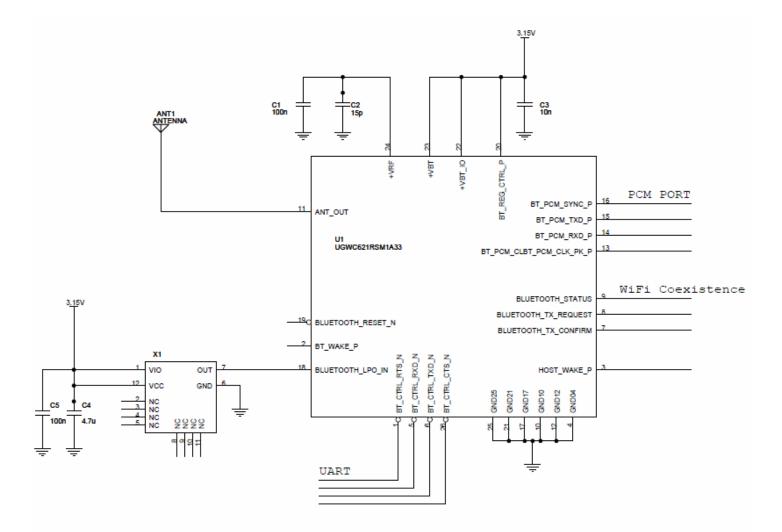

| TYPICAL APPLICATION CIRCUITS                    | 48 |

| NEMO with out external 32kHz slow clock source: | 48 |

| NEMO with external 32kHz slow clock source:     | 49 |

| MECHANICAL DRAWINGS                             | 50 |

| REFERENCE DOCUMENTATION                         | 51 |

| CONTACT INFORMATION                             | 51 |

## LIST OF FIGURES

| Figure 1: NEMO Module Block Diagram                                  | _9     |

|----------------------------------------------------------------------|--------|

| Figure 2: CSR BlueCore 6 ROM Block Diagram                           | _10    |

| Figure 3: NEMO Module Pin Locations                                  | _11    |

| Figure 4: BlueCore Bluetooth HCI Stack                               | _18    |

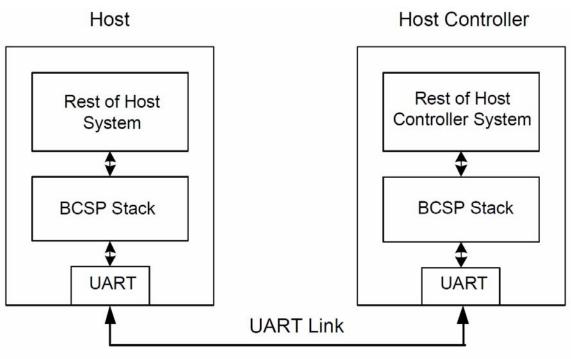

| Figure 5: UART Host Connection                                       | _23    |

| Figure 6: BCSP Context                                               | _23    |

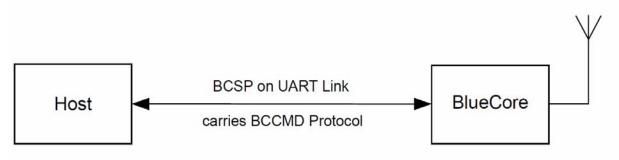

| Figure 7: BCCMD Interface                                            | _24    |

| Figure 8: PCM Interface Master                                       | _25    |

| Figure 9: PCM Interface Slave                                        | _26    |

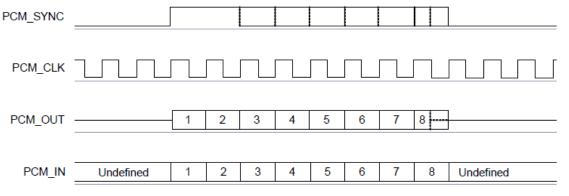

| Figure 10: Long Frame Sync (Shown with 8-bit Companded Sample) _     | _27    |

| Figure 11: Short Frame Sync (Shown with 16-bit Sample)               | _28    |

| Figure 12: Multi-slot Operation with Two Slots and 8-bit Companded S | amples |

|                                                                      | _29    |

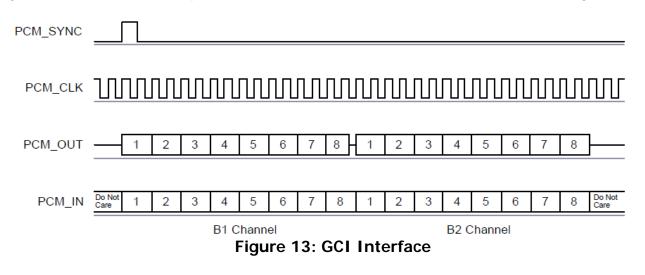

| Figure 13: GCI Interface                                             | _30    |

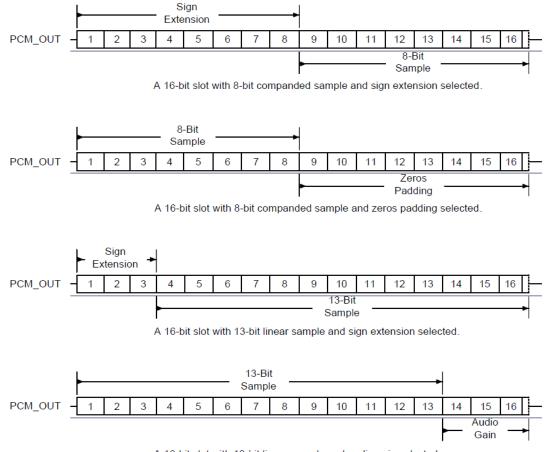

| Figure 14: 16-Bit Slot Length and Sample Formats                     | _31    |

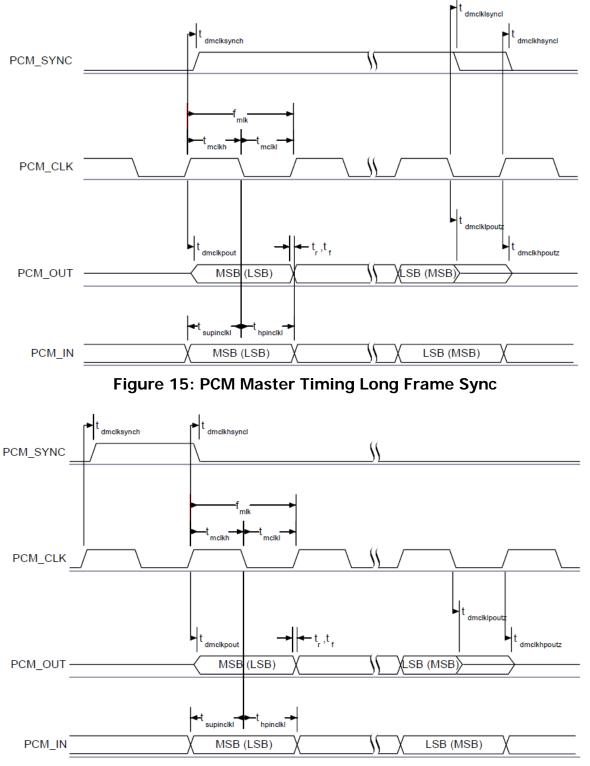

| Figure 15: PCM Master Timing Long Frame Sync                         | _33    |

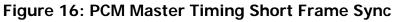

| Figure 16: PCM Master Timing Short Frame Sync                        | _33    |

| Figure 17: PCM slave Timing Short Frame Sync                         | _34    |

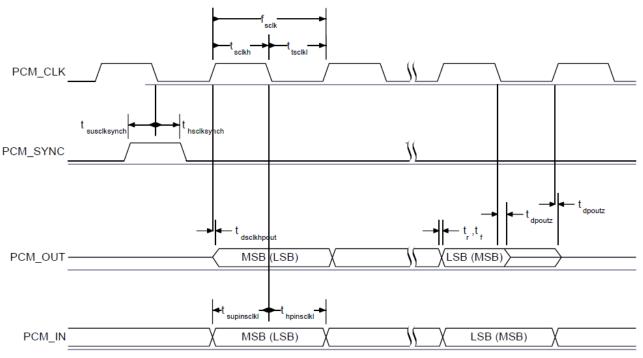

| Figure 18: I <sup>2</sup> S Mode Digital Audio Interface             | _39    |

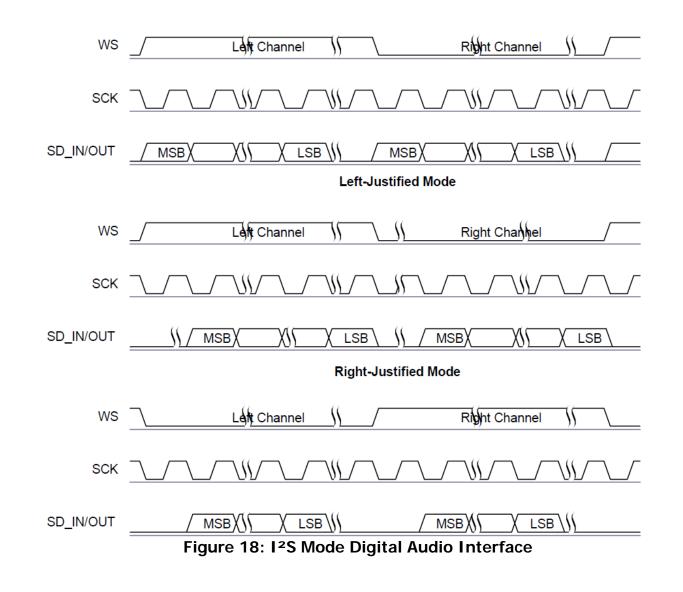

| Figure 19: Digital Audio Interface Slave Timing                      | _40    |

| Figure 20: Digital Audio Interface Master Timing                     | _41    |

| Figure 21: NEMO Example Application Circuit; No External Slow Clock  | Source |

|                                                                      | _48    |

| Figure 22: NEMO Example Application Circuit; External Slow Clock     | Source |

|                                                                      | _49    |

| Figure 23: NEMO Mechanical Drawing                                   | _50    |

Solutions for a Real Time World

Datasheet

## LIST OF TABLES

| TABLE 1: NEMO PIN FUNCTIONS                                | 12       |

|------------------------------------------------------------|----------|

| TABLE 2: ABSOLUTE MAXIMUM RATINGS                          | 13       |

| TABLE 3: RECOMMENDED OPERATING CONDITIONS                  | 13       |

| TABLE 4: RF CHARACTERISTICS                                | 14       |

| TABLE 5: EXTERNAL SLOW CLOCK CHARACTERISTICS               | 14       |

| TABLE 6: PCM TIMING TABLE                                  | 32       |

| TABLE 7: PSKEY_PCM_LOW_JITTER_CONFIG DESCRIPTION           | 36       |

| TABLE 8: PSKEY_PCM_CONFIG32 DESCRIPTION                    | 36       |

| TABLE 9: ALTERNATIVE FUNCTIONS OF THE DIGITAL AUDIO BUS II | NTERFACE |

| ON THE PCM INTERFACE                                       | 38       |

| TABLE 10: PSKEY_DIGITAL_AUDIO_CONFIG                       | 38       |

| TABLE 11: DIGITAL AUDIO INTERFACE SLAVE TIMING             | 40       |

| TABLE 12: DIGITAL AUDIO INTERFACE MASTER TIMING            | 41       |

| TABLE 13: OPERATING POWER CONSUMPTION FIGURES              | 42       |

| TABLE 14: PEAK CURRENT                                     | 43       |

| TABLE 15: BOOT PSKEY LIST                                  | 46       |

| TABLE 16: REFERENCE DOCUMENTATION                          | 51       |

Datasheet

Solutions for a Real Time World

### **PRODUCT INTRODUCTION**

The Nemo Bluetooth radio module enables Bluetooth functionality to any hosted system. Nemo supports Bluetooth version 2.1 with Enhanced Data Rate mode for up to 3Mbps throughput. Nemo's small module footprint and low power consumption makes it attractive for small, handheld, battery powered devices for short range wireless communications. Bluetooth is a cable replacement radio technology. The advanced Bluetooth protocol stack adds seamless, secure, adhoc, point to multi-point communications between other Bluetooth enabled devices regardless of manufacturer. Bluetooth enables personal area networks and short range communications between devices such as portable handhelds, personal computers, embedded devices and industrial communication devices.

### **FEATURES AND BENEFITS**

- Bluetooth v2.1+EDR compliant

- CSR BlueCore 6 ROM

- 2.40-2.480 GHz FHSS Radio

- Max Data Rate 3Mbps

- ±10PPM Crystal Oscillator Included

- 4Mbit High Speed UART Interface

- Single 3.3V Power Supply

- Bluetooth Co-existence Support with 802.11

- Deep Sleep Mode of 40µA With Fast Wake-up

### Solutions for a Real Time World

Datasheet

### Applications

- Short Range Radio Systems

- Point-to-Point Systems

- Point-to-Multi-Point Systems

- Cable Replacement

- Portable Devices

- Mobile Phones

- Headsets

- Hand Free Kits

- Personal Computers

- Laptops

- Personal Hand Handhelds

- Remote Controls

- Mouse

- Keyboards

- Human Interface Devices (HID)

- Embedded Devices

- Asset Tracking

- Barcode Scanners

- Data Acquisition Devices

#### Solutions for a Real Time World

# **NEMO Bluetooth Radio Module**

Datasheet

## **PRODUCT DESCRIPTION**

### **NEMO Module**

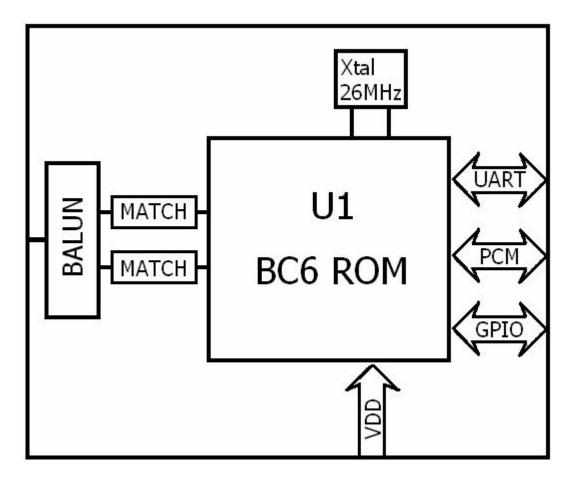

The Nemo module is a complete 2.4GHz radio transceiver operating in the license free ISM (Industrial, Scientific and Medical) band. The Nemo module has CSR's BlueCore 6 ROM Bluetooth solution. The CSR BlueCore 6 ROM is a single-chip radio and baseband IC for Bluetooth 2.4GHz systems including enhanced data rate (EDR) to 3Mbps. With the on-chip CSR Bluetooth software stack, it provides a fully compliant Bluetooth v2.1 + EDR specification system for data and voice communications. The module dimensions measure  $6.5mm \times 5.5mm \times 1.5mm$ . A single 3.3V power supply input, single ended RF output/input, and a low 26 pin count makes the NEMO module easy to interface with.

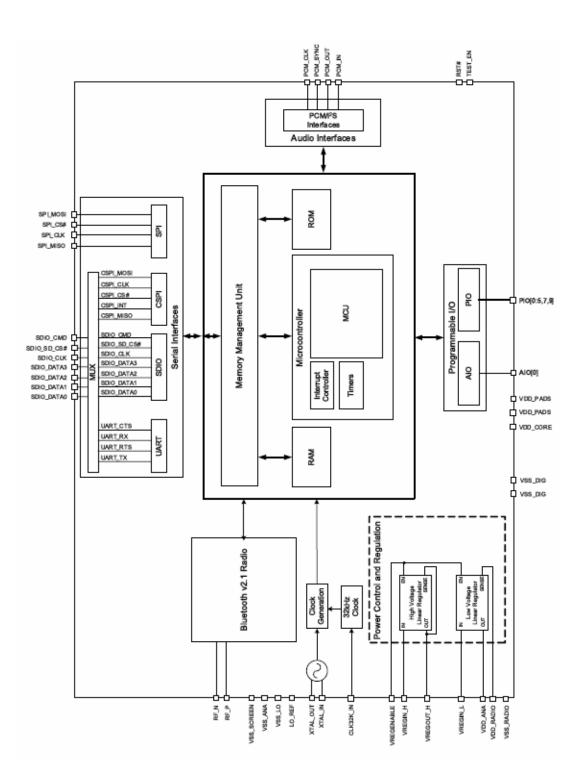

### CSR BlueCore 6 ROM Transceiver IC

BlueCore<sup>™</sup>6-ROM is a single-chip radio and baseband IC for Bluetooth 2.4 GHz systems including enhanced data rates (EDR) to 3Mbits/s. With the on-chip CSR Bluetooth software stack, it provides a fully compliant Bluetooth system to v2.1 of the specification for data and voice communications.

BlueCore6-ROM has been designed to reduce the number of external components required which ensures production costs are minimized. BlueCore6-ROM includes the AuriStream baseband CODEC, which offers significant power reduction over the CVSD based system when used at both ends of the link. The device incorporates auto-calibration and built-in self-test (BIST) routines to simplify development, type approval and production test. All hardware and device firmware is fully compliant with the Bluetooth v2.1 +EDR specification (all mandatory and optional features). To improve the performance of both Bluetooth and 802.11b/g co-located systems a wide range of coexistence features are available including a variety of hardware signaling: basic activity signaling and Intel WCS activity and channel signaling.

Solutions for a Real Time World

Datasheet

### **Functional Block Diagrams**

Figure 1: NEMO Module Block Diagram

### Solutions for a Real Time World

Datasheet

### Figure 2: CSR BlueCore 6 ROM Block Diagram

Re-Tek - 1573 94539 support@unigen.com http://www.unigen.com Copyright Unigen Corporation, 2008 45388 Warm Springs Blvd. Fremont, CA

# PIN ASSIGNMENT

Datasheet

### 16 18 20 19 $\frac{17}{17}$ 5 4 Ω, 21 R 2 23 Ē 24 10 23 σ 26 ω ഥ CO. 4

Figure 3: NEMO Module Pin Locations

Solutions for a Real Time World

## NEMO Bluetooth Radio Module Datasheet

## **PIN FUNCTIONS**

| CTRL_RTS_N<br>T_WAKE_P<br>ST_WAKE_P<br>GND<br>CTRL_RXD_N<br>CTRL_TXD_N<br>OTH_TX_CONFIRM<br>OTH_TX_REQUEST<br>OOTH_STATUS<br>GND<br>ANT_OUT<br>GND | Output<br>Input<br>Output<br><br>Input<br>Output<br>Input<br>Output<br>Output<br><br>Output | UART RTS<br>Module wakeup<br>Host device wakeup<br>Ground Reference<br>UART RXD<br>UART TXD<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ST_WAKE_P<br>GND<br>CTRL_RXD_N<br>CTRL_TXD_N<br>OTH_TX_CONFIRM<br>OTH_TX_REQUEST<br>OOTH_STATUS<br>GND<br>ANT_OUT<br>GND                           | Output<br><br>Input<br>Output<br>Input<br>Output<br>Output<br>                              | Host device wakeup<br>Ground Reference<br>UART RXD<br>UART TXD<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference                              |

| GND<br>CTRL_RXD_N<br>CTRL_TXD_N<br>DTH_TX_CONFIRM<br>DTH_TX_REQUEST<br>TOOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                       | <br>Input<br>Output<br>Input<br>Output<br>Output<br>                                        | Ground Reference<br>UART RXD<br>UART TXD<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference                                                    |

| CTRL_RXD_N<br>CTRL_TXD_N<br>DTH_TX_CONFIRM<br>DTH_TX_REQUEST<br>OOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                               | Input<br>Output<br>Input<br>Output<br>Output<br>                                            | UART RXD<br>UART TXD<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference                                                                        |

| CTRL_TXD_N<br>DTH_TX_CONFIRM<br>DTH_TX_REQUEST<br>OOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                                             | Output<br>Input<br>Output<br>Output<br>                                                     | UART TXD<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference                                                                                    |

| DTH_TX_CONFIRM<br>DTH_TX_REQUEST<br>TOOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                                                          | Input<br>Output<br>Output<br>                                                               | Wi-Fi Coexistence signalWi-Fi Coexistence signalWi-Fi Coexistence signalGround Reference                                                                                                            |

| DTH_TX_REQUEST<br>OOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                                                                             | Output<br>Output<br>                                                                        | Wi-Fi Coexistence signal<br>Wi-Fi Coexistence signal<br>Ground Reference                                                                                                                            |

| OOTH_STATUS<br>GND<br>ANT_OUT<br>GND                                                                                                               | Output<br>                                                                                  | Wi-Fi Coexistence signal<br>Ground Reference                                                                                                                                                        |

| GND<br>ANT_OUT<br>GND                                                                                                                              |                                                                                             | Ground Reference                                                                                                                                                                                    |

| ANT_OUT<br>GND                                                                                                                                     | <br>Output                                                                                  |                                                                                                                                                                                                     |

| GND                                                                                                                                                | Output                                                                                      |                                                                                                                                                                                                     |

|                                                                                                                                                    |                                                                                             | Antenna Output                                                                                                                                                                                      |

|                                                                                                                                                    |                                                                                             | Ground Reference                                                                                                                                                                                    |

| _PCM_CLK_P                                                                                                                                         | Input                                                                                       | PCM_CLK                                                                                                                                                                                             |

| PCM_RXD_P                                                                                                                                          | Input                                                                                       | PCM RXD serial input                                                                                                                                                                                |

| _PCM_TXD_P                                                                                                                                         | Output                                                                                      | PCM TXD serial output                                                                                                                                                                               |

| PCM_SYNC_P                                                                                                                                         | Input                                                                                       | PCM SYNC                                                                                                                                                                                            |

| GND                                                                                                                                                |                                                                                             | Ground Reference                                                                                                                                                                                    |

| FOOTH_LPO_IN                                                                                                                                       | Input                                                                                       | 32.768kHz low power<br>clock input                                                                                                                                                                  |

| OOTH_RESET_N                                                                                                                                       | Input                                                                                       | Module Reset                                                                                                                                                                                        |

| REG_CTRL_P                                                                                                                                         | Input                                                                                       | Internal regulator<br>enable/disable                                                                                                                                                                |

| GND                                                                                                                                                |                                                                                             | Ground Reference                                                                                                                                                                                    |

| +VBT_IO                                                                                                                                            | Input                                                                                       | I/O Power Supply                                                                                                                                                                                    |

| +VBT                                                                                                                                               | Input                                                                                       | Main supply input                                                                                                                                                                                   |

| +VRF                                                                                                                                               |                                                                                             | Bypass Capacitor connection for RF VDD.                                                                                                                                                             |

| GND                                                                                                                                                |                                                                                             | Ground Reference                                                                                                                                                                                    |