1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## PCF7941ATJ

# PCF7341ATJ

# Security Transponder and RISC Controller (STARC 2XLite)

Product Specification CONFIDENTIAL

2013 Oct 15

#### CONTENT

|     |      |                                 | - |

|-----|------|---------------------------------|---|

| 1   |      | ATURES                          |   |

| 2   | GE   | NERAL DESCRIPTION               |   |

| 3   | OR   | DERING INFORMATION              | 4 |

| 4   | ΤY   | PICAL APPLICATION               | 4 |

| 5   | BL   | OCK DIAGRAM                     | 5 |

| 6   | QU   | JICK REFERENCE DATA             | 6 |

|     | 6.1  | Transponder Operation           | 6 |

|     | 6.2  | RISC Controller and Peripherals | 6 |

| 7   | PIN  | NNING                           | 7 |

| 8   | FU   | NCTIONAL DESCRIPTION            | 9 |

|     | 8.1  | LF Field Power On Reset         |   |

| 9   | EE   | PROM CONTENT AT DELIVERY        |   |

| 10  | LIN  | /ITING VALUES                   |   |

| 11  | DE   | VICE CHARACTERISTICS            |   |

|     | 11.1 | Electrical Characteristics      |   |

|     | 11.2 | Timing Characteristics          |   |

|     | 11.3 | Mechanical Characteristics      |   |

| 12  | TE   | ST SETUP                        |   |

| 13  |      | LATED DOCUMENTS                 |   |

| 14  | DE   | VELOPMENT TOOLS                 |   |

| 15  |      | VISION HISTORY                  |   |

| 16  |      | GAL INFORMATION                 |   |

|     | 16.1 | Data sheet status               |   |

|     | 16.2 | Definitions                     |   |

|     | 16.3 | Disclaimers                     |   |

| 17  |      | ntact information               |   |

| . / | 00   |                                 |   |

PCF7x41ATJ

#### **1 FEATURES**

- Single chip Security Transponder and Remote Keyless

Entry solution

- RISC programmable device features

- Up to seven Keyless Entry command buttons

- 512 Byte EEPROM for extended data storage

- 32 bit unique device and product type identification

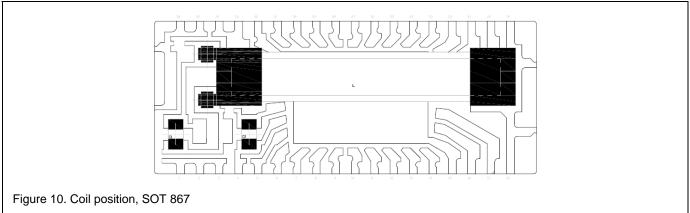

- Package integrated Transponder LF coil

#### Security Transponder

- Transponder operation like PCF7936 family

- Fast mutual authentication, 39ms (48 bit Secret Key)

- EEPROM read/write protection capability

- RISC programmable transponder extensions

#### **Calculation Unit**

- Hardwired security algorithm

- 48 (96) bit Secret Key

- **RISC Controller and Peripherals**

- 8 Bit RISC Architecture (MRK II)

- 4 kByte E-ROM respectively ROM (application)

- 4 kByte ROM (device firmware and library functions)

- 128 Byte User RAM

- 11 general purpose I/O (incl. 7 command button inputs)

- Two 8 Bit Timer/Counter

- Optional external clock input for Timer/Counter

- Watchdog

- Single level interrupt architecture

- On-chip RC Oscillator (< ±8%)

- Short instruction execution time (as fast as 0.5 µs)

- Programmable battery low detection

- Low power consumption RUN: 300 μA, IDLE: 20μA, PD: 100 nA

- Single Lithium cell operation, 2.1V to 3.6V

#### 2 GENERAL DESCRIPTION

The PCF7x41ATJ is a high performance single chip Security Transponder and RISC Controller, ideally suited for automotive applications with combined vehicle Immobilization and Remote Keyless Entry functions.

Unless other products, the device comes with a package integrated Transponder LF coil to operate as Security Transponder and enable contactless communication with the base station. Neither other external components nor an additional battery supply is needed. The basic transponder operation is emulated utilizing the on-chip RISC and may feature a customized functions or may utilize the built in Transponder Library, that offer HT2 functional compatible operation (e.g. PCF7936), except for the ReadOnly mode.

The Security Transponder operation features secure contactless authentication, employing a Secret Key and a random number in order to cipher any communication between the device and the base station. The device features a factory programmed unique serial number that also serves as product type identification.

Device operation is controlled by a ROM or E-ROM (FLASH like features) based RISC Controller, powered by NXP' low power 8-Bit MICRO RISC KERNEL (MRK II). 11 general purpose I/Os are provided for command buttons, LED, or control of an external RF transmitter/transceiver circuitry.

In case of Remote Keyless Entry applications, the application program may accomplish rolling code generation using the hardwired Calculation Unit. The Calculation Unit may operate in standard HITAG2 (48 bit Shift Register) or Enhanced mode (64 bit Shift Register).

The RISC employs a 2 stage pipeline architecture in order to execute an instruction in a single clock cycle. Device timing is derived from an on-chip low tolerance RC Oscillator that provides a programmable system clock, with a frequency up to 2 MHz. The system clock may also be derived from the transponder interface, e.g. LF field clock.

Depending on the operation mode, the RISC is powered from the external battery or derives its power supply by inductive coupling to the LF field generated by the base station.

The PCF7x41ATJ incorporates an advanced power management that supports battery voltage measurement. For increased battery lifetime the device quiescent current is minimized in POWER-OFF state by disconnecting the battery from most of the internal circuitry.

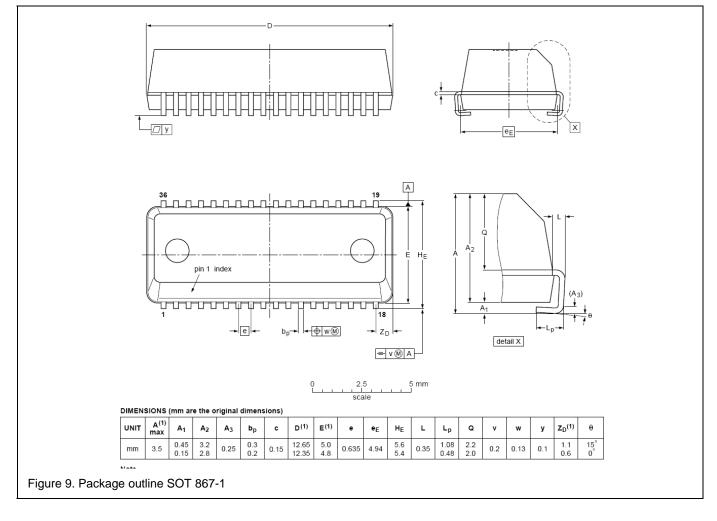

The device comes in a 36 pin Leaded Stick Package (LSP). The device is available as E-ROM (FLASH like features) and ROM coded product. In case of the E-ROM version, in-circuit program download and debugging is supported.

For further detailed descriptions about features, functional blocks and known anomalies not related to the integrated Transponder functionality, please refer to datasheet PCF7x41A compiled for the SSOP and TSSOP package.

PCF7x41ATJ

#### **3 ORDERING INFORMATION**

| EXTENDED            |       | PACKAGE              |                 | TEMPERATURE    |

|---------------------|-------|----------------------|-----------------|----------------|

| TYPE NUMBER         | NAME  | DESCRIPTION          | OUTLINE VERSION | RANGE (°C)     |

| PCF7941ATJ/CA1B00E0 | SOJ36 | Leaded Stick Package | SOT867-1        | -40°C to +85°C |

| PCF7941ATJ/CA1Brrff | SOJ36 | Leaded Stick Package | SOT867-1        | -40°C to +85°C |

| PCF7341ATJ/C0ABrrff | SOJ36 | Leaded Stick Package | SOT867-1        | -40°C to +85°C |

Note

- PCF7941ATJ/CA1B00E0 represents the E-ROM product for development and applications with low quantities. The customer shall perform E-ROM programming and EEPROM initialization. The Monitor and Download Interface (MSDA/MSCL) supports E-ROM download and ERASE/WRITE as fast as 700ms for 4 kByte.

- 2. PCF7941ATJ/CA1Brrff represents a customized E-ROM product. Under certain conditions NXP Semiconductors may perform E-ROM programming with a customer application code and/or customer EEPROM pattern. The actual customer application code and customer EEPROM fabkey is specified by a 2 digit code at location marked "ff". The ROM code is specified by a 2 digit code at location marked "rr"

- 2. PCF7341ATJ/C0ABrrff represents the ROM coded product for high volume applications. The actual customer ROM code and customer EEPROM fabkey is specified by a 2 digit code at location marked "rr", respectively "ff"

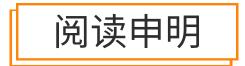

#### **4 TYPICAL APPLICATION**

## PCF7x41ATJ

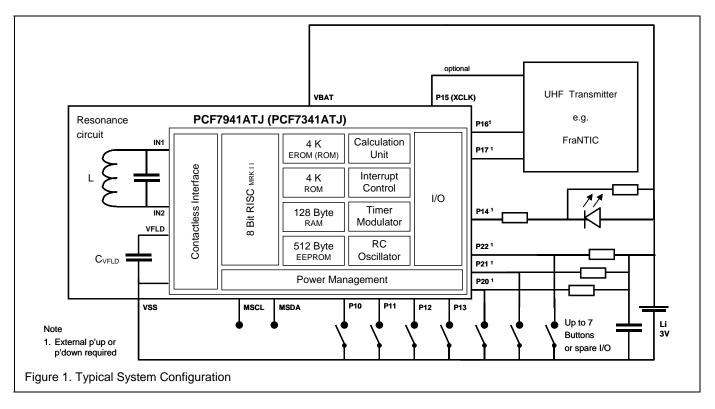

#### 5 BLOCK DIAGRAM

The PCF7x41ATJ features a high degree of integration and incorporates the chip, coil and capacitors assembled in a leaded stick package, see Figure 2.

#### Package

- L/C Resonance Circuit

- Rectified LF Filed supply blocking capacitor

#### **Contactless Interface**

- Rectifier and Voltage Limiter

- Modulator

- Clock Recovery

- Demodulator

- LF Field Detection

#### **Calculation Unit**

HT2 (48 bit) and HT3 (96 bit) Algorithm

#### **Power Management**

- Supply Switch Logic

- Wake Up Sense (Button I/O)

- Watchdog Timer

- Reset Logic

#### **RISC Controller and Peripherals**

- 8 Bit RISC (MRK II)

- ROM (Firmware)

- E-ROM (Application program)

- RAM

- EEPROM

- Interrupt Control

- Timers / Counters

- I/O Ports

- Programmable Voltage Comparator

- System Clock (including on-chip RC oscillator)

## PCF7x41ATJ

#### 6 QUICK REFERENCE DATA

#### 6.1 Transponder Operation

| PARAMETER              | VALUE                                 | UNIT   |  |

|------------------------|---------------------------------------|--------|--|

| Carrier frequency      | 125                                   | kHz    |  |

| Data rate              |                                       |        |  |

| - read                 | 4.0                                   | kbit/s |  |

| - write                | 5.2                                   | kbit/s |  |

| Data coding            |                                       |        |  |

| - read                 | Manchester or Bi-Phase                |        |  |

| - write                | Binary Pulse Length Modulation (BPLM) |        |  |

| Data transmission mode | Half-Duplex                           |        |  |

| Modulation             | Amplitude Shift Keying (ASK)          |        |  |

#### 6.2 RISC Controller and Peripherals

| Р                      | ARAMETER                                                            | VALUE                                     | UNIT |  |

|------------------------|---------------------------------------------------------------------|-------------------------------------------|------|--|

| Operating supply volta | ge (RISC)                                                           | 2.1 - 3.6                                 | V    |  |

| Power-down current (ty | ypical)                                                             | 400                                       | nA   |  |

| ROM (Firmware - Sys    | tem ROM)                                                            | 4 K                                       | Byte |  |

| E-ROM (Application pr  | ogram)                                                              | 4 K                                       | Byte |  |

| RAM                    |                                                                     | 128                                       | Byte |  |

| EEPROM                 |                                                                     | 512                                       | Byte |  |

| General purpose /O     |                                                                     | 11                                        |      |  |

| Operating speed, as de | erived from on-chip RC oscillator                                   | 0.125 - 2                                 | MHz  |  |

| Special Features       | EEPROM Erase/Write over full operating voltage range (2.1 to 3.6 V) |                                           |      |  |

|                        | Full control about Contact                                          | ctless LF Interface                       |      |  |

|                        | Programmable voltage of                                             | comparator for battery voltage monitoring |      |  |

|                        | PWM generation                                                      |                                           |      |  |

|                        | Watchdog timer                                                      |                                           |      |  |

|                        | Up to 7 dedicated Wake                                              | -Up button inputs                         |      |  |

| Calculation Unit       | Features HT2 (48 bit) or                                            | Features HT2 (48 bit) or HT3 (96 bit)     |      |  |

|                        | Supports Pseudo Random Number generation (Rolling Code)             |                                           |      |  |

PCF7x41ATJ

## Security Transponder and RISC Controller (STARC 2XLite)

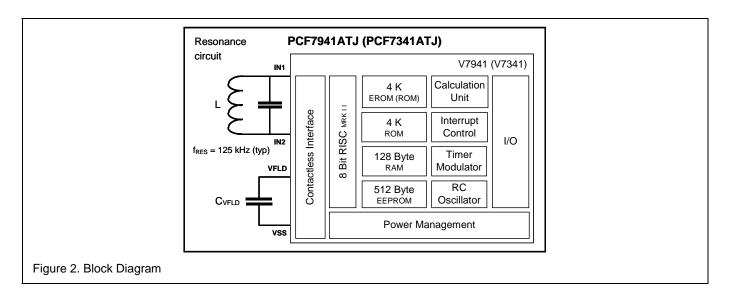

#### 7 PINNING

Table 1. Pin Assignment

| FUNCTION | DESCRIPTION                                                                    | PIN | NOTE |

|----------|--------------------------------------------------------------------------------|-----|------|

| i.c. A   | Internally connected (node reference A)                                        | 1   | 2    |

| i.c. A   | Internally connected (node reference A)                                        | 2   | 2    |

| i.c. A   | Internally connected (node reference A)                                        | 3   | 2    |

| VSS      | Common Ground digital section (Battery neg. Terminal)                          | 4   |      |

| n.c.     | Not connected                                                                  | 5   | 1    |

| n.c.     | Not connected                                                                  | 6   | 1    |

| n.c.     | Not connected                                                                  | 7   | 1    |

| P20      | General purpose I/O, Wake Up sense and Digital modulator output                | 8   |      |

| P16      | General purpose I/O, voltage comparator input                                  | 9   |      |

| P17      | General purpose I/O, Digital modulator outpu                                   | 10  |      |

| P15      | General purpose I/O and external clock input                                   | 11  |      |

| P10      | General purpose I/O with internal pull-up, Wake Up sense                       | 12  |      |

| P21      | General purpose I/O, Wake Up sense and Timer 1 Capture input / Interrupt input | 13  |      |

| n.c.     | Not connected                                                                  | 14  |      |

| i.c. B   | Internally connected (node reference B)                                        | 15  | 3    |

| n.c.     | Not connected                                                                  | 16  |      |

| MSDA     | ROM Monitor Serial Data with internal pull-up                                  | 17  | 4    |

| i.c. C   | Internally connected (node reference C)                                        | 18  | 2    |

| i.c. C   | Internally connected (node reference C)                                        | 19  | 2    |

| MSCL     | ROM Monitor Serial Clock Output                                                | 20  |      |

| n.c.     | Not connected                                                                  | 21  |      |

| n.c.     | Not connected                                                                  | 22  |      |

| P22      | General purpose I/O, Wake Up sense and Timer 1 Compare output (PWM)            | 23  |      |

| P11      | General purpose I/O with internal pull-up and Wake Up sense                    | 24  |      |

| P12      | General purpose I/O with internal pull-up and Wake Up sense                    | 25  |      |

| P13      | General purpose I/O with internal pull-up and Wake Up sense                    | 26  |      |

| TEST     | Reserved                                                                       | 27  | 1    |

| TEST     | Reserved                                                                       | 28  | 1    |

| TEST     | Reserved                                                                       | 29  | 1    |

| VBAT     | Battery Supply Voltage digital section (Battery pos. Terminal)                 | 30  |      |

| P14      | General purpose I/O                                                            | 31  |      |

| i.c. B   | Internally connected (node reference B)                                        | 32  | 3    |

| i.c. F   | Internally connected (node reference F)                                        | 33  | 2    |

| i.c. F   | Internally connected (node reference F)                                        | 34  | 2    |

| i.c. E   | Internally connected (node reference E)                                        | 35  | 2    |

| i.c. E   | Internally connected (node reference E)                                        | 36  | 2    |

#### Note

1. Reserved for device test purposes. Required to be left unconnected or connected to VSS

2. Internally connected to another pin and not connected to the chip.

3. Internally connected to another pin and not connected to the chip, but connected to the chip die attach.

4. MSCL is an output and must be left unconnected in the application. MSDA features an on-chip pull-up to VBAT, and may be left open or terminated to VBAT, as desired. For details please refer to the 'PCF7941 Monitor and Download Interface' (see 13 RELATED DOCUMENTS).

CONFIDENTIAL

#### Product Specification

## PCF7x41ATJ

#### 8 FUNCTIONAL DESCRIPTION

The PCF7x41ATJ incorporates Security Transponder and Remote Keyless Entry features that are specified in detail by the data sheet PCF7x41 and the corresponding ROM Library Description; see section 13.

#### 8.1 LF Field Power On Reset

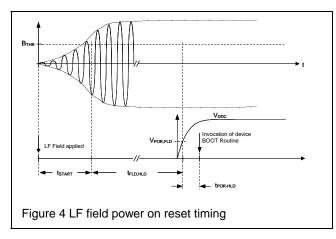

When the transponder enters a LF Field a rectifier circuitry becomes operational and the rectified voltage develops. The LF Field has to be present for at least 2ms ( $t_{FLD,HLD}$ ) before this supply voltage is passed on to become the transponder supply voltage ( $V_{DDC}$ ). As soon as the supply voltage ( $V_{DDC}$ ) exceeds the LF Field Power-On Reset threshold voltage ( $V_{POR,FLD}$ ) the device performs a chip reset and starts its initialization sequence by executing its boot routine, see Figure 4.

Subsequently, the transponder is muted and does not respond to any command until termination of the device boot sequence. The startup time,  $t_{START}$ , depends on the base station configuration, the resonance circuit properties and the system coupling factor, however, is small compared with the LF Field hold time ( $t_{FLD,HLD}$ ).

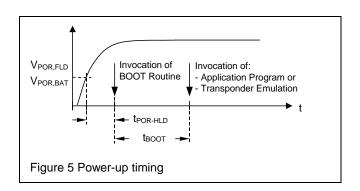

Regardless of the supply condition, once the supply voltage (VDD) exceeds the Power On Reset threshold voltage (VPOR,BAT respectively VPOR,FLD), POR becomes low. After a short delay (TPOR,HLD), the flip-flop is forced into latch state freezing the supply switch state and the RISC Controller becomes operational. Program execution commences starting with the BOOT Routine, before the application Program or Transponder Emulation is being invoked, see Figure 5

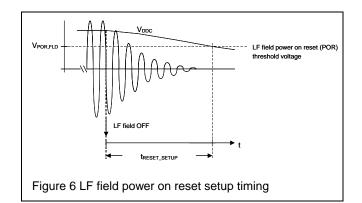

In order to force a LF Field Power-On Reset and proper device initialization at any time, the LF field OFF condition must be applied for at least  $t_{RESET,SETUP}$ , in order to ensure that the INTERNAL device supply voltage,  $V_{DDc}$ , drops below the threshold voltage ( $V_{POR,FLD}$ ), see Figure 6.

#### 9 EEPROM CONTENT AT DELIVERY

The PCF7x41ATJ EEPROM content is initialized during device manufacturing, according to Table 2.

However the EEPROM content may be modified as desired by the application, except for the page 0 block 0 which holds the Identifier (IDE) and serves the function of a serial number and product type ID.

for the PCF7x41ATJ. For system compatibility reasons, the same product type Identifier is used by PCF7x21 (KEECOR).

2. Locations marked 'X' are undefined and may hold any pattern.

Consequently, the device is configured for PCF7936 (HITAG2) transponder emulation and set to INIT mode, providing full support regarding the Monitor and Download Interface.

Table 2. EEPROM Content Upon Delivery

|     | Content [HEX] | Page     | Note |

|-----|---------------|----------|------|

|     | ХХ ХХ ХХ 6Х   | 0        | 1    |

|     | 4D 49 4B 52   | 1        |      |

|     | 00 00 4F 4E   | 2        |      |

|     | 00 AA 48 54   | 3        |      |

|     | XX XX XX XX   | 4 to 126 |      |

|     | X6 XX 80 00   | 127      |      |

| MSB | LSB           |          |      |

MSB

```

Note

```

1. Bit 7 to 4 of this page (Identifier) serve the function of a product type (application) identifier and are set to '0110'

#### **10 LIMITING VALUES**

All values are in accordance with Absolute Maximum Rating System (IEC 134)

| PARAMETER                                                             | MIN | МАХ   | UNIT |

|-----------------------------------------------------------------------|-----|-------|------|

| Operating temperature range                                           | -40 | +85   | °C   |

| Storage temperature range                                             | -55 | +125  | °C   |

| Reflow soldering peak temperature, Note 2                             |     | 232,5 | °C   |

| Package Mositure Sensitivity Level (MSL)                              |     | 3     |      |

| Magnetic flux density (resistance against magnetic pulses)            |     | 0.2   | Т    |

| Latch-up current, Note 3                                              | 100 |       | mA   |

| ESD, human body model, Note 4                                         | 2   |       | kV   |

| ESD, human body model for pins VBAT and VSS, Note 4                   | 4   |       | kV   |

| ESD, machine model, Note 5                                            | 250 |       | V    |

| ESD CDM, Field Induced Model for corner pins, Note 6                  | 750 |       | V    |

| ESD CDM, Field Induced Model for all pins besides corner pins, Note 6 | 650 |       | V    |

| Vibration<br>- 10 - 2000Hz<br>- 3.axis<br>- IEC 68-2-6, Test Fc       |     | 10    | g    |

| Shock<br>- 3.axis<br>- IEC 68-2-27, Test Ea                           |     | 1500  | g    |

| Mechanical stress (F <sub>MAX</sub> ), Note 1                         |     | 10    | N    |

Note

- 1.  $F_{MAX}$  is specified as indicated in Test Setup, section 12.

- 2. Reflow stress levels in accordance with JEDEC 22 A113D, excluding limitation of peak temperature.

- 3. According to JEDEC, JESD 17.

- 4. According to JEDEC, JESD 22-A114.

- 5. According to JEDEC, JESD 22-A115.

- 6. According to JEDEC, JESD 22-C101.

## PCF7x41ATJ

#### **11 DEVICE CHARACTERISTICS**

#### **11.1 Electrical Characteristics**

Tamb = -40 to +85°C,  $f_{SYS}$  = 125kHz,  $T_O$  = 1/ $f_{SYS}$ . Unless otherwise specified

| SYMBOL            | PARAMETER                                                                                   | CONDITION                                                    | MIN | ТҮР | MAX | UNIT             |

|-------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|------------------|

| Operating         | Conditions                                                                                  |                                                              |     |     |     |                  |

| C <sub>VFLD</sub> | Supply blocking capacitor                                                                   |                                                              |     | 22  |     | nF               |

| L                 | Transponder coil inductance                                                                 |                                                              |     | 4.8 |     | mH               |

| f <sub>RES</sub>  | Resonance frequency                                                                         |                                                              | 119 |     | 131 | kHz              |

| BW                | Bandwidth                                                                                   |                                                              | 2.3 |     |     | kHz              |

| B <sub>THR</sub>  | Magnetic flux density,<br>Read direction                                                    |                                                              | 60  |     | 400 | μT <sub>PP</sub> |

| B <sub>PRG</sub>  | Magnetic flux density for EEPROM programming                                                | m = 0,95, T <sub>WRP</sub> = 8 T <sub>O</sub><br>Note 1      | 60  |     | 400 | μT <sub>PP</sub> |

| B <sub>AUT</sub>  | Magnetic flux density for device authentication                                             | m = 0,95, T <sub>WRP</sub> = 8 T <sub>O</sub><br>Note 1      | 60  |     | 400 | μT <sub>PP</sub> |

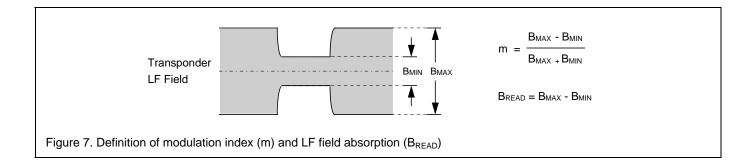

| B <sub>READ</sub> | LF field absorption in read direction, Note 1                                               | $B_{FIELD} = 60 \ \mu T_{PP}$                                | 4.5 |     |     | μT <sub>PP</sub> |

| MI <sub>PRG</sub> | Minimum modulation index (m)<br>Write direction (device programming and<br>authentication). | $B_{FIELD} = 60 \ \mu T_{PP}, T_{WRP} = 8 \ T_{O}$<br>Note 1 |     |     | 95  | %                |

Note

- 1. Modulation index (m) and LF Field absorption ( $B_{READ}$ ) are defined according to Figure 7.

- 2. Parameters are measured with the Scemtech test equipment STM-1 in a Helmholtz arrangement according to section 12.

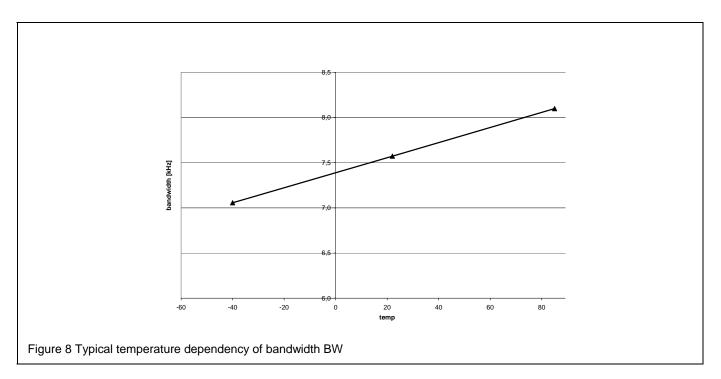

- 3. Typical temperature dependency of bandwidth BW shown in Figure 8.

## PCF7x41ATJ

#### 11.2 Timing Characteristics

Tamb = -40 to +85°C,  $f_{SYS}$  = 125kHz,  $T_O$  = 1/ $f_{SYS}$ . Unless otherwise specified

| SYMBOL                          | SYMBOL PARAMETER CONDITION         |  | MIN | ТҮР | MAX | UNIT |

|---------------------------------|------------------------------------|--|-----|-----|-----|------|

| LF Field Power On Reset, Note 1 |                                    |  |     |     |     |      |

| t <sub>FLD,HLD</sub>            | LF Field hold time                 |  | 250 |     |     | Τo   |

| t <sub>POR-HLD</sub>            | Power On Reset Hold time           |  |     | 200 | 480 | μS   |

| t <sub>RESET,SETUP</sub>        | LF Field Power On Reset setup time |  | 11  |     |     | ms   |

Notes

1. Values based on PCF7x41A PQP with additional safety margin considering application of LSP resonance circuit.

**NXP Semiconductors**

## Security Transponder and RISC Controller (STARC 2XLite)

#### **11.3 Mechanical Characteristics**

#### **12 TEST SETUP**

Device characteristics are measured according to the test setups given below.

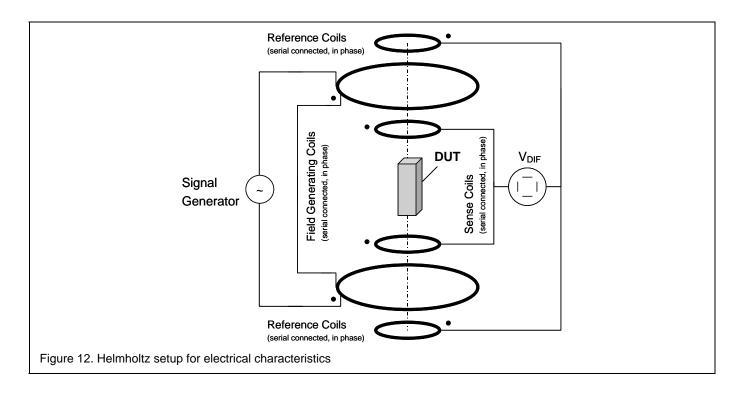

Electrical characteristics are measured in a Helmholtz arrangement that generates an almost homogenous magnetic field at the position of the device under test (transponder); see Figure 12. The sense coils detect the absorption modulation induced by the transponder, whereas the reference coils sense the magnetic flux generated by the field generating coils only. The voltage difference measured between the sense coils and reference coils is proportional to the magnetic field absorption induced by the transponder.

**F**MAX

DUT

PCF7x41ATJ

#### **13 RELATED DOCUMENTS**

| Туре       | Name / Reference                       | Description                    |

|------------|----------------------------------------|--------------------------------|

| Data Sheet | PCF7941 / PCF7341                      | Product Specification          |

| Data Sheet | PCF7x41 ROM Library                    | Implementation and Description |

| Data Sheet | PCF7941 Monitor and Download Interface | Functional Description         |

#### 14 DEVELOPMENT TOOLS

| Reference | Name                                                            | Description                                                        |  |

|-----------|-----------------------------------------------------------------|--------------------------------------------------------------------|--|

| OM6710    | OM6710 RIDE Software development suite                          |                                                                    |  |

| OM6713    | Universal Download and Debug Board<br>(U-DDB)                   | Hardware and software Interface between host PC and target device. |  |

| OM6714    | EWMRKII (Embedded workbench for<br>MRKII microcontroller cores) | New Software development suite with C-compiler and for emulation   |  |

| OM6715    | 2LINK hardware                                                  | USB connection with emulation electronic for OM6714                |  |

#### **15 REVISION HISTORY**

| Revision    | Page | Description                                                                          |  |  |

|-------------|------|--------------------------------------------------------------------------------------|--|--|

| 2006 Apr 24 |      | Objective Specification                                                              |  |  |

| 2006 Jul 19 |      | Editorial changes and correction                                                     |  |  |

|             |      | LIMITING VALUES updated                                                              |  |  |

|             | 11   | + Moisture Sensitivity Level fixed to MSL 2                                          |  |  |

| 2007 Jun 20 | all  | Editorial changes and correction                                                     |  |  |

|             | 11   | + Moisture Sensitivity Level fixed to MSL 3                                          |  |  |

|             |      | Table 11.1      Electrical Characteristics: Magnetic flux density MIN values adapted |  |  |

| 2007 Nov 1  | 9    | nserted Chapter 8.1 LF Field Power On Reset                                          |  |  |

|             |      | Product specification release                                                        |  |  |

| 2011 Aug 10 |      | Editorial changes                                                                    |  |  |

|             | 17   | Jpdate Legal Information.                                                            |  |  |

| 2013 Oct 15 | 4    | Update ORDERING INFORMATION.                                                         |  |  |

## PCF7x41ATJ

#### **16 LEGAL INFORMATION**

#### 16.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                          |

|-----------------------------------|-------------------------------|-------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification or product development |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification                      |

| Product [short] data sheet        | Production                    | This document contains the product specification                                    |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 16.2 Definitions

#### Draft

The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### Short data sheet

A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 16.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use in automotive applications — This NXP Semiconductors product has been qualified for use in automotive applications. The product is not designed, authorized or warranted to be suitable for any other use, including medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customers own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

2013 Oct 15

#### PCF7x41ATJ

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

#### **17 Contact information**

For sales office addresses, please send an email to: <u>salesaddresses@nxp.com</u> For additional information, please visit: <u>http://www.nxp.com</u>

> Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, email to: sales.addresses@www.nxp.com