# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# 96 kHz digital audio interface transmitter

Datasheet - production data

#### **Features**

- Monolithic digital audio interface transmitter

- 3.3 V supply voltage

- Supports:

- AES/EBU, IEC 958

- S/PDIF, & EIAJ CP-340

- Professional and consumer formats

- Parity bits and CRC codes generated

- Transparent mode allows direct connection of STA020 and STA120

## **Description**

The STA020 is a monolithic CMOS device which encodes and transmits audio data according to the AES/EBU, IEC 958, S/PDIF, & EIAJ CP-340 interface standards. It supports 96 kHz sample rate operation.

The STA020 accepts audio and digital data which is then multiplexed, encoded and driven onto a cable.

The audio serial port is double-buffered and capable of supporting a wide variety of formats.

The STA020 multiplexes the channel, user, and validity data directly from the serial input pins with dedicated input pins for the most important channel status bits.

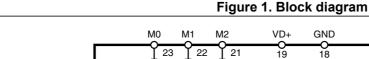

Overview STA020

### 1 Overview

Table 1. Absolute maximum ratings

| Symbol           | Parameter                                     | Value                       | Unit |

|------------------|-----------------------------------------------|-----------------------------|------|

| V <sub>D+</sub>  | DC power supply                               | 4                           | V    |

| V <sub>IND</sub> | Digital input voltage                         | -0.3 to V <sub>D+</sub> 0.3 | V    |

| T <sub>amb</sub> | Ambient operating temperature (power applied) | -20 to +85                  | °C   |

| T <sub>stg</sub> | Storage temperature                           | -40 to 150                  | °C   |

**Table 2. Recommended operating conditions** (GND = 0 V; all voltages with respect to ground)

| Symbol           | Parameter               | Test condition | Min. | Тур. | Max. | Unit |

|------------------|-------------------------|----------------|------|------|------|------|

| $V_{D+}$         | DC voltage              |                | 3    | 3.3  | 3.6  | V    |

| T <sub>amb</sub> | Ambient operating temp. |                | 0    | 25   | 70   | °C   |

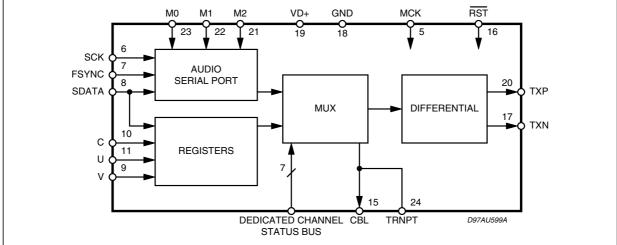

Figure 2. Pin connections (top view)

Table 3. Pin description

| N°        | Pin                      | Function                                                                                                                                                                                                                  |  |  |  |

|-----------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Power sup | Power supply connections |                                                                                                                                                                                                                           |  |  |  |

| 18        | GND                      | Ground.                                                                                                                                                                                                                   |  |  |  |

| 19        | VD+                      | Positive digital power. Nominally +3.3 V.                                                                                                                                                                                 |  |  |  |

| Audio inp | ut interface             |                                                                                                                                                                                                                           |  |  |  |

|           |                          | Serial clock.                                                                                                                                                                                                             |  |  |  |

| 6         | SCK                      | Serial clock for SDATA pin which can be configured (via the M0, M1 and M2 pins) as an input or output and can sample data on the rising or falling edge. As an output, SCK will contain 32 clocks for every audio sample. |  |  |  |

STA020 Overview

Table 3. Pin description (continued)

| N°           | Pin                            | Function                                                                                                                                                                                                                                                                                                              |

|--------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                                | Frame sync.                                                                                                                                                                                                                                                                                                           |

| 7            | FSYNC                          | Delineates the serial data and may indicate the particular channel, left or right, and may be an input or output. The format is based on M0, M1 and M2 pins.                                                                                                                                                          |

| 8            | SDATA                          | Serial data. Audio data serial input pin.                                                                                                                                                                                                                                                                             |

| 21,<br>22,23 | M0, M1, M2                     | Serial port mode select. Selects the format of FSYNC and the sample edge of SCK with respect                                                                                                                                                                                                                          |

| Control pi   | l<br>ns                        | to SDATA.                                                                                                                                                                                                                                                                                                             |

|              |                                | Channel status bit 7/Channel status bit 3                                                                                                                                                                                                                                                                             |

| 1            | <del>C</del> 7/ <del>C</del> 3 | In professional mode, C7 is the inverse of channel status bit 7. In consumer mode, C3 is the inverse of channel status bit 3, C7/C3 are ignored in transparent mode.                                                                                                                                                  |

| 2            | PRO                            | Professional/Consumer select.  Selects between professional mode (PRO low) and consumer mode (PRO high). This pin defines the functionality of the channel status                                                                                                                                                     |

|              |                                | parallel pins. PRO is ignored in transparent mode.                                                                                                                                                                                                                                                                    |

| 3            | C1/FC0                         | Channel status bit 1/Frequency control 0. In professional mode, C1 is the inverse of channel status bit 1. In consumer mode, FC0 and FC1 are encoded versions of channel status bits 24 and 25 (bits 0 and 1 of byte 3). When FC0 and FC1 are both high, CD mode is selected. C1/FC0 are ignored in transparent mode. |

| 4            | <u>C6/C2</u>                   | Channel status bit 6/Channel status bit 2. In professional mode, $\overline{C6}$ is the inverse of channel status bit 6. In consumer mode, $\overline{C2}$ is the inverse of channel status bit 2. $\overline{C6}/\overline{C2}$ are ignored in transparent mode                                                      |

| 9            | V                              | Validity.  Validity bit serial input port. This bit is defined as per the digital audio standards wherein V = 0 signifies the audio signal is suitable for conversion to analog. V = 1 signifies the audio signal is not suitable for conversion to analog, i.e. invalid.                                             |

| 10           | C/SBF                          | Channel status serial input/Subcode frame clock.  In professional and consumer modes this pin is the channel status serial input port. In CD mode this pin inputs the CD subcode frame clock.                                                                                                                         |

| 11           | U                              | User bit. User bit serial input port.                                                                                                                                                                                                                                                                                 |

| 12           | C9/C15                         | Channel status bit 9/Channel status bit 15. In professional mode, $\overline{C9}$ is the inverse of channel status bit 9 (bit 1 of byte 1). In consumer mode, $\overline{C15}$ is the inverse of channel status bit 15 (bit 7 of byte 1). $\overline{C9/C15}$ are ignored in transparent mode.                        |

| 13           | EM1/C8                         | Emphasis 1/Channel status bit 8.  In professional mode, EM0 and EM1 encode channel status bits 2, 3 and 4. In consumer mode, $\overline{C8}$ is the inverse of channel status bit 8 (bit 0 of byte 1). EM1/ $\overline{C8}$ are ignored in transparent mode.                                                          |

Overview STA020

Table 3. Pin description (continued)

| N°         | Pin                                                                                                                                                                                                                                | Function                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14         | Emphasis 0/Channel status bit 9. In professional mode, EM0 and EM1 encode channel status bit and 4. In consumer mode, C9 is the inverse of channel status bit of byte 1). EM0/C9 are ignored in transparent mode.                  |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 15         | CBL/SBC  Channel status block output/Subcode bit clock.  In professional and consumer modes, the channel status block output is high for the first 15 bytes of channel status. In CD mode, this pin outputs the subcode bit clock. |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 16         | RST                                                                                                                                                                                                                                | RST Master reset. When low, all internal counters are reset.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 24         | TRNPT/FC1                                                                                                                                                                                                                          | Transparent mode/Frequency control 1. In professional mode, setting TRNPT low selects normal operation & CBL is an output. Setting TRNPT high allows the STA020 to be connected directly to an STA120. In transparent mode, CBL is an input & MCK must be at 256 Fs. In consumer mode, FC0 and FC1 are encoded versions of channel status bits 24 and 25. When FC0 and FC1 are both high, CD mode is selected. |  |  |  |

| Transmitte | er interface                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 5          | MCK                                                                                                                                                                                                                                | Master clock. Clock input at 128x the sample frequency which defines the transmit timing. In transparent mode MCK must be 256 Fs.                                                                                                                                                                                                                                                                              |  |  |  |

| 20, 17     | TXP, TXN                                                                                                                                                                                                                           | Differential line drivers.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

Table 4. Digital characteristics ( $T_{amb} = 25$ °C;  $V_{D+} = 3.3 \text{ V } 10\%$ )

|                 |                           | Min.                       | _                        |      |                          |      |

|-----------------|---------------------------|----------------------------|--------------------------|------|--------------------------|------|

| Symbol          | Parameter                 | Parameter Test condition N |                          | Тур. | Max.                     | Unit |

| V <sub>IH</sub> | High-level input voltage  |                            | 2.0                      |      | V <sub>DD</sub> +0.<br>3 | V    |

| V <sub>IL</sub> | Low-level input voltage   |                            | -0.3                     |      | +0.8                     | V    |

| V <sub>OH</sub> | High-level output voltage | Ι <sub>Ο</sub> = 200 μΑ    | V <sub>DD</sub> -<br>1.0 |      |                          | V    |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>O</sub> = 3.2 mA    |                          |      | 0.4                      | V    |

| I <sub>in</sub> | Input leakage current     |                            |                          | 1.0  | 10                       | Α    |

| MCK             | Master clock frequency    | (Note: 1)                  |                          |      | 26                       | MHz  |

| WOR             | Master clock duty cycle   | (high time/cycle time)     | 40                       |      | 60                       | %    |

Note:

1. MCK must be 128x the input word rate, except in transparent mode where MCK is 256x the input word rate.

4/15 DocID006832 Rev 7

STA020 Overview

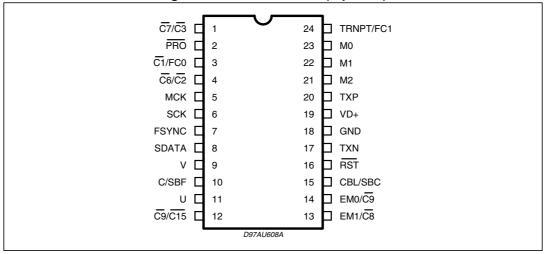

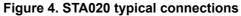

Figure 3. STA020 professional & consumer modes typical connections

# 2 General description

The STA020 is a monolithic CMOS circuit that encodes and transmits audio and digital data according to the AES/EBU, IEC 958, S/PDIF, and EIAJ CP-340 interface standards. The chip accepts audio and control data separately; multiplex and biphase-mark encode the data internally and drive it, directly or through a transformer, to a transmission line.

The STA020 has dedicated pins for the most important control bits and a serial input port for the C, U and V bits.

The STA020 accepts 16 to 24-bit audio samples through a serial port configured in one of seven formats; provides several pins dedicated to particular channel status bits and allows all channel status, user and validity bits to be serially input through port pins. This data is multiplexed, the parity bit is generated and the bit stream is biphase-mark encoded and driven through an RS422 line driver.

The STA020 operates as a professional or consumer interface transmitter selectable by pin 2, PRO. As a professional interface device, the dedicated channel status input pins are defined according to the professional standard, and the CRC code (C.S. byte 23) can be internally generated.

As a consumer device, the dedicated channel status input pins are defined according to the consumer standard. A submode provided under the consumer mode is compact disk, CD, mode. When transmitting data from a compact disk, the CD subcode port can accept CD subcode data, extract channel status information from it, and transmit it as user data.

The master clock, MCK, controls timing for the entire chip and must be 128xFs. As an example, if stereo data is input to the STA020 at 44.1kHz, MCK input must be 128 times that or 5.6448 MHz.

#### 2.1 Line drivers

The differential line drivers for STA020 are low skew, low impedance, differential outputs capable of driving 110 Ohm transmission lines. (RS422 line driver compatible).

They can also be disabled by resetting the device (RST = low).

# 2.2 Audio serial port

6/15

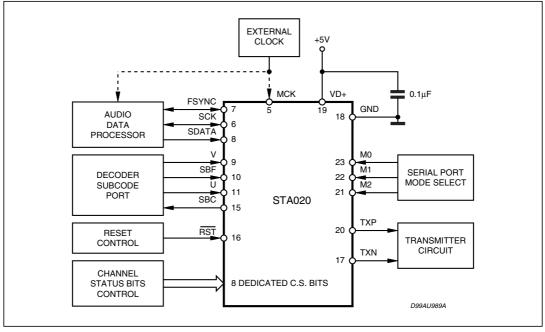

The audio serial port is used to enter audio data and consists of three pins: SCK, SDATA and FSYNC, SCK clocks in SDATA, which is double buffered, while FSYNC delineates the audio samples and may indicate the particular channel, left or right. To support many different interfaces, M2, M1 and M0 select one of seven different formats for the serial port. The coding is shown in *Table 5* while the formats are shown in *Figure 5*.

Format 0 and 1 are designed to interface with crystal ADCs. Format 2 communicates with Motorola and TI DSPs. Format 3 is reserved. Format 4 is compatible with the I<sup>2</sup>S standard. Formats 5 and 6 make the STA020 look similar to existing 16- and 18-bit DACs and interpolation filters. Format 7 is an MSB-last format and is conducive to serial arithmetic. SCK and FSYNC are outputs in Format 0 and inputs in all other formats. In Format 2, the rising edge of FSYNC delineates samples and the falling edge must occur a minimum of one bit period before or after the rising edge. In all formats except 2, FSYNC contains left/right information requiring both edges of FSYNC to delineate samples. Formats 5 and 6

DocID006832 Rev 7

STA020 General description

require a minimum of 16- or 18-bit audio words respectively. In all formats other than 5 and 6, the STA020 can accept any word length from 16 to 24 bits by adding leading zeros in format 7 and trailing zeros in the other formats, or by restricting the number of SCK periods between active edges of FSYNC to the sample word length.

FSYNC must be derived from MCK, either through a DSP using the same clock or using counters. If SFYNC moves (jitters) with respect to MCK by four MCK periods, the internal counters and CBL may be reset.

Table 5. Audio port modes

| M2 | M1 | МО | Format                                        |  |  |

|----|----|----|-----------------------------------------------|--|--|

| 0  | 0  | 0  | 0 - FSYNC & SCK output                        |  |  |

| 0  | 0  | 1  | 1 - Left/Right, 16-24 bits                    |  |  |

| 0  | 1  | 0  | 2 - Word sync, 16-24 bits                     |  |  |

| 0  | 1  | 1  | 3 - Reserved                                  |  |  |

| 1  | 0  | 0  | 0 4 - Left/Right, I <sup>2</sup> S compatible |  |  |

| 1  | 0  | 1  | 5 - LSB justified, 16 bits                    |  |  |

| 1  | 1  | 0  | 6 - LSB justified, 18 bits                    |  |  |

| 1  | 1  | 1  | 7 - MSB last, 16-24 bits                      |  |  |

Figure 5. Audio serial port formats

#### 2.3 C, U, V serial port

The serial input pins for channel status (C), user (U), and validity (V) are sampled during the first bit period after the active edge of FSYNC for all formats except Format 4. Format 4 is sampled during the second bit period (coincident with the MSB). In *Figure 5*, the arrows on SCK indicate when the C, U, and V bits are sampled. The C, U, and V bits are transmitted with the audio sample entered before FSYNC edge that sampled it. The V bit, as defined in the audio standards, is set to zero to indicate the audio data is suitable for conversion to analog. Therefore, when the audio data is errored, or the data is not audio, the V bit should be set high. The channel status serial input pin (C) is not available in consumer mode when the CD subcode port is enabled (FC1 = FC0 = high). Any channel status data entered through the channel status serial input (C) is logically OR'ed with the data entered through the dedicated pins or internally generated.

# 2.4 RST and CBL (TRNPT is low)

When RST goes low, the differential line drivers are set to ground. In order to properly synchronize the STA020 to the audio serial port, the transmit timing counters, which include CBL, are not enabled after RST goes high until eight and one half SCK periods after reset is exited) of FSYNC. When FSYNC is configured as a left/right signal (all defined formats except 2), the counters and CBL are not enabled until the right sample is being transmitted). This guarantees that channel A is left and channel B is right as per the digital audio interface specs.

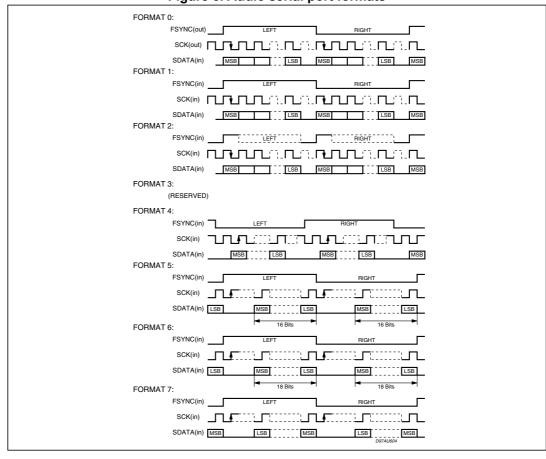

As shown in *Figure 4*, channel block start output (CBL) can assist in serially inputting the C, U and V bits as CBL goes high one bit period before the first bit of the preamble of the first sub-frame of the channel status block is transmitted. This sub-frame contains channel status byte 0, bit 0. CBL returns low one bit period before the start of the frame that contains bit 0 of channel status byte 16. CBL is not available when the CD subcode port is enabled.

Figure 4 illustrates timing for stereo data input on the audio port. Notice how CBL rises while the right channel data (Right 0) is input, but the previous left channel (Left 0) is being transmitted as the first sub-frame of the channel status block (starting with preamble Z). The C, U, and V input ports only need to be valid for a short period after FSYNC changes. A sub-frame includes one audio sample while a frame includes a stereo pair. A channel status (C.S.) block contains 24 bytes of channel status and 384 audio samples (or 192 stereo pairs, or frames, of samples). Figure 4 shows the CUV ports as having left and right bits (e.g. CUV0L, CUV0R). Since the C.S. block is defined as 192 bits, or one bit per frame, there are actually 2 C.S. blocks, one for channel A (left) and one for channel B (right). When inputting stereo audio data, both blocks normally contain the same information, so C0L and C0R from the input port pin are both channel status bit 0 of byte 0, which is defined as professional/consumer. These first two bits from the port, C0L and C0R, are logically OR'ed with the inverse PRO, since PRO is a dedicated channel status pin defined as C.S. bit 0.

Also, if in professional mode,  $\overline{C1}$ ,  $\overline{C6}$ ,  $\overline{C7}$  and  $\overline{C9}$  are dedicated C.S. pins. The inverse of C1 is logically OR'ed with channel status input ports bits C1L and C1R. In similar fashion,  $\overline{C6}$ ,  $\overline{C7}$  and  $\overline{C9}$  are OR'ed with their respective input bits. Also, the C bits in CUV128L and CUV128R are both channel status block bit 128, which is bit 0 of channel status byte 16.

8/15 DocID006832 Rev 7

STA020 General description

Figure 6. CBL and transmitter timing

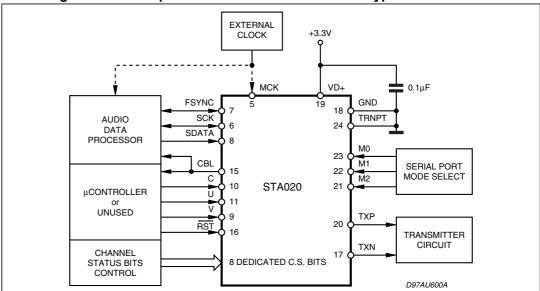

### 2.5 Transparent mode

In certain applications it is desirable to receive digital audio data with the STA120 and retransmit it with the STA020. In this case, channel status, user and validity information must pass through unaltered. For studio environments, AES recommends that signal timing synchronization be maintained throughout the studio. Frame synchronization of digital audio signals input to and output from a piece of equipment must be within ±5%.

The transparent mode of the STA020 is selected by setting TRNPT, pin 24, high. In this mode, the CBL pin becomes an input, allowing direct connection of the outputs of the STA120 to the inputs of the STA020 as shown in *Figure 7*. The transmitter and receiver are synchronized by the FSYNC signal. CBL specifies the start of a new channel status block boundary, allowing the transmit block structure to be slaved to the block structure of the receiver.

In the transparent mode, C, U and V are now transmitted with the current audio sample as shown in *Figure 7* (TRNPT high) and the dedicated channel status pins are ignored.

When FSYNC is a word clock (Format 2), CBL is sampled when left C, U, V are sampled. When FSYNC is Left/Right, CBL is sampled when left C, U, V are sampled. The channel status block boundary is reset when CBL transitions from low to high (based on two successive samples of CBL). MCK for the STA020 is normally expected to be 128 times the sample frequency, in the transparent mode MCK must be 256 Fs.

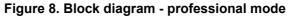

#### 2.6 Professional mode

Setting PRO low places the STA020 in professional mode as shown in *Figure 8*. In professional mode, channel status bit 0 is transmitted as a one and bits 1, 2, 3, 4, 6, 7 and 9 can be controlled via dedicated pins. The pins are actually the inverse of the identified bit.

For example, tying the  $\overline{C1}$  pin low places a one in channel status bit 1. As shown in the application note, "Overview of AES/EBU Digital Audio Interface Data Structures",  $\overline{C1}$

indicates audio/non-audio;  $\overline{C6}$  and  $\overline{C7}$  determine the sample frequency and  $\overline{C9}$  allows the encoded channel mode to be stereophonic. EM1 and EM0 determine emphasis and encode  $\overline{C2}$ ,  $\overline{C3}$ ,  $\overline{C4}$  as shown in *Table 6*. The dedicated channel status pins are read at the appropriate time and are logically OR'ed with data input on the channel status port, C. In transparent mode, these dedicated channel status pins are ignored and channel status bits are input at the C pin.

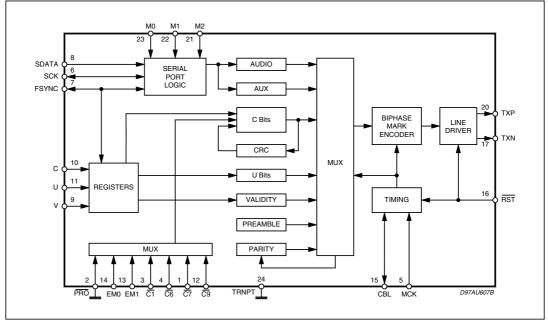

#### 2.7 Consumer mode

Setting PRO high places the STA020 in consumer mode which redefines the pins as shown in *Figure 9*. In consumer mode, channel status bit 0 is transmitted as a zero and channel status bits 2, 3, 8, 9, 15, 24 and 25 are controlled via dedicated pins.

The pins are actually the inverse of the bit so if pin  $\overline{C2}$  is tied high, channel status bit 2 will be transmitted as a zero. Also, FC0 and FC1 are encoded versions of channel status bits 24 and 25, which define the sample frequency.

When FC0 and FC1 are both high, the part is placed in a CD submode which activates the CD subcode port. This submode is described in detail in the next section. *Table 7* describes the encoding of C24 and C25 through the FC1 and FC0 pins. According to AES/EBU standards, C2 is copy prohibit/permit. C3 specifies pre-emphasis, C8 and C9 define the category code and C15 identifies the generation status of the transmitted material (i.e. first generation, second generation).

EM1 EM<sub>0</sub> C2 C3 C4 0 0 1 1 1 0 1 1 1 0 1 0 1 0 0 1 1 0 0 0

Table 6. Emphasis encoding

| Table 7  | Sample   | frequency  | encoding / |

|----------|----------|------------|------------|

| Table 1. | Jailible | II Equelle | CIICOUIIIG |

| FC1 | FC0 | C24 | C25 | Comments          |

|-----|-----|-----|-----|-------------------|

| 0   | 0   | 0   | 0   | 44.1 kHz          |

| 0   | 1   | 0   | 1   | 48 kHz            |

| 1   | 0   | 1   | 1   | 32 kHz            |

| 1   | 1   | 0   | 0   | 44.1 kHz, CD mode |

MCK CBL TRNPT U TXP ٧ FSYNC RXN TXN SDATA STA120 STA020 DATA PROCESSING D97AU605

Figure 7. Transparent mode interface

Figure 9. Block diagram - consumer mode

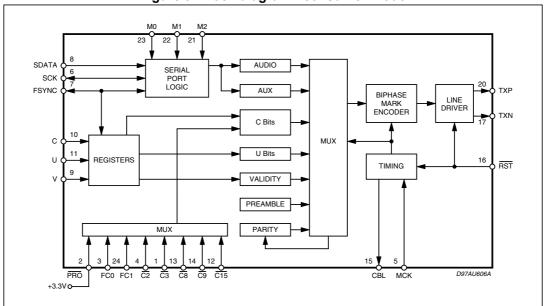

**STA020** Package information

#### **Package information** 3

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

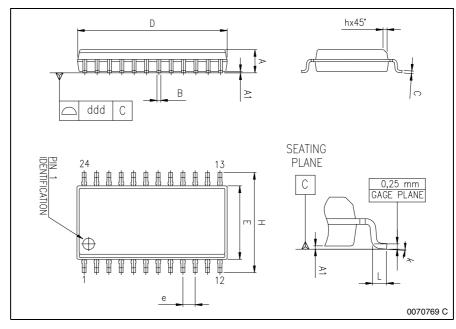

Figure 10. SO24 outline and dimensions

<sup>(1) &</sup>quot;D" dimension does not include mold flash, protusions or gate burrs. Mold flash, protusions or gate burrs shall not exceed 0.15mm per side.

#### **OUTLINE AND MECHANICAL DATA**

Revision history STA020

# 4 Revision history

**Table 8. Document revision history**

| Date        | Revision | Changes                                                                                          |

|-------------|----------|--------------------------------------------------------------------------------------------------|

| 03-Sep-2014 | 7        | Revised presentation of document along with active status, production data Minor textual updates |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics – All rights reserved