# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# ANALOG Audio Processor for Auvaniceu iv with DEVICES Sound IF Demodulator and Stereo Decoder

**ADAV4622**

#### **FEATURES**

algorithms

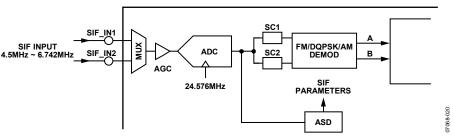

Sound IF (SIF) processor

SIF demodulator and broadcast stereo decoder NICAM (BG, DK, I, L), A2 (BG, DK, M), BTSC (M, N), EIAJ (M) **Automatic sound IF standard detection**

Fully programmable 28-bit audio processor for enhanced ATV sound—default TV audio flow loaded on reset Implements Analog Devices and third-party branded audio

Adjustable digital delay line for audio/video Synchronization for up to 200 ms stereo delay

High performance 24-bit ADC and DAC

94 dB DNR performance on DAC channels

95 dB DNR performance on ADC channels

Dual headphone outputs with integrated amplifiers

High performance pulse-width modulation (PWM) digital outputs

Multichannel digital baseband I/O

4 stereo synchronous digital I<sup>2</sup>S input channels One 6-channel sample rate converter (SRC) and one stereo SRC supporting input sample rates from 5 kHz to 50 kHz

One stereo synchronous digital I2S output S/PDIF output with S/PDIF input mux capability Fast I<sup>2</sup>C control

Operates from 3.3 V (analog), 1.8 V (digital core), and 3.3 V (digital interface)

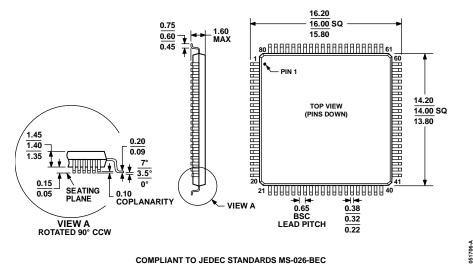

**Available in 80-lead LQFP**

#### **APPLICATIONS**

General-purpose consumer audio postprocessing Home audio **DVD** recorders Home theater in a box (HTIB) systems and DVD receivers Audio processing subsystems for DTV-ready TVs Analog broadcast capability for iDTVs

#### PRODUCT OVERVIEW

The ADAV4622 is an enhanced audio processor targeting advanced TV applications with full support for digital and analog baseband audio as well as multistandard broadcast SIF demodulation and decoding.

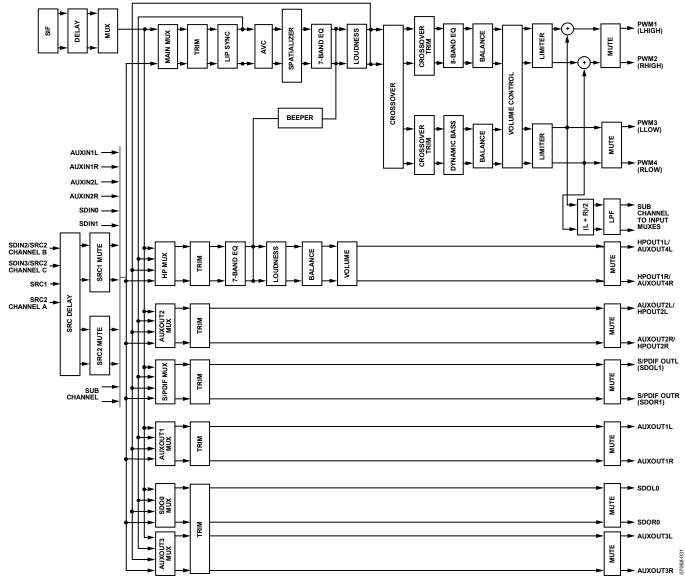

The audio processor, by default, loads a dedicated TV audio flow that incorporates full matrix switching (any input to any output), automatic volume control that compensates for volume changes during advertisements or when switching channels, dynamic bass, a multiband equalizer, and up to 200 ms of stereo delay memory for audio-video synchronization.

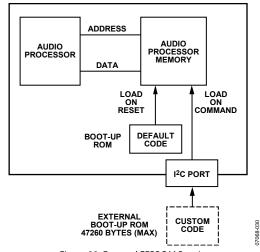

Alternatively, Analog Devices, Inc., offers an award-winning graphical programming tool (SigmaStudio™) that allows custom flows to be quickly developed and evaluated. This allows the creation of customer-specific audio flows, including use of the Analog Devices library of third-party algorithms.

The analog I/O integrates Analog Devices proprietary continuous-time, multibit  $\Sigma$ - $\Delta$  architecture to bring a higher level of performance to ATV systems, required by third-party algorithm providers to meet system branding certification. The analog input is provided by 95 dB dynamic range (DNR) ADCs, and analog output is provided by 94 dB DNR DACs.

The main speaker outputs can be supplied as a digitally modulated PWM stream to support digital amplifiers.

The ADAV4622 includes multichannel digital inputs and outputs. In addition, digital input channels can be routed through integrated sample rate converters (SRC), which are capable of supporting any arbitrary sample rate from 5 kHz to 50 kHz.

# **ADAV4622\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS -

View a parametric search of comparable parts.

### **EVALUATION KITS**

· ADAV4622 Evaluation Board

### **DOCUMENTATION**

#### **Data Sheet**

ADAV4622: Audio Processor for Advanced TV with Sound IF Demodulator and Stereo Decoder Data Sheet

### SOFTWARE AND SYSTEMS REQUIREMENTS 🖳

• Firmware Loader for SigmaDSPs

### **TOOLS AND SIMULATIONS**

• SigmaDSP Processors: Software and Tools

## **DESIGN RESOURCES**

- ADAV4622 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all ADAV4622 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

# **TABLE OF CONTENTS**

| Features 1                                                                         | VREF                                                | 20   |

|------------------------------------------------------------------------------------|-----------------------------------------------------|------|

| Applications1                                                                      | FILTA and FILTD                                     | 20   |

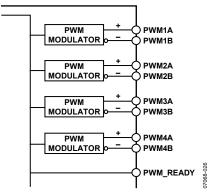

| Product Overview1                                                                  | PWM1A, PWM1B, PWM2A, PWM2B, PWM3A, PW               | М3В, |

| Revision History                                                                   | PWM4A, and PWM4B                                    |      |

| Functional Block Diagram3                                                          | PWM_READY                                           | 20   |

| Specifications4                                                                    | AVDD                                                | 20   |

| Performance Parameters 4                                                           | DVDD                                                | 20   |

| Timing Specifications9                                                             | ODVDD                                               | 20   |

| Timing Diagrams10                                                                  | DGND                                                | 20   |

| Absolute Maximum Ratings12                                                         | AGND                                                | 20   |

| Thermal Resistance                                                                 | ODGND                                               | 20   |

| Thermal Conditions                                                                 | SIF_REFP, SIF_REFCM, and SIF_REFN                   | 20   |

| ESD Caution                                                                        | SIF_IN1 and SIF_IN2                                 | 20   |

| Pin Configuration and Function Descriptions                                        | SIF_PGA_REF                                         | 20   |

| Typical Performance Characteristics                                                | ISET                                                | 20   |

| 71 Terminology                                                                     | Functional Descriptions                             | 21   |

| Pin Functions                                                                      | SIF Processor                                       | 21   |

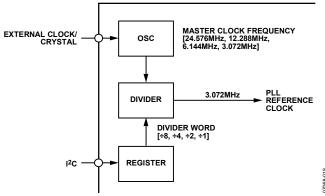

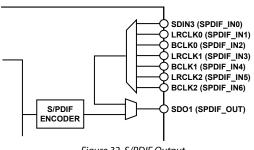

| SDIN0, SDIN1, SDIN2, and SDIN3/SPDIF_IN019                                         | Master Clock Oscillator                             | 21   |

| LRCLK0, BCLK0, LRCLK1, BCLK1, LRCLK2, and BCLK2 19                                 | I <sup>2</sup> C Interface                          | 22   |

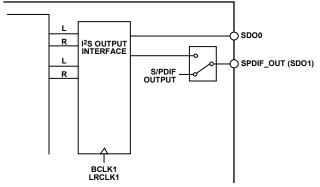

| SDO0/AD0                                                                           | ADC Inputs                                          | 22   |

| SPDIF_OUT (SDO1)                                                                   | I <sup>2</sup> S Digital Audio Inputs               | 22   |

| MCLKI/XIN                                                                          | DAC Voltage Outputs                                 | 23   |

| XOUT                                                                               | PWM Outputs                                         | 24   |

| MCLK OUT                                                                           | Headphone Outputs                                   | 24   |

| SDA                                                                                | I <sup>2</sup> S Digital Audio Outputs              | 24   |

| SCL                                                                                | S/PDIF Input/Output                                 |      |

| MUTE                                                                               | Hardware Mute Control                               |      |

| RESET                                                                              | Audio Processor                                     | 25   |

|                                                                                    | Graphical Programming Environment                   | 25   |

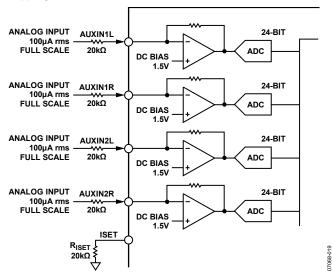

| AUXIN1L, AUXIN2L, AUXIN1R, and AUXIN2R20                                           | Application Layer                                   |      |

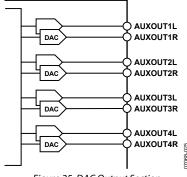

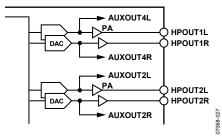

| AUXOUT1L, AUXOUT2L, AUXOUT3L, AUXOUT4L, AUXOUT1R, AUXOUT2R, AUXOUT3R, and AUXOUT4R | Loading a Custom Audio Processing Flow              |      |

| 20                                                                                 | Outline Dimensions                                  |      |

| HPOUT1L, HPOUT2L, HPOUT1R, and HPOUT2R 20                                          | Ordering Guide                                      |      |

| PLL_LF                                                                             |                                                     |      |

| REVISION HISTORY                                                                   | Change to Hardware Mute Control, Graphical Programm | ning |

| 7/09—Rev. A to Rev. B                                                              | Environment, and Application Layer Sections         |      |

| Added Advantiv Logo                                                                | Changes to Ordering Guide                           | 28   |

| Change to PWM Outputs Section24                                                    | 11/00 TO TOTAL INITIAL VEISION                      |      |

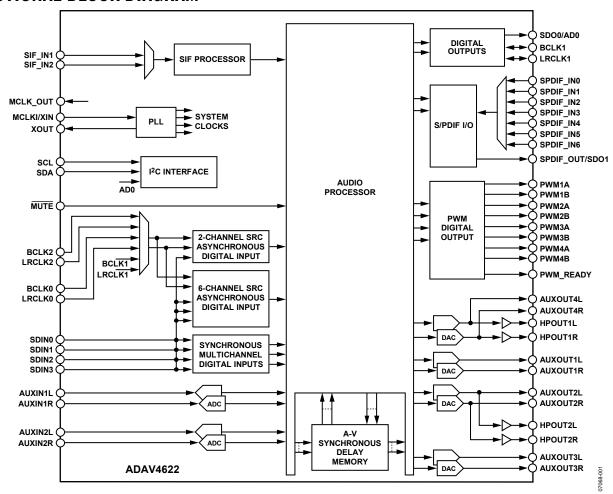

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. ADAV4622 with PWM-Based Speaker Outputs

# **SPECIFICATIONS**

AVDD = 3.3 V, DVDD = 1.8 V, ODVDD = 3.3 V, operating temperature =  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , master clock = 24.576 MHz, measurement bandwidth = 20 Hz to 20 kHz, ADC input signal = DAC output signal = 1 kHz, unless otherwise noted.

#### **PERFORMANCE PARAMETERS**

Table 1.

| Parameter                              | Min Typ   | Max | Unit  | Test Conditions/Comments                                                                                                |

|----------------------------------------|-----------|-----|-------|-------------------------------------------------------------------------------------------------------------------------|

| SIF ADC INPUT SECTION                  |           |     |       |                                                                                                                         |

| Analog Input Frequency Range           |           | 10  | MHz   |                                                                                                                         |

| Recommended Analog Input Level         | 90 ± 18 0 | dB  | dBu   | FM, AGC in PGA priority mode                                                                                            |

| Maximum Analog Input Range             | 1.6       |     | V p-p | Default setting                                                                                                         |

| Input Impedance                        | 12        |     | kΩ    | PGA Gain = 0 dB                                                                                                         |

|                                        | 6         |     | ΚΩ    | PGA Gain = 10 dB                                                                                                        |

|                                        | 2.3       |     | kΩ    | PGA Gain = 20 dB                                                                                                        |

| DC Bias Level                          | 1.9       |     | V     |                                                                                                                         |

| SIF Input Isolation                    | 60        |     | dB    | SIF_IN1 to SIF_ IN2                                                                                                     |

| FM Limiting Sensitivity                | 32        |     | dBu   | A2 (DK), Mono, deviation mode = 100%, $f_{\text{FM}}$ = 400 Hz, $\Delta f$ = 50 kHz, BW = 20 Hz to 15 kHz, rms detector |

|                                        | 31        |     | dBu   | A2 (I), Mono, deviation mode = 100%, $f_{FM}$ = 400 Hz, $\Delta f$ = 50 kHz, BW = 20 Hz to 15 kHz, rms detector         |

|                                        | 31        |     | dBu   | A2 (BG), Mono, deviation mode = 100%, $f_{EM}$ = 400 Hz,<br>$\Delta f$ = 50 kHz, BW = 20 Hz to 15 kHz, rms detector     |

|                                        | 34        |     | dBu   | BTSC (M, N), Mono, deviation mode = 100%, $f_{FM} = 400$ Hz, $\Delta f = 25$ kHz, BW = 20 Hz to 15 kHz, rms detector    |

|                                        | 28.5      |     | dBu   | A2 (M), Mono, deviation mode = 100%, $f_{FM}$ = 400 Hz, $\Delta f$ = 25 kHz, BW = 20 Hz to 15 kHz, rms detector         |

|                                        | 30        |     | dBu   | EIAJ (M), Mono, deviation mode = 100%, $f_{EM}$ = 400 Hz, $\Delta f$ = 25 kHz, BW = 20 Hz to 15 kHz, rms detector       |

| FM Output Level at 25% Deviation Mode  | 53.7      |     | % FS  | A2 (DK, I, BG), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz, $\Delta f = 12.5$ kHz, rms detector                        |

|                                        | 53.6      |     | % FS  | BTSC (M, N), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 6.25 kHz, rms detector                           |

|                                        | 56.3      |     | % FS  | A2 (M), Mono, $V_{SIF}=100$ mV, $f_{FM}=400$ Hz, $\Delta f=6.25$ kHz, rms detector                                      |

|                                        | 56.7      |     | % FS  | EIAJ (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 6.25 kHz, rms detector                              |

| FM Output Level at 50% Deviation Mode  | 53.7      |     | % FS  | A2 (DK, I, BG), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz, $\Delta f = 25$ kHz, rms detector                          |

|                                        | 53.6      |     | % FS  | BTSC (M, N), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 12.5 kHz, rms detector                           |

|                                        | 56.3      |     | % FS  | A2 (M), Mono, $V_{SIF}=100$ mV, $f_{FM}=400$ Hz, $\Delta f=12.5$ kHz, rms detector                                      |

|                                        | 56.7      |     | % FS  | EIAJ (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 12.5 kHz, rms detector                              |

| FM Output Level at 100% Deviation Mode | 53.7      |     | % FS  | A2 (DK, I, BG), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz, $\Delta f = 50$ kHz, rms detector                          |

|                                        | 53.6      |     | % FS  | BTSC (M, N), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 25 kHz, rms detector                             |

|                                        | 56.3      |     | % FS  | A2 (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 25 kHz, rms detector                                  |

|                                        | 56.7      |     | % FS  | EIAJ (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 25 kHz, rms detector                                |

| FM Output Level at 200% Deviation Mode | 53.7      |     | % FS  | A2 (DK, I, BG), Mono, $V_{SIF}$ =100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 100 kHz, rms detector                          |

|                                        | 53.6      |     | % FS  | BTSC (M, N), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 50 kHz, rms detector                             |

|                                        | 56.3      |     | % FS  | A2 (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 50 kHz, rms detector                                  |

|                                        | 56.7      |     | % FS  | EIAJ (M), Mono, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 50 kHz, rms detector                                |

| Parameter                              | Min Ty   |    | Max         | Unit | Test Conditions/Comments                                                                                                                                                                                   |

|----------------------------------------|----------|----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM Output Level at 400% Deviation Mode | 53.      | .7 |             | % FS | A2 (DK, I, BG), Mono, $V_{SIF} = 100 \text{ mV}$ , $f_{FM} = 400 \text{ Hz}$ , $\Delta f = 200 \text{ kHz}$ , rms detector                                                                                 |

|                                        | 53.      | .6 |             | % FS | BTSC (M, N), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz, $\Delta f = 100$ kHz, rms detector                                                                                                               |

|                                        | 56       | .4 |             | % FS | A2 (M), Mono, $V_{SIF} = 100 \text{ mV}$ , $f_{FM} = 400 \text{ Hz}$ , $\Delta f = 100 \text{ kHz}$ , rms detector                                                                                         |

|                                        | 56.      | .7 |             | % FS | EIAJ (M), Mono, $V_{SIF} = 100 \text{ mV}$ , $f_{FM} = 400 \text{ Hz}$ , $\Delta f = 100 \text{ kHz}$ , rms detector                                                                                       |

| FM Output Level at 800% Deviation Mode | 53.      | .7 |             | % FS | A2 (DK, I, BG), Mono, $V_{SIF} = 100 \text{ mV}$ , $f_{FM} = 400 \text{ Hz}$ , $\Delta f = 400 \text{ kHz}$ , rms detector                                                                                 |

|                                        | 53       | .6 |             | % FS | BTSC (M, N), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz,<br>$\Delta f = 200$ kHz, rms detector                                                                                                            |

|                                        | 56       | .3 |             | % FS | A2 (M), Mono, $V_{SIF} = 100 \text{ mV}$ , $f_{FM} = 400 \text{ Hz}$ , $\Delta f = 200 \text{ kHz}$ , rms detector                                                                                         |

|                                        | 56       | .7 |             | % FS | EIAJ (M), Mono, $V_{SIF} = 100$ mV, $f_{FM} = 400$ Hz, $\Delta f = 200$ kHz, rms detector                                                                                                                  |

| AM Rejection Ratio                     | 69.      | .5 |             | dB   | A2 (DK), Mono, deviation mode = 100%, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 27 kHz, $f_{AM}$ = 400 Hz, $\Delta f$ = 30%, BW = 20 Hz to 15 kHz, rms detector                                  |

|                                        | 70       |    |             | dB   | A2 (I), Mono, deviation mode = $100\%$ , $V_{SIF}$ = $100$ mV, $f_{FM}$ = $400$ Hz, $\Delta f$ = $27$ kHz, $f_{AM}$ = $400$ Hz, $MOD_{AM}$ = $30\%$ , BW = $20$ Hz to 15 kHz, rms detector                 |

|                                        | 70       |    |             | dB   | A2 (BG), Mono, deviation mode = 100%, $V_{SF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 27 kHz, $f_{AM}$ = 400 Hz, MOD <sub>AM</sub> = 30%, BW = 20 Hz to 15 kHz, rms detector                            |

|                                        | 70.      | .5 |             | dB   | Mono (M), deviation mode = 100%, $V_{SIF}$ = 100 mV, $f_{FM}$ = 400 Hz, $\Delta f$ = 13.5 kHz, $f_{AM}$ = 400 Hz, $\Delta f$ = 30%, BW = 20 Hz to 15 kHz, rms detector                                     |

| AM Sensitivity                         | 40       |    |             | dBu  | Mono (L), $f_{AM}$ = 400 Hz, MOD = 30%, BW = 20 Hz to 15 kHz, rms detector, (S + N)/N = 10 dB                                                                                                              |

| BTSC (M) PERFORMANCE                   |          |    |             |      | Measured at analog audio output, video = 75% color bar $f_{SC}$ = 4.5 MHz, $f_{FM}$ = 1 kHz, $\Delta f$ = 25 kHz (100%), deemphasis = 75 $\mu$ s, measuring BW = 20 Hz to 15 kHz with dBX NR               |

| Dynamic Range                          |          |    |             |      |                                                                                                                                                                                                            |

| Stereo Channel                         | 62       |    |             | dB   | Stereo L or R (L = -R), 100%, 1 kHz                                                                                                                                                                        |

| SAP Channel                            | 68       |    |             | dB   | SAP channel with Mono 100%, 1 kHz                                                                                                                                                                          |

| Total Harmonic Distortion + Noise      |          |    |             | ub.  | 374 CHAINE WITH MONO 10079 1 Kinz                                                                                                                                                                          |

| Stereo Channel                         | -4       | 6  |             | dB   | Stereo L or R (L = $-$ R), 100%, 1 kHz                                                                                                                                                                     |

| SAP Channel                            | -4<br>-4 |    |             | dB   | SAP 100%, 1 kHz                                                                                                                                                                                            |

| Frequency Response                     | -4       | .0 |             | ub   | f <sub>EM</sub> = 20 Hz to 12 kHz                                                                                                                                                                          |

|                                        |          |    | .01/ 07     | 70   |                                                                                                                                                                                                            |

| Stereo Channel                         |          |    | +0.1/-0.7   | dB   | Stereo L or R, 50%, $(L = -R)$                                                                                                                                                                             |

| SAP Channel                            |          |    | +2.5/-2.5   | dB   | SAP 50%, Mono 100%, 1 kHz                                                                                                                                                                                  |

| Crosstalk                              | _        |    |             |      |                                                                                                                                                                                                            |

| Stereo-to-SAP Channel                  | -7       |    |             | dB   | L or R 50%, 1 kHz                                                                                                                                                                                          |

| SAP-to-Stereo Channel                  | -7       |    |             | dB   | SAP 50%, 1 kHz                                                                                                                                                                                             |

| Stereo Separation dBX                  | 30       |    |             | dB   | L off, R 50%, 1 kHz                                                                                                                                                                                        |

| EIAJ (M) PERFORMANCE                   |          |    |             |      | Measured at analog audio output, video = 75% color bar $f_{SC} = 4.5 \text{ MHz}$ , $f_{FM} = 1 \text{ kHz}$ , $\Delta f = 25 \text{ kHz}$ (100%), deemphasis = 75 $\mu$ s, measuring BW = 20 Hz to 15 kHz |

| Dynamic Range                          |          |    |             |      | 2012013112                                                                                                                                                                                                 |

| Stereo Channel                         | 58       |    |             | dB   | Stereo L or R, 100%, 1 kHz                                                                                                                                                                                 |

| Dual Channel                           | 56       |    |             | dB   | Dual channel with Mono 100%, 1 kHz                                                                                                                                                                         |

| Total Harmonic Distortion + Noise      | 30       |    |             | ub   | Dual Charmer with Mono 10070, 1 KHZ                                                                                                                                                                        |

|                                        | -        | _  |             | 40   | Change Law D 1000/ 1 kHz                                                                                                                                                                                   |

| Stereo Channel                         | -5       |    |             | dB   | Stereo L or R, 100%, 1 kHz                                                                                                                                                                                 |

| Dual Channel                           | -4       | .1 |             | dB   | Dual 50%, 1 kHz                                                                                                                                                                                            |

| Frequency Response                     |          |    |             |      | f <sub>FM</sub> = 20 Hz to 10 kHz                                                                                                                                                                          |

| Stereo Channel                         |          |    | +0.03/-0.53 | dB   | Stereo L or R, 100%                                                                                                                                                                                        |

| Dual Channel                           |          |    | +0.17/–1.4  | dB   | Dual 100%, Mono 100%, 1 kHz                                                                                                                                                                                |

| Crosstalk                              |          |    |             |      |                                                                                                                                                                                                            |

| Main-to-Dual Channel                   | -7       | 5  |             | dB   | Main 100%, 1 kHz                                                                                                                                                                                           |

| Dual-to-Main Channel                   | -8       | 3  |             | dB   | Dual 100%, 1 kHz                                                                                                                                                                                           |

| Stereo Separation                      | 39       |    |             | dB   | Stereo L or R, 100%, 1 kHz                                                                                                                                                                                 |

| Parameter                         | Min Typ | Max         | Unit | Test Conditions/Comments                                                                                                                                                                                                    |

|-----------------------------------|---------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2 (M) PERFORMANCE                |         |             |      | Measured at analog audio output, video = 75% color bar,                                                                                                                                                                     |

|                                   |         |             |      | $f_{SC1}=4.5$ MHz, $f_{SC2}=4.724$ MHz, $f_{FM}=1$ kHz, $\Delta f=25$ kHz (100%), deemphasis = 75 $\mu$ s, measuring BW = 20 Hz to 15 kHz                                                                                   |

| Dynamic Range                     | 60      |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Total Harmonic Distortion + Noise | _64     |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Frequency Response                | 04      | +0.4/-0.05  | dB   | Mono 100%, FkHz  Mono 100%, f <sub>FM</sub> = 25 Hz to 15 kHz                                                                                                                                                               |

| Crosstalk (Dual)                  | -88     | +0.4/ -0.03 | dB   | Mono or dual off, 100%, 1 kHz                                                                                                                                                                                               |

| Channel Separation (Stereo)       | 66      |             | dB   | Stereo L off, R 50%, 1 kHz                                                                                                                                                                                                  |

| •                                 | 00      |             | UB   |                                                                                                                                                                                                                             |

| A2 (DK1/DK2/DK3) PERFORMANCE      |         |             |      | Measured at analog audio output, video = 75% color bar, $f_{SC1} = 6.5$ MHz, $f_{SC2} = 6.742$ MHz, (DK2 worst case), $f_{FM} = 1$ kHz, $\Delta f = 50$ kHz (100%), deemphasis = 50 $\mu$ s, measuring BW = 20 Hz to 15 kHz |

| Dynamic Range                     | 74      |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Total Harmonic Distortion + Noise | -66     |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Frequency Response                |         | +0.1/-0.3   | dB   | Mono 100%, f <sub>FM</sub> = 20 Hz to 15 kHz                                                                                                                                                                                |

| Crosstalk (Dual)                  | -88     |             | dB   | Mono or dual off, 100%, 1 kHz                                                                                                                                                                                               |

| Channel Separation (Stereo)       | 77      |             | dB   | Stereo L off, R 50%, 1 kHz                                                                                                                                                                                                  |

| A2 (BG) PERFORMANCE               |         |             |      | Measured at analog audio output, video = 75% color bar, $f_{SC1} = 5.5$ MHz, $f_{SC2} = 5.742$ MHz, $f_{FM} = 1$ kHz, $\Delta f = 50$ kHz (100%), deemphasis = $50$ $\mu$ s, measuring BW = $20$ Hz to $15$ kHz             |

| Dynamic Range                     | 74      |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Total Harmonic Distortion + Noise | -61     |             | dB   | Mono 100%, 1 kHz                                                                                                                                                                                                            |

| Frequency Response                |         | +0.1/-0.3   | dB   | Mono 100%, $f_{EM} = 25 \text{ Hz to } 15 \text{ kHz}$                                                                                                                                                                      |

| Crosstalk (Dual)                  | -89     |             | dB   | Mono or dual off, 100%, 1 kHz                                                                                                                                                                                               |

| Channel Separation (Stereo)       | 70      |             | dB   | Stereo L off, R 50%, 1 kHz                                                                                                                                                                                                  |

| NICAM (I) PERFORMANCE             |         |             |      | Measured at analog audio output, video = 75% color bar,<br>1 kHz, unweighted, deemphasis = J17, measuring BW = 20<br>Hz to 15 kHz                                                                                           |

| Dynamic Range                     | 72      |             | dB   | Stereo L or R, 0 dB, 1 kHz                                                                                                                                                                                                  |

| Total Harmonic Distortion + Noise | -63     |             | dB   | Stereo L or R, 0 dB, 1 kHz                                                                                                                                                                                                  |

| Frequency Response                |         | -1.3/+0.07  | dB   | Stereo L or R, 0 dB                                                                                                                                                                                                         |

| Crosstalk                         | -80     |             | dB   | Mono or dual, 0 dB, 1 kHz                                                                                                                                                                                                   |

| Stereo Separation                 | 73      |             | dB   | L or R, 0 dB, 1 kHz                                                                                                                                                                                                         |

| Bit Error Rate                    | 0       |             |      | FM and NICAM nominal conditions                                                                                                                                                                                             |

| NICAM (BG, DK, L) PERFORMANCE     |         |             |      | Measured at analog audio output, video = 75% color bar,<br>1 kHz, unweighted, deemphasis = J17, measuring BW =<br>20 Hz to 15 kHz                                                                                           |

| Dynamic Range                     | 72      |             | dB   | Stereo L or R, 0 dB, 1 kHz                                                                                                                                                                                                  |

| Total Harmonic Distortion + Noise | -63     |             | dB   | Stereo L or R, 0 dB, 1 kHz                                                                                                                                                                                                  |

| Frequency Response                |         | -1.3/+0.07  | dB   | Stereo L or R, 0 dB                                                                                                                                                                                                         |

| Crosstalk                         | -80     |             | dB   | Mono or dual, 0 dB, 1 kHz                                                                                                                                                                                                   |

| Stereo Separation                 | 74      |             | dB   | L or R, 0 dB, 1 kHz                                                                                                                                                                                                         |

| Bit Error Rate                    | 0       |             |      | FM and NICAM nominal conditions                                                                                                                                                                                             |

| AM PERFORMANCE                    |         |             |      | Measured at analog audio output, 1 kHz,<br>AM carrier 6.5 MHz measuring BW = 20 Hz to 15 kHz                                                                                                                                |

| Dynamic Range                     |         |             |      | 3                                                                                                                                                                                                                           |

| RMS/FLAT                          | 55      |             | dB   | AM = 54% modulation                                                                                                                                                                                                         |

| QP/CCIR                           | 35      |             | dB   | CCIR filter, AM = 54% modulation                                                                                                                                                                                            |

| Total Harmonic Distortion + Noise | -49     |             | dB   | AM = 54% modulation                                                                                                                                                                                                         |

| Frequency Response                | .,      | +0.03/-1.2  | dB   | AM = 54% modulation                                                                                                                                                                                                         |

| REFERENCE SECTION                 |         | . 0.03/ 1.2 | 1    | 5 .//                                                                                                                                                                                                                       |

| Absolute Voltage V <sub>REF</sub> | 1.53    |             | V    |                                                                                                                                                                                                                             |

| , woodate voilage viter           | 1.55    |             | I *  |                                                                                                                                                                                                                             |

| Parameter                                          | Min | Тур         | Max | Unit   | Test Conditions/Comments                                                               |

|----------------------------------------------------|-----|-------------|-----|--------|----------------------------------------------------------------------------------------|

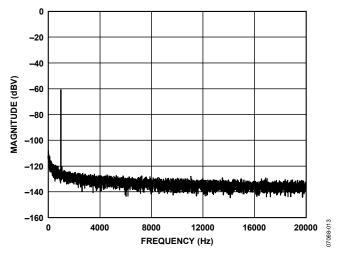

| ADC SECTION                                        |     |             |     |        |                                                                                        |

| Number of Channels                                 |     | 4           |     |        | Two stereo channels                                                                    |

| Full-Scale Input Level                             |     | 100         |     | μA rms |                                                                                        |

| Resolution                                         |     | 24          |     | Bits   |                                                                                        |

| Dynamic Range (Stereo Channel)                     |     |             |     |        |                                                                                        |

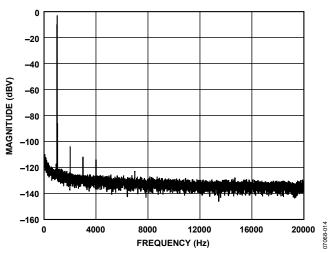

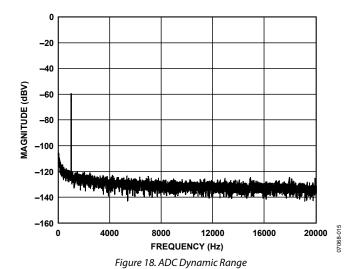

| A-Weighted                                         |     | 95          |     | dB     | -60 dBFS with respect to full-scale analog input                                       |

| Total Harmonic Distortion + Noise (Stereo Channel) |     | -90         |     | dB     | -3 dBFS with respect to full-scale analog input                                        |

| Gain Mismatch                                      |     | 0.2         |     | dB     | Left- and right-channel gain mismatch                                                  |

| Crosstalk (Left to Right, Right to Left)           |     | -110        |     | dB     |                                                                                        |

| Gain Error                                         |     | -1          |     | dB     | Input signal is 100 μA rms                                                             |

| Current Setting Resistor (RISET)                   |     | 20          |     | kΩ     | External resistor to set current input range of ADC for nominal 2.0 V rms input signal |

| Power Supply Rejection                             |     | -87         |     | dB     | 1 kHz, 300 mV p-p signal at AVDD                                                       |

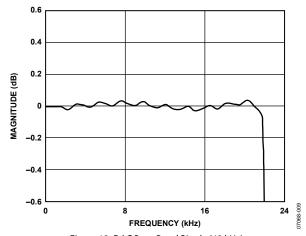

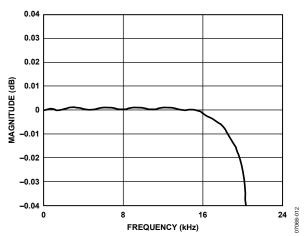

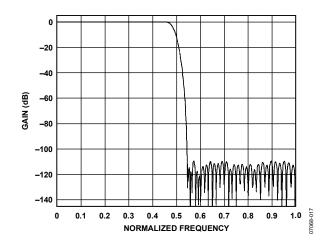

| ADC DIGITAL DECIMATOR FILTER CHARACTERISTICS       |     |             |     |        | At 48 kHz, guaranteed by design                                                        |

| Pass Band                                          | 1   | 22.5        |     | kHz    |                                                                                        |

| Pass-Band Ripple                                   |     | ±0.0002     |     | dB     |                                                                                        |

| Stop Band                                          |     | 26.5        |     | kHz    |                                                                                        |

| Stop-Band Attenuation                              |     | 100         |     | dB     |                                                                                        |

| Group Delay                                        |     | 1040        |     | μs     |                                                                                        |

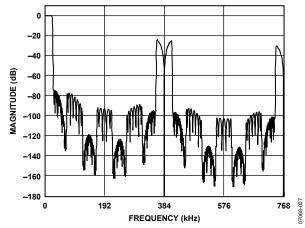

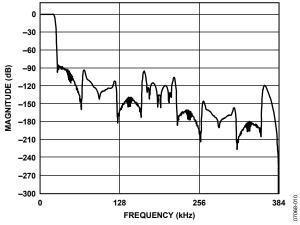

| PWM SECTION                                        | +   |             |     | Pro-   |                                                                                        |

| Frequency                                          |     | 384         |     | kHz    | Guaranteed by design                                                                   |

| Modulation Index                                   |     | 0.976       |     | 2      | Guaranteed by design                                                                   |

| Dynamic Range                                      |     | 0.570       |     |        | Guaranteed by design                                                                   |

| A-Weighted                                         |     | 98          |     | dB     | -60 dB with respect to full-scale code input                                           |

| Total Harmonic Distortion + Noise                  |     | –78         |     | dB     | -3 dB with respect to full-scale code input                                            |

| DAC SECTION                                        |     | 70          |     | ub.    | 3 db With respect to run scale code input                                              |

| Number of Auxiliary Output Channels                |     | 8           |     |        | Four stereo channels                                                                   |

| Resolution                                         |     | 24          |     | Bits   | Tour stered charmers                                                                   |

| Full-Scale Analog Output                           |     | 1           |     | V rms  |                                                                                        |

| Dynamic Range                                      |     |             |     | VIIIIS |                                                                                        |

| A-Weighted                                         |     | 94          |     | dB     | -60 dBFS with respect to full-scale code input                                         |

| Total Harmonic Distortion + Noise                  |     | -86         |     | dB     | -3 dBFS with respect to full-scale code input                                          |

| Crosstalk (Left to Right, Right to Left)           |     | -30<br>-102 |     | dB     | -3 dbi 3 with respect to full-scale code input                                         |

| Interchannel Gain Mismatch                         |     | 0.1         |     | dB     | Left- and right-channel gain mismatch                                                  |

| Gain Error                                         |     | 0.525       |     | dB     | 1 V rms output                                                                         |

| DC Bias                                            |     |             |     | V      | 1 v mis output                                                                         |

|                                                    |     | 1.53<br>–90 |     | dB     | 1 kHz 200 m// m in signal at AVDD                                                      |

| Power Supply Rejection Output Impedance            |     | -90<br>235  |     | Ω      | 1 kHz, 300 mV p-p signal at AVDD                                                       |

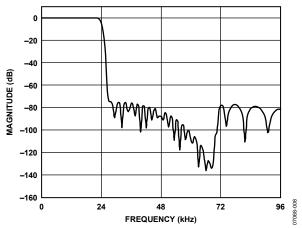

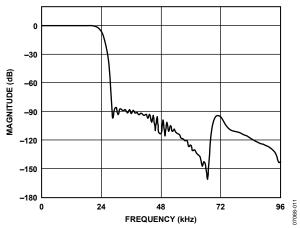

| DAC DIGITAL INTERPOLATION FILTER CHARACTERISTICS   |     | 233         |     | 12     | At 48 kHz, guaranteed by design                                                        |

| Pass Band                                          |     | 21.769      |     | kHz    |                                                                                        |

| Pass Band<br>Pass-Band Ripple                      | 1   | ±0.01       |     | dB     |                                                                                        |

| • • • • • • • • • • • • • • • • • • • •            | 1   |             |     |        |                                                                                        |

| Transition Band                                    |     | 23.95       |     | kHz    |                                                                                        |

| Stop Band                                          |     | 26.122      |     | kHz    |                                                                                        |

| Stop-Band Attenuation                              | 1   | 75<br>590   |     | dB     |                                                                                        |

| Group Delay                                        | 1   | 580         |     | μs     | Massimad at heading and a sustaint of the 20 O.L.                                      |

| HEADPHONE AMPLIFIER                                |     | 4           |     |        | Measured at headphone output with 32 $\Omega$ load                                     |

| Number of Channels                                 |     | 4           |     | ,,,    | Two stereo channels                                                                    |

| Full-Scale Output Power                            | 1   | 31          |     | mW rms | 1 V rms output                                                                         |

| Dynamic Range                                      | 1   |             |     |        |                                                                                        |

| A-Weighted                                         | 1   | 93          |     | dB     | -60 dBFS with respect to full-scale code input                                         |

| Total Harmonic Distortion + Noise                  |     | -83         |     | dB     | -3 dBFS with respect to full-scale code input                                          |

| Interchannel Gain Mismatch                         |     | 0.1         |     | dB     |                                                                                        |

| DC Bias                                            | 1   | 1.53        |     | V      |                                                                                        |

| Power Supply Rejection                             | 1   | -85         |     | dB     | 1 kHz, 300 mV p-p signal at AVDD                                                       |

| Parameter                                                                                                            | Min  | Тур    | Max   | Unit | Test Conditions/Comments                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|--------|-------|------|----------------------------------------------------------------------------------------------|

| SRC                                                                                                                  |      |        |       |      |                                                                                              |

| Number of Channels                                                                                                   |      | 8      |       |      | Two channels (SRC1), six channels (SRC2)                                                     |

| Dynamic Range                                                                                                        |      |        |       |      |                                                                                              |

| A-Weighted                                                                                                           |      | 115    |       | dB   | $-60$ dBFS input (worst-case input $f_S = 50$ kHz)                                           |

| Total Harmonic Distortion + Noise                                                                                    |      | -113   |       | dB   | $-3$ dBFS input (worst-case input $f_S = 50$ kHz)                                            |

| Sample Rate                                                                                                          | 5    |        | 50    | kHz  |                                                                                              |

| SRC DIGITAL INTERPOLATION FILTER CHARACTERISTICS                                                                     |      |        |       |      | At 48 kHz, guaranteed by design                                                              |

| Pass Band                                                                                                            |      | 21.678 |       | kHz  |                                                                                              |

| Pass-Band Ripple                                                                                                     |      | 0.005  |       | dB   |                                                                                              |

| Stop Band                                                                                                            |      | 26.232 |       | kHz  |                                                                                              |

| Stop-Band Attenuation                                                                                                |      | 110    |       | dB   |                                                                                              |

| Group Delay                                                                                                          |      | 876    |       | μs   |                                                                                              |

| DIGITAL INPUT/OUTPUT                                                                                                 |      |        |       | '    |                                                                                              |

| Input Voltage High (V <sub>IH</sub> )                                                                                | 2.0  |        | ODVDD | V    |                                                                                              |

| Input Voltage Low (V <sub>L</sub> )                                                                                  |      |        | 0.8   | V    |                                                                                              |

| Input Leakage                                                                                                        |      |        |       |      |                                                                                              |

| I <sub>IH</sub> (SDINO, SDIN1, SDIN2, SDIN3, LRCLKO,<br>LRCLK1, LRCLK2, BCLKO, BCLK1, BCLK2,<br>SPDIF_OUT, SPDIF_IN) |      | 40     |       | μΑ   | $V_{IH}$ = ODVDD, equivalent to a 90 k $\Omega$ pull-up resistor                             |

| I <sub>IH</sub> (RESET)                                                                                              |      | 13.5   |       | μΑ   | $V_{IH} = ODVDD$ , equivalent to a 266 k $\Omega$ pull-up resistor                           |

| I <sub>IL</sub> (SDO0, SCL, SDA)                                                                                     |      | -40    |       | μA   | $V_{\parallel} = 0 \text{ V}$ , equivalent to a 90 k $\Omega$ pull-down resistor             |

| Output Voltage High (V <sub>OH</sub> )                                                                               | 2.4  |        |       | v    | I <sub>OH</sub> = 0.4 mA                                                                     |

| Output Voltage Low (V <sub>OL</sub> )                                                                                |      |        | 0.4   | V    | $I_{OL} = -2 \text{ mA}$                                                                     |

| Output Voltage High (VoH) (MCLK_OUT)                                                                                 | 1.4  |        |       | V    | $I_{OH} = 0.4 \text{ mA}$                                                                    |

| Output Voltage Low (V <sub>OL</sub> ) (MCLK_OUT)                                                                     |      |        | 0.4   | V    | $I_{OL} = -3.2 \text{ mA}$                                                                   |

| Input Capacitance                                                                                                    |      | 10     |       | pF   |                                                                                              |

| SUPPLIES                                                                                                             |      |        |       | · ·  |                                                                                              |

| Analog Supplies (AVDD)                                                                                               | 3.0  | 3.3    | 3.6   | V    |                                                                                              |

| Digital Supplies (DVDD)                                                                                              | 1.65 | 1.8    | 2.0   | V    |                                                                                              |

| Interface Supply (ODVDD)                                                                                             | 3.0  | 3.3    | 3.6   | V    |                                                                                              |

| Supply Currents                                                                                                      |      |        |       |      | MCLK = 24 MHz, ADCs and DACs active, headphone outputs active and driving a 16 $\Omega$ load |

| Analog Current                                                                                                       |      | 260    |       | mA   |                                                                                              |

| Digital Current                                                                                                      |      | 350    |       | mA   |                                                                                              |

| Interface Current                                                                                                    |      | 2      |       | mA   |                                                                                              |

| Power Dissipation                                                                                                    |      | 1.495  |       | W    |                                                                                              |

| Standby Currents                                                                                                     |      |        |       |      | ADC, DAC, and headphone outputs floating, RESET low,                                         |

| Analog Current                                                                                                       |      | 10     |       | mA   |                                                                                              |

| Digital Current                                                                                                      |      | 4      |       | mA   |                                                                                              |

| Interface Current                                                                                                    |      | 1.6    |       | mA   |                                                                                              |

| TEMPERATURE RANGE                                                                                                    |      |        |       |      |                                                                                              |

| Operating Temperature                                                                                                | -40  |        | +85   | °C   |                                                                                              |

| Storage Temperature                                                                                                  | -65  |        | +150  | °C   |                                                                                              |

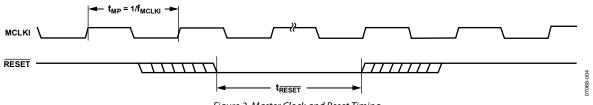

### **TIMING SPECIFICATIONS**

Table 2.

| Parameter               | Description         | Min             | Max    | Unit | Comments                                        |

|-------------------------|---------------------|-----------------|--------|------|-------------------------------------------------|

| MASTER CLOCK AND RESET  |                     |                 |        |      |                                                 |

| f <sub>MCLKI</sub>      | MCLKI frequency     | 3.072           | 24.576 | MHz  |                                                 |

| t <sub>MCH</sub>        | MCLKI high          | 10              |        | ns   |                                                 |

| t <sub>MCL</sub>        | MCLKI low           | 10              |        | ns   |                                                 |

| t <sub>reset</sub>      | RESET low           | 200             |        | ns   |                                                 |

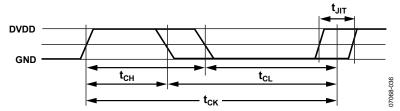

| MASTER CLOCK OUTPUT     |                     |                 |        |      |                                                 |

| tлт                     | Period jitter       |                 | 800    | ps   |                                                 |

| t <sub>CH</sub>         | MCLK_OUT high       | 45              | 55     | %    |                                                 |

| tcı                     | MCLK_OUT low        | 45              | 55     | %    |                                                 |

| I <sup>2</sup> C PORT   |                     |                 |        |      |                                                 |

| f <sub>SCL</sub>        | SCL clock frequency |                 | 400    | kHz  |                                                 |

| tsclh                   | SCL high            | 600             |        | ns   |                                                 |

| tscll                   | SCL low             | 1.3             |        | μs   |                                                 |

| Start Condition         |                     |                 |        | '    |                                                 |

| tscs                    | Setup time          | 600             |        | ns   | Relevant for repeated start condition           |

| t <sub>SCH</sub>        | Hold time           | 600             |        | ns   | After this period, the first clock is generated |

| t <sub>DS</sub>         | Data setup time     | 100             |        | ns   |                                                 |

| t <sub>SCR</sub>        | SCL rise time       |                 | 300    | ns   |                                                 |

| t <sub>SCF</sub>        | SCL fall time       |                 | 300    | ns   |                                                 |

| t <sub>SDR</sub>        | SDA rise time       |                 | 300    | ns   |                                                 |

| t <sub>SDF</sub>        | SDA fall time       |                 | 300    | ns   |                                                 |

| Stop Condition          |                     |                 |        |      |                                                 |

| <b>t</b> scs            | Setup time          | 0               |        | ns   |                                                 |

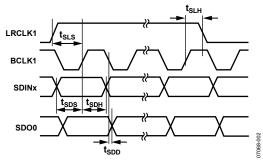

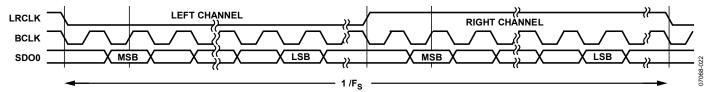

| SERIAL PORTS            |                     |                 |        |      |                                                 |

| Slave Mode              |                     |                 |        |      |                                                 |

| <b>t</b> <sub>SBH</sub> | BCLK high           | 40              |        | ns   |                                                 |

| t <sub>SBL</sub>        | BCLK low            | 40              |        | ns   |                                                 |

| $f_{SBF}$               | BCLK frequency      | $64 \times f_S$ |        |      |                                                 |

| t <sub>SLS</sub>        | LRCLK setup         | 10              |        | ns   | To BCLK rising edge                             |

| t <sub>SLH</sub>        | LRCLK hold          | 10              |        | ns   | From BCLK rising edge                           |

| t <sub>SDS</sub>        | SDIN setup          | 10              |        | ns   | To BCLK rising edge                             |

| $t_{SDH}$               | SDIN hold           | 10              |        | ns   | From BCLK rising edge                           |

| t <sub>SDD</sub>        | SDO delay           |                 | 50     | ns   | From BCLK falling edge                          |

| Master Mode             |                     |                 |        |      | _                                               |

| t <sub>MLD</sub>        | LRCLK delay         |                 | 25     | ns   | From BCLK falling edge                          |

| $t_{MDD}$               | SDO delay           |                 | 15     | ns   | From BCLK falling edge                          |

| t <sub>MDS</sub>        | SDIN setup          | 10              |        | ns   | From BCLK rising edge                           |

| t <sub>MDH</sub>        | SDIN hold           | 10              |        | ns   | From BCLK rising edge                           |

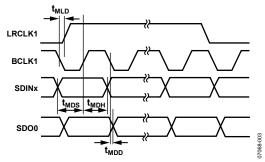

#### **TIMING DIAGRAMS**

Figure 2. Master Clock and Reset Timing

Figure 3. Master Clock Output Timing

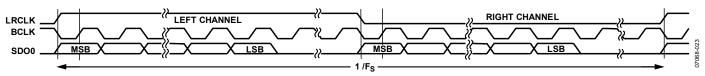

Figure 4. Serial Port Slave Mode Timing

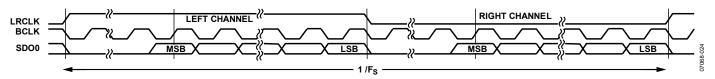

Figure 5. Serial Port Master Mode Timing

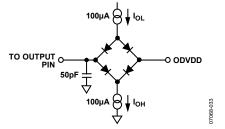

Figure 6. Load Circuit for Digital Output Timing Specifications

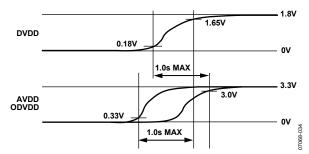

Figure 7. Power-Up Sequence Timing

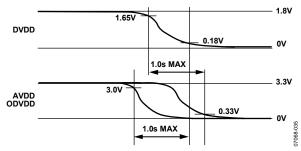

Figure 8. Power-Down Sequence Timing

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter          | Rating                             |

|--------------------|------------------------------------|

| DVDD to DGND       | 0 V to 2.2 V                       |

| ODVDD to DGND      | 0 V to 4 V                         |

| AVDD to AGND       | 0 V to 4 V                         |

| AGND to DGND       | -0.3 V to +0.3 V                   |

| Digital Inputs     | DGND - 0.3 V to ODVDD + 0.3 V      |

| Analog Inputs      | AGND – 0.3 V to AVDD + 0.3 V       |

| Reference Voltage  | Indefinite short circuit to ground |

| Soldering (10 sec) | 300°C                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 4. Thermal Resistance<sup>1</sup>

| Package Type | θја  | θıc | Unit |

|--------------|------|-----|------|

| 80-Lead LQFP | 38.1 | 7.6 | °C/W |

<sup>&</sup>lt;sup>1</sup>Based on JEDEC 2S2P PCB.

#### THERMAL CONDITIONS

To ensure correct operation of the device, the case temperature ( $T_{CASE}$ ) must be kept below 121°C to keep the junction temperature ( $T_{J}$ ) below the maximum allowed, 125°C.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

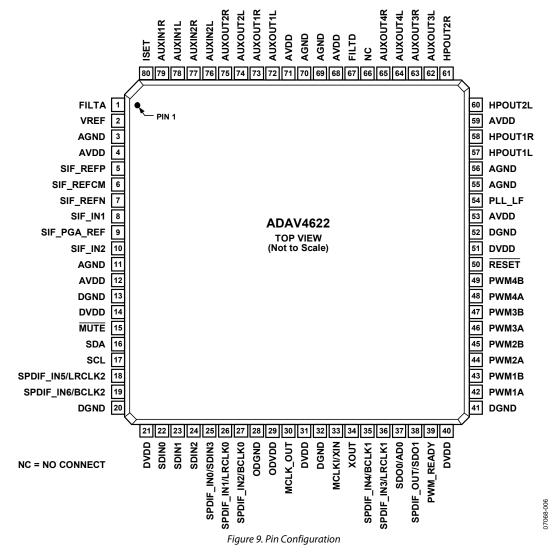

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic    | Description                                  |

|---------|-------------|----------------------------------------------|

| 1       | FILTA       | ADC Filter Capacitor.                        |

| 2       | VREF        | Reference Capacitor.                         |

| 3       | AGND        | ADC Ground.                                  |

| 4       | AVDD        | ADC Supply (3.3 V).                          |

| 5       | SIF_REFP    | SIF ADC Positive Reference (Typical 1.4 V).  |

| 6       | SIF_REFCM   | SIF ADC Common-Mode Reference (Typical 1 V). |

| 7       | SIF_REFN    | SIF ADC Negative Reference (Typical 0.6 V).  |

| 8       | SIF_IN1     | SIF Input 1.                                 |

| 9       | SIF_PGA_REF | SIF PGA Reference.                           |

| 10      | SIF_IN2     | SIF Input 2.                                 |

| 11      | AGND        | SIF AGND.                                    |

| 12      | AVDD        | SIF Supply (3.3 V).                          |

| 13      | DGND        | Digital Ground.                              |

| 14      | DVDD        | Digital Supply (1.8 V).                      |

| 15      | MUTE        | Active Low Mute Request Input Signal.        |

| Pin No.  | Mnemonic         | Description                                                                                                               |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------------|

| 16       | SDA              | I <sup>2</sup> C Data.                                                                                                    |

| 17       | SCL              | I <sup>2</sup> C Clock.                                                                                                   |

| 18       | SPDIF_IN5/LRCLK2 | External Input to S/PDIF Mux/Left/Right Clock for SRC2 (Default).                                                         |

| 19       | SPDIF_IN6/BCLK2  | External Input to S/PDIF Mux/Bit Clock for SRC2 (Default).                                                                |

| 20       | DGND             | Digital Ground.                                                                                                           |

| 21       | DVDD             | Digital Supply (1.8 V).                                                                                                   |

| 22       | SDIN0            | Serial Data Input 0/SRC Data Input.                                                                                       |

| 23       | SDIN1            | Serial Data Input 1/SRC Data Input.                                                                                       |

| 24       | SDIN2            | Serial Data Input 2/SRC Data Input.                                                                                       |

| 25       | SPDIF_IN0/SDIN3  | External Input to S/PDIF Mux/SRC Data Input/Serial Data Input 3 (Default).                                                |

| 26       | SPDIF_IN1/LRCLK0 | External Input to S/PDIF Mux/Left/Right Clock for SRC1 (Default).                                                         |

| 27       | SPDIF_IN2/BCLK0  | External Input to S/PDIF Mux/Bit Clock for SRC1 (Default).                                                                |

| 28       | ODGND            | Digital Ground.                                                                                                           |

| 29       | ODVDD            | Digital Interface Supply (3.3 V).                                                                                         |

| 30       | MCLK_OUT         | Master Clock Output.                                                                                                      |

| 31       | DVDD             | Digital Supply (1.8 V).                                                                                                   |

| 32       | DGND             | Digital Ground.                                                                                                           |

| 33       | MCLKI/XIN        | Master Clock/Crystal Input.                                                                                               |

| 33<br>34 | XOUT             | Crystal Output.                                                                                                           |

|          |                  | •                                                                                                                         |

| 35       | SPDIF_IN4/BCLK1  | External Input to S/PDIF Mux/Bit Clock for Serial Data I/O (Default).                                                     |

| 36<br>37 | SPDIF_IN3/LRCLK1 | External Input to S/PDIF Mux/Left/Right Clock for Serial Data I/O (Default).                                              |

| 37       | SDO0/AD0         | Serial Data Output. This pin acts as the I <sup>2</sup> C address select on reset. It has an internal pull-down resistor. |