1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## Si53102-A1/A2/A3 Data Sheet

### PCI-Express Gen 1, Gen 2, Gen 3, and Gen 4 1:2 Fan-out Clock Buffer

Si53102-A1/A2/A3 is a family of high-performance 1:2 PCIe fan output buffers. This lowadditive-jitter clock buffer family is compliant to PCIe Gen 1, Gen 2, Gen 3, and Gen 4 specifications. The ultra-small footprint (1.4x1.6 mm) and industry-leading low power consumption make the Si53102-A1/A2/A3 the ideal clock solution for consumer and embedded applications. Measuring PCIe clock jitter is quick and easy with the Silicon Labs PCIe Clock Jitter Tool. Download it for free at www.silabs.com/pcie-learningcenter.

#### Applications

- Network Attached Storage

- Multi-function Printer

- Wireless Access Point

- · Server/Storage

#### KEY FEATURES

- PCI-Express Gen 1, Gen 2, Gen 3, and Gen 4 common clock compliant

- Two low-power PCIe clock outputs

- Supports Serial-ATA (SATA) at 100 MHz

- No termination resistors required for differential clocks

- 2.5 V or 3.3 V Power supply

- Spread Spectrum Tolerant

- Extended Temperature Range

-40 to 85 °C

- Small package 8-pin TDFN (1.4 x 1.6 mm)

- For PCIe Gen 1: Si53102-A1

- For PCIe Gen 2: Si53102-A2

- For PCIe Gen 3/4: Si53102-A3

## 1. Ordering Guide

#### Table 1.1. Ordering Guide

| Part Number    | Package Type             | Temperature            |

|----------------|--------------------------|------------------------|

| Si53102-A1-GM  | 8-pin TDFN               | Extended, -40 to 85 °C |

| Si53102-A1-GMR | 8-pin TDFN—Tape and Reel | Extended, -40 to 85 °C |

| Si53102-A2-GM  | 8-pin TDFN               | Extended, -40 to 85 °C |

| Si53102-A2-GMR | 8-pin TDFN—Tape and Reel | Extended, -40 to 85 °C |

| Si53102-A3-GM  | 8-pin TDFN               | Extended, -40 to 85 °C |

| Si53102-A3-GMR | 8-pin TDFN—Tape and Reel | Extended, -40 to 85 °C |

## **Table of Contents**

| 1. | Ordering Guide               |

|----|------------------------------|

| 2. | Electrical Specifications    |

| 3. | Test and Measurement Setup   |

| 4. | Recommended Design Guideline |

| 5. | Pin Descriptions             |

| 6. | Package Outline              |

| 7. | Land Pattern                 |

| 8. | Revision History             |

|    | 8.1 Revision 1.0             |

|    | 8.2 Revision 1.1             |

|    | 8.3 Revision 1.2             |

|    | 8.4 Revision 1.3             |

## 2. Electrical Specifications

| Parameter                     | Symbol          | Test Condition | Min  | Тур | Мах  | Unit |

|-------------------------------|-----------------|----------------|------|-----|------|------|

| Supply Voltage (3.3 V Supply) | V <sub>DD</sub> | 3.3 V ± 10%    | 2.97 | 3.3 | 3.63 | V    |

| Supply Voltage (2.5 V Supply) | V <sub>DD</sub> | 2.5 V ± 10%    | 2.25 | 2.5 | 2.75 | V    |

### Table 2.1. Recommended Operating Conditions

#### Table 2.2. DC Electrical Specifications

| Parameter                                   | Symbol           | Test Condition         | Min  | Тур  | Мах  | Unit |

|---------------------------------------------|------------------|------------------------|------|------|------|------|

| Operating Voltage (V <sub>DD</sub> = 3.3 V) | V <sub>DD</sub>  | 3.3 V ± 10%            | 2.97 | 3.30 | 3.63 | V    |

| Operating Voltage (V <sub>DD</sub> = 2.5 V) | V <sub>DD</sub>  | 2.5 V ± 10%            | 2.25 | 2.5  | 2.75 | V    |

| Operating Supply Current                    | I <sub>DD</sub>  | Full Active            | _    | _    | 15   | mA   |

| Input Pin Capacitance                       | C <sub>IN</sub>  | Input Pin Capacitance  | _    | 3    | 5    | pF   |

| Output Pin Capacitance                      | C <sub>OUT</sub> | Output Pin Capacitance |      |      | 5    | pF   |

## Table 2.3. AC Electrical Specifications<sup>1, 2, 3</sup>

| Parameter                                | Symbol                          | Condition                                  | Min  | Тур | Мах  | Unit |

|------------------------------------------|---------------------------------|--------------------------------------------|------|-----|------|------|

| DIFFIN at 0.7 V                          |                                 |                                            |      |     |      |      |

| Input frequency                          | Fin                             |                                            | 10   | 100 | 175  | MHz  |

| DIFFIN and DIFFINb                       | T <sub>R</sub> / T <sub>F</sub> | Single ended measurement:                  | 0.6  | _   | 4    | V/ns |

| Rising/Falling Slew Rate                 |                                 | VOL = 0.175 to VOH =<br>0.525 V (Averaged) |      |     |      |      |

| Differential Input High Volt-<br>age     | V <sub>IH</sub>                 |                                            | 150  | _   | _    | mV   |

| Differential Input Low Volt-<br>age      | V <sub>IL</sub>                 |                                            | —    |     | -150 | mV   |

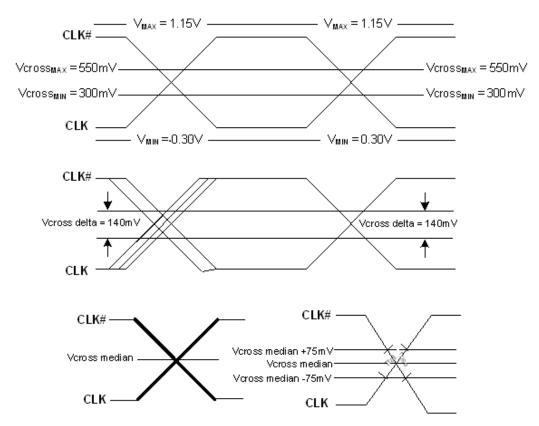

| Crossing Point Voltage at<br>0.7 V Swing | V <sub>OX</sub>                 | Single-ended measurement                   | 250  | _   | 550  | mV   |

| Vcross Variation Over All edges          | ΔV <sub>OX</sub>                | Single-ended measurement                   | _    | _   | 140  | mV   |

| Differential Ringback Volt-<br>age       | V <sub>RB</sub>                 |                                            | -100 | _   | 100  | mV   |

| Time before Ringback Al-<br>lowed        | T <sub>STABLE</sub>             |                                            | 500  | _   | _    | ps   |

| Absolute Maximum Input<br>Voltage        | V <sub>MAX</sub>                |                                            |      | _   | 1.15 | V    |

| Absolute Minimum Input<br>Voltage        | V <sub>MIN</sub>                |                                            | -0.3 | _   | _    | V    |

| Parameter                           | Symbol                | Condition                         | Min | Тур | Мах  | Unit |

|-------------------------------------|-----------------------|-----------------------------------|-----|-----|------|------|

| DIFFIN and DIFFINb Duty<br>Cycle    | T <sub>DC</sub>       | Measured at crossing point<br>VOX | 45  | _   | 55   | %    |

| Rise/Fall Matching                  | T <sub>RFM</sub>      | Determined as a fraction of       |     | _   | 20   | %    |

|                                     |                       | 2 x (TR – TF)/(TR + TF)           |     |     |      |      |

| DIFF Clocks                         |                       | 1 1                               |     |     |      |      |

| Duty Cycle                          | T <sub>DC</sub>       | Measured at crossing point<br>VOX | 45  | -   | 55   | %    |

| Output Skew                         | T <sub>SKEW</sub>     | Measured at 0 V differential      | —   | _   | 100  | ps   |

| Frequency Accuracy                  | F <sub>ACC</sub>      | All output clocks                 |     | _   | 100  | ppm  |

| Slew Rate                           | t <sub>r/f2</sub>     | Measured differentially from      | 0.6 | _   | 4.0  | V/ns |

|                                     |                       | ±150 mV                           |     |     |      |      |

| PCIe Gen 1 Pk-Pk Additive           | Pk-Pk <sub>GEN1</sub> | PCle Gen 1                        | _   | _   | 10   | ps   |

| Jitter                              |                       | Si53102-A1                        |     |     |      |      |

| PCIe Gen 2 Additive Phase           | RMS <sub>GEN2</sub>   | 10 kHz < F < 1.5 MHz,             | _   | _   | 0.50 | ps   |

| Jitter                              |                       | Si53102-A2                        |     |     |      |      |

| PCIe Gen 2 Additive Phase           | RMS <sub>GEN2</sub>   | 1.5 MHz < F < Nyquist,            | _   | _   | 0.50 | ps   |

| Jitter                              |                       | Si53102-A2                        |     |     |      |      |

| PCIe Gen 3 Additive Phase           | RMS <sub>GEN3</sub>   | Includes PLL BW 2–4 MHz,          | _   | _   | 0.22 | ps   |

| Jitter                              |                       | CDR = 10 MHz,                     |     |     |      |      |

|                                     |                       | Si53102-A3, VDD=3.3 V             |     |     |      |      |

|                                     |                       | Includes PLL BW 2–4 MHz,          | —   | _   | 0.25 | ps   |

|                                     |                       | CDR = 10 MHz,                     |     |     |      |      |

|                                     |                       | Si53102-A3, VDD=2.5V              |     |     |      |      |

| PCIe Gen 4 Additive Phase           | RMS <sub>GEN4</sub>   | PCIe Gen4, VDD=3.3V               | _   | _   | 0.20 | ps   |

| Jitter                              |                       | PCIe Gen4, VDD=2.5V               |     |     | 0.25 | ps   |

| Crossing Point Voltage at           | V <sub>OX</sub>       | VDD = 3.3 V                       | 300 | _   | 550  | mV   |

| 0.7 V Swing VDD = 2                 |                       | VDD = 2.5 V                       | 200 | _   | 550  | mV   |

| Enable/Disable and Setup            |                       |                                   |     |     |      |      |

| Clock Stabilization from<br>Powerup | T <sub>STABLE</sub>   | Power up to first output — —      |     | 3.0 | ms   |      |

2. Gen 4 specifications based on the PCI-Express Base Specification 4.0 rev. 0.5.

3. Download the Silicon Labs PCIe Clock Jitter Tool at www.silabs.com/pcie-learningcenter.

| Parameter                             | Symbol            | Condition       | Min | Тур | Мах  | Unit |

|---------------------------------------|-------------------|-----------------|-----|-----|------|------|

| Temperature, Storage                  | Τ <sub>S</sub>    | Non-functional  | -65 |     | 150  | °C   |

| Temperature, Operating<br>Ambient     | Τ <sub>Α</sub>    | Functional      | -40 |     | 85   | °C   |

| Temperature, Junction                 | TJ                | Functional      | _   |     | 150  | °C   |

| Dissipation, Junction to<br>Case      | $\theta_{\rm JC}$ | JEDEC (JESD 51) | _   |     | 38.3 | °C/W |

| Dissipation, Junction to Am-<br>bient | $\theta_{JA}$     | JEDEC (JESD 51) | _   |     | 90.4 | °C/W |

#### Table 2.4. Thermal Conditions

#### Table 2.5. Absolute Maximum Conditions

| Parameter                            | Symbol               | Condition                   | Min  | Тур | Max | Unit            |

|--------------------------------------|----------------------|-----------------------------|------|-----|-----|-----------------|

| Main Supply Voltage                  | V <sub>DD_3.3V</sub> |                             | _    |     | 4.6 | V               |

| Input Voltage                        | V <sub>IN</sub>      | Relative to V <sub>SS</sub> | -0.5 |     | 4.6 | V <sub>DC</sub> |

| ESD Protection (Human<br>Body Model) | ESD <sub>HBM</sub>   | JEDEC (JESD 22-A114)        | 2000 |     | _   | V               |

| Flammability Rating                  | UL-94                | UL (Class)                  | V-0  |     |     |                 |

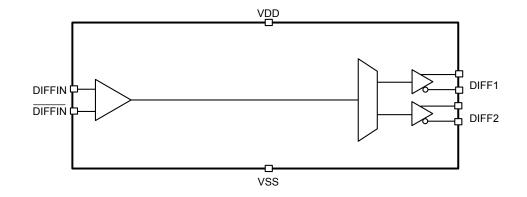

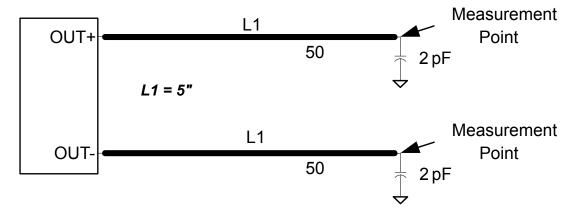

#### 3. Test and Measurement Setup

The following figures show the test load configurations for the differential clock signals.

Figure 3.1. 0.7 V Differential Load Configuration

The outputs from this device can also support LVDS, LVPECL, or CML differential signaling levels using alternative termination. For recommendations on how to achieve this, see "AN781: Alternative Output Termination for Si5211x, Si5213x, Si5214x, Si5216x, Si5310x, Si5311x, and Si5315x PCIe Clock Generator and Buffer Families.

Figure 3.2. Differential Measurement for Differential Output Signals (AC Parameters Measurement)

Figure 3.3. Single-Ended Measurement for Differential Output Signals (AC Parameters Measurement)

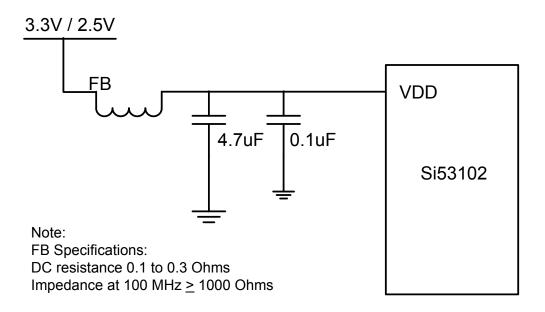

## 4. Recommended Design Guideline

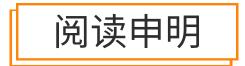

Figure 4.1. Recommended Application Schematic

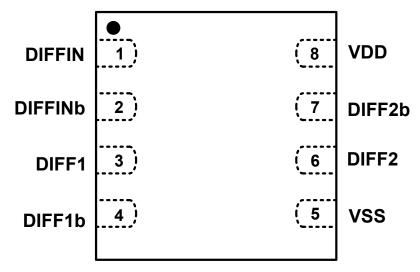

## 5. Pin Descriptions

| Pin # | Name    | Туре   | Description                              |

|-------|---------|--------|------------------------------------------|

| 1     | DIFFIN  | O, DIF | 0.7 V, 100 MHz differentials clock input |

| 2     | DIFFINb | O, DIF | 0.7 V, 100 MHz differentials clock input |

| 3     | DIFF1   | O, DIF | 0.7 V, 100 MHz differential clock output |

| 4     | DIFF1b  | O, DIF | 0.7 V, 100 MHz differential clock output |

| 5     | GND     | GND    | Ground                                   |

| 6     | DIFF2   | O, DIF | 0.7 V, 100 MHz differential clock output |

| 7     | DIFF2b  | O, DIF | 0.7 V, 100 MHz differential clock output |

| 8     | VDD     | PWR    | 2.5 V or 3.3 V Power supply              |

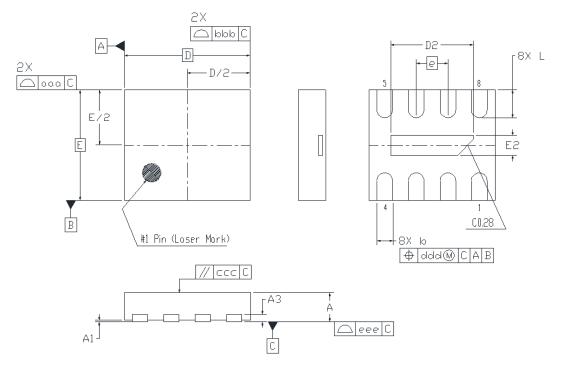

## 6. Package Outline

The figure below illustrates the package details for the Si53102-A1-A2-A3 in an 8-Pin TDFN package. The table lists the values for the dimensions shown in the illustration.

Figure 6.1. 8-Pin TDFN Package Drawing

| Dimension | Min      | Nom       | Мах  |  |  |

|-----------|----------|-----------|------|--|--|

| A         | 0.70     | 0.75      | 0.80 |  |  |

| A1        | 0.00     | 0.02      | 0.05 |  |  |

| A3        |          | 0.20 REF. |      |  |  |

| b         | 0.15     | 0.20      | 0.25 |  |  |

| D         |          | 1.60 BSC  |      |  |  |

| D2        | 1.00     | 1.10      |      |  |  |

| e         | 0.40 BSC |           |      |  |  |

| E         | 1.40 BSC |           |      |  |  |

| E2        | 0.20     | 0.25      | 0.30 |  |  |

| L         | 0.30     | 0.35      | 0.40 |  |  |

| ааа       |          | 0.10      |      |  |  |

| bbb       | 0.10     |           |      |  |  |

| ссс       | 0.10     |           |      |  |  |

| ddd       | 0.07     |           |      |  |  |

| eee       |          | 0.08      |      |  |  |

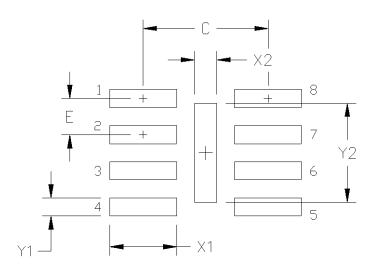

#### 7. Land Pattern

The following figure illustrates the land pattern details for the Si53102-A1-A2-A3 in an 8-Pin TDFN package. The table lists the values for the dimensions shown in the illustration.

Figure 7.1. 8-Pin TDFN Land Pattern

#### Table 7.1. Land Pattern Dimensions

| mm   |

|------|

| 1.40 |

| 0.40 |

| 0.75 |

| 0.20 |

| 0.25 |

| 1.10 |

|      |

#### Notes:

#### General

- 1. All dimensions shown are in millimeters (mm).

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

- 3. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

#### Solder Mask Design

1. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60 µm minimum, all the way around the pad.

#### Stencil Design

- 1. A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 2. The stencil thickness should be 0.125 mm (5 mils).

- 3. The ratio of stencil aperture to land pad size should be 1:1 for all pads.

#### **Card Assembly**

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

## 8. Revision History

#### 8.1 Revision 1.0

Full-production revision from Rev 0.4

- Updated AC Electrical Specifications table.

- Updated input frequency min and max specs.

- Updated Test and Measurement Setup section.

- Added text and reference to AN781.

#### 8.2 Revision 1.1

- Moved Recommended Design Guideline section.

- Updated Pin Descriptions.

- Updated Package Outline.

- Added Land Pattern.

#### 8.3 Revision 1.2

- Updated Features.

- Updated Description.

- Updated AC Electrical Specifications table.

#### 8.4 Revision 1.3

- Updated IDD max specification.

- Separated VOX into 2.5 V and 3.3 V specifications.

- Separated PCie Gen3 jitter into 2.5 V and 3.3 V specifications.

- Separated PCIe Gen4 jitter into 2.5 V and 3.3 V specifications.

#### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com