## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

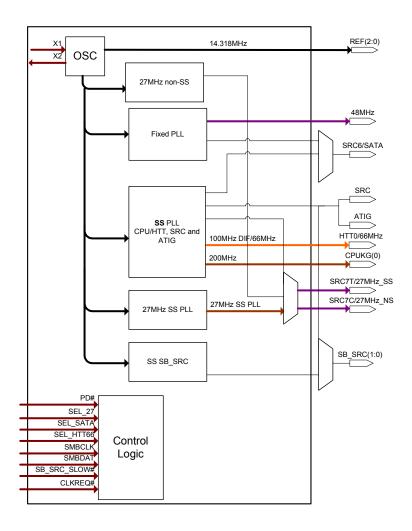

## System Clock for Embedded AMD<sup>TM</sup> based Systems

#### **Recommended Application:**

AMD M690T/780E systems

#### **Output Features:**

- Integrated series resistors on all differential outputs.

- 1 Greyhound compatible low-power CPU pair

- 6 low-power differential SRC pairs

- 2 low-power differential chipset SouthBridge SRC pairs

- 1 Selectable low-power differential 100MHz non-spread SATA/ SRC output

- 1 Selectable low-power differential SRC / 27MHz Single Ended output

- 1 Selectable HT3 100MHz low-power differential hypertransport clock / HT66MHz Single Ended output

- 2 48MHz USB clock

- 3 14.318MHz Reference clock

- 3 low-power differential ATIG pairs

- 5- Dedicated CLKREQ# pins

#### **Key Specifications:**

- CPU outputs cycle-to-cycle jitter < 150ps</li>

- SRC outputs cycle-to-cycle jitter < 125ps

- SB SRC outputs cycle-to-cycle jitter < 125ps</li>

- +/- 100ppm frequency accuracy on CPU, SRC, ATIG

- Oppm frequency accuracy on 48MHz

#### Features/Benefits:

Power Saving Features:

SB\_SRC\_SLOW# input to throttle Chipset clocks (SB\_SRC) to 80% of normal.

Optional Separate supply rail for SRC low Voltage I/O

- ~33% power saving when 1.5V is used for this rail

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus

- External crystal load capacitors for maximum frequency accuracy

1616—08/20/09

\*Other names and brands may be claimed as the property of others.

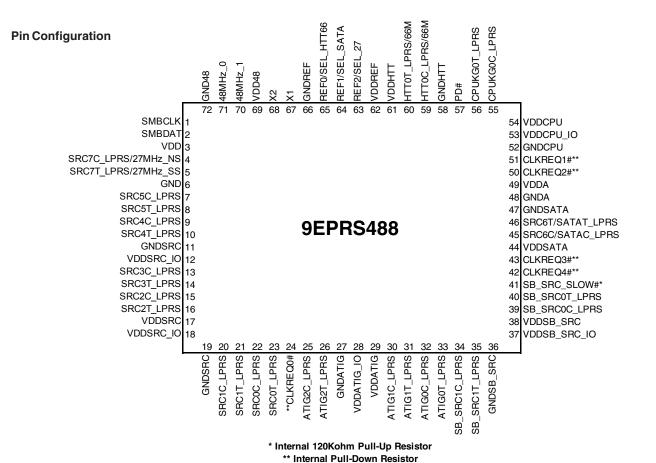

## **Pin Description**

| PRIA # PIN NAME PRIYEE IN Clock pin of SMBus circuity, 5V tolerant.  SMBCAT IN DO Data pin for SMBus circuity, 5V tolerant.  SMBCAT PRIS PROVEN BY Provided the Complement of SMBus circuity, 5V tolerant.  The clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm sensor pair pair pair pair pair pair pair pai                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | Description              |          |                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------|----------|------------------------------------------------------------------------------------------------------|

| SMEDAT   NO   Data in for SMBus circuity, 5V bolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIN # | PIN NAME                 | PIN TYPE |                                                                                                      |

| VDD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                          |          | Clock pin of SMBus circuitry, 5V tolerant.                                                           |

| SRC7C_LPRS27MHz_SS   OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2     |                          |          |                                                                                                      |

| series resistor needed ()27MHz 3.3 V Single-ended non-spread output for discrete graphics of SRCT_LPRS27MHz, SS OUT CPRS27MHz, SS OUT CPRS27MHz SS OUT SRC5_LPRS OUT SRC5_LPRS OUT CPRS27MHz SS OUT CPRS27MHz CPRS27MH | 3     | VDD                      | PWR      | 11.7                                                                                                 |

| Series resistor needed)2/MHz 3-3 Visingle-ended non-spread output for discrete graphics  6 SNO GND GND GND GND GND GND GND GND gover differential SRC clock pair. (no 500hm shunt resistor to GND and no 30 ohm senies resistor needed)2/MHz 3-3 Visingle-ended spreading output for discrete graphics  7 SRC5C_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  8 SRC5T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  9 SRC4C_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  10 SRC4T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  11 GNDSRC OND Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  12 VDDSRC IO PMR Power supply for differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  13 SRC3T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  14 SRC3T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  15 SRC3T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  16 SRC3T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  17 VDDSRC PWR Supply for SRC core, 33 N nominal 1 0.5V to 3.3V  18 SRC5T_LPRS OUT Gnorphomotic clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm senies resistor needed)  18 SRC5T_LPRS OUT Gnorphomotic clock of low power different | 1     | SRC7C LPRS/27MHz NS      | OUT      | True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm   |

| ohm senies resistor needed)/27/MHz 3.3V Single-ended spreading output for discrete graphics  ROSC_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT series resistor needed)  SRC4C_LPRS OUT series resistor needed)  SRC4C_LPRS OUT series resistor needed)  ROSSCC GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -     | 511070_E1 110/27W112_140 | 001      |                                                                                                      |

| omin sense resistor needed)/// White 23 y Single-ended spreading output for discrete graphics  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ROSC_LPRS OUT of series resistor needed)  ROSC_LPRS OUT STREET COMPLETE COMPLET | 5     | SBC7T LPBS/27MHz SS      | OUT      | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 |

| SRCSC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT SRC4C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT SRC4C_ | 3     | 311071_E1110/27WH12_99   | 0        | ohm series resistor needed)/27MHz 3.3V Single-ended spreading output for discrete graphics           |

| sRCS_LPRS OUT both series resistor needed)  SRC4C_LPRS OUT colock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  The clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT SRC4C_LPRS OUT SRC4C_LPRS OUT SRC4C_LPRS OUT SRC5C_LPRS OUT SRC5C_LPR | 6     | GND                      | GND      | Ground pin for SRC7/27MHz                                                                            |

| SRCST_LPRS OUT series resistor needed)  SRC4C_LPRS OUT colcox of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4C_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC4T_LPRS OUT series resistor needed)  SRC3C_LPRS OUT college from the series resistor needed)  SRC3C_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC3C_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC3C_LPRS OUT complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC3C_LPRS OUT clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  SRC3C_LPRS OUT series resistor needed)  IN series resistor needed)  SRC3C_LPRS OUT series resistor needed)  The clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resisto | 7     | SDCEC I DDS              | OUT      | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 |

| series resistor needed)  SRC4C_LPRS OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ,     | 511030_E1110             | 001      |                                                                                                      |

| Senes resistor needed)  SRC4C_LPRS  OUT  OUT  OUT  SRC4T_LPRS  OUT  OUT  OUT  OUT  OUT  OUT  OUT  OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | g     | SRC5T LPRS               | OUT      | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm   |

| SRC4T_LPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | G11001_E1110             | 001      |                                                                                                      |

| ohm series resistor needed) 11 GNDSRC GND Ground pin for the SRC outputs 12 VDDSRC_IO PWR Power supply for differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 13 SRC3C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 14 SRC3T_LPRS OUT True clock of the power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 15 SRC3C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 16 SRC3T_LPRS OUT True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 17 VDDSRC PWR Supply for SRC core, 3.37 nominal 1.05V to 3.3V 18 VDDSRC PWR Supply for SRC core, 3.37 nominal 1.05V to 3.3V 19 GNDSRC GND Ground pin for the SRC outputs 20 SRC1C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 21 SRC1T_LPRS OUT True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 22 SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 23 SRC0T_LPRS OUT True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 24 "CLKREOW" No SRC sequest pin for SRC outputs. If outputs is selected for control, then that output is controlled as follows: 0 centre of the series resistor needed) 25 ATIG2C_LPRS OUT True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 26 ATIG2T_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed) 36 ATIG2T_LPRS OUT True | a     | SRCAC I PRS              | OUT      | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 |

| 10   SNC41_LPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | J     | GITO40_EITTO             | 001      |                                                                                                      |

| Series resistor needed)  12 VDDSRC IO PWR Power supply for differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  13 SRC3C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  14 SRC3C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  15 SRC3C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  16 SRC3C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  17 VDDSRC PWR Supply for SRC core, 3.3Y nominal  18 VDDSRC IO PWR Power supply for differential SRC outputs, nominal 1.05V to 3.3V  19 GNDSRC GND Ground pin for the SRC outputs  20 SRC1C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  21 SRC1T_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  22 SRC3C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  23 SRC0T_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  24 "CLKREQ0# IN IN IN INTERPRETATION OF True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  25 ATIG2C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  26 ATIG2C_LPRS OUT Complement clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  27 GNDATIG OPWR Power supply for differential ATIG outp | 10    | SRC4T LPRS               | OUT      | True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm   |

| VDDSRC_IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -10   |                          | 001      | ,                                                                                                    |

| SRC3C_LPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11    | GNDSRC                   | GND      |                                                                                                      |

| obm series resistor needed)  14 SRC3C_LPRS  OUT  True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  15 SRC2C_LPRS  OUT  OUT  OUT  OUT  OUT  OUT  OUT  OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12    | VDDSRC_IO                | PWR      |                                                                                                      |

| SRC3T_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  PWR Supply for SRC core, 3.3V nominal  VDDSRC ID PWR Power supply for differential SRC outputs, nominal 1.05V to 3.3V  GND Ground pin for the SRC outputs  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  SRC1T_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  SRC0C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  SRC0C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt res | 13    | SBC3C LPBS               | OUT      | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 |

| SRC3_LPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -10   | G11000_E1110             |          |                                                                                                      |

| Series resistor needed)  OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  PWR Supply for SRC core, 3.3V nominal  NDSRC PWR Supply for differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  BY ODSRC GND GND Ground pin for the SRC outputs  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  O = enabled, 1 = Low-Low  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series r | 1.4   | SDC3T I DDS              | OUT      | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm   |

| ohm series resistor needed) True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  NDDSRC PWR Supply for SRC core, 3.3V nominal NDDSRC GND PWR Power supply for differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  RCC_LPRS OUT Complementary clock of low-power differ | 14    | 311031_EF113             | 001      |                                                                                                      |

| omm series resistor needed)  True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  RC1_LPRS OUT SRC core, 3.3V nominal  PWR Power supply for differential SRC outputs, nominal 1.05V to 3.3V  GNDSRC GND Ground pin for the SRC outputs  Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  RC1_LPRS OUT True clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  RC2_SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  RC2_SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  RC2_SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as to follows:  O = enabled, 1 = Low-Low  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 500hm shunt resistor to GND and no 33 ohm series resi | 15    | SBC2C LPBS               | OUT      | Complement clock of low power differential SRC clock pair. (no 500hm shunt resistor to GND and no 33 |

| SRC2F_LPRS OUT Series resistor needed)  PWR Supply for SRC core, 3.3V nominal  POWSRC_IO PWR QNDSRC GND GND Ground pin for the SRC outputs, nominal 1.05V to 3.3V  Complement clock of Iow power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  PROPER GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13    | SHOZO_EFHS               | 0        |                                                                                                      |

| VDDSRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16    | SDC2T LDDS               | OUT      | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm   |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10    | ShC21_LFh3               | 001      | ,                                                                                                    |

| 9 GNDSRC GND Ground pin for the SRC outputs Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows: 0 = enabled, 1 = Low-Low Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) GRODATIG GND Ground pin for the ATIG outputs. OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed) ATIG1C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt res | 17    |                          | PWR      |                                                                                                      |

| Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)   SRC1T_LPRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18    | VDDSRC_IO                | PWR      | Power supply for differential SRC outputs, nominal 1.05V to 3.3V                                     |

| SRC1C_LPRS OUT clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  22 SRC0C_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  23 SRC0C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  24 **CLKREQ0# IN clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  25 ATIG2C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  26 ATIG2T_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  27 GNDATIG GND GND GND GND GND GND GND GND GND GN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19    | GNDSRC                   | GND      |                                                                                                      |

| SRC1T_LPRS OUT SRC1T_LPRS OUT Sreiclock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  SRC0C_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  OUT Structure of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and  | 20    | SRC1C LPRS               | OUT      | Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 |

| SRCOC_LPRS OUT Series resistor needed)  OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRCO outputs. If output is selected for control, then that output is controlled as follows:  O = enabled, 1 = Low-Low  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential ATIG outputs, nominal 1.05V to 3.3V  Power supply for ATIG core, nominal 3.3V  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resi | 20    | SHOTO_ELTIO              | 001      |                                                                                                      |

| SRCOC_LPRS OUT Complement clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows:  0 = enabled, 1 = Low-Low Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS  OUT  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor t | 21    | SBC1T LPBS               | OUT      | True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm   |

| ohm series resistor needed)  SRCOT_LPRS  OUT  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS  OUT  OUT  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1C_LPRS  OUT  OUT  OUT  OUT  OUT  OUT  OUT  OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | GHOTI_EITHO              | 001      |                                                                                                      |

| SRCOT_LPRS OUT True clock of low power differential SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows: 0 = enabled, 1 = Low-Low  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG2T_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG2T_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  WDDATIG IO PWR Power supply for differential ATIG outputs, nominal 1.05V to 3.3V  VDDATIG IO PWR Power supply for ATIG core, nominal 3.3V  Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG1T_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG0T_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG0T_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  ATIG0T_LPRS OUT Complement clock of low power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  SB_SRC1T_LPRS OUT Complement clock of low power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resi | 22    | SBC0C LPBS               | OUT      |                                                                                                      |

| series resistor needed)  24 **CLKREQO# IN Clock Request pin for SRC0 outputs. If output is selected for control, then that output is controlled as follows: 0 = enabled, 1 = Low-Low  25 ATIG2C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  26 ATIG2T_LPRS OUT Tue clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  27 GNDATIG GND Ground pin for the ATIG outputs 28 VDDATIG PWR Power supply for ATIG core, nominal 3.3V  29 VDDATIG PWR Power supply for ATIG core, nominal 3.3V  30 ATIG1C_LPRS OUT Complementary clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  31 ATIG1T_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  32 ATIG0C_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  33 ATIG0T_LPRS OUT True clock of low-power differential push-pull PCI-Express pair with integrated series resistor. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  34 SB_SRC1C_LPRS OUT True clock of low-power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)  35 SB_SRC1T_LPRS OUT True clock of low power differential Chipset-to-Chipset SRC clock pair. (no 50ohm shunt resistor to GND and no 33 ohm series resistor needed)                                                                                                                                                                                                                                               |       | 5.1666_E. 116            |          |                                                                                                      |