1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# () IDT.

## DATASHEET

## 12-OUTPUT DIFFERENTIAL Z-BUFFER FOR PCIE GEN3 AND QPI

## 9ZX21200

## Description

The 9ZX21200 is a small-footprint 12-output differential buffer that meets all the performance requirements of the Intel DB1200Z specification. The 9ZX21200 is backwards compatible to PCIe Gen1 and Gen2 applications. A fixed, internal feedback path maintains low drift for critical QPI applications. In bypass mode, the 9ZX21200 can provide outputs up to 150MHz.

## **Recommended Application**

12-output PCIe Gen3/ QPI differential buffer for Romley and newer platforms

## **Key Specifications**

- Cycle-to-cycle jitter <50ps

- Output-to-output skew < 65 ps

- Input-to-output delay variation <50ps

- PCIe Gen3 phase jitter < 1.0ps RMS

- QPI 9.6GT/s 12UI phase jitter < 0.2ps RMS

## Features/Benefits

- Space-saving 56-pin package

- · Fixed feedback path for 0ps input-to-output delay

- 9 Selectable SMBus Addresses; Mulitple devices can share the same SMBus Segment

- 4 OE# pins; Hardware control of four outputs

- PLL or bypass mode; PLL can dejitter incoming clock

- 100MHz or 133MHz PLL mode operation; supports PCIe and QPI applications

- Selectable PLL bandwidth; minimizes jitter peaking in downstream PLL's

- Spread Spectrum Compatible; tracks spreading input clock for low EMI

- Software control of PLL Bandwidth and Bypass Settings/PLL can dejitter incoming clock (B Rev only)

## **Output Features**

• 12 - 0.7V differential HCSL output pairs

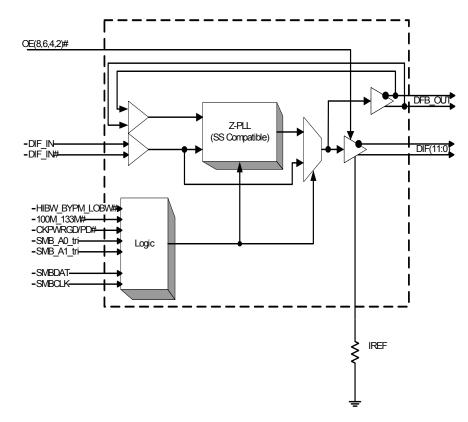

## **Block Diagram**

1

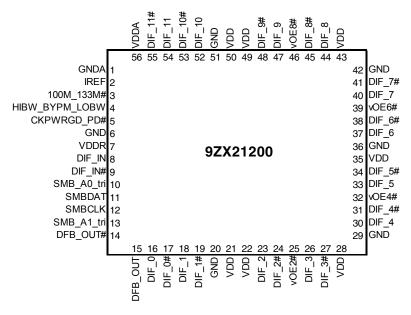

## **Pin Configuration**

Notes: Pins with ^ prefix have internal 120K pullup

Pins with v prefix have internal 120K pulldown. Even though the feedback path is fixed, the DFB\_OUT pair still needs a termination network for the part to function.

#### **Power Management Table**

| CKPWRGD_PD# | DIF_IN/<br>DIF_IN# | SMBus<br>EN bit | DIF(11:0)/<br>DIF(11:0)# | PLL STATE<br>IF NOT IN<br>BYPASS<br>MODE |

|-------------|--------------------|-----------------|--------------------------|------------------------------------------|

| 0           | Х                  | Х               | Low/Low                  | OFF                                      |

| 1           | Running            | 0               | Low/Low                  | ON                                       |

| 1           | nunning            | 1               | Running                  | ON                                       |

#### **MLF Power Connections**

|          | Pin Number  | r                  | <b>.</b>     |

|----------|-------------|--------------------|--------------|

| VDD      | VDD         | GND                | Description  |

| 56       |             | 1                  | Analog PLL   |

| 7        |             | 6                  | Analog Input |

| 21,35,50 | 22,28,43,49 | 20,29,36,42,<br>51 | DIF clocks   |

#### Functionality at Power-up (PLL mode)

| 100M_133M# | DIF_IN<br>MHz | DIF(11:0) |

|------------|---------------|-----------|

| 1          | 100.00        | DIF_IN    |

| 0          | 1 33.33       | DIF_IN    |

#### PLL Operating Mode Readback Table

| HiBW_BypM_LoBW# | Byte0, bit 7 | Byte 0, bit 6 |

|-----------------|--------------|---------------|

| Low (Low BW)    | 0            | 0             |

| Mid (Bypass)    | 0            | 1             |

| High (High BW)  | 1            | 1             |

#### PLL Operating Mode Table

| HiBW_BypM_LoBW#        | MODE      |

|------------------------|-----------|

| Low                    | PLL Lo BW |

| Mid                    | Bypass    |

| High                   | PLL Hi BW |

| NOTE: DLL in OFF in By | naca Mada |

NOTE: PLL is OFF in Bypass Mode

#### **Tri-Level Input Thresholds**

| Level | Voltage                           |

|-------|-----------------------------------|

| Low   | <0.8V                             |

| Mid   | 1.2 <vin<1.8v< th=""></vin<1.8v<> |

| High  | Vin > 2.2V                        |

#### 9ZX21200 SMBus Addressing

| Pi         | Pin        |               |  |  |  |

|------------|------------|---------------|--|--|--|

| SMB_A1_tri | SMB_A0_tri | SMBus Address |  |  |  |

| 0          | 0          | D8            |  |  |  |

| 0          | М          | DA            |  |  |  |

| 0          | 1          | DE            |  |  |  |

| М          | 0          | C2            |  |  |  |

| М          | М          | C4            |  |  |  |

| М          | 1          | C6            |  |  |  |

| 1          | 0          | CA            |  |  |  |

| 1          | М          | CC            |  |  |  |

| 1          | 1          | CE            |  |  |  |

2

9ZX21200

## **Pin Descriptions**

| 2   IREF   OUT   resistor to ground. 4750hm is the standard value for 1000hm differential impedance. Other impedances require different values. See data sheet.     3   100M_133M#   IN   3.3V Input to select operating frequency See Functionality Table for Definition     4   HIBW_BYPM_LOBW#   IN   Trilevel input to select High BW, Bypass or Low BW mode. See PLL Operating Mode Table for Details.     5   CKPWRGD_PD#   IN   Trilevel input to select not analy and the probability. See PLL Operating Mode Table for Details.     6   GND   PWR   Ground pin.     7   VDDR   PWR   Ground pin.     8   DIF_IN   IN   0.7 V Differential input clock (receiver). This VDD should be treated as an analog power rail and filtered appropriately.     8   DIF_IN   IN   0.7 V Differential TRUE input     9   DIF_IN#   IN   0.7 V Differential Complementary Input     10   SMB_A0_tri   IN   SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A1 to decode 1 of 9 SMBus addresses.     11   SMBDAT   I/O   Data pin of SMBUS circuitry, 5V tolerant     12   SMBLA   IN   Clock pin of SMBUS circuitry, 5V tolerant     13   SMB_A1_tri   IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PIN #          | PIN NAME        | TYPE   | DESCRIPTION                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P     REF     OUT     resistor to ground 4750m is the standard value for 100chm differential impedance. Other impedances require different values. See data sheet.       3     10M_133M#     N     3.47 Imput to select dop and prequency see for the post to select Hot Table for Definition and start up on first hot senset.       6     INEW_SPFM_LOBW#     IN     Tribuel imput to select Hot Table for Definition and start up on first hot senset.       7     VDDR     PM     Northe advices to we start Power Down Mode.       8     INE IM     IN     0.77 Imput and the table and start up on first hot senset.       8     INE IM     IN     0.77 Imput and the advices and table and start up on first hot senset.       8     INE IM     IN     0.77 Imput and table and start up on first hot senset.       8     INE IM     IN     0.77 Imput and table and start to table and start up the advice in conjunction with the SMB_AD to decode 1 of 9       10     SMB_AD_1 fm     SMBus addresses     This is in the start end provides incedback signal to the PLL for synchronization with the information and start up addresses.       11     SMBus addresses     The start and start and start up addresses.     The start addresses.       12 </td <td>1</td> <td>GNDA</td> <td>PWR</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1              | GNDA            | PWR    |                                                                                                                                                                                                                       |

| 3     3.3 <sup>1</sup> Input to select High Englands       4     Hisky_BYPM_LOBW/     N       5     CKPWRGD_PDe     N       6     BND     PWR       7     VDDR     PWR       8     DRID     PWR       8     DRID     PWR       9     DRIN     Notifies device to sample latched input and start up on first high assertion, or exit Power Down Mode       6     GND     PWR     337 byower for differential ruput dock (receiver). This VDD should be treated as an analog power rail and fillered appropriately.       8     DFL IN     IN     0.7 V Dfferential TRUE input       9     DFL IN     IN     0.7 V Dfferential Complementary input       10     SMB_AD_Ltri     IN     SMBus Addresses.       11     SMBDAT     IO     Data prior SMBUS Scrutzly, SV betrant       12     SMBLAL     IN     SMBus Addresses.       13     SMBLAL     IN     MBus Addresses.     INT intour addresses.       14     DFE_OUT     OUT     Complementary bit of differential feedback cuput, provides feedback signal to the PLL for synchronization with the in the into in conjunction with the SMB_AD to d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2              | IREF            | OUT    | This pin establishes the reference for the differential current-mode output pairs. It requires a fixed precision resistor to ground. 475ohm is the standard value for 100ohm differential impedance. Other impedances |

| 3     100, TSSMP     11     See Functionally Table for Definition       4     HBW_BYPM_LOBW#     IT     See Functionally Table for Details.       5     CKPWRGD_PW     IN     Trilvevil nput to seeled High BW, Bypass or Low BW mode.       6     GND     PVM     Save power to stable accel house and statu up on first high assertion, or exit Power Down Mode.       6     GND     PVM     Save power to stable accel house and statu up on first high assertion, or exit Power Down Mode.       7     VDDR     PVM     Save power to stable accel house and statu up on first high assertion, or exit Power Down Mode.       8     DIF IM     IN     0.7.V Differential Complementary Input       9     DIF IM     IN     0.7.V Differential Complementary Input       10     SMBLs Address accels     This is a finite with and statu in conjunction with the SMB_AI to decode 1 of 9       11     SMBLs Address acceles     This is a finite with accel to align at a statu and SMBLs address accel input the works in conjunction with the SMB_AI to decode 1 of 9       13     SMBLs Address acceles     This is a finite with acceles to align.       14     OFB_OUT     OUT     OUT     This is a finite with acceles to align.       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |                 |        | require different values. See data sheet.                                                                                                                                                                             |

| 4     HIBM_BYPH_LOBUM     IN     Thiskel input to select High BW, Stypess or Low BW mode.       5     CKPWRGD_PDB     IN     Notifies device to sample latched inputs and start up on first high assertion, or exit Power Down Made on subsequent assertions. Low end set server Down Mode.       6     GND     PWR     Graund pm.     3.07 power on the minital input clock (receiver). This VDD should be treated as an analog power rail and 3.07 power on the minital input clock (receiver). This VDD should be treated as an analog power rail and 3.07 power on the minital complementary input.       8     DIF. IN     IN     0.72 VDIfferential Complementary input.       10     SMB_Ad_Lin     IN     0.72 VDIfferential Complementary input.       11     SMBDAT     IO     Data pin of SMBUS contury. SV bierant       12     SMBLAL     IN     Clock pin of SMBUS contury. SV bierant       13     SMBLA     IN     SMBUS Addresses on differential feedback cuput, provides feedback signal to the PLL for synchronization with the in final dock to gliminate phase error.       13     SMBLA     OU     OV     The final ddfffferential feedback cuput, provides feedback signal to the PLL for synchronization to clock to gliminate phase error.       14     DFE_10     OU     OV differential Complementary dock output       15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3              | 100M_133M#      | IN     |                                                                                                                                                                                                                       |

| 4     No. By Public LOwer     NN     See PLL Operating Mode <sup>7</sup> table for Details.       5     CKPWRGD_PDF     NN     Notifies device to sample lathed inputs and start up on first high assertion, or exit Power Down Mode on subsequent assertions. Low enters Power Down Mode.       7     VDDR     PWR     3.7 brown for differential input dock (receiver). This VDD should be treated as an analog power rail and faitered appropriately.       8     DIF_IN     NN     0.7 V Differential TRUE input.       9     DIF_IN     NN     0.7 V Differential TRUE input.       10     SMB_A_0_rti     NN     SMBUS and dressee.       11     SMBCLK     NN     Condumtry Studies and therein input thore when so conjunction with the SMB_AI to decode 1 of 9       SMB_A1_rti     NN     SMBUS and dressee.     Componentary half of differential feedback output, provides feedback signal to the PLL for synchronization with the Intig dock to efficiential beback output, provides feedback signal to the PLL for synchronization with the Intig dock to efficiential beback output.       10     DFE_0     OUT     OUT differential feedback output, provides feedback signal to the PLL for synchronization with the Intig dock output.       10     DFE_1     OUT     OV differential bree dock output.       10     DFE_1     OUT <td< td=""><td></td><td>_</td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                | _               |        |                                                                                                                                                                                                                       |

| 5     CAPWR0L_PUP     IN     subsequent asertions. Low enters Power Down Mode.       6     RND     PVM     3/X power for differential input dock (receiver). This VDD should be treated as an analog power rail and filtered appropriately.       8     DIF IN     IN     0.7.V Differential TRUE input       9     DIF IN     IN     0.7.V Differential Complementary Input       10     SMB_AD_th     IN     SMBUs Addresses.       11     SMBDAT     IO     Data info SMBUS Addresses.       12     SMBLAL     IN     Clock pt of SMBUS Addresses.       13     SMBLA     IN     Clock pt of SMBUS Addresses.       14     DFB_OUT#     OUT     SMBUS Addresses.       15     DFB_OUT#     OUT     SMBUS Addresses.       16     DFB_OUT#     OUT     Complementary facto differential feedback cuput, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.       17     DFB_OUT     OUT     C/V differential Complementary dock output       18     DFT_1     OUT     C/V differential Complementary dock output       19     DFT_1     OUT     C/V differential Complementa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4              | HIBW_BYPM_LOBW# | IN     | See PLL Operating Mode Table for Details.                                                                                                                                                                             |

| 6     NDD     PWR     Ground pin.       7     VDDR     PWR     3/X power for differential input dock (receiver). The VDD should be treated as an analog power rail and fittered appropriately.       9     DFI IN     IN     0.7 V Differential Complementary Input.       9     DFI INF     IN     0.7 V Differential Complementary Input.       11     SMB.addresses.     IN     SMB.addresses.       12     SMB.dx Addresses.     IN     SMB.addresses.       13     SMB.A.t.ri     IN     SMB.addresses.       14     DFB_OUT#     OUT     SMB.addresses.       15     DFB_OUT#     OUT     True hail of differential feedback output, provides feedback signal to the PLL for synchronization with height addresses.       16     DFB_OUT     OUT     True hail of differential feedback output, provides feedback signal to the PLL for synchronization with neight addresses.       17     DFB_0     OUT     True hail of differential feedback output.       18     DF1_1     OUT     True hail of differential reserver.       19     DF1_2     OUT     True field of differential reserver.       20     DF2_2     OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5              | CKPWRGD_PD#     | IN     |                                                                                                                                                                                                                       |

| 7     VDDR     PWR<br>Hared appropriately.     3.39 power for differential imput dock (receiver). This VDD should be treated as an analog power rail and<br>Hared appropriately.       8     DIF IN     IN     0.7 U Differential Complementary Input       10     SMB_AO_Iri     IN     0.7 U Differential Complementary Input       10     SMB_AO_Iri     IN     SMBUS documentary Input that works in conjunction with the SMB_A1 to decode 1 of 9       11     SMBDAT     IO     Data pin of SMBUS documentary, EV tolerant       12     SMBCLACH     IN     Cock pin of SMBUS documentary, EV tolerant       13     SMBD_A1_tri     IN     SMBUS Addresses.     Contrained the second tolerant and tolerant a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6              | GND             | PWR    |                                                                                                                                                                                                                       |

| B     DIF. IN     IN     D.7.V Differential Complementary Input       9     DIF. IN     IN     0.7.V Differential Complementary Input       10     SMB_AO_tri     IN     SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A1 to decode 1 of 9       11     SMBDAT     IO     Data pin of SMBUS occurry, SV tolerant       12     SMBLAT_tri     IN     Clock pin of SMBUS occurry, SV tolerant       13     SMBLAT_tri     IN     SMBUS Address bit. This is a tri-level input that works in conjunction with the SMB_AD decode 1 of 9       14     OFB_OUT#     OUT     True half of differential free dack adjuct, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.       16     DIF_0     OUT     OV     True that of differential free dock output     Provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.       16     DIF_1     OUT     OV differential True dock output     Provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.       17     DIF_6     OUT     0.7V differential True dock output     Provides feedback signal to the PLL for synchronization with the in clock output       10     DIF_6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                 |        | 3.3V power for differential input clock (receiver). This VDD should be treated as an analog power rail and                                                                                                            |

| 9     DIF NM     IN     0.7.0 Differential Complementary Input       10     SMB_ Ad_Lin     IN     SMB us Addresses.       11     SMBDCIX     IN     SMBUS dicates bit. This is a threwin input that works in conjunction with the SMB_A1 to decode 1 of 9       12     SMBCIX     IN     Clock pin of SMBUS circuitry, SV tolerant       13     SMB_A1_tri     IN     SMBUS dicates bit. This is a triveel input that works in conjunction with the SMB_A0 to decode 1 of 9       14     DFB_OUT#     OUT     True half of differential leedback output, provides feedback signal to the PLL for synchronization with the in       15     DFB_OUT#     OUT     Complementary lead ock output       17     DFF 0     OUT     Covid differential leedback output       18     DFF 0     OUT     Covid differential leedback output       19     DFF 0     OUT     Covid differential leedback output       19     DFF 0     OUT     Covid differential leedback output       20     NDD     PVMF     Prover supply, nominal 3.3V       21     NDD     PVMF     Prover supply, nominal 3.3V       22     NDF 2     OUT     7.V di                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0              |                 | INI    |                                                                                                                                                                                                                       |

| NBE_A0_th   IN   SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A1 to decode 1 of 9     11   SMBDAT   I/O   Data pin of SMBUS circuity, SV lolerant     12   SMBLA   I/N   Clock pin of SMBUS circuity, SV lolerant     13   SMB_A1_th   I/N   SMBUS address bit. This is a tri-level input that works in conjunction with the SMB_A0 to decode 1 of 9     14   DFB_OUT#   Out   Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.     15   DFB_OUT   Out   Ture half of differential free dock output   provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.     16   DFF_0   Out   0.7V differential Complementary dock output   1000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -              |                 |        |                                                                                                                                                                                                                       |

| INSERTION     IN     SMBus Addresses.       10     SMBCLK     IN     Obox prior of SMBUS circuity. SV loterant       12     SMBCLK     IN     Clock prior of SMBUS circuity. SV loterant       13     SMBL AL_tri     IN     Clock prior of SMBUS circuity. SV loterant       14     DFB_OUT#     SMBLs Addresses.     Complementary haif of differential feedback output, provides feedback signal to the PLL for synchronization       15     DFB_OUT     OUT     True haif of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.       16     DIF_0     OUT     0.7V differential true clock output       17     DIF 1     OUT     0.7V differential true clock output       18     DIF_1     OUT     0.7V differential true clock output       19     DIF 2     OUT     0.7V differential Complementary dock output       20     VDD     PWR     Power supply, nominal 3.3V       21     VDD     PWR     Power supply, nominal 3.3V       22     VDD     PVR     Power supply, nominal 3.3V       23     DIF 2     OUT     0.7V differential Complementar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                 | 1      |                                                                                                                                                                                                                       |

| 12 SMBCLK IN Clock pin of SMBUS circuitry, 5V tolerant:   13 SMB_A1_tri IN Clock pin of SMBUS dire sees.   14 DFB_OUT# SMBus darlerses.   15 DFB_OUT Curry Curry   16 DFB_OUT Curry True half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.   16 DFF_0 Curr True half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eliminate phase error.   17 DIF_1 Curr 0.7V differential true dock output   18 DIF_1 Curr 0.7V differential true dock output   19 DIF_1 Curr 0.7V differential true dock output   10 DVD PWR Power supply, nominal 3.3V   20 VDD PWR Power supply, nominal 3.3V   21 VDD PVR Power supply, nominal 3.3V   22 VDD PVR Power supply, nominal 3.3V   23 DIF_2 OUT 0.7V differential Complementary dock output   24 DIF_3 OUT 0.7V differential Complementary dock output   25 VDD PVR Power supply, nominal 3.3V   26 DIF_4 OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                 |        | SMBus Addresses.                                                                                                                                                                                                      |

| 13     SMB_A1_tri     IN     SMBus darderss bit.     This is a tri-level input that works in conjunction with the SMB_A0 to decode 1 of 9<br>SMBus darderss bit.       14     OFB_OUT#     OUT     SMBus darderss bit.     The second darderss bit.       15     OFB_OUT#     OUT     Orgenentary half of differential feedback output, provides feedback signal to the PLL for synchronization<br>with input dock to aliminate phase error.       16     DIF_0     OUT     0.7V differential Conglementary dock output       17     DIF_0     OUT     0.7V differential Conglementary dock output       18     DIF_1     OUT     0.7V differential Conglementary dock output       20     ISF.2     OUT     0.7V differential Conglementary dock output       21     VDD     PVM     Power supply, nominal 3.W       22     VDD     PVM     Power supply, nominal 3.W       23     DIF_2     OUT     0.7V differential true dock output       24     DIF_3     OUT     0.7V differential true dock output       25     VDD     PVM     Power supply, nominal 3.W       26     DIF_3     OUT     0.7V differential true dock output       27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                 |        |                                                                                                                                                                                                                       |

| Simple Art_In     IN     SMBLe Addresses.       10     DFB_OUT#     OUT     Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to afiminate phase error.       15     DFB_OUT     OUT     True half of differential teedback output.       17     DIF_O     OUT     0.7V differential to edo ko uput.       18     DIF_1     OUT     0.7V differential true clock output.       19     DIF_1     OUT     0.7V differential true clock output.       19     DIF_1     OUT     0.7V differential true clock output.       19     DIF_1     OUT     0.7V differential true clock output.       20     OD     PWR     Power supphy, nominal 3.3V       20     VDD     PWR     Power supphy, nominal 3.3V       21     VDD     PVRP     Power supphy, nominal 3.3V       22     VDD     PVRP     Power supphy, nominal 3.3V       24     DIF_2#     OUT     0.7V differential true clock output       25     VDE#     IN     Active low input for enabling DIF pair 2.       26     IDF     OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12             | SMBCLK          | IN     |                                                                                                                                                                                                                       |

| 1     DFB_OUT#     OUT     Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eleminate phase error.       15     DFB_OUT     OUT     True half of differential feedback output, provides feedback signal to the PLL for synchronization with the in clock to eleminate phase error.       16     DIF_0     OUT     0.7V differential True clock output.       17     DIF_0     OUT     0.7V differential True clock output.       18     DIF_1     OUT     0.7V differential Complementary clock output.       20     SND     PVM     Ground pin.       21     VDD     PVM fore supply, nominal 3.3V       22     VDD     PVM Foreer supply, nominal 3.3V       23     DIF_2     OUT     0.7V differential Complementary clock output       24     DIF_2     OUT     0.7V differential Complementary clock output       25     vOEz#     IN     Active low input for enable outputs       26     DIF_3     OUT     0.7V differential Complementary clock output       27     VDD     PVM Forcen dpf n.       30     DIF_4     OUT     0.7V differentinta clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13             | SMB_A1_tri      | IN     |                                                                                                                                                                                                                       |

| - $                                                                                                                                                                       -$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14             |                 |        | Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization                                                                                                           |

| 18UPS_UUTUUTclock to eliminate phase error.17DIF 0OUT0.77 differential Complementary clock output18DIF 1OUT0.77 differential Complementary clock output19DIF 10UT0.77 differential Complementary clock output20GNDPWRFournamentary clock output21VDDPWRPower suppy, nominal 3.3V22VDDPWRPower suppy, nominal 3.3V23DIF 2OUT0.77 differential trock clock output24DIF 2OUT0.77 differential cock output25VDE 2*NActive low input for enabling DIF pare 2.26VDE 7*OUT0.77 differential trock clock output27DIF 3*OUT0.77 differential trock clock output28VDE 2*NActive low input for enabling DIF pare 2.29ND 7*7*Mifferential trock clock output29DIF 3*OUT0.77 differential trock clock output20DIF 4OUT0.77 differential trock clock output21DIF 4OUT0.77 differential Complementary clock output22VDDPWRRower suppy, nominal 3.3V23VDE 4*IN1disable outputs, 0 = enable outputs34VDE4#IN1disable outputs, 0 = enable outputs35VDDPWRRower suppy, nominal 3.3V36NDDPWRRower suppy, nominal 3.3V37DIF 6OUT0.77 differential Complementary clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 14             | DFB_001#        | 001    |                                                                                                                                                                                                                       |

| Image: Constraint of the set of the se | 15             | DFB OUT         | OUT    |                                                                                                                                                                                                                       |

| 17   DIF 0   0.7V differential Complementary clock output     18   DIF 1   0.0T   0.7V differential Complementary clock output     19   DIF 1#   0.0T   0.7V differential Complementary clock output     21   VDD   PWR   Ground pin.     22   VDD   PWR   Prower supply, nominal 3.3V     24   DIF 2   OUT   0.7V differential Complementary clock output     25   VDE 2#   OUT   0.7V differential Complementary clock output     26   DIF 2#   OUT   0.7V differential Complementary clock output     27   DIF 3#   OUT   0.7V differential Complementary clock output     28   VDE2#   IN   Active fock output     29   DIF 3#   OUT   0.7V differential Complementary clock output     20   DIF 4   OUT   0.7V differential Complementary clock output     30   DIF 5   OUT   0.7V differential Complementary clock output     31   DIF 6   OUT   0.7V differential Complementary clock output     32   VDE4#   IN   1-disable outputs 0.0   enal 4     34   DIF 5   OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |                 |        |                                                                                                                                                                                                                       |

| 18   DiF.1   OUT   0.7V differential true dock output     20   GND   PWR   Gound pin.     21   VDD   PWR   Power supply, nominal 3.3V     22   VDD   PWR   Power supply, nominal 3.3V     23   DIF.2   OUT   0.7V differential rue dock output     24   DIF.2   OUT   0.7V differential rue dock output     25   VDD   PWR   Power supply, nominal 3.3V     26   DIF.2   OUT   0.7V differential rue dock output     27   VD2   PWR   Power supply, nominal 3.3V     28   VD2   PWR   Power supply, nominal 3.3V     29   GND   PWR   Ground pin.     30   DIF.3   OUT   0.7V differential rue dock output     31   DIF.4#   OUT   0.7V differential rue dock output     32   vCE4#   IN   Active low input for reabing DF pair 4     1   1   1   disable outputs, 0   = enable outputs     30   DIF.5   OUT   0.7V differential rue dock output   0     34   DIF.5#   OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |                 |        |                                                                                                                                                                                                                       |

| 19   DIF_1#   OUT   0.7V differential Complementary clock output     20   GND   PWR   Ground pin.     21   VDD   PWR   Power supply, nominal 3.3V     22   VDD   PWR   Power supply, nominal 3.3V     23   DIF_2   OUT   0.7V differential to clock output     24   DIF_2#   OUT   0.7V differential to clock output     25   VC2#   N   Active low input for enabling DIF pair 2.     26   DIF_3#   OUT   0.7V differential to clock output     27   DIF_3#   OUT   0.7V differential clock output     28   VDD   PWR   Foreund pin.     29   GND   PWR   Foreund pin.     20   DIF_4   OUT   0.7V differential Complementary clock output     29   GND   PWR   Ground pin.     30   DIF_4   OUT   0.7V differential true clock output     31   DIF_5   OUT   0.7V differential true clock output     32   VDD   PWR   Power supply, nominal 3.3V     33   DIF_6   OUT   0.7V differential true clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                 |        |                                                                                                                                                                                                                       |

| 20GNDPWRProver supply, nominal 3.3V21VDDPWRPower supply, nominal 3.3V23DIF_2OUT0.7V differential rue dock output24DIF_2#OUT0.7V differential rue dock output25VOE2#NActive low input for enabling DIF pair 2.<br>1 = disable outputs. 0. = enable outputs.26DIF_3#OUT0.7V differential complementary dock output27DIF.3OUT0.7V differential complementary dock output28DIF_4OUT0.7V differential complementary dock output29GNDPWRPower supply, nominal 3.3V29GNDPWRRover supply, nominal 3.3V29GNDPWRRover supply, nominal 3.3V29GNDPWRRound pin.30DIF_4OUT0.7V differential Complementary dock output31DIF_5OUT0.7V differential Complementary dock output32vOE4#INA ctive low input for enabling DIF pair 433DIF_5OUT0.7V differential Complementary dock output34DIF_6#OUT0.7V differential true dock output35VDDPWRRound pin.36GNDPWRRound pin.37DIF_6#OUT0.7V differential true dock output38DIF_6#OUT0.7V differential true dock output39DIF_6#OUT0.7V differential true dock output39DIF_6#OUT0.7V differential true dock output<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                 |        |                                                                                                                                                                                                                       |

| 21     VDD     PWR     Power supply, nominal 3.3V       22     VDD     PWR     Power supply, nominal 3.3V       23     DIF_2     OUT     0.7V differential true clock output       24     DIF_2#     OUT     0.7V differential true clock output       25     VDE2#     IN     Active low input for enabling DIF pair 2.       1=disable outputs, 0 = enable outputs     1     1=disable outputs, 0 = enable output       27     DIF_3#     OUT     0.7V differential rue clock output       28     VDD     PWR     Power supply, nominal 3.3V       29     GND     PWR     Ground spin.       30     DIF_4     OUT     0.7V differential true clock output       31     DIF_5     OUT     0.7V differential true clock output       32     VDE4#     IN     Active low input for enabling DIF pair 4       1=disable outputs, 0 = enable outputs     0     0       33     DIF_5     OUT     0.7V differential true clock output       34     DIF_6     OUT     0.7V differential true clock output       35     DDF     PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |                 |        |                                                                                                                                                                                                                       |

| 22     VDD     PVWR     Power supply, nominal 3.3V       24     DIF_2     OUT     0.7V differential complementary clock output       24     DIF_2#     OUT     0.7V differential rue clock output       25     VOE2#     IN     Active low input for enabling DIF pair 2.       26     DIF_3     OUT     0.7V differential rue clock output       26     DIF_3     OUT     0.7V differential rue clock output       27     DIF_3#     OUT     0.7V differential rue clock output       28     VDD     PVWR     Ground pin.       29     GND     PVWR     Ground pin.       20     VCE4#     OUT     0.7V differential complementary clock output       30     DIF_4     OUT     0.7V differential rue clock output       31     DIF_5     OUT     0.7V differential rue clock output       32     VOE4#     IN     Active low input for enabling DIF pair 4       1_disable outputs, 0 = enable outputs     1_disable outputs     0       33     DIF_5     OUT     0.7V differential rue clock output       34     DIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |                 |        |                                                                                                                                                                                                                       |

| 23   DIF 2   OUT   0.77 differential Complementary clock output     24   DIF 2#   OUT   0.77 differential Complementary clock output     25   VCE2#   IN   Active Iow input for enabling DIF pair 2.     1=disable outputs.   0= enable outputs     27   DIF.3#   OUT   0.77 differential true clock output     28   VDD   PWR   Power supply, nominal 3.3V     28   GND   PWR   Power supply, nominal 3.3V     29   GND   PWR   Forund plin.     30   DIF_4   OUT   0.77 differential true clock output     30   DIF_5#   OUT   0.77 differential Complementary clock output     31   DIF_5#   OUT   0.77 differential true clock output     32   VOE4#   In   1=disable outputs.0   e outputs     33   DIF_5   OUT   0.77 differential true clock output   e outputs     34   DIF_5#   OUT   0.77 differential true clock output   e outputs     38   DIF 6#   OUT   0.77 differential true clock output   e outputs     39   VCE6#   IN   Activ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                 |        |                                                                                                                                                                                                                       |

| 24   DJF $2^{\#}$ QUT   0.7V differential Complementary dock output     25   vGE#   IN   Active low input for enabling DJF pair 2.     26   DJF.3   QUT   0.7V differential true clock output     27   DJF.3#   QUT   0.7V differential Complementary clock output     28   VDD   PWR   Power supply, nominal 3.3V     29   GND   PWR   Ground pin.     30   DJF_4   QUT   0.7V differential Complementary clock output     31   DJF_4   QUT   0.7V differential Complementary clock output     32   vQE4#   IN   Active low input for enabling DJF pair 4     1   -tdisable outputs, 0 = enable outputs   -     33   DJF_5   OUT   0.7V differential Complementary clock output     34   DJF_5#   OUT   0.7V differential Complementary clock output     35   VDD   PWR   Power supply, nominal 3.3V     36   GND   PWR   Power supply, nominal 3.3V     37   DJF_6   OUT   0.7V differential true clock output     38   DJF 6#   OUT   0.7V differential true clock output </td <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                 |        |                                                                                                                                                                                                                       |

| 25<br>v $VGE2#$ Active low input for enabling DIF pair 2.<br>1 =disable outputs.26DIF_3OUT 0.7V differential True dock output27DIF_3#OUT 0.7V differential Complementary dock output28VDDPVRR29GNDPVRR29GNDPVRR30DIF_4OUT 0.7V differential Complementary dock output31DIF_4#OUT 0.7V differential true dock output32VOE4#N33DIF_5OUT 0.7V differential Complementary dock output34DIF_5#OUT 0.7V differential Complementary dock output35VDDPVRR36GNDPVRR37DIF_5#OUT 0.7V differential rue dock output38VDDPVRR39VOE6#IN31Active low input for enabling DIF pair 4.<br>1 = disable outputs, 0 = enable outputs39VOE6#IN39VOE6#IN40DIF_7#OUT 0.7V differential rue dock output30DIF_7#OUT 0.7V differential Complementary dock output39VOE6#IN40DIF 7#OUT 0.7V differential rue dock output41DIF 7#OUT 0.7V differential rue dock output42GNDPVRR44DIF 8OUT 0.7V differential rue dock output45VDDPVRR46VOE8#IN47DIF 9OUT 0.7V differential rue dock output48DIF 8#OUT 0.7V differential rue dock output<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |                 |        |                                                                                                                                                                                                                       |

| 2VDE2#IN1 =disable outputs.0 = enable outputs26DIF_3OUT0.7V differential true clock output27DIF_3#OUT0.7V differential Complementary clock output28VDDPWRPower supply, nominal 3.3V29GNDPWRPower supply, nominal 3.3V29GNDPWRForund pin.30DIF_4OUT0.7V differential Complementary clock output31DIF_4#OUT0.7V differential Complementary clock output32VOE4#NActive low input for enabling DIF pair 433DIF_5OUT0.7V differential Complementary clock output34DIF_5#OUT0.7V differential Complementary clock output35VDDPWRPower supply, nominal 3.3V36GNDPWRPower supply, nominal 3.3V37DIF_6#OUT0.7V differential Complementary clock output38DIF_6#OUT0.7V differential Complementary clock output39VOE6#NActive low input for enabling DIF pair 6.411-disable outputs, 0 = enable outputs142GNDPVRGround pin.43VDDPVRGround pin.44DIF_7#OUT0.7V differential Complementary clock output44DIF_8#OUT0.7V differential Complementary clock output44DIF_9OUT0.7V differential Complementary clock output45DIF_8#OUT0.7V differential Complementary cl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |                 |        |                                                                                                                                                                                                                       |

| 26     DiF_3     OUT     0.7V differential rue dock output       27     DIF_3#     OUT     0.7V differential Complementary dock output       28     VDD     PWR     Rower supply, nominal 3.3V       29     GND     PWR     Ground pin.       30     DIF_4     OUT     0.7V differential rue dock output       31     DIF_4     OUT     0.7V differential rue dock output       32     VOE4#     N     Active Iow input for enabling DIF pair 4       33     DIF_5     OUT     0.7V differential rue dock output       34     DIF_5     OUT     0.7V differential rue dock output       35     VDD     PWR     Power supply, nominal 3.3V       36     GND     PWR     Ground pin.       37     DIF_6     OUT     0.7V differential Complementary dock output       38     DIF_6     OUT     0.7V differential Complementary dock output       40     DIF_7     OUT     0.7V differential rue dock output       41     DIF 7#     OUT     0.7V differential Complementary dock output       42     GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25             | vOE2#           | IN     |                                                                                                                                                                                                                       |

| 27DiF, $3#$ OUT0.7V differential Complementary clock output28VDDPWRPower supply, nominal 3.3V29GNDPWRGround pin.30DiF_4OUT0.7V differential true clock output31DiF_4#OUT0.7V differential Complementary clock output32vOE##INActive low input for enabling DIF pair 4<br>1 = disable outputs, 0 = enable outputs33DiF_5OUT0.7V differential true clock output34DiF_5#OUT0.7V differential true clock output35VDDPWRPower supply, nominal 3.3V36GNDPWRGround pin.37DiF_6OUT0.7V differential Complementary clock output38DIF_6#OUT0.7V differential Complementary clock output39vOE6#INActive low input for enabling DIF pair 6.<br>1 = disable outputs, 0 = enable outputs40DIF_7OUT0.7V differential Complementary clock output41DIF 7#OUT0.7V differential Complementary clock output42GNDPWRPower supply, nominal 3.3V43VDDPWRPower supply, nominal 3.3V44DIF 8#OUT0.7V differential true clock output45VIE0.7V differential true clock output46VDDPWRPower supply, nominal 3.3V47DIF 8#OUT0.7V differential true clock output48DIF 8#OUT0.7V differential Complementary clock output <td< td=""><td>26</td><td>DIF 3</td><td>OUT</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26             | DIF 3           | OUT    |                                                                                                                                                                                                                       |