# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

### **General Description**

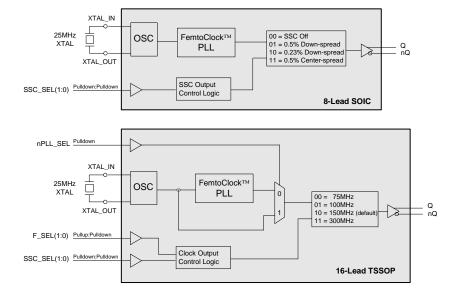

The 844441 is a low jitter, high performance clock generator and a member of the FemtoClock<sup>®</sup> family of silicon timing products. The 844441 is designed for use in applications using the SAS and SATA interconnect. The 844441 uses an external, 25MHz, parallel resonant crystal to generate four selectable output frequencies: 75MHz, 100MHz, 150MHz, and 300MHz. This silicon based approach provides excellent frequency stability and reliability. The 844441 features down and center spread spectrum (SSC) clocking techniques.

# **Applications**

- SAS/SATA Host Bus Adapters

- SATA Port Multipliers

- SAS I/O Controllers

- TapeDrive and HDD Array Controllers

- SAS Edge and Fanout Expanders

- HDDs and TapeDrives

- Disk Storage Enterprise

#### **Features**

- Designed for use in SAS, SAS-2, and SATA systems

- Center (±0.17%) Spread Spectrum Clocking (SSC)

- Down (-0.23% or -0.5%) SSC

- Better frequency stability than SAW oscillators

- One differential 2.5V LVDS output

- Crystal oscillator interface designed for 25MHz (C<sub>L</sub> = 12pF) frequency

- External fundamental crystal frequency ensures high reliability and low aging

- Selectable output frequencies: 75MHz, 100MHz, 150MHz, 300MHz

- Output frequency is tunable with external capacitors

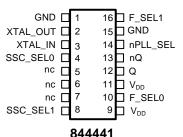

- RMS phase jitter @ 100MHz, using a 25MHz crystal (12kHz – 20MHz): 1.1936ps (typical)

- 2.5V operating supply

- -40°C to 85°C ambient operating temperature

- Lead-free (RoHS 6) packaging

# **Block Diagrams**

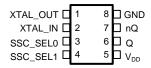

## **Pin Assignment**

844441 8-Lead SOIC, 3.90mm x 4.90mm Package

16-Lead TSSOP, 4.4mm x 5.0mm Package

# **Pin Description and Pin Characteristic Tables**

**Table 1. Pin Descriptions**

| Name                  | Туре   |          | Description                                                                 |

|-----------------------|--------|----------|-----------------------------------------------------------------------------|

| XTAL_OUT,<br>XTAL_IN  | Input  |          | Crystal oscillator interface. XTAL_IN is the input, XTAL_OUT is the output. |

| SSC_SEL0,<br>SSC_SEL1 | Input  | Pulldown | SSC select pins. See Table 3A. LVCMOS/LVTTL interface levels.               |

| F_SEL0                | Input  | Pulldown | Output frequency select pin. See Table 3B. LVCMOS/LVTTL interface levels.   |

| F_SEL1                | Input  | Pullup   | Output frequency select pin. See Table 3B. LVCMOS/LVTTL interface levels.   |

| nPLL_SEL              | Input  | Pulldown | PLL Bypass pin. LVCMOS/LVTTL interface levels.                              |

| Q, nQ                 | Output |          | Differential clock outputs. LVDS interface levels.                          |

| GND                   | Power  |          | Power supply ground.                                                        |

| V <sub>DD</sub>       | Power  |          | Power supply pin.                                                           |

| nc                    | Unused |          | No connect.                                                                 |

NOTE: Pullup/Pulldown refers to internal input resistors. See Table 2, Pin Characteristics, for typical values.

**Table 2. Pin Characteristics**

| Symbol                | Parameter               | Test Conditions                    | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|------------------------------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       | nPLL_SEL, F_SEL[1:0], SSC_SEL[1:0] |         | 4       |         | pF    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                                    |         | 51      |         | kΩ    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor   |                                    |         | 51      |         | kΩ    |

## **Function Tables**

Table 3A. SSC\_SEL[1:0] Function Table

| Inputs      |             |                     |

|-------------|-------------|---------------------|

| SSC_SEL1    | SSC_SEL0    | Mode                |

| 0 (default) | 0 (default) | SSC Off             |

| 0           | 1           | 0.5% Down-spread    |

| 1           | 0           | 0.23% Down-spread   |

| 1           | 1           | 0.34% Center-spread |

Table 3B. F\_SEL[1:0] Function Table

| Inp         | uts         |                        |

|-------------|-------------|------------------------|

| F_SEL1      | F_SEL0      | Output Frequency (MHz) |

| 0           | 0           | 75                     |

| 0           | 1           | 100                    |

| 1 (default) | 0 (default) | 150                    |

| 1           | 1           | 300                    |

# **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics or AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                                                       | Rating                                |

|----------------------------------------------------------------------------|---------------------------------------|

| Supply Voltage, V <sub>DD</sub>                                            | 4.6V                                  |

| Inputs, V <sub>I</sub>                                                     | -0.5V to V <sub>DD</sub> + 0.5V       |

| Outputs, I <sub>O</sub> Continuous Current Surge Current                   | 10mA<br>15mA                          |

| Package Thermal Impedance, θ <sub>JA</sub><br>16 Lead TSSOP<br>8 Lead SOIC | 81.2°C/W (0 mps)<br>96.0°C/W (0 lfpm) |

| Storage Temperature, T <sub>STG</sub>                                      | -65°C to 150°C                        |

### **DC Electrical Characteristics**

Table 4A. Power Supply DC Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol          | Parameter            | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------|-----------------|---------|---------|---------|-------|

| $V_{DD}$        | Power Supply Voltage |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub> | Power Supply Current |                 |         |         | 73      | mA    |

Table 4B. LVCMOS/LVTTL DC Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40$ °C to 85°C

| Symbol                                   | Paramete                          | er                                | Test Conditions                              | Minimum | Typical | Maximum               | Units |

|------------------------------------------|-----------------------------------|-----------------------------------|----------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub>                          | Input High                        | n Voltage                         |                                              | 1.7     |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>                          | Input Low                         | Voltage                           |                                              | -0.3    |         | 0.7                   | V     |

| Input<br>I <sub>IH</sub> High<br>Current | F_SEL1                            | $V_{DD} = V_{IN} = 2.5V$          |                                              |         | 5       | μA                    |       |

|                                          | SSC_SEL[0:1],<br>F_SEL0, nPLL_SEL | $V_{DD} = V_{IN} = 2.5V$          |                                              |         | 150     | μA                    |       |

|                                          | Input                             | F_SEL1                            | $V_{DD} = 2.5V, V_{IN} = 0V$                 | -150    |         |                       | μA    |

| I <sub>IL</sub> Low Current              | Low<br>Current                    | SSC_SEL[0:1],<br>F_SEL0, nPLL_SEL | V <sub>DD</sub> = 2.5V, V <sub>IN</sub> = 0V | -5      |         |                       | μA    |

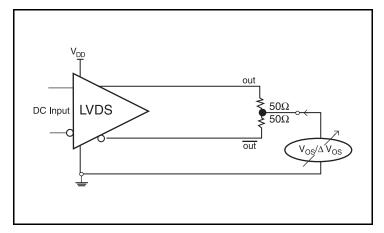

Table 4C. LVDS DC Characteristics,  $V_{DD} = 2.5V \pm 5\%$ ,  $T_A = -40$ °C to 85°C

| Symbol           | Parameter                        | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------|-----------------|---------|---------|---------|-------|

| V <sub>OD</sub>  | Differential Output Voltage      |                 | 200     |         | 454     | mV    |

| $\Delta V_{OD}$  | V <sub>OD</sub> Magnitude Change |                 |         |         | 50      | mV    |

| Vos              | Offset Voltage                   |                 | 1       |         | 1.375   | V     |

| ΔV <sub>OS</sub> | V <sub>OS</sub> Magnitude Change |                 |         |         | 50      | mV    |

#### **Table 4D. Crystal Characteristics**

| Parameter                          | Test Conditions | Minimum | Typical     | Maximum | Units |

|------------------------------------|-----------------|---------|-------------|---------|-------|

| Mode of Oscillation                |                 |         | Fundamental |         |       |

| Frequency                          |                 |         | 25          |         | MHz   |

| Equivalent Series Resistance (ESR) |                 |         |             | 50      | Ohm   |

| Shunt Capacitance                  |                 |         |             | 7       | pF    |

| Load Capacitance (C <sub>L</sub> ) |                 |         | 12          |         | pF    |

# **AC Electrical Characteristics**

Table 5. AC Characteristics,  $V_{DD}$  = 2.5V ± 5%,  $T_A$  = -40°C to 85°C

| Symbol           | Parameter             | Test Conditions                             | Minimum | Typical | Maximum | Units |

|------------------|-----------------------|---------------------------------------------|---------|---------|---------|-------|

|                  |                       | F_SEL(1:0) = 00                             |         | 75      |         | MHz   |

|                  | Output Francisco      | F_SEL(1:0) = 01                             |         | 100     |         | MHz   |

| f <sub>OUT</sub> | Output Frequency      | F_SEL(1:0) = 10                             |         | 150     |         | MHz   |

|                  |                       | F_SEL(1:0) = 11                             |         | 300     |         | MHz   |

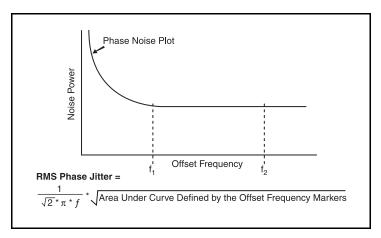

| tjit(Ø)          |                       | 75MHz, Integration Range:<br>12kHz – 20MHz  |         | 1.19602 |         | ps    |

|                  | RMS Phase Jitter      | 100MHz, Integration Range:<br>12kHz – 20MHz |         | 1.1936  |         | ps    |

|                  | (Random); NOTE 1      | 150MHz, Integration Range:<br>12kHz – 20MHz |         | 1.22743 |         | ps    |

|                  |                       | 300MHz, Integration Range:<br>12kHz – 20MHz |         | 1.15011 |         | ps    |

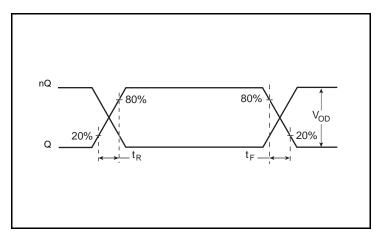

| $t_R / t_F$      | Output Rise/Fall Time | 20% to 80%                                  | 100     |         | 400     | ps    |

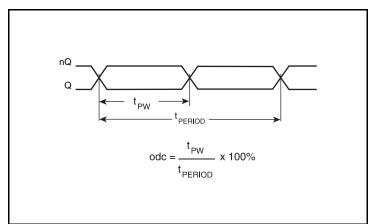

| odc              | Output Duty Cycle     |                                             | 45      |         | 55      | %     |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

NOTE: Characterized using a 25MHz, 12pF quartz crystal.

NOTE 1: Please refer to the Phase Noise plot.

# **Typical Phase Noise at 100MHz**

## **Parameter Measurement Information**

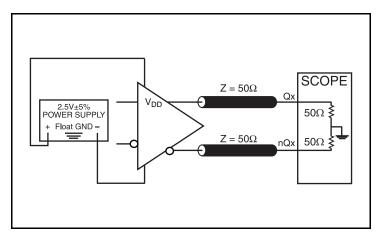

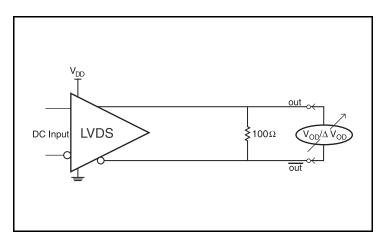

2.5V LVDS Output Load Test Circuit

**Output Rise/Fall Time**

**Offset Voltage Setup**

**RMS Phase Jitter**

**Output Duty Cycle/Pulse Width/Period**

**Differential Output Voltage Setup**

## **Application Information**

#### Overdriving the XTAL Interface

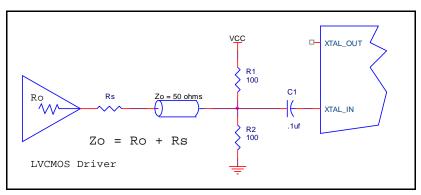

The XTAL\_IN input can be overdriven by an LVCMOS driver or by one side of a differential driver through an AC coupling capacitor. The XTAL\_OUT pin can be left floating. The amplitude of the input signal should be between 500mV and 1.8V and the slew rate should not be less than 0.2V/ns. For 3.3V LVCMOS inputs, the amplitude must be reduced from full swing to at least half the swing in order to prevent signal interference with the power rail and to reduce internal noise. Figure 1A shows an example of the interface diagram for a high speed 3.3V LVCMOS driver. This configuration requires that the sum of the output impedance of the driver (Ro) and the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This

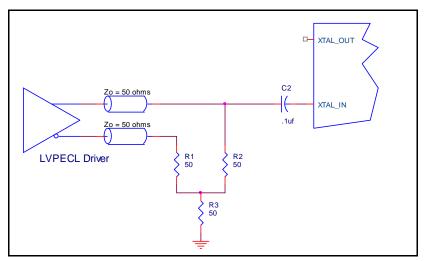

can be done in one of two ways. First, R1 and R2 in parallel should equal the transmission line impedance. For most  $50\Omega$  applications, R1 and R2 can be  $100\Omega$ . This can also be accomplished by removing R1 and changing R2 to  $50\Omega$ . The values of the resistors can be increased to reduce the loading for a slower and weaker LVCMOS driver. Figure 1B shows an example of the interface diagram for an LVPECL driver. This is a standard LVPECL termination with one side of the driver feeding the XTAL\_IN input. It is recommended that all components in the schematics be placed in the layout. Though some components might not be used, they can be utilized for debugging purposes. The datasheet specifications are characterized and guaranteed by using a quartz crystal as the input.

Figure 1A. General Diagram for LVCMOS Driver to XTAL Input Interface

Figure 1B. General Diagram for LVPECL Driver to XTAL Input Interface

#### **Recommendations for Unused Input Pins**

#### Inputs:

#### **LVCMOS Control Pins**

All control pins have internal pull-ups; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

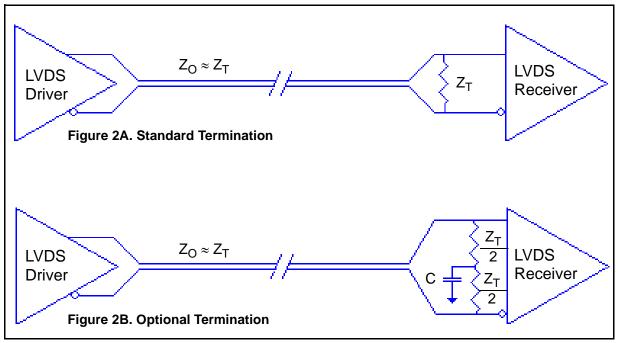

#### **LVDS Driver Termination**

For a general LVDS interface, the recommended value for the termination impedance  $(Z_T)$  is between  $90\Omega$  and  $132\Omega.$  The actual value should be selected to match the differential impedance  $(Z_0)$  of your transmission line. A typical point-to-point LVDS design uses a  $100\Omega$  parallel resistor at the receiver and a  $100\Omega$  differential transmission-line environment. In order to avoid any transmission-line reflection issues, the components should be surface mounted and must be placed as close to the receiver as possible. IDT offers a full line of LVDS compliant devices with two types of output structures: current source and voltage source. The

standard termination schematic as shown in *Figure 2A* can be used with either type of output structure. *Figure 2B*, which can also be used with both output types, is an optional termination with center tap capacitance to help filter common mode noise. The capacitor value should be approximately 50pF. If using a non-standard termination, it is recommended to contact IDT and confirm if the output structure is current source or voltage source type. In addition, since these outputs are LVDS compatible, the input receiver's amplitude and common-mode input range should be verified for compatibility with the output.

**LVDS Termination**

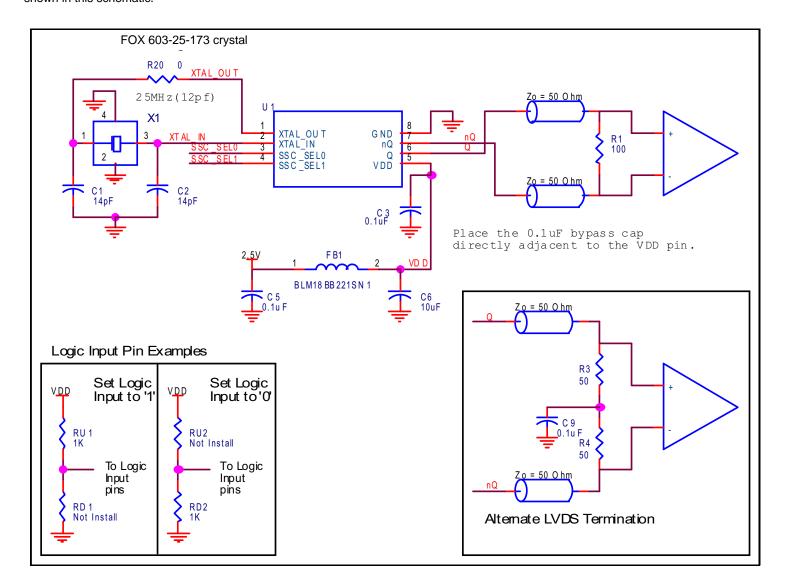

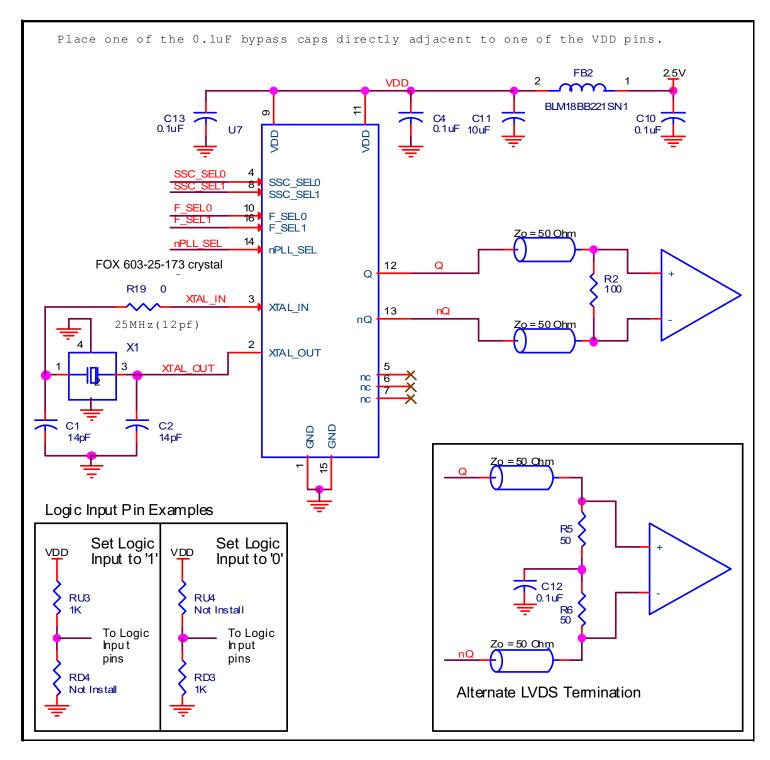

#### **Schematic Example**

Figures 3A and 3B are example 844441 application schematics for either the 8 pin M package or the 16 pin G package. The schematic examples focus on functional connections and are not configuration specific. Refer to the pin description and functional tables in the datasheet to ensure that the logic control inputs are properly set.

In this example, the device is operated at  $V_{DD} = 2.5 \text{V}$ . A 12pF parallel resonant 25MHz crystal is used with tuning capacitors C1 = C2 =14pF, which are recommended for frequency accuracy. Depending on the variation of the parasitic stray capacity of the printed circuit board traces between the crystal and the Xtal\_In and Xtal\_Out pins, the values of C1 and C2 might require a slight adjustment to optimize the frequency accuracy. Crystals with other load capacitance specifications can be used, but this will require adjusting C1 and C2. In circuit board design, return the capacitors to ground through a single point contact close to the package. Two examples of terminations for LVDS receivers without built-in termination are shown in this schematic.

In order to achieve the best possible filtering, it is recommended that the placement of the power filter components be on the device side of the PCB as close to the power pins as possible. If space is limited, the  $0.1\mu F$  capacitor in each power pin filter should be placed on the device side. The other components can be on the opposite side of the PCB.

Power supply filter recommendations are a general guideline to be used for reducing external noise from coupling into the devices. The filter performance is designed for a wide range of noise frequencies. This low-pass filter starts to attenuate noise at approximately 10kHz. If a specific frequency noise component is known, such as switching power supplies frequencies, it is recommended that component values be adjusted and if required, additional filtering be added. Additionally, good general design practices for power plane voltage stability suggests adding bulk capacitance in the local area of all devices.

Figure 3A. 844441 Schematic Example

Figure 3B. 844441 Schematic Example

#### **Power Considerations**

This section provides information on power dissipation and junction temperature for the 844441. Equations and example calculations are also provided.

#### 1. Power Dissipation.

The total power dissipation for the 844441 is the sum of the core power plus the power dissipated due to loading. The following is the power dissipation for  $V_{DD} = 2.5V + 5\% = 2.625V$ , which gives worst case results.

Total Power  $_{MAX} = V_{DD MAX} * I_{DD MAX} = 2.625 V * 73 mA = 191.7 mW$

#### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad, and directly affects the reliability of the device. The maximum recommended junction temperature is 125°C. Limiting the internal transistor junction temperature, Tj, to 125°C ensures that the bond wire and bond pad temperature remains below 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + T<sub>A</sub>

Tj = Junction Temperature

$\theta_{JA}$  = Junction-to-Ambient Thermal Resistance

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta_{JA}$  must be used. Assuming no air flow and a multi-layer board, the appropriate value is 96°C/W per Table 6B below.

Therefore, Tj for an ambient temperature of 85°C with all outputs switching is:

$85^{\circ}\text{C} + 0.192\text{W} * 96^{\circ}\text{C/W} = 103.4^{\circ}\text{C}$ . This is well below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the supply voltage, air flow and the type of board (multi-layer).

#### Table 6A. Thermal Resistance $\theta_{JA}$ for 16 Lead TSSOP, Forced Convection

| $\theta_{JA}$ vs. Air Flow                  |          |          |          |  |  |

|---------------------------------------------|----------|----------|----------|--|--|

| Meters per Second                           | 0        | 1        | 2.5      |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 81.2°C/W | 73.9°C/W | 70.2°C/W |  |  |

#### Table 6B. Thermal Resistance $\theta_{JA}$ for 8 Lead SOIC, Forced Convection

| $	heta_{JA}$ vs. Air Flow                   |        |        |        |  |

|---------------------------------------------|--------|--------|--------|--|

| Linear Feet per Second                      | 0      | 200    | 500    |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 96°C/W | 87°C/W | 82°C/W |  |

# **Reliability Information**

# Table 7A. $\theta_{JA}$ vs. Air Flow Table for a 16 Lead TSSOP

| $	heta_{JA}$ vs. Air Flow                   |          |          |          |  |

|---------------------------------------------|----------|----------|----------|--|

| Meters per Second                           | 0        | 1        | 2.5      |  |

| Multi-Layer PCB, JEDEC Standard Test Boards | 81.2°C/W | 73.9°C/W | 70.2°C/W |  |

# Table 7B. $\theta_{\text{JA}}$ vs. Air Flow Table for a 8 Lead SOIC

| $\theta_{\sf JA}$ vs. Air Flow              |        |        |        |

|---------------------------------------------|--------|--------|--------|

| Linear Feet per Second                      | 0      | 200    | 500    |

| Multi-Layer PCB, JEDEC Standard Test Boards | 96°C/W | 87°C/W | 82°C/W |

#### **Transistor Count**

The transistor count for 844441 is: 3374

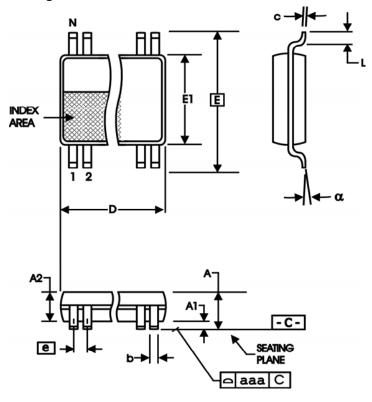

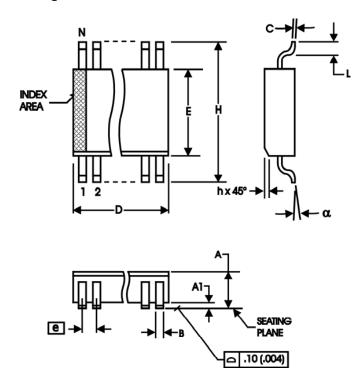

# **Package Outline and Package Dimensions**

#### Package Outline - G Suffix for 16-Lead TSSOP

Table 8A. Package Dimensions for 16 Lead TSSOP

| All Dimensions in Millimeters |                 |      |  |  |

|-------------------------------|-----------------|------|--|--|

| Symbol                        | Minimum Maximum |      |  |  |

| N                             | 1               | 6    |  |  |

| Α                             |                 | 1.20 |  |  |

| A1                            | 0.05            | 0.15 |  |  |

| A2                            | 0.80            | 1.05 |  |  |

| b                             | 0.19            | 0.30 |  |  |

| С                             | 0.09            | 0.20 |  |  |

| D                             | 4.90            | 5.10 |  |  |

| E                             | 6.40 Basic      |      |  |  |

| E1                            | 4.30            | 4.50 |  |  |

| е                             | 0.65 Basic      |      |  |  |

| L                             | 0.45            | 0.75 |  |  |

| α                             | 0°              | 8°   |  |  |

| aaa                           |                 | 0.10 |  |  |

Reference Document: JEDEC Publication 95, MO-153

Package Outline - M Suffix for 8 Lead SOIC

Table 8B. Package Dimensions for 8 Lead SOIC

| All Din | All Dimensions in Millimeters |      |  |  |  |

|---------|-------------------------------|------|--|--|--|

| Symbol  | Minimum Maximum               |      |  |  |  |

| N       |                               | 8    |  |  |  |

| Α       | 1.35                          | 1.75 |  |  |  |

| A1      | 0.10                          | 0.25 |  |  |  |

| В       | 0.33                          | 0.51 |  |  |  |

| С       | 0.19                          | 0.25 |  |  |  |

| D       | 4.80                          | 5.00 |  |  |  |

| E       | 3.80                          | 4.00 |  |  |  |

| е       | 1.27 Basic                    |      |  |  |  |

| Н       | 5.80 6.20                     |      |  |  |  |

| h       | 0.25                          | 0.50 |  |  |  |

| L       | 0.40                          | 1.27 |  |  |  |

| α       | 0°                            | 8°   |  |  |  |

Reference Document: JEDEC Publication 95, MS-012

# **Ordering Information**

# **Table 9. Ordering Information**

| Part/Order Number | Marking  | Output Frequency<br>(MHz) | Package                  | Shipping Packaging | Temperature   |

|-------------------|----------|---------------------------|--------------------------|--------------------|---------------|

| 844441DGILF       | 44441DIL | 75, 100, 150, 300         | 16 Lead TSSOP, Lead-Free | Tube               | -40°C to 85°C |

| 844441DGILFT      | 44441DIL | 75, 100, 150, 300         | 16 Lead TSSOP, Lead-Free | Tape & Reel        | -40°C to 85°C |

| 844441DMI-75LF    | 441DI75L | 75                        | 8 Lead SOIC, Lead-Free   | Tube               | -40°C to 85°C |

| 844441DMI-75LFT   | 441DI75L | 75                        | 8 Lead SOIC, Lead-Free   | Tape & Reel        | -40°C to 85°C |

| 844441DMI-100LF   | 41DI100L | 100                       | 8 Lead SOIC, Lead-Free   | Tube               | -40°C to 85°C |

| 844441DMI-100LFT  | 41DI100L | 100                       | 8 Lead SOIC, Lead-Free   | Tape & Reel        | -40°C to 85°C |

| 844441DMI-150LF   | 41DI150L | 150                       | 8 Lead SOIC, Lead-Free   | Tube               | -40°C to 85°C |

| 844441DMI-150LFT  | 41DI150L | 150                       | 8 Lead SOIC, Lead-Free   | Tape & Reel        | -40°C to 85°C |

| 844441DMI-300LF   | 41DI300L | 300                       | 8 Lead SOIC, Lead-Free   | Tube               | -40°C to 85°C |

| 844441DMI-300LFT  | 41DI300L | 300                       | 8 Lead SOIC, Lead-Free   | Tape & Reel        | -40°C to 85°C |

# **Revision History Sheet**

| Rev | Table     | Page                  | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|-----|-----------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| В   | T4D<br>T5 | 1<br>4<br>4<br>9 - 10 | Features Section, Crystal Oscillator bullet, added additional crystal recommendation. Crystal Characteristics Table - added crystal recommendation note. AC Characteristics Table - added additional crystal recommendation to 2nd note. Application Schematics - in schematics, added additional crystal recommendation. Deleted part number prefix/suffix throughout the datasheet. Updated datasheet header/footer. | 5/5/15   |

| С   |           | 9 - 10                | Updated Application Schematics.                                                                                                                                                                                                                                                                                                                                                                                        | 7/31/15  |

| D   |           | 1                     | PDN #CQ-15-04 Product Discontinuance Notice – Last Time buy Expires on August 14, 2016.                                                                                                                                                                                                                                                                                                                                | 08/21/15 |

| Е   |           | 9 - 10                | The 844441 datasheet is obsolete per PDN #CQ-15-04. Application Schematic, IDT crystal part number was replaced by FOX part number.                                                                                                                                                                                                                                                                                    | 11/2/16  |

#### **Corporate Headquarters**

6024 Silver Creek Valley Road San Jose, CA 95138 USA www.IDT.com

#### Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

#### **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc. All rights reserved.