## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# 5V/3.3V 32-1250Mbps AnyRate® CLOCK AND DATA RECOVERY

SY87701V

Use lower-power SY87701AL for 3.3V systems

#### **FEATURES**

- 3.3V and 5V power supply options

- Clock and data recovery from 32Mbps up to 1.25Gbps NRZ data stream, clock generation from 32Mbps to 1.25Gbps

- Complies with Bellcore, ITU/CCITT and ANSI specifications for applications such as OC-1, OC-3, OC-12, ATM, FDDI, Fibre Channel and Gigabit Ethernet, as well as proprietary applications

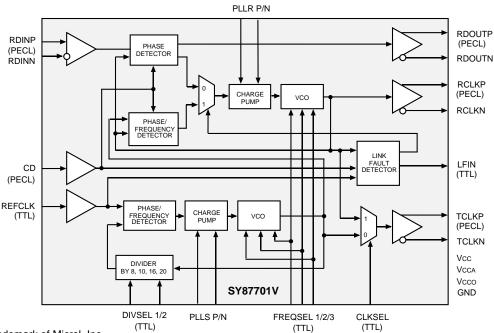

- Two on-chip PLLs: one for clock generation and another for clock recovery

- Selectable reference frequencies

- Differential PECL high-speed serial I/O

- Line receiver input: no external buffering needed

- **■** Link fault indication

- 100K ECL compatible I/O

- Available in 32-pin EPAD-TQFP and 28-pin SOIC packages (28-pin SOIC is available, but not recommended for new designs, see page 2 for details

#### **APPLICATIONS**

- SONET/SDH/ATM OC-1, OC-3, OC-12, OC-24

- **■** Fibre Channel, Escon, SMPTE 259

- Gigabit Ethernet/Fast Ethernet

- Proprietary architecture up to 1.25Gbps

AnyRate<sup>®</sup>

#### **DESCRIPTION**

The SY87701V is a complete Clock Recovery and Data Retiming integrated circuit for data rates from 32Mbps up to 1.25Gbps NRZ. The device is ideally suited for SONET/SDH/ATM and Fibre Channel applications and other high-speed data transmission systems.

Clock recovery and data retiming is performed by synchronizing the on-chip VCO directly to the incoming data stream. The VCO center frequency is controlled by the reference clock frequency and the selected divide ratio. On-chip clock generation is performed through the use of a frequency multiplier PLL with a byte rate source as reference.

The SY87701V also includes a link fault detection circuit.

Datasheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **BLOCK DIAGRAM**

AnyRate is a registered trademark of Micrel, Inc.

Rev.: O Amendment: /0

Issue Date: July 2008

### **PACKAGE/ORDERING INFORMATION**

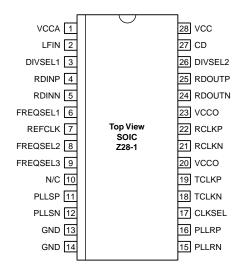

28-Pin SOIC (Z28-1)

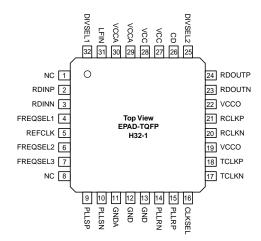

32-Pin EPAD TQFP (H32-1)

## Ordering Information<sup>(1)</sup>

| Part Number                       | Package<br>Type | Operating<br>Range | Package<br>Marking                            | Lead<br>Finish    |

|-----------------------------------|-----------------|--------------------|-----------------------------------------------|-------------------|

| SY87701VZC <sup>(3, 4)</sup>      | Z28-1           | Commercial         | SY87701VZC                                    | Sn-Pb             |

| SY87701VZCTR <sup>(2, 3, 4)</sup> | Z28-1           | Commercial         | SY87701VZC                                    | Sn-Pb             |

| SY87701VHC <sup>(3)</sup>         | H32-1           | Commercial         | SY87701VHC                                    | Sn-Pb             |

| SY87701VHCTR <sup>(2, 3)</sup>    | H32-1           | Commercial         | SY87701VHC                                    | Sn-Pb             |

| SY87701VZH <sup>(3, 4)</sup>      | Z28-1           | Commercial         | SY87701VZH with Pb-Free bar line indicator    | NiPdAu<br>Pb-Free |

| SY87701VZHTR <sup>(2, 3, 4)</sup> | Z28-1           | Commercial         | SY87701VZH with Pb-Free bar line indicator    | NiPdAu<br>Pb-Free |

| SY87701VHH <sup>(3)</sup>         | H32-1           | Commercial         | SY87701VHH with Pb-Free bar line indicator    | NiPdAu<br>Pb-Free |

| SY87701VHHTR <sup>(2, 3)</sup>    | H32-1           | Commercial         | SY87701VHH with<br>Pb-Free bar line indicator | NiPdAu<br>Pb-Free |

#### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25$ °C, DC Electricals only.

- 2. Tape and Reel.

- 3. Pb-Free package is recommended for new designs.

- 4. For optimum reliability, care should be taken when using the Z28-1 SOIC package to maintain the package case temperature at or below 70°C.

#### **PIN DESCRIPTIONS**

#### **INPUTS**

#### RDINP, RDINN [Serial Data Input] Differential PECL.

These built-in line receiver inputs are connected to the differential receive serial data stream. An internal receive PLL recovers the embedded clock (RCLK) and data (RDOUT) information. The incoming data rate can be within one of eight frequency ranges depending on the state of the FREQSEL pins. See "Frequency Selection" Table.

#### REFCLK [Reference Clock] TTL Input.

This input is used as the reference for the internal frequency synthesizer and the "training" frequency for the receiver PLL to keep it centered in the absence of data coming in on the RDIN inputs.

#### CD [Carrier Detect] PECL Input.

This input controls the recovery function of the Receive PLL and can be driven by the carrier detect output of optical modules or from external transition detection circuitry. When this input is HIGH the input data stream (RDIN) is recovered normally by the Receive PLL. When this input is LOW the data on the inputs RDIN will be internally forced to a constant LOW, the data outputs RDOUT will remain LOW, the Link Fault Indicator output LFIN forced LOW and the clock recovery PLL forced to lock onto the clock frequency generated from REFCLK.

## FREQSEL1, ..., FREQSEL3 [Frequency Select] TTL Inputs.

These inputs select the output clock frequency range as shown in the "Frequency Selection" Table.

#### DIVSEL1, DIVSEL2 [Divider Select] TTL Inputs.

These inputs select the ratio between the output clock frequency (RCLK/TCLK) and the REFCLK input frequency as shown in the "Reference Frequency Selection" Table.

#### CLKSEL [Clock Select] TTL Input.

This input is used to select either the recovered clock of the receiver PLL (CLKSEL = HIGH) or the clock of the frequency synthesizer (CLKSEL = LOW) to the TCLK outputs.

#### **OUTPUTS**

#### LFIN [Link Fault Indicator] TTL Output.

This output indicates the status of the input data stream RDIN. Active HIGH signal is indicating when the internal clock recovery PLL has locked onto the incoming data stream. LFIN will go HIGH if CD is HIGH and RDIN is within the frequency range of the Receive PLL (1000ppm). LFIN is an asynchronous output.

## **RDOUTP, RDOUTN [Receive Data Output]** Differential PECL.

These ECL 100K outputs (+3.3V or +5V referenced) represent the recovered data from the input data stream (RDIN). This recovered data is sampled on the rising edge of RCLK.

#### RCLKP, RCLKN [Clock Output] Differential PECL.

These ECL 100K outputs (+3.3V or +5V referenced) represent the recovered clock used to sample the recovered data (RDOUT).

#### TCLKP, TCLKN [Clock Output] Differential PECL.

These ECL 100K outputs (+3.3V or +5V referenced) represent either the recovered clock (CLKSEL = HIGH) used to sample the recovered data (RDOUT) or the transmit clock of the frequency synthesizer (CLKSEL = LOW).

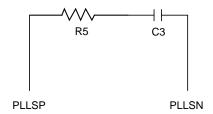

## PLLSP, PLLSN [Clock Synthesis PLL Loop Filter]

External loop filter pins for the clock synthesis PLL.

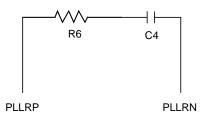

## PLLRP, PLLRN [Clock Recovery PLL Loop Filter]

External loop filter pins for the receiver PLL.

#### **POWER & GROUND**

**V<sub>CC</sub>** Supply Voltage<sup>(Note 1)</sup>

V<sub>CCA</sub> Analog Supply Voltage(Note 1)

V<sub>CCO</sub> Output Supply Voltage<sup>(Note 1)</sup>

GND Ground

N/C No Connect

Note 1.  $V_{CC}$ ,  $V_{CCA}$ ,  $V_{CCO}$  must be the same value.

#### **FUNCTIONAL DESCRIPTION**

#### **Clock Recovery**

Clock Recovery, as shown in the block diagram generates a clock that is at the same frequency as the incoming data bit rate at the Serial Data input. The clock is phase aligned by a PLL so that it samples the data in the center of the data eye pattern.

The phase relationship between the edge transitions of the data and those of the generated clock are compared by a phase/frequency detector. Output pulses from the detector indicate the required direction of phase correction. These pulses are smoothed by an integral loop filter. The output of the loop filter controls the frequency of the Voltage Controlled Oscillator (VCO), which generates the recovered clock.

Frequency stability without incoming data is guaranteed by an alternate reference input (REFCLK) that the PLL locks onto when data is lost. If the Frequency of the incoming signal varies by greater than approximately 1000ppm with respect to the synthesizer frequency, the PLL will be declared out of lock, and the PLL will lock to the reference clock.

The loop filter transfer function is optimized to enable the PLL to track the jitter, yet tolerate the minimum transition density expected in a received SONET data signal. This transfer function yields a 30µs data stream of continuous 1's or 0's for random incoming NRZ data.

The total loop dynamics of the clock recovery PLL provides jitter tolerance which is better than the specified tolerance in GR-253-CORE.

#### **Lock Detect**

The SY87701V contains a link fault indication circuit which monitors the integrity of the serial data inputs. If the received serial data fails the frequency test, the PLL will be forced to lock to the local reference clock. This will maintain the correct frequency of the recovered clock output under loss of signal or loss of lock conditions. If the recovered clock frequency deviates from the local reference clock frequency by more than approximately 1000ppm, the PLL will be declared out of lock. The lock detect circuit will poll the input data stream in an attempt to reacquire lock to data. If the recovered clock frequency is determined to be within approximately 1000ppm, the PLL will be declared in lock and the lock detect output will go active.

#### **CHARACTERISTICS**

#### **Performance**

The SY87701V PLL complies with the jitter specifications proposed for SONET/SDH equipment defined by the Bellcore Specifications: GR-253-CORE, Issue 2, December 1995 and ITU-T Recommendations: G.958 document, when used with differential inputs and outputs.

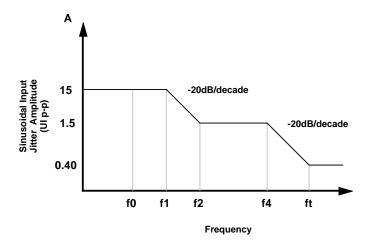

#### **Input Jitter Tolerance**

Input jitter tolerance is defined as the peak-to-peak amplitude of sinusoidal jitter applied on the input signal that causes an equivalent 1dB optical/electrical power penalty. SONET input jitter tolerance requirement condition is the input jitter amplitude which causes an equivalent of 1dB power penalty.

#### **Jitter Transfer**

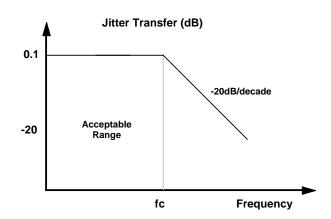

Jitter transfer function is defined as the ratio of jitter on the output OC-N/STS-N signal to the jitter applied on the input OC-N/STS-N signal versus frequency. Jitter transfer requirements are shown in Figure 2.

#### **Jitter Generation**

The jitter of the serial clock and serial data outputs shall not exceed .01 U.I. rms when a serial data input with no jitter is presented to the serial data inputs.

| OC/STS-N<br>Level | f0<br>(Hz) | f1<br>(Hz) | f2<br>(Hz) | f3<br>(kHz) | ft<br>(kHz) |

|-------------------|------------|------------|------------|-------------|-------------|

| 3                 | 10         | 30         | 300        | 6.5         | 65          |

| 12                | 10         | 30         | 300        | 25          | 250         |

Figure 1. Input Jitter Tolerance

| OC/STS-N<br>Level | fc<br>(kHz) | P<br>(dB) |

|-------------------|-------------|-----------|

| 3                 | 130         | 0.1       |

| 12                | 225         | 0.1       |

Figure 2. Jitter Transfer

## **FREQUENCY SELECTION TABLE**

| FREQSEL1 | FREQSEL2 | FREQSEL3 | f <sub>VCO</sub> /f <sub>RCLK</sub> | f <sub>RCLK</sub> Data Rates (Mbps) |

|----------|----------|----------|-------------------------------------|-------------------------------------|

| 0        | 0        | 0        | 1                                   | 750 – 1250                          |

| 0        | 0        | 1        | 2                                   | 375 – 625                           |

| 0        | 1        | 0        | 4                                   | 188 – 313                           |

| 0        | 1        | 1        | 6                                   | 125 – 208                           |

| 1        | 0        | 0        | 8                                   | 94 – 157                            |

| 1        | 0        | 1        | 12                                  | 63 – 104                            |

| 1        | 1        | 0        | 16                                  | 47 – 78                             |

| 1        | 1        | 1        | 24                                  | 32 – 52                             |

## REFERENCE FREQUENCY SELECTION

| DIVSEL1 | DIVSEL2 | f <sub>RCLK</sub> /f <sub>REFCLK</sub> |

|---------|---------|----------------------------------------|

| 0       | 0       | 8                                      |

| 0       | 1       | 10                                     |

| 1       | 0       | 16                                     |

| 1       | 1       | 20                                     |

## LOOP FILTER COMPONENTS(Note 1)

#### Wide Range

$R5 = 350\Omega$

$C3 = 1.0 \mu F$  (X7R Dielectric)

#### Wide Range

$R6 = 680\Omega$

$C4 = 1.0 \mu F$  (X7R Dielectric)

**Note 1.** Suggested Values. Values may vary for different applications.

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol             | Rating                |                  | Value                 | Unit |

|--------------------|-----------------------|------------------|-----------------------|------|

| V <sub>CC</sub>    | Power Supply Voltage  |                  | .5 to +7.0            | V    |

| V <sub>IN</sub>    | Input Voltage         |                  | .5 to V <sub>CC</sub> | V    |

| l <sub>оит</sub>   | Output Current - Co   | ontinuous<br>rge | 50<br>100             | mA   |

| T <sub>store</sub> | Storage Temperature   | -6               | 5 to +150             | °C   |

| T <sub>A</sub>     | Operating Temperature | (                | ) to +85              | °C   |

| T <sub>C</sub>     | Case Temperature      | (                | ) to +70              | °C   |

SY87701V

**Note 1.** Permanent device damage may occur if "Absolute Maximum Ratings" are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to "Absolute Maximum Ratings" conditions for extended periods may affect device reliability.

## PACKAGE THERMAL DATA<sup>(1)</sup>

θ<sub>JA</sub> (°C/W) by Velocity (LFPM)

| Package <sup>(1, 2)</sup>       | 0    | 200  | 500  |

|---------------------------------|------|------|------|

| 28-Pin SOIC <sup>(1, 2)</sup>   | 80   | _    |      |

| 32-Pin EPAD-TQFP <sup>(3)</sup> | 27.6 | 22.6 | 20.7 |

- Note 1. Case temperature not to exceed 70°C recommended for 28-pin SOIC.

- Note 2. 28-pin SOIC package is NOT recommended for new designs.

- **Note 3.** Using JEDEC standard test boards with die attach pad soldered to PCB. See www.amkor.com for additional package details.

### DC ELECTRICAL CHARACTERISTICS

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\%$  or 5.0V  $\pm 5\%$ ,  $T_A = 0^{\circ}C$  to + 85°C for 32-TQFP,  $T_C = 0^{\circ}C$  to 70°C for SOIC.

| Symbol          | Parameter            | Min.         | Тур.       | Max.         | Unit   | Condition |

|-----------------|----------------------|--------------|------------|--------------|--------|-----------|

| V <sub>CC</sub> | Power Supply Voltage | 3.15<br>4.75 | 3.3<br>5.0 | 3.45<br>5.25 | V<br>V |           |

| I <sub>CC</sub> | Power Supply Current | _            | 170        | 230          | mA     |           |

### PECL 100K DC ELECTRICAL CHARACTERISTICS

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\% \text{ or } 5.0V \pm 5\%; T_A = 0^{\circ}C \text{ to } +85^{\circ}C$

| Symbol          | Parameter           | Min.                   | Тур. | Max.                   | Unit | Condition                  |

|-----------------|---------------------|------------------------|------|------------------------|------|----------------------------|

| V <sub>IH</sub> | Input HIGH Voltage  | V <sub>CC</sub> –1.165 | _    | V <sub>CC</sub> -0.880 | V    |                            |

| $V_{IL}$        | Input LOW Voltage   | V <sub>CC</sub> –1.810 | _    | V <sub>CC</sub> -1.475 | V    |                            |

| V <sub>OH</sub> | Output HIGH Voltage | V <sub>CC</sub> –1.075 | _    | V <sub>CC</sub> -0.830 | V    | 50Ω to V <sub>CC</sub> –2V |

| V <sub>OL</sub> | Output LOW Voltage  | V <sub>CC</sub> –1.860 | _    | V <sub>CC</sub> –1.570 | V    | 50Ω to V <sub>CC</sub> –2V |

| I <sub>IL</sub> | Input LOW Current   | 0.5                    | _    | _                      | μΑ   | $V_{IN} = V_{IL}(Min.)$    |

#### TTL DC ELECTRICAL CHARACTERISTICS

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\%$  or 5.0V  $\pm 5\%$ ;  $T_A = 0^{\circ}C$  to + 85°C for 32-TQFP,  $T_C = 0^{\circ}C$  to 70°C for SOIC.

| Symbol          | Parameter                    | Min. | Тур. | Max.     | Unit | Condition                            |

|-----------------|------------------------------|------|------|----------|------|--------------------------------------|

| V <sub>IH</sub> | Input HIGH Voltage           | 2.0  |      | $V_{CC}$ | V    |                                      |

| V <sub>IL</sub> | Input LOW Voltage            | _    | _    | 0.8      | V    |                                      |

| V <sub>OH</sub> | Output HIGH Voltage          | 2.0  | _    | _        | V    | I <sub>OH</sub> = -0.4mA             |

| V <sub>OL</sub> | Output LOW Voltage           | _    | _    | 0.5      | V    | I <sub>OL</sub> = 4mA                |

| I <sub>IH</sub> | Input HIGH Current           | -175 | _    | _        | μΑ   | $V_{IN} = 2.7V$ , $V_{CC} = Max$ .   |

|                 |                              | _    |      | +100     | μΑ   | $V_{IN} = V_{CC}, V_{CC} = Max.$     |

| I <sub>IL</sub> | Input LOW Current            | -300 |      |          | μΑ   | $V_{IN} = 0.5V$ , $V_{CC} = Max$ .   |

| Ios             | Output Short Circuit Current | 15   | _    | 100      | mA   | V <sub>OUT</sub> = 0V (maximum 1sec) |

#### **AC ELECTRICAL CHARACTERISTICS**

$V_{CC} = V_{CCO} = V_{CCA} = 3.3V \pm 5\%$  or 5.0V  $\pm 5\%$ ;  $T_A = 0^{\circ}$ C to + 85°C for 32-TQFP,  $T_C = 0^{\circ}$ C to 70°C for SOIC.

| Symbol                           | Parameter                              | Min.                           | Тур. | Max. | Unit    | Condition                         |

|----------------------------------|----------------------------------------|--------------------------------|------|------|---------|-----------------------------------|

| f <sub>VCO</sub>                 | VCO Center Frequency                   | 750                            |      | 1250 | MHz     | f <sub>REFCLK</sub> × Byte Rate   |

| $\Delta f_{VCO}$                 | VCO Center Frequency<br>Tolerance      |                                | 5    | ı    | %       | Nominal                           |

| t <sub>ACQ</sub>                 | Acquisition Lock Time                  |                                | 1    | 15   | μs      |                                   |

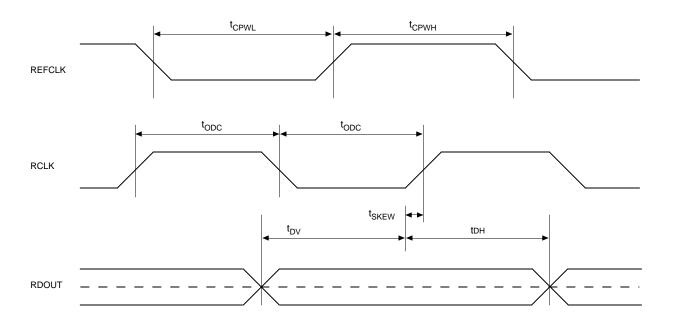

| t <sub>CPWH</sub>                | REFCLK Pulse Width HIGH                | 4                              |      |      | ns      |                                   |

| t <sub>CPWL</sub>                | REFCLK Pulse Width LOW                 | 4                              | _    | _    | ns      |                                   |

| t <sub>ir</sub>                  | REFCLK Input Rise Time                 | _                              | 0.5  | 2    | ns      |                                   |

| t <sub>ODC</sub>                 | Output Duty Cycle (RCLK/TCLK)          | 45                             |      | 55   | % of UI |                                   |

| t <sub>r</sub><br>t <sub>f</sub> | ECL Output Rise/Fall Time (20% to 80%) | 100                            | _    | 500  | ps      | 50 $\Omega$ to V <sub>CC</sub> –2 |

| t <sub>SKEW</sub>                | Recovered Clock Skew                   | -200                           | _    | +200 | ps      |                                   |

| t <sub>DV</sub>                  | Data Valid                             | 1/(2×f <sub>RCLK</sub> ) – 200 | _    | _    | ps      |                                   |

| t <sub>DH</sub>                  | Data Hold                              | 1/(2×f <sub>RCLK</sub> ) – 200 |      | _    | ps      |                                   |

## TIMING WAVEFORMS

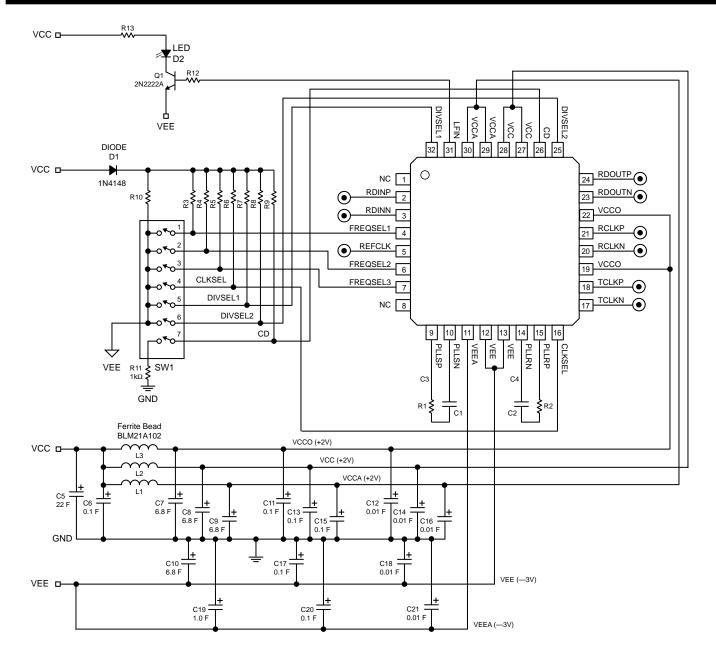

## **32-PIN APPLICATION EXAMPLE**

#### Note:

C3, C4 are optional

| C1 = C2 = 1.0μF             |

|-----------------------------|

| $R1 = 350\Omega$            |

| $R2 = 680\Omega$            |

| R3 through R10 = $5k\Omega$ |

| $R12 = 12k\Omega$           |

| $R13 = 130\Omega$           |

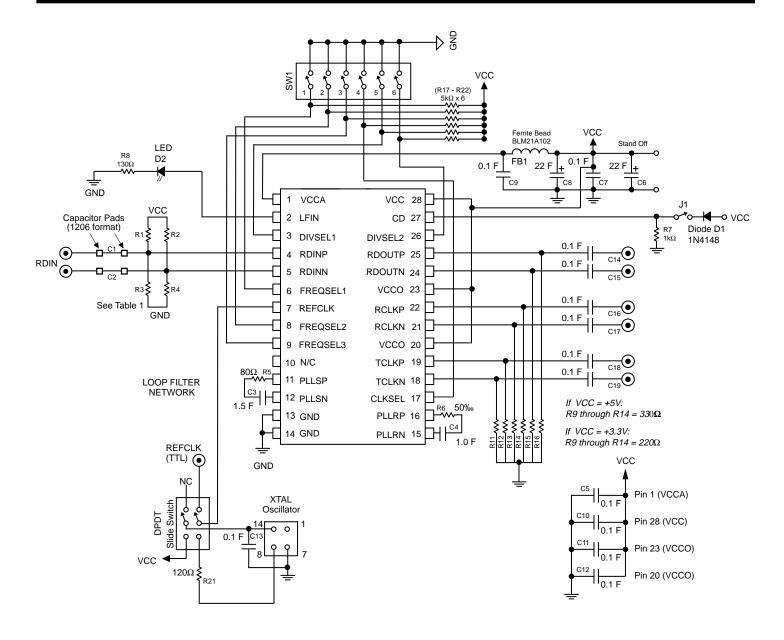

### **28-PIN APPLICATION EXAMPLE**

**Note 1.** C5 and C10–C12 are decoupling capacitors and should be kept as close to the power pins as possible.

| For AC-Coupling Only   |                       | For DC Mode Only      |                   |

|------------------------|-----------------------|-----------------------|-------------------|

| when VCC = +5V         | when VCC = +3.3V      | when VCC = +5V        | when VCC = +3.3V  |

| C1 = C2 = 0.1μF        | C1 = C2 = 0.1μF       | C1 = C2 = Shorted     | C1 = C2 = Shorted |

| R1 = R2 = 1.2kΩ        | $R1 = R2 = 680\Omega$ | R1 = R2 = 82Ω         | R1 = R2 = 130Ω    |

| $R3 = R4 = 3.4k\Omega$ | $R3 = R4 = 1k\Omega$  | $R3 = R4 = 130\Omega$ | R3 = R4 = 82Ω     |

Table 1.

## **BILL OF MATERIALS (32-PIN EPAD-TQFP)**

| Item                                                   | em Part Number  |                       | Description                                                                   | Qty. |

|--------------------------------------------------------|-----------------|-----------------------|-------------------------------------------------------------------------------|------|

| C1, C2                                                 | VJ0603Y105JXJAT | Vishay                | 1.0μF Ceramic Capacitor, Size 0603<br>X7R Dielectric, Loop Filter, Critical   | 2    |

| C3, C4                                                 | VJ0603Y105JXJAT | Vishay                | 1.0μF Ceramic Capacitor, Size 0603<br>X7R Dielectric, Loop Filter, Optional   | 2    |

| C5                                                     | ECS-T1ED226R    | Panasonic             | 22μF Tantalum Electrolytic Capacitor, Size D                                  | 1    |

| C6                                                     | ECU-V1H104KBW   | Panasonic             | 0.1μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, Power Supply Decoupling | 1    |

| C7, C8, C9, C10                                        | ECS-T1EC685R    | Panasonic             | 6.8μF Tantalum Electrolytic Capacitor, Size C                                 |      |

| C19                                                    | ECJ-3YB1E105K   | Panasonic             | 1.0μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VEEA Decoupling         | 1    |

| C11, C13                                               | ECU-V1H104KBW   | Panasonic             | 0.1μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VCCO/VCC Decoupling     | 1    |

| C15, C17                                               | ECU-V1H104KBW   | Panasonic             | 0.1μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VCCA/VEEA Decoupling    | 1    |

| C20                                                    | ECU-V1H104KBW   | Panasonic             | 0.1μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VEEA Decoupling         | 1    |

| C12, C14                                               | ECU-V1H103KBW   | Panasonic             | 0.01μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VCCO/VCC Decoupling    | 1    |

| C16, C18                                               | ECU-V1H103KBW   | Panasonic             | 0.01μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VCCA/VEEA Decoupling   | 1    |

| C21                                                    | ECU-V1H103KBW   | Panasonic             | 0.01μF Ceramic Capacitor, Size 1206<br>X7R Dielectric, VEEA Decoupling        | 1    |

| D1                                                     | 1N4148          |                       | Diode                                                                         | 1    |

| D2                                                     | P300-ND/P301-ND | Panasonic             | T-1 3/4 Red LED                                                               | 1    |

| J1, J2, J3, J4, J5<br>J6, J7, J8, J9,<br>J10, J11, J12 | 142-0701-851    | Johnson<br>Components | Gold Plated, Jack, SMA, PCB Mount                                             |      |

| L1, L2, L3                                             | BLM21A102F      | Murata                | Ferrite Beads, Power Noise Suppression                                        | 3    |

| Q1                                                     | NTE123A         | NTE                   | 2N2222A Buffer/Driver Transistor, NPN                                         | 1    |

| R1                                                     |                 |                       | 350Ω Resistor, 2%, Size 0402<br>Loop Filter Component, Critical               |      |

| R2                                                     |                 |                       | 680Ω Resistor, 2%, Size 0402<br>Loop Filter Component, Critical               |      |

| R3, R4, R5, R6<br>R7, R8, R9, R10                      |                 |                       | 5kΩ Pullup Resistors, 2%, Size 1206                                           | 8    |

| R11                                                    |                 |                       | 1kΩ Pulldown Resistor, 2%, Size 1206                                          | 1    |

| R12                                                    |                 |                       | 12kΩ Resistor, 2%, Size 1206                                                  |      |

| R13                                                    |                 |                       | 130Ω Pullup Resistor, 2%, Size 1206                                           |      |

| SW1                                                    | 206-7           | CTS                   | SPST, Gold Finish, Sealed Dip Switch                                          | 1    |

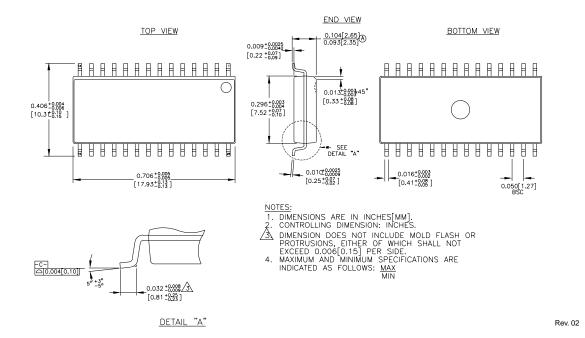

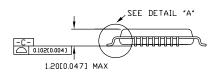

## 28 LEAD SOIC .300" WIDE (Z28-1)

#### Note:

The 28 Lead SOIC package is NOT recommended for new designs.

SY87701V Micrel, Inc.

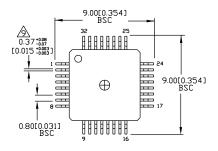

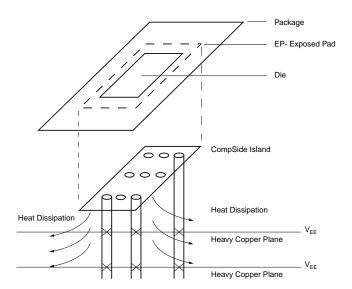

### 32 LEAD EPAD TQFP (DIE UP) (H32-1)

TOP VIEW

SIDE VIEW

3.5 ÷0.30 → [0.138 ÷0.012] BOTTOM VIEW 8 PLACES 0° MIN. 🔌 DATUM 1.00 0.20[0.008] 0.09[0.0035]

3.5 -0.30 7.00[0.276] 3.5 -0.30 BSC [0.138 -0.012]

0.15 [0.006] 0.05 [0.002]

DETAIL "A"

1.00[0.039] REF.

J<sub>0-7</sub>•

--- 0.60 \*0.15 [0.024 \*0.006]

NOTES:

1. DIMENSIONS ARE IN MMCINCHESI.

2. CONTROLLING DIMENSION: MM.

3. DIMENSION DOES NOT INCLUDE MOLD FLASH

OR PROTROUSIONS, EITHER OF WHICH SHALL NOT

EXCEED 0.254 (0.010).

4. LEAD DIMENSION DOES NOT INCLUDE DAMBAR

PROTRUSION.

5. MAXIMUM AND MINIMUM SPECIFICATIONS ARE

INDICATED AS FOLLOWS: MAX/MIN.

6. THESE DIMENSIONS TO BE DETERMINED AT DATUM PLANE HE

7. PACKAGE TOP DIMENSIONS ARE SMALLER THAN BOTTOM DIMENSIONS

AND TOP OF PACKAGE WILL NOT OVERHANG BOTTOM OF PACKAGE.

8. EXPOSED PAD SHALL BE COPLANAR WITH PACKAGE BOTTOM WITHIN 0.05mm

EXPOSED PADS CU WITH Sn/Pb PLATING

9. DIMENSION INCLUDES LEAD FINISH.

PCB Thermal Consideration for 32-Pin EPAD-TQFP Package

#### **APPENDIX A**

#### **Layout and General Suggestions**

- 1. Establish controlled impedance stripline, microstrip, or co-planar construction techniques.

- 2. Signal paths should have, approximately, the same width as the device pads.

- 3. All differential paths are critical timing paths, where skew should be matched to within ±10ps.

- 4. Signal trace impedance should not vary more than ±5%. If in doubt, perform TDR analysis of all high-speed signal traces.

- 5. Maintain compact filter networks as close to filter pins as possible. Provide ground plane relief under filter path to reduce stray capacitance. Be careful of crosstalk coupling into the filter network.

- 6. Maintain low jitter on the REFCLK input. Isolate the XTAL oscillator from power supply noise by adequately decoupling. Keep XTAL oscillator close to device, and minimize capacitive coupling from adjacent signals.

- 7. Higher speed operation may require use of fundamental-tone (third-overtone typically have more jitter) crystal based oscillator for optimum performance. Evaluate and compare candidates by measuring TXCLK jitter.

- 8. All unused outputs must be terminated. To conserve power, unused PECL outputs can be terminated with a  $1k\Omega$  resistor to  $V_{\text{FF}}$ .

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.