1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# Timing-Safe<sup>™</sup> Peak EMI Reduction IC

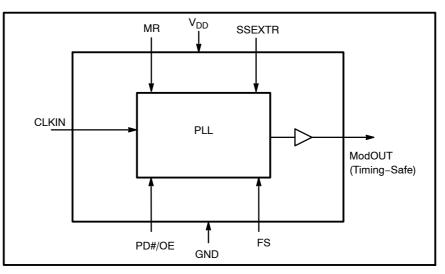

#### **Functional Description**

P3PS850BH is a versatile, Timing–Safe peak EMI reduction IC. P3PS850BH accepts one input from an external reference, and locks on to it delivering a 1x Timing–Safe output clock. P3PS850BH has a Frequency Selection (FS) control that facilitates selecting one of the two operating frequency ranges. Refer to the *frequency Selection table*. The device has an SSEXTR pin to select different deviations depending upon the value of an external resistor connected at this pin to GND. P3PS850BH has an MR pin for selecting one of the two Modulation Rates. PD#/OE provides the Power Down option. Outputs will be tri–stated when power down is active.

P3PS850BH operates over a supply voltage range of 2.3 V to 3.6 V, and is available in an 8 Pin WDFN (2 mm x 2 mm) Package.

#### **General Features**

- 1x, LVCMOS Timing-Safe Peak EMI Reduction

- Input Clock Frequency:

- 18 MHz 72 MHz

- Output Clock Frequency( Timing-Safe):

- ◆ 18 MHz 72 MHz

- Analog Frequency Deviation Selection

- Two different Modulation Rate Selection

- Power Down Option for Power Save

- Output Buffer Strength: 16 mA

- Supply Voltage: 2.3 V 3.6 V

- 8 pin WDFN 2 mm x 2 mm, (TDFN) Package

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### Application

• P3PS850BH is targeted for use in consumer electronic applications like mobile phones, Camera modules, MFP and DPF.

# **ON Semiconductor®**

http://onsemi.com

- M = Date Code

- = Pb-Free Device

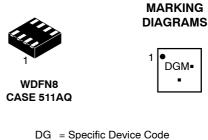

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

1

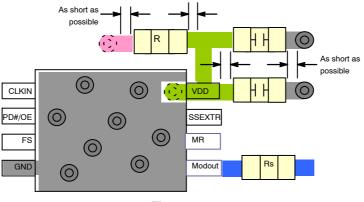

Figure 1. Block Diagram

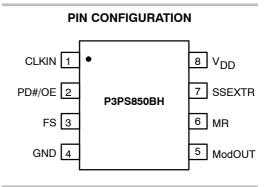

#### Table 1. PIN DESCRIPTION

| Pin# | Pin Name        | Туре | Description                                                                                                                                                            |

|------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | CLKIN           | I    | External reference Clock input.                                                                                                                                        |

| 2    | PD# / OE        | I    | Power Down. Pull LOW to enable Power Down. Outputs will be tri-stated when power down is enabled. Pull HIGH to disable power down and enable output. NO default state. |

| 3    | FS              | I    | Frequency Select .NO default state. Refer to the Frequency Selection table                                                                                             |

| 4    | GND             | Р    | Ground                                                                                                                                                                 |

| 5    | ModOUT          | 0    | Buffered modulated Timing-Safe clock output                                                                                                                            |

| 6    | MR              | I    | Modulation Rate Select. When LOW, selects Low Modulation Rate. Selects High Modulation Rate when pulled HIGH. Has an internal pull-up resistor.                        |

| 7    | SSEXTR          | I    | Analog Deviation Selection through external resistor to GND.                                                                                                           |

| 8    | V <sub>DD</sub> | Р    | Supply Voltage                                                                                                                                                         |

#### Table 2. FREQUENCY SELECTION TABLE

| FS | Frequency (MHz) |

|----|-----------------|

| 0  | 18–36           |

| 1  | 36–72           |

#### **Table 3. OPERATING CONDITIONS**

| Symbol          | Parameter             | Min | Max | Unit |

|-----------------|-----------------------|-----|-----|------|

| V <sub>DD</sub> | Supply Voltage        |     | 3.6 | V    |

| T <sub>A</sub>  | Operating Temperature |     | +85 | °C   |

| CL              | Load Capacitance      |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance     |     | 7   | pF   |

#### Table 4. ABSOLUTE MAXIMUM RATING

| Symbol           | Parameter                                            | Rating       | Unit |

|------------------|------------------------------------------------------|--------------|------|

| $V_{DD,} V_{IN}$ | Voltage on any input pin with respect to Ground      | -0.5 to +4.6 | V    |

| T <sub>STG</sub> | Storage temperature                                  | -65 to +125  | °C   |

| Ts               | Max. Soldering Temperature (10 sec)                  | 260          | °C   |

| TJ               | Junction Temperature                                 | 150          | °C   |

| T <sub>DV</sub>  | Static Discharge Voltage (As per JEDEC STD22-A114-B) | 2            | kV   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Table 5. DC ELECTRICAL CHARACTERISTICS

| Symbol          | Parameter              | Test Conditions                   |                                   | Min                    | Тур | Max                    | Unit |

|-----------------|------------------------|-----------------------------------|-----------------------------------|------------------------|-----|------------------------|------|

| V <sub>DD</sub> | Supply Voltage         |                                   |                                   | 2.3                    | 2.7 | 3.6                    | V    |

| V <sub>IH</sub> | Input HIGH Voltage     |                                   |                                   | 0.65 * V <sub>DD</sub> |     |                        | V    |

| V <sub>IL</sub> | Input LOW Voltage      |                                   |                                   |                        |     | 0.35 * V <sub>DD</sub> | V    |

| I <sub>IH</sub> | Input HIGH Current     | V <sub>IN</sub> = V <sub>DD</sub> | V <sub>IN</sub> = V <sub>DD</sub> |                        |     | 10                     | μA   |

| I <sub>IL</sub> | Input LOW Current      | V <sub>IN</sub> = 0 V for MR pir  | 1                                 |                        |     | 10                     | μA   |

| V <sub>OH</sub> | Output HIGH Voltage    | I <sub>OH</sub> = -16 mA          | I <sub>OH</sub> = -16 mA          |                        |     |                        | V    |

| V <sub>OL</sub> | Output LOW Voltage     | I <sub>OL</sub> = 16 mA           |                                   |                        |     | 0.25 * V <sub>DD</sub> | V    |

| I <sub>CC</sub> | Static Supply Current  | PD#/OE pin pulled to GND          |                                   |                        |     | 10                     | μA   |

| I <sub>DD</sub> | Dynamic Supply Current | Unloaded Output                   | FS = 0, @ 18 MHz                  |                        | 6   | 10                     | mA   |

|                 |                        |                                   | FS = 0, @ 24 MHz                  |                        | 7   | 12                     |      |

|                 |                        |                                   | FS = 0, @ 36 MHz                  |                        | 10  | 17                     |      |

|                 |                        |                                   | FS = 1, @ 36 MHz                  |                        | 9   | 14                     |      |

|                 |                        |                                   | FS = 1, @ 48 MHz                  |                        | 11  | 19                     |      |

|                 |                        |                                   | FS = 1, @ 72 MHz                  |                        | 16  | 28                     |      |

| Zo              | Output Impedance       |                                   | •                                 |                        | 13  |                        | Ω    |

#### Table 6. AC ELECTRICAL CHARACTERISTICS

| Parameter                            | Test Conditions                 | Min | Тур | Max | Unit |

|--------------------------------------|---------------------------------|-----|-----|-----|------|

| Input Frequency                      | FS = 0                          | 18  | 24  | 36  | MHz  |

|                                      | FS = 1                          | 36  | 48  | 72  | 1    |

| ModOUT                               | FS = 0                          | 18  | 24  | 36  | 1    |

|                                      | FS = 1                          | 36  | 48  | 72  | 1    |

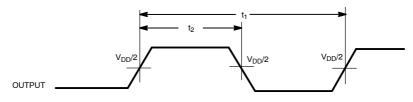

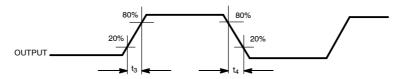

| Duty Cycle (Note 1 and 2)            | Measured at V <sub>DD</sub> / 2 | 45  | 50  | 55  | %    |

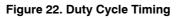

| Rise Time (Note 1 and 2)             | Measured between 20% to 80%     |     | 0.8 | 1.2 | ns   |

| Fall Time (Note 1 and 2 <sup>)</sup> | Measured between 80% to 20%     |     | 0.8 | 1.2 | ns   |

1. All parameters are specified with 15 pF loaded output.

2. Parameter is guaranteed by design and characterization. Not 100% tested in production.

### Table 6. AC ELECTRICAL CHARACTERISTICS

| Parameter                      | Test C                  | Test Conditions                                                                               |  | Тур  | Max  | Unit |

|--------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|--|------|------|------|

| Cycle-to-Cycle Jitter (Note 2) | with SSEXTR pin<br>OPEN | FS = 0, 18 MHz                                                                                |  | ±250 | ±350 | ps   |

|                                |                         | FS = 0, 24 MHz                                                                                |  | ±150 | ±225 |      |

|                                |                         | FS = 0, 36 MHz                                                                                |  | ±75  | ±125 |      |

|                                |                         | FS = 1, 36 MHz                                                                                |  | ±150 | ±200 |      |

|                                |                         | FS = 1, 48 MHz                                                                                |  | ±100 | ±150 |      |

|                                |                         | FS = 1, 72 MHz                                                                                |  | ±75  | ±125 |      |

| PLL Lock Time (Note 2)         |                         | Stable power supply, valid clock presen-<br>ted on CLKIN pin, PD# toggled from Low<br>to High |  |      | 1    | ms   |

All parameters are specified with 15 pF loaded output.

Parameter is guaranteed by design and characterization. Not 100% tested in production.

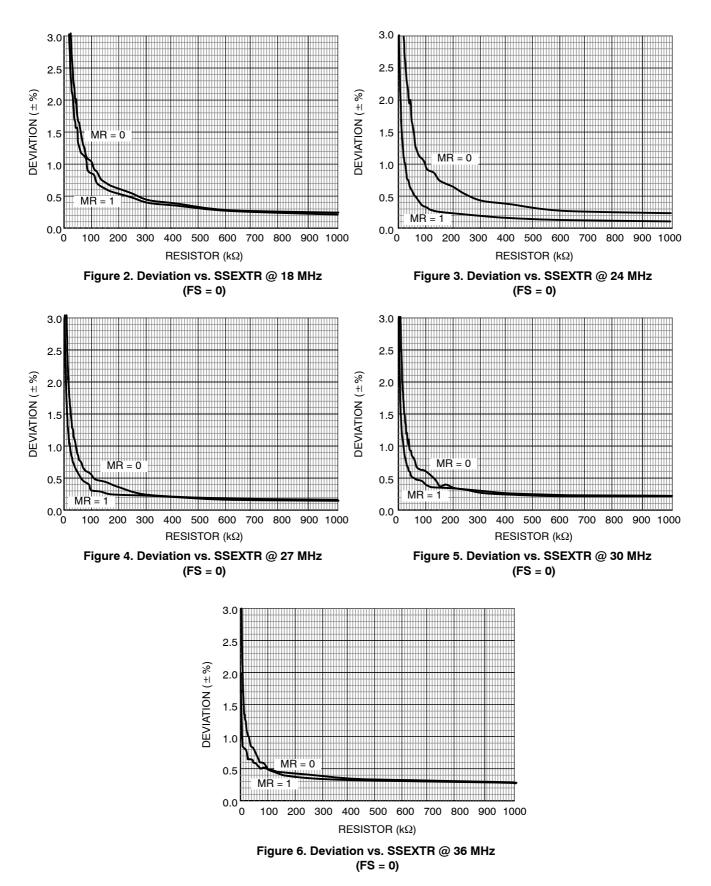

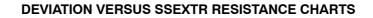

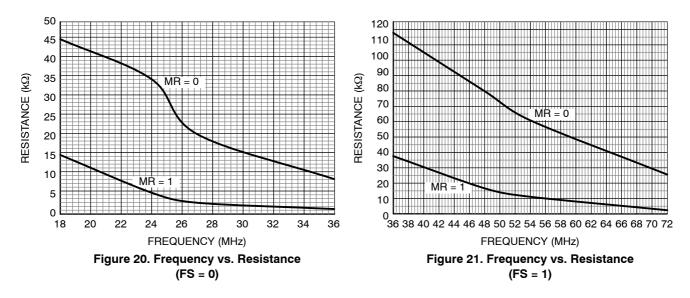

#### **DEVIATION VERSUS SSEXTR RESISTANCE CHARTS**

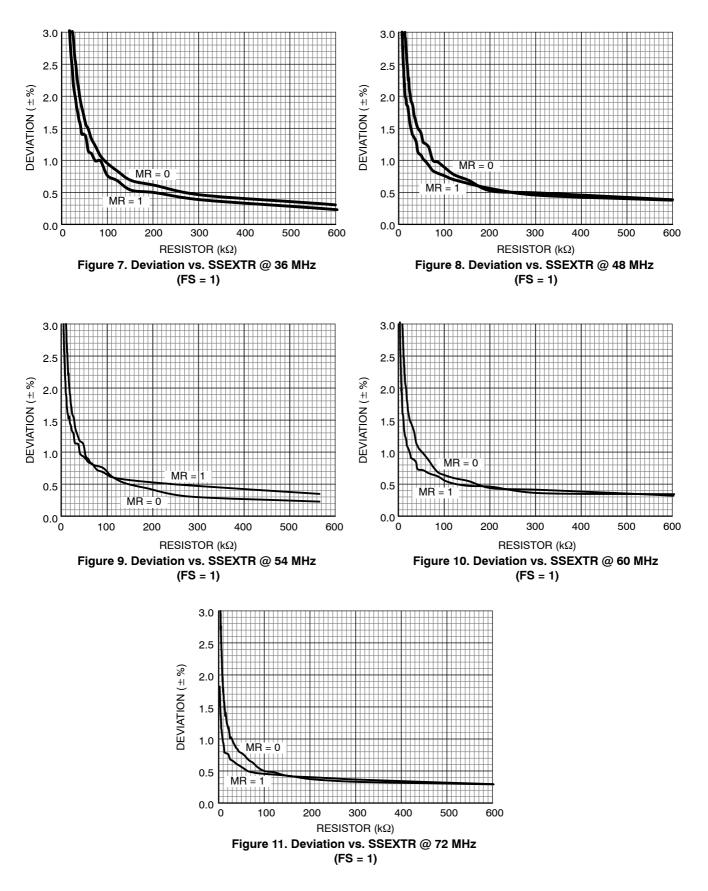

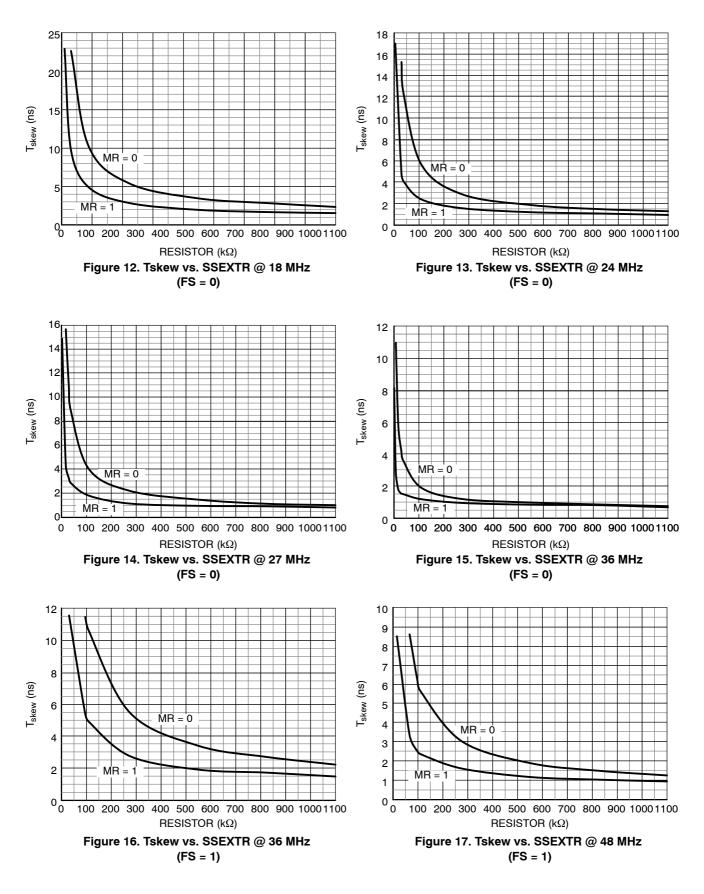

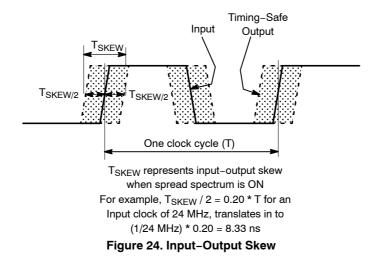

### **TSKEW VERSUS SSEXTR RESISTANCE CHARTS**

# **TSKEW VERSUS SSEXTR RESISTANCE CHARTS**

NOTE: Device-to-Device variation of Deviation and Tskew is  $\pm 10\%$

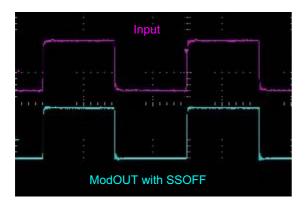

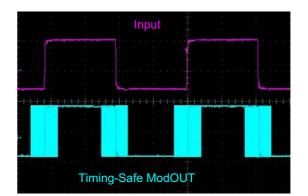

# SWITCHING WAVEFORMS

Figure 23. Output Rise/Fall Time

Figure 25. Typical Example of Timing–Safe Waveform

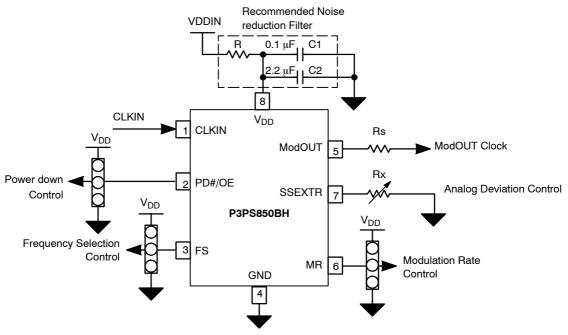

NOTE: Refer Pin Description table for Functionality details.

Figure 26. Typical Application Schematic

#### **PCB Layout Recommendation**

For optimum device performance, following guidelines are recommended.

- $\bullet~$  Dedicated  $V_{DD}$  and GND planes.

- The device must be isolated from system power supply noise. A 0.1 μF and a 2.2 μF decoupling capacitor should be mounted on the component side of the board as close to the V<sub>DD</sub> pin as possible. No vias should be used between the decoupling capacitor and V<sub>DD</sub> pin. The PCB trace to V<sub>DD</sub> pin and the ground via should be kept as short as possible. All the V<sub>DD</sub> pins should have decoupling capacitors.

- In an optimum layout all components are on the same side of the board, minimizing vias through other signal layers.

- A typical layout is shown in Figure 27.

Figure 27.

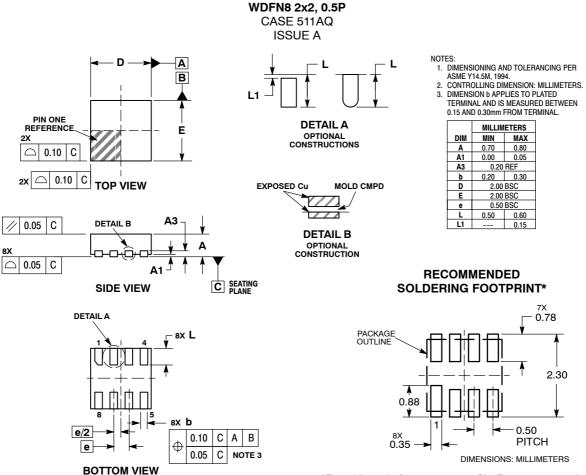

#### **ORDERING INFORMATION**

| Part Number     | Top<br>Marking | Temperature    | Package Type                                | Shipping <sup>†</sup> |

|-----------------|----------------|----------------|---------------------------------------------|-----------------------|

| P3PS850BHG-08CR | DG             | –20°C to +85°C | 8–Pin (2 mm x 2 mm) WDFN(TDFN)<br>(Pb–Free) | 3000 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*A "microdot" placed at the end of last row of marking or just below the last row toward the center of package indicates Pb-Free.

#### PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Timing-Safe is a trademark of Semiconductor Components Industries, LLC (SCILLC).

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use performance is and sole provided in an equation of personal injury or death ages court. Science and every services and expenses, and expenses, and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative