# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

## 3.3V ZERO DELAY **CLOCK BUFFER**

IDT2309A

### **FEATURES:**

- Phase-Lock Loop Clock Distribution

- 10MHz to 133MHz operating frequency

- Distributes one clock input to one bank of five and one bank of four outputs

- · Separate output enable for each output bank

- Output Skew < 250ps

- · Low jitter <200 ps cycle-to-cycle

- · IDT2309A-1 for Standard Drive

- · IDT2309A-1H for High Drive

- No external RC network required

- Operates at 3.3V VDD

- Available in SOIC and TSSOP packages

### **DESCRIPTION:**

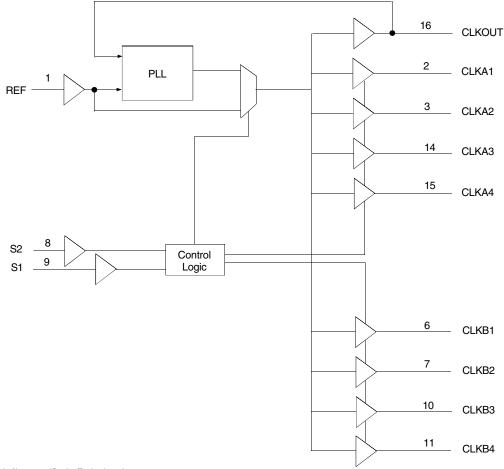

The IDT2309A is a high-speed phase-lock loop (PLL) clock buffer, designed to address high-speed clock distribution applications. The zero delay is achieved by aligning the phase between the incoming clock and the output clock, operable within the range of 10 to 133MHz.

The IDT2309A is a 16-pin version of the IDT2305A. The IDT2309A accepts one reference input, and drives two banks of four low skew clocks. The -1H version of this device operates up to 133MHz frequency and has higher drive than the -1 device. All parts have on-chip PLLs which lock to an input clock on the REF pin. The PLL feedback is on-chip and is obtained from the CLKOUT pad. In the absence of an input clock, the IDT2309A enters power down. In this mode, the device will draw less than 12µA for Commercial Temperature range and less than 25µA for Industrial temperature range, and the outputs are tri-stated.

The IDT2309A is characterized for both Industrial and Commercial operation.

### **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology. Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

**AUGUST 2012**

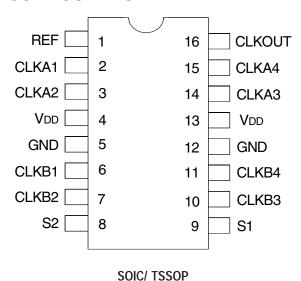

#### **PIN CONFIGURATION**

**TOP VIEW**

### **APPLICATIONS:**

- SDRAM

- Telecom

- Datacom

- PC Motherboards/Workstations

- Critical Path Delay Designs

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol                        | Rating                    | Max.         | Unit |

|-------------------------------|---------------------------|--------------|------|

| VDD                           | Supply Voltage Range      | -0.5 to +4.6 | V    |

| VI <sup>(2)</sup>             | Input Voltage Range (REF) | -0.5 to +5.5 | V    |

| Vı                            | Input Voltage Range       | -0.5 to      | V    |

|                               | (except REF)              | VDD+0.5      |      |

| IIK (VI < 0)                  | Input Clamp Current       | -50          | mA   |

| Io (Vo = 0 to VDD)            | Continuous Output Current | ±50          | mA   |

| VDD or GND                    | Continuous Current        | ±100         | mA   |

| Ta = 55°C                     | Maximum Power Dissipation | 0.7          | W    |

| (in still air) <sup>(3)</sup> |                           |              |      |

| Tstg                          | Storage Temperature Range | -65 to +150  | °C   |

| Operating                     | CommercialTemperature     | 0 to +70     | °C   |

| Temperature                   | Range                     |              |      |

| Operating                     | Industrial Temperature    | -40 to +85   | °C   |

| Temperature                   | Range                     |              |      |

#### NOTES:

- 1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

### **PIN DESCRIPTION**

| Pin Name              | Pin Number | Туре | Functional Description                       |

|-----------------------|------------|------|----------------------------------------------|

| REF                   | 1          | IN   | Input reference clock, 5 Volt tolerant input |

| CLKA1 <sup>(1)</sup>  | 2          | Out  | Output clock for bank A                      |

| CLKA2 <sup>(1)</sup>  | 3          | Out  | Output clock for bank A                      |

| V <sub>DD</sub>       | 4, 13      | PWR  | 3.3V Supply                                  |

| GND                   | 5,12       | GND  | Ground                                       |

| CLKB1 <sup>(1)</sup>  | 6          | Out  | Output clock for bank B                      |

| CLKB2 <sup>(1)</sup>  | 7          | Out  | Output clock for bank B                      |

| S2 <sup>(2)</sup>     | 8          | IN   | Select input Bit 2                           |

| S1 <sup>(2)</sup>     | 9          | IN   | Select input Bit 1                           |

| CLKB3 <sup>(1)</sup>  | 10         | Out  | Output clock for bank B                      |

| CLKB4 <sup>(1)</sup>  | 11         | Out  | Output clock for bank B                      |

| CLKA3 <sup>(1)</sup>  | 14         | Out  | Output clock for bank A                      |

| CLKA4 <sup>(1)</sup>  | 15         | Out  | Output clock for bank A                      |

| CLKOUT <sup>(1)</sup> | 16         | Out  | Output clock, internal feedback on this pin  |

#### NOTES:

- 1. Weak pull down on all outputs.

- 2. Weak pull ups on these inputs.

## **FUNCTION TABLE**(1)

| S2 | S1 | CLKA      | CLKB      | CLKOUT <sup>(2)</sup> | Output Source | PLL Shut Down |

|----|----|-----------|-----------|-----------------------|---------------|---------------|

| L  | L  | Tri-State | Tri-State | Driven                | PLL           | N             |

| L  | Н  | Driven    | Tri-State | Driven                | PLL           | N             |

| Н  | L  | Driven    | Driven    | Driven                | REF           | Υ             |

| Н  | Н  | Driven    | Driven    | Driven                | PLL           | N             |

#### NOTES:

- 1. H = HIGH Voltage Level.

- L = LOW Voltage Level

- 2. This output is driven and has an internal feedback for the PLL. The load on this output can be adjusted to change the skew between the REF and the output.

### DC ELECTRICAL CHARACTERISTICS-COMMERCIAL

| Symbol | Parameter                | Condi                      | tions                        | Min. | Max. | Unit |

|--------|--------------------------|----------------------------|------------------------------|------|------|------|

| VIL    | Input LOW Voltage Level  |                            |                              | _    | 0.8  | V    |

| VIH    | Input HIGH Voltage Level |                            |                              | 2    | _    | V    |

| lıL    | Input LOW Current        | VIN = 0V                   |                              | _    | 50   | μA   |

| Іін    | Input HIGH Current       | VIN = VDD                  |                              | _    | 100  | μΑ   |

| Vol    | Output LOW Voltage       | Standard Drive             | IoL = 8mA                    | _    | 0.4  | V    |

|        |                          | High Drive                 | IOL = 12mA (-1H)             | 1    |      |      |

| Vон    | Output HIGH Voltage      | Standard Drive             | Iон = -8mA                   | 2.4  | _    | V    |

|        |                          | High Drive                 | Iон = -12mA (-1H)            | ]    |      |      |

| IDD_PD | Power Down Current       | REF = 0MHz (S2 = S1 = H)   |                              | _    | 12   | μΑ   |

| IDD    | Supply Current           | Unloaded Outputs at 66.66M | Hz, SEL inputs at VDD or GND | _    | 32   | mA   |

### **OPERATING CONDITIONS-COMMERCIAL**

| Symbol | Parameter                                   | Min. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|

| Vdd    | Supply Voltage                              | 3    | 3.6  | V    |

| TA     | Operating Temperature (Ambient Temperature) | 0    | 70   | °C   |

| CL     | Load Capacitance < 100MHz                   | _    | 30   | pF   |

|        | Load Capacitance 100MHz - 133MHz            | _    | 10   |      |

| Cin    | Input Capacitance                           | _    | 7    | pF   |

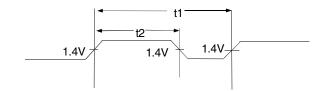

# SWITCHING CHARACTERISTICS (2309A-1) - COMMERCIAL (1,2)

| Symbol | Parameter                                                   | Conditions                                            | Min. | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı     | Output Frequency                                            | 10pF Load                                             | 10   | _    | 133  | MHz  |

|        |                                                             | 30pF Load                                             | 10   | _    | 100  |      |

|        | Duty Cycle = t2 ÷ t1                                        | Measured at 1.4V, Fout = 66.66MHz                     | 40   | 50   | 60   | %    |

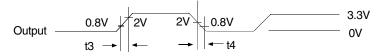

| t3     | RiseTime                                                    | Measured between 0.8V and 2V                          | _    | _    | 2.5  | ns   |

| t4     | FallTime                                                    | Measured between 0.8V and 2V                          | _    | _    | 2.5  | ns   |

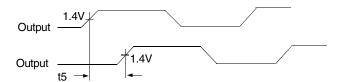

| t5     | Output to Output Skew                                       | All outputs equally loaded                            | _    | _    | 250  | ps   |

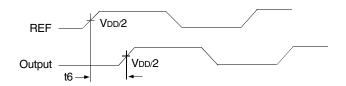

| t6A    | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

| t6B    | Delay, REF Rising Edge to CLKOUT Rising Edge <sup>(2)</sup> | Measured at VDD/2 in PLL bypass mode (IDT2309A only)  | 1    | 5    | 8.7  | ns   |

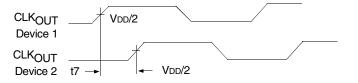

| t7     | Device-to-Device Skew                                       | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| tı     | Cycle-to-Cycle Jitter                                       | Measured at 66.66MHz, loaded outputs                  | _    | _    | 200  | ps   |

| tlock  | PLL Lock Time                                               | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

#### NOTES

- 1. REF Input has a threshold voltage of VDD/2.

- 2. All parameters specified with loaded outputs.

# SWITCHING CHARACTERISTICS (2309A-1H)-COMMERCIAL (1,2)

| Symbol | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı     | Output Frequency                             | 10pF Load                                             | 10   | _    | 133  | MHz  |

|        |                                              | 30pF Load                                             | 10   | _    | 100  |      |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT = 66.66MHz                     | 40   | 50   | 60   | %    |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, FOUT <50MHz                         | 45   | 50   | 55   | %    |

| t3     | RiseTime                                     | Measured between 0.8V and 2V                          |      | _    | 1.5  | ns   |

| t4     | Fall Time                                    | Measured between 0.8V and 2V                          |      | _    | 1.5  | ns   |

| t5     | Output to Output Skew                        | All outputs equally loaded                            | _    | _    | 250  | ps   |

| t6A    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

| t6B    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2 in PLL bypass mode (IDT2309A only)  | 1    | 5    | 8.7  | ns   |

| t7     | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| t8     | Output Slew Rate                             | Measured between 0.8V and 2V using Test Circuit 2     | 1    | _    | _    | V/ns |

| tı     | Cycle-to-Cycle Jitter                        | Measured at 66.66MHz, loaded outputs                  |      |      | 200  | ps   |

| tlock  | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

#### NOTES:

- REF Input has a threshold voltage of VDD/2.

All parameters specified with loaded outputs.

### DC ELECTRICAL CHARACTERISTICS-INDUSTRIAL

| Symbol | Parameter                | Conditi                     | ons                         | Min. | Max. | Unit |

|--------|--------------------------|-----------------------------|-----------------------------|------|------|------|

| VIL    | Input LOW Voltage Level  |                             |                             | _    | 0.8  | V    |

| VIH    | Input HIGH Voltage Level |                             |                             | 2    | _    | V    |

| lıL    | Input LOW Current        | VIN = 0V                    |                             | _    | 50   | μΑ   |

| Іін    | Input HIGH Current       | VIN = VDD                   |                             | _    | 100  | μΑ   |

| Vol    | Output LOW Voltage       | Standard Drive              | IoL = 8mA                   | _    | 0.4  | V    |

|        |                          | High Drive                  | IOL = 12mA (-1H)            |      |      |      |

| Vон    | Output HIGH Voltage      | Standard Drive              | Iон = -8mA                  | 2.4  | _    | V    |

|        |                          | High Drive                  | Iон = -12mA (-1H)           |      |      |      |

| IDD_PD | Power Down Current       | REF = 0MHz (S2 = S1 = H)    |                             | _    | 25   | μΑ   |

| IDD    | Supply Current           | Unloaded Outputs at 66.66MH | z, SEL inputs at VDD or GND | _    | 35   | mA   |

## **OPERATING CONDITIONS-INDUSTRIAL**

| Symbol | Parameter                                   | Min. | Max. | Unit |

|--------|---------------------------------------------|------|------|------|

| Vdd    | Supply Voltage                              | 3    | 3.6  | V    |

| TA     | Operating Temperature (Ambient Temperature) | -40  | +85  | °C   |

| CL     | Load Capacitance < 100MHz                   | _    | 30   | pF   |

|        | Load Capacitance 100MHz - 133MHz            | _    | 10   |      |

| CIN    | Input Capacitance                           | _    | 7    | pF   |

# SWITCHING CHARACTERISTICS (2309A-1)-INDUSTRIAL (1,2)

| Symbol | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| tı     | Output Frequency                             | 10pF Load                                             | 10   | _    | 133  | MHz  |

|        |                                              | 30pF Load                                             | 10   | _    | 100  |      |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, Fout = 66.66MHz                     | 40   | 50   | 60   | %    |

| ts     | Rise Time                                    | Measured between 0.8V and 2V                          |      | _    | 2.5  | ns   |

| t4     | FallTime                                     | Measured between 0.8V and 2V                          | _    | _    | 2.5  | ns   |

| t5     | Output to Output Skew                        | All outputs equally loaded                            | -    | _    | 250  | ps   |

| t6A    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     |      | 0    | ±350 | ps   |

| t6B    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2 in PLL bypass mode (IDT2309A only)  | 1    | 5    | 8.7  | ns   |

| t      | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | -    | 0    | 700  | ps   |

| tı     | Cycle-to-Cycle Jitter                        | Measured at 66.66MHz, loaded outputs                  |      | _    | 200  | ps   |

| tlock  | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

#### NOTES:

- 1. REF Input has a threshold voltage of  $V\mbox{DD}/2$ .

- 2. All parameters specified with loaded outputs.

## SWITCHING CHARACTERISTICS (2309A-1H)-INDUSTRIAL (1,2)

| Symbol | Parameter                                    | Conditions                                            | Min. | Тур. | Max. | Unit |

|--------|----------------------------------------------|-------------------------------------------------------|------|------|------|------|

| t1     | Output Frequency                             | 10pF Load                                             | 10   | _    | 133  | MHz  |

|        |                                              | 30pF Load                                             | 10   | _    | 100  |      |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, Fout = 66.66MHz                     | 40   | 50   | 60   | %    |

|        | Duty Cycle = t2 ÷ t1                         | Measured at 1.4V, Fout <50MHz                         | 45   | 50   | 55   | %    |

| t3     | RiseTime                                     | Measured between 0.8V and 2V                          | _    | _    | 1.5  | ns   |

| t4     | FallTime                                     | Measured between 0.8V and 2V                          | _    | _    | 1.5  | ns   |

| t5     | Output to Output Skew                        | All outputs equally loaded                            | _    | _    | 250  | ps   |

| t6A    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2                                     | _    | 0    | ±350 | ps   |

| t6B    | Delay, REF Rising Edge to CLKOUT Rising Edge | Measured at VDD/2 in PLL bypass mode (IDT2309A only)  | 1    | 5    | 8.7  | ns   |

| t7     | Device-to-Device Skew                        | Measured at VDD/2 on the CLKOUT pins of devices       | _    | 0    | 700  | ps   |

| t8     | Output Slew Rate                             | Measured between 0.8V and 2V using Test Circuit 2     | 1    | _    | _    | V/ns |

| tı     | Cycle-to-Cycle Jitter                        | Measured at 66.66MHz, loaded outputs                  | _    | _    | 200  | ps   |

| tlock  | PLL Lock Time                                | Stable power supply, valid clock presented on REF pin | _    | _    | 1    | ms   |

#### NOTES:

- 1. REF Input has a threshold voltage of VDD/2.

- 2. All parameters specified with loaded outputs.

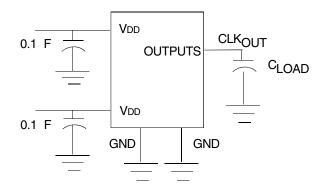

#### ZERO DELAY AND SKEW CONTROL

All outputs should be uniformly loaded in order to achieve Zero I/O Delay. Since the CLKOUT pin is the internal feedback for the PLL, its relative loading can affect and adjust the input/output delay. The Output Load Difference diagram illustrates the PLL's relative loading with respect to the other outputs that can adjust the Input-Output (I/O) Delay.

For designs utilizing zero I/O Delay, all outputs including CLKOUT must be equally loaded. Even if the output is not used, it must have a capacitive load equal to that on the other outputs in order to obtain true zero I/O Delay. For zero output-to-output skew, all outputs must be loaded equally.

### **SWITCHING WAVEFORMS**

**Duty Cycle Timing**

All Outputs Rise/Fall Time

Output to Output Skew

Input to Output Propagation Delay

Device to Device Skew

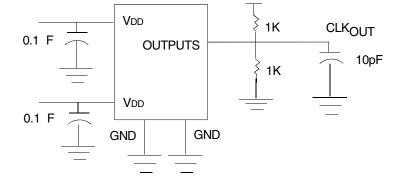

# **TEST CIRCUITS**

Test Circuit 1 (all Parameters Except t8)

Test Circuit 2 (t8, Output Slew Rate On -1H Devices)

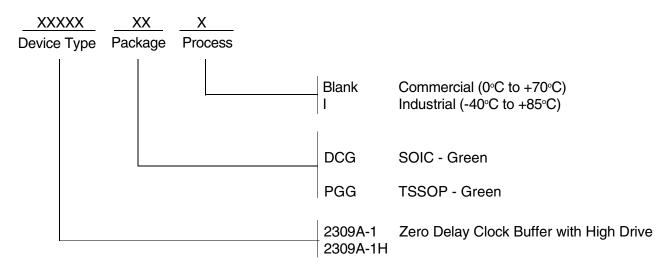

### **ORDERING INFORMATION**

| Ordering Code | Package Type | Operating Range |

|---------------|--------------|-----------------|

|               |              |                 |

| 2309A-1DCG    | 16-Pin SOIC  | Commercial      |

| 2309A-1DCGI   | 16-Pin SOIC  | Industrial      |

|               |              |                 |

| 2309A-1HDCG   | 16-Pin SOIC  | Commercial      |

| 2309A-1HDCGI  | 16-Pin SOIC  | Industrial      |

| 2309A-1HPGG   | 16-Pin TSSOP | Commercial      |

| 2309A-1HPGGI  | 16-Pin TSSOP | Industrial      |