## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

## ASSP Dual Serial Input PLL Frequency Synthesizer Datasheet

### **Description**

The Cypress Semiconductor MB15F73UL is a serial input Phase Locked Loop (PLL) frequency synthesizer with a 2250 MHz and a 600-MHz prescalers. A 64/65 or a 128/129 for the 2250-MHz prescaler, and a 8/9 or a 16/17 for the 600 MHz prescaler can be selected for the prescaler that enables pulse swallow operation.

The BiCMOS process is used, as a result a supply current is typically 3.2 mA at 2.7 V. The supply voltage range is from 2.4 V to 3.6 V. A refined charge pump supplies well-balanced output current with 1.5 mA and 6 mA selectable by serial date. The data format is the same as the previous one MB15F03SL and MB15F73SP. Fast locking is achieved for adopting the new circuit.

### **Features**

- High frequency operation

- ☐ RF synthesizer: 2250 MHz Max☐ IF synthesizer: 600 MHz Max☐

- Low power supply voltage: Vcc = 2.4 V to 3.6 V

- Ultra low power supply current: lcc = 3.2 mA Typ (Vcc = Vp = 2.7 V, SW<sub>IF</sub> = SW<sub>RF</sub> = 0, Ta = +25 °C, in IF, RF locking state)

- Direct power saving function: Power supply current in power saving mode

- $\Box$  Typ 0.1 μA (V<sub>CC</sub> = Vp = 2.7 V, Ta = +25 °C)  $\Box$  Max 10 μA (V<sub>CC</sub> = Vp = 2.7 V)

- Software selectable charge pump current: 1.5 mA/6.0 mA Typ

- Dual modulus prescaler: 2250-MHz prescaler (64/65 or 128/129) /600 MHz prescaler (8/9 or 16/17)

- 23-bit shift register

- Serial input binary 14-bit programmable reference divider: R = 3 to 16,383

- Serial input programmable divider consisting of:

Binary 7-bit swallow counter: 0 to 127

Binary 11-bit programmable counter: 3 to 2,047

- Built-in high-speed tuning, low-noise phase comparator,

- current-switching type constant current circuit

- $\blacksquare$  On-chip phase control for phase comparator

- On-chip phase comparator for fast lock and low noise

- Built-in digital locking detector circuit to detect PLL locking and unlocking.

- Operating temperature: Ta = -40 °C to +85 °C

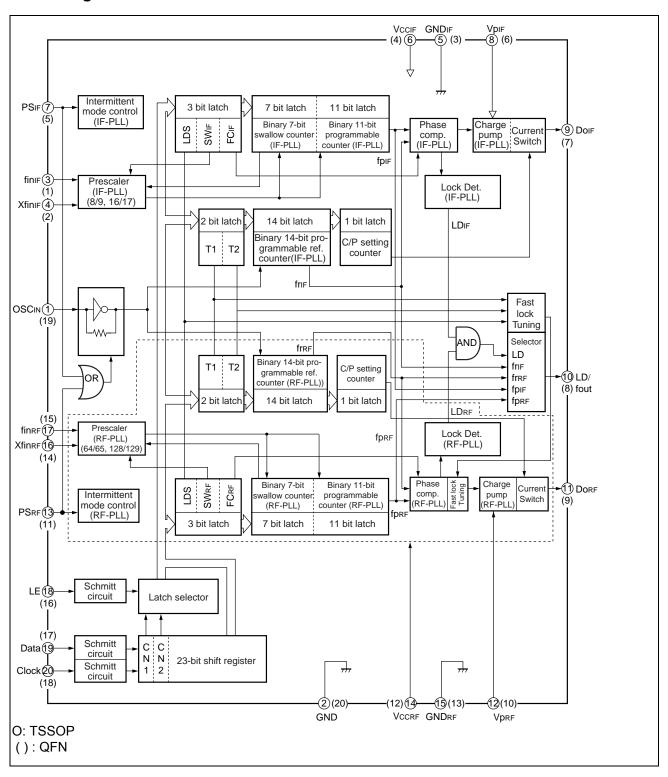

### **Block Diagram**

### MB15F73UL

### **Contents**

| Pin Assignments                               | 4  |

|-----------------------------------------------|----|

| Pin Description                               | 5  |

| Absolute Maximum Ratings                      | 6  |

| Recommended Operating Conditions              | 6  |

| Electrical Characteristics                    | 7  |

| Functional Description                        |    |

| Pulse swallow function                        | g  |

| Serial Data Input                             | g  |

| Shift Register Configuration                  |    |

| Data setting                                  | 10 |

| Power Saving Mode (Intermittent Mode          |    |

| Control Circuit)                              | 12 |

| Serial Data Input Timing                      | 13 |

| Phase Comparator Output Waveform              | 14 |

| LD Output Logic                               | 14 |

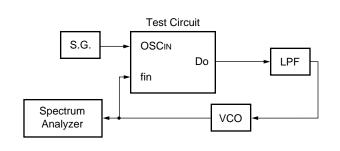

| Test Circuit (for Measuring Input Sensitivity |    |

| fin/OSCIN)                                    | 15 |

| Typical Characteristics                       | 16 |

| Fin Input Sensitivity                         | 16 |

| OSCIN input sensitivity                       | 17 |

| RF-PLL Do output current                             | 10     |

|------------------------------------------------------|--------|

| IF-PLL Do output current                             | 19     |

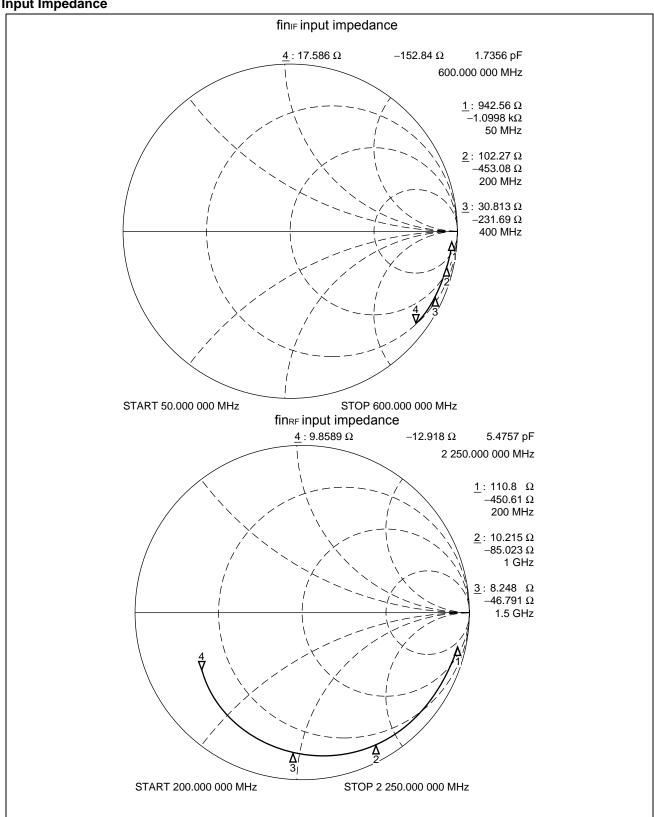

| fin input impedance                                  | 20     |

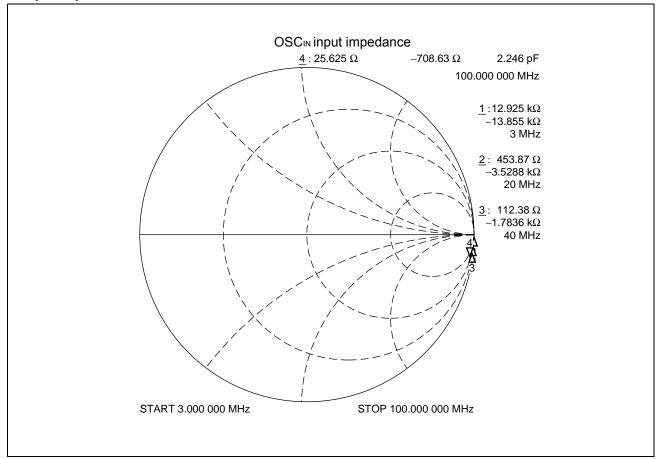

| OSCIN input impedance                                | 21     |

| Reference Information (for Lock-up Time, Phase Noise | e, and |

| Reference Leakage)                                   | 22     |

| Application Example                                  |        |

| Usage Precautions                                    | 25     |

| Ordering Information                                 |        |

| Package Dimensions                                   | 26     |

| Document History Page                                | 28     |

| Sales, Solutions, and Legal Information              | 29     |

| Worldwide Sales and Design Support                   | 29     |

| Products                                             | 29     |

| PSoC® Solutions                                      | 29     |

| Cypress Developer Community                          | 29     |

| Technical Support                                    |        |

|                                                      |        |

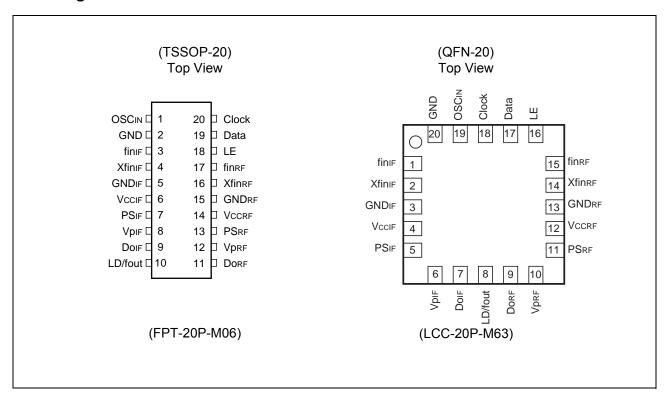

### **Pin Assignments**

### **Pin Description**

| Pin r | 10. |                   |     |                                                                                                                                                                                                                                 |

|-------|-----|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | QFN | Pin name          | 1/0 | Descriptions                                                                                                                                                                                                                    |

| 1     | 19  | OSCIN             | ı   | The programmable reference divider input pin. TCXO should be connected with an AC coupling capacitor.                                                                                                                           |

| 2     | 20  | GND               | _   | Ground pin for OSC input buffer and the shift register circuit.                                                                                                                                                                 |

| 3     | 1   | fin⊩              | I   | Prescaler input pin for the IF-PLL. Connection to an external VCO should be via AC coupling.                                                                                                                                    |

| 4     | 2   | Xfin⊩             | I   | Prescaler complimentary input for the IF-PLL section. This pin should be grounded via a capacitor.                                                                                                                              |

| 5     | 3   | GND <sub>IF</sub> | _   | Ground pin for the IF-PLL section.                                                                                                                                                                                              |

| 6     | 4   | Vccif             | -   | Power supply voltage input pin for the IF-PLL section (except for the charge pump circuit), the shift register, and the oscillator input buffer.                                                                                |

| 7     | 5   | PS⊩               | I   | Power saving mode control for the IF-PLL section. This pin must be set at "L" when the power supply is started up. (Open is prohibited.) $PS_{IF} = "H"$ ; Normal mode / $PS_{IF} = "L"$ ; Power saving mode                    |

| 8     | 6   | VpiF              | _   | Power supply voltage input pin for the IF-PLL charge pump.                                                                                                                                                                      |

| 9     | 7   | Doif              | 0   | Charge pump output for the IF-PLL section.                                                                                                                                                                                      |

| 10    | 8   | LD/fout           | 0   | Lock detect signal output (LD) /phase comparator monitoring output (fout) pin.The output signal is selected by LDS bit in the serial data. LDS bit = "H"; outputs fout signal / LDS bit = "L"; outputs LD signal                |

| 11    | 9   | Dorf              | 0   | Charge pump output for the RF-PLL section.                                                                                                                                                                                      |

| 12    | 10  | Vprf              | _   | Power supply voltage input pin for the RF-PLL charge pump.                                                                                                                                                                      |

| 13    | 11  | PS <sub>RF</sub>  | I   | Power saving mode control for the RF-PLL section. This pin must be set at "L" when the power supply is started up. (Open is prohibited.)  PSRF = "H"; Normal mode / PSRF = "L"; Power saving mode                               |

| 14    | 12  | Vccrf             | _   | Power supply voltage input pin for the RF-PLL section (except for the charge pump circuit)                                                                                                                                      |

| 15    | 13  | GNDrf             | _   | Ground pin for the RF-PLL section                                                                                                                                                                                               |

| 16    | 14  | Xfinrf            | I   | Prescaler complimentary input pin for the RF-PLL section. This pin should be grounded via a capacitor.                                                                                                                          |

| 17    | 15  | finrf             | I   | Prescaler input pin for the RF-PLL. Connection to an external VCO should be via AC coupling.                                                                                                                                    |

| 18    | 16  | LE                | I   | Load enable signal input pin (with the schmitt trigger circuit) When LE is set "H", data in the shift register is transferred to the corresponding latch according to the control bit in the serial data.                       |

| 19    | 17  | Data              | I   | Serial data input pin (with the schmitt trigger circuit) Data is transferred to the corresponding latch (IF-ref. counter, IF-prog. counter, RF-ref. counter, RF-prog. counter) according to the control bit in the serial data. |

| 20    | 18  | Clock             | I   | Clock input pin for the 23-bit shift register (with the schmitt trigger circuit) One bit of data is shifted into the shift register on a rising edge of the clock.                                                              |

### **Absolute Maximum Ratings**

| Parame               | tor        | Symbol          | Rat        | ing     | Unit  |

|----------------------|------------|-----------------|------------|---------|-------|

| raiaille             | itei       | Symbol          | Min        | Max     | Offic |

| Power supply voltage |            | Vcc             | -0.5       | +4.0    | V     |

|                      |            | Vp              | Vcc        | 4.0     | V     |

| Input voltage        |            | Vı              | -0.5       | Vcc+0.5 | V     |

| Output voltage       | LD/fout    | Vo              | GND        | Vcc     | V     |

|                      | Doif, Dorf | V <sub>DO</sub> | GND        | Vp      | V     |

| Storage temperature  | •          | Tstg            | <b>-55</b> | +125    | °C    |

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### **Recommended Operating Conditions**

| Parameter             | Symbol |     | Value |     | Unit | Remarks       |

|-----------------------|--------|-----|-------|-----|------|---------------|

| Farameter             | Symbol | Min | Тур   | Max | Onit | Remarks       |

| Power supply voltage  | Vcc    | 2.4 | 2.7   | 3.6 | V    | Vccrf = Vccif |

|                       | Vp     | Vcc | 2.7   | 3.6 | V    |               |

| Input voltage         | Vı     | GND | -     | Vcc | V    |               |

| Operating temperature | Та     | -40 | _     | +85 | °C   |               |

Note: ■ VccrF, VprF, VcciF and VpiF must supply equal voltage.

Even if either RF-PLL or IF-PLL is not used, power must be supplied to VCCRF, VPRF, VCCIF and VPIF to keep them equal. It is recommended that the non-use PLL is controlled by power saving function.

- ■Although this device contains an anti-static element to prevent electrostatic breakdown and the circuitry has been improved in electrostatic protection, observe the following precautions when handling the device.

- □ When storing and transporting the device, put it in a conductive case.

- □ Before handling the device, confirm the (jigs and) tools to be used have been uncharged (grounded) as well as yourself. Use a conductive sheet on working bench.

- □ Before fitting the device into or removing it from the socket, turn the power supply off.

- □ When handling (such as transporting) the device mounted board, protect the leads with a conductive sheet.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges.

Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the datasheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

Document Number: 002-08480 Rev. \*A

### **Electrical Characteristics**

$(V_{CC} = 2.4 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

|                               |                                                            |                            |                                                                              | (100 2.1110  |         |               | 1                           |

|-------------------------------|------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------|--------------|---------|---------------|-----------------------------|

| Parameter                     |                                                            | Symbol                     | Condition                                                                    |              | Value   |               | Unit                        |

| T di diliotoi                 |                                                            | Cymber                     | Containon                                                                    | Min          | Тур     | Max           | 0                           |

| Power supply current          |                                                            | IcciF <sup>[1]</sup>       | fin <sub>IF</sub> = 480 MHz<br>V <sub>CCIF</sub> = V <sub>DIF</sub> = 2.7 V  | 0.8          | 1.2     | 1.7           | mA                          |

|                               |                                                            | Iccrf <sup>[1]</sup>       | fin <sub>RF</sub> = 2000 MHz<br>V <sub>CCRF</sub> = V <sub>PRF</sub> = 2.7 V | 1.3          | 2.0     | 2.8           | mA                          |

| Power saving current          |                                                            | IPSIF                      | PS <sub>IF</sub> = PS <sub>RF</sub> = "L"                                    | _            | 0.1[2]  | 10            | μΑ                          |

|                               |                                                            | IPSRF                      | PS <sub>IF</sub> = PS <sub>RF</sub> = "L"                                    | _            | 0.1 [2] | 10            | μΑ                          |

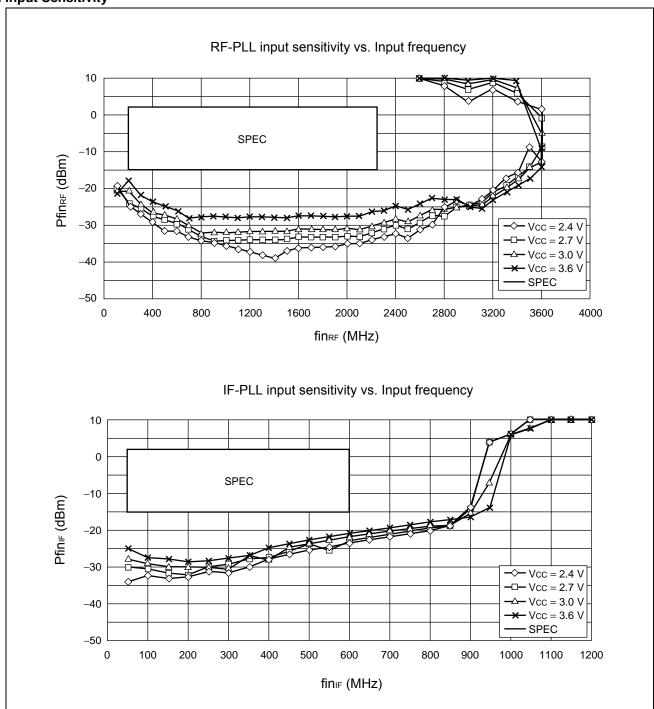

| Operating frequency           | fin <sub>IF</sub> [3]                                      | finı⊧                      | IF PLL                                                                       | 50           | _       | 600           | MHz                         |

|                               | fin <sub>RF</sub> [3]                                      | fin <sub>RF</sub>          | RF PLL                                                                       | 200          | _       | 2250          | MHz                         |

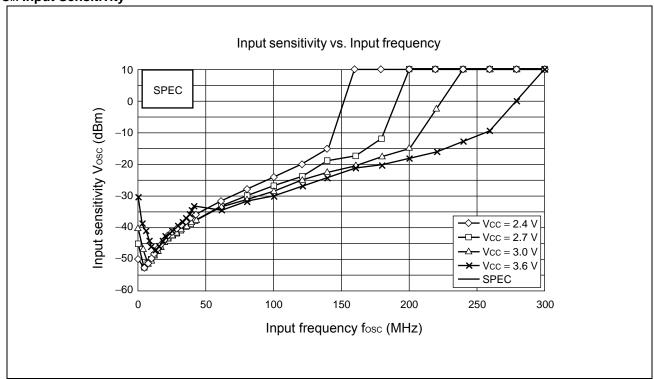

|                               | OSCIN                                                      | fosc                       | _                                                                            | 3            | _       | 40            | MHz                         |

| Input sensitivity             | fin⊩                                                       | Pfin⊩                      | IF PLL, 50 Ω system                                                          | -15          | _       | +2            | dBm                         |

|                               | fin <sub>RF</sub>                                          | Pfinre                     | RF PLL, 50 Ω system                                                          | -15          | _       | +2            | dBm                         |

|                               | OSCIN                                                      | Vosc                       | _                                                                            | 0.5          | _       | Vcc           | V <sub>P</sub> <sub>P</sub> |

| "H" level input voltage       | Data, LE,<br>Clock                                         | Vін                        | Schmitt trigger input                                                        | 0.7 Vcc +0.4 | _       | -             | V                           |

| "L" level input voltage       |                                                            | VIL                        | Schmitt trigger input                                                        | -            | _       | 0.3 Vcc – 0.4 | V                           |

| "H" level input voltage       | PS <sub>IF</sub> , PS <sub>RF</sub>                        | VIH                        | _                                                                            | 0.7 Vcc      | _       | _             | V                           |

| "L" level input voltage       |                                                            | VIL                        | _                                                                            | _            | _       | 0.3 Vcc       | V                           |

| "H" level input current       | Data, LE,<br>Clock, PS <sub>IF</sub> ,<br>PS <sub>RF</sub> | I <sub>IH</sub> [4]        | _                                                                            | -1.0         | -       | +1.0          | μА                          |

| "L" level input current       |                                                            | I <sub>IL</sub> [4]        | _                                                                            | -1.0         | -       | +1.0          | μΑ                          |

| "H" level input current       | OSCIN                                                      | Іін                        | _                                                                            | 0            | _       | +100          | μΑ                          |

| "L" level input current       | 1                                                          | <sub>IL</sub> [4]          | _                                                                            | -100         | _       | 0             | μΑ                          |

| "H" level output voltage      | LD/fout                                                    | Vон                        | Vcc = Vp = 2.7 V,<br>Iон = -1 mA                                             | Vcc-0.4      | _       | _             | V                           |

| "L" level output voltage      |                                                            | Vol                        | Vcc = Vp = 2.7 V,<br>lo <sub>L</sub> = 1 mA                                  | -            | _       | 0.4           | V                           |

| "H" level output voltage      | Doif,<br>Dorf                                              | V <sub>DOH</sub>           | Vcc = Vp = 2.7 V,<br>Ідон = -0.5 mA                                          | Vp – 0.4     | _       | _             | V                           |

| "L" level output voltage      |                                                            | V <sub>DOL</sub>           | Vcc = Vp = 2.7 V,<br>IDDL = 0.5 mA                                           | -            | -       | 0.4           | V                           |

| High impedance cutoff current | Doif,<br>Dorf                                              | loff                       | V <sub>CC</sub> = Vp = 2.7 V<br>V <sub>OFF</sub> = 0.5 V to Vp — 0.5 V       | _            | -       | 2.5           | nA                          |

| "H" level output current      | LD/fout                                                    | <b>І</b> он <sup>[4]</sup> | Vcc = Vp = 2.7 V                                                             | _            | _       | -1.0          | mA                          |

| "L" level output current      | 1                                                          | loL                        | Vcc = Vp = 2.7 V                                                             | 1.0          | _       | _             | mA                          |

- 1. Conditions; fosc = 12.8 MHz, Ta = +25 °C, SW = "L" in locking state.

2. V<sub>CCIF</sub> = V<sub>DIF</sub> = V<sub>CCIF</sub> = V<sub>PIF</sub> = 2.7 V, fosc = 12.8 MHz, Ta = +25 °C, in power saving mode PS<sub>IF</sub> = PS<sub>RF</sub> = GND, V<sub>IH</sub> = V<sub>CC</sub>, V<sub>IL</sub> = GND (at CLK, Data, LE).

3. AC coupling. 1000 pF capacitor is connected under the condition of minimum operating frequency.

4. The symbol "-" (minus) means the direction of current flow.

$(V_{CC} = 2.4 \text{ V to } 3.6 \text{ V}, \text{ Ta} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$

| Paramete                 | -                             | Symbol                      | Cond                                              | ition        |      | Value |      | Unit |

|--------------------------|-------------------------------|-----------------------------|---------------------------------------------------|--------------|------|-------|------|------|

| Faramete                 | '                             | Syllibol                    | Cond                                              | ition        | Min  | Тур   | Max  | Onit |

| "H" level output current | Doif <sup>[5]</sup> ,<br>Dorf | <b>I</b> DOH <sup>[4]</sup> | $V_{CC} = Vp = 2.7 V,$<br>$V_{DOH} = Vp / 2,$     | CS bit = "H" | -8.2 | -6.0  | -4.1 | mA   |

|                          |                               |                             | Ta = +25 °C                                       | CS bit = "L" | -2.2 | -1.5  | -0.8 | mA   |

| "L" level output current | Doif <sup>[5]</sup> ,<br>Dorf | Ірог                        | $V_{CC} = Vp = 2.7 V,$<br>$V_{DOL} = Vp / 2,$     | CS bit = "H" | 4.1  | 6.0   | 8.2  | mA   |

|                          |                               |                             | Ta = +25 °C                                       | CS bit = "L" | 0.8  | 1.5   | 2.2  | mA   |

| Charge pump              | Idol/Idoh                     | I <sub>DOMT</sub> [6]       | V <sub>DO</sub> = Vp / 2                          | •            | _    | 3     | _    | %    |

| current rate             | vs. V <sub>DO</sub>           | I <sub>DOVD</sub> [7]       | $0.5 \text{ V} \le \text{V}_{DO} \le \text{Vp} -$ | 0.5 V        | _    | 10    | -    | %    |

|                          | vs.Ta                         | I <sub>DOTA</sub> [8]       | -40 °C ≤ Ta ≤ +85<br>V <sub>DO</sub> = Vp / 2     | °C,          | _    | 5     | -    | %    |

#### Notes

- Notes

5. When Charge pump current is measured, set LDS = "L" T1 = "L" and T2 = "H".

6. Vcc = Vp = 2.7 V, Ta = +25 °C (|||s| ||s||) / [(||s| + ||s||) / 2] × 100 (%).

7. Vcc = Vp = 2.7 V, Ta = +25 °C [(|||s| ||s||) / 2] / [(||s| + ||s||) / 2] × 100 (%); (Applied to both looL and looH).

8. Vcc = Vp = 2.7 V, [||||DD (+85 °C)| ||DD (+40 °C)| / 2] × 100 (%) (Applied to both looL and looH).

### **Functional Description**

#### **Pulse Swallow Function**

- $\blacksquare$  fvco = [ (P X N) + A] X fosc  $\div$  R

- $\hfill \ensuremath{\square}$  fvco : Output frequency of external voltage controlled oscillator (VCO)

- □ P : Preset divide ratio of dual modulus prescaler (8 or 16 for IF-PLL, 64 or 128 for RF-PLL)

- □ N : Preset divide ratio of binary 11-bit programmable counter (3 to 2,047)

- ightharpoonup A : Preset divide ratio of binary 7-bit swallow counter (0 ≤ A ≤ 127, A < N)

- $\hfill \ensuremath{\square}$  fosc : Reference oscillation frequency (OSC  $_{\ensuremath{\square}}$  input frequency)

- □ R : Preset divide ratio of binary 14-bit programmable reference counter (3 to 16,383)

### **Serial Data Input**

The serial data is entered using three pins, Data pin, Clock pin, and LE pin. Programmable dividers of IF/RF-PLL sections, and programmable reference dividers of IF/RF-PLL sections are controlled individually.

The serial data of binary data is entered through Data pin.

On a rising edge of Clock, one bit of the serial data is transferred into the shift register. On a rising edge of load enable signal, the data stored in the shift register is transferred to one of latches depending upon the control bit data setting.

|     | The programmable reference counter for the IF-PLL |   | The programmable counter and the swallow counter for the IF-PLL |   |

|-----|---------------------------------------------------|---|-----------------------------------------------------------------|---|

| CN1 | 0                                                 | 1 | 0                                                               | 1 |

| CN2 | 0                                                 | 0 | 1                                                               | 1 |

### **Shift Register Configuration**

| 1   | 2   | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14  | 15  | 16  | 17  | 18  | 19 | 20 | 21 | 22 | 23 |

|-----|-----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|----|----|----|----|----|

| CN1 | CN2 | T1 | T2 | R1 | R2 | R3 | R4 | R5 | R6 | R7 | R8 | R9 | R10 | R11 | R12 | R13 | R14 | CS | Χ  | Χ  | Χ  | Χ  |

CS : Charge pump current select bit

R1 to R14 : Divide ratio setting bits for the programmable reference counter (3 to 16,383)

T1, T2 : LD/fout output setting bit.

CN1, CN2 : Control bit

X : Dummy bits (Set "0" or "1")

Note: Data input with MSB first.

- (LSB) Data Flow ——► (MSB)

| 1   | 2   | 3   | 4                | 5                  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22  | 23  |

|-----|-----|-----|------------------|--------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|

| CN1 | CN2 | LDS | SW <sub>IF</sub> | FC <sub>IF</sub> / | A1 | A2 | A3 | A4 | A5 | A6 | A7 | N1 | N2 | N3 | N4 | N5 | N6 | N7 | N8 | N9 | N10 | N11 |

A1 to A7 : Divide ratio setting bits for the swallow counter (0 to 127)

N1 to N11 : Divide ratio setting bits for the programmable counter (3 to 2,047)

LDS : LD/fout signal select bit

$\begin{array}{ll} SW_{IF}/RF & : Divide \ ratio \ setting \ bit \ for \ the \ prescaler \ (IF:SW_{IF}, RF:SW_{RF}) \\ FC_{IF}/RF & : Phase \ control \ bit \ for \ the \ phase \ detector \ (IF:FC_{IF}, RF:FC_{RF}) \\ \end{array}$

CN1, CN2 : Control bit

Note: : Data input with MSB first.

### **Data Setting**

■ Binary 14-bit Programmable Reference Counter Data Setting (R1 to R14)

| Divide ratio | R14         | R13 | R12 | R11         | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 |

|--------------|-------------|-----|-----|-------------|-----|----|----|----|----|----|----|----|----|----|

| 3            | 0           | 0   | 0   | 0           | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4            | 0           | 0   | 0   | 0           | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 16383        | •<br>•<br>1 | 1   | 1   | •<br>•<br>1 | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note: Divide ratio less than 3 is prohibited.

■ Binary 11-bit Programmable Counter Data Setting (N1 to N11)

| Divide ratio | N11 | N10 | N9 | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 |

|--------------|-----|-----|----|----|----|----|----|----|----|----|----|

| 3            | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4            | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| 2047         | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

Note: : Divide ratio less than 3 is prohibited.

■ Binary 7-bit Swallow Counter Data Setting (A1 to A7)

| Divide ratio | A7 | A6 | A5 | A4 | А3 | A2 | A1 |

|--------------|----|----|----|----|----|----|----|

| 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| 1            | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

|              |    |    |    |    |    |    |    |

| 127          | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

### ■ Prescaler Data Setting (SW)

| Divide ratio                  | SW = "H" | SW = "L" |

|-------------------------------|----------|----------|

| Prescaler divide ratio IF-PLL | 8/9      | 16/17    |

| Prescaler divide ratio RF-PLL | 64/65    | 128/129  |

### ■ Charge Pump Current Setting (CS)

| Current value | CS |

|---------------|----|

| ±6.0 mA       | 1  |

| ±1.5 mA       | 0  |

### ■ LD/fout output Selectable Bit Setting

| LD/fout Pin State |                  | LDS | T1 | T2 |

|-------------------|------------------|-----|----|----|

| LD output         |                  | 0   | 0  | 0  |

|                   |                  |     | 1  | 0  |

|                   |                  |     | 1  | 1  |

| fout              | fr⊫              | 1   | 0  | 0  |

| outputs           | fr <sub>RF</sub> | 1   | 1  | 0  |

|                   | fpı⊧             | 1   | 0  | 1  |

|                   | fpref            | 1   | 1  | 1  |

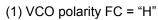

### ■ Phase Comparator Phase Switching Data Setting (FC<sub>IF</sub>, FC<sub>RF</sub>)

| Phase comparator input  | FC <sub>IF</sub> = "H" | FCRF = "H" | FC <sub>IF</sub> = "L" | FCRF = "L" |

|-------------------------|------------------------|------------|------------------------|------------|

| r nase comparator input | Doir                   | Dorf       | Doir                   | Dorf       |

| fr > fp                 | H                      |            | L                      | =          |

| fr < fp                 | L                      |            | ŀ                      | 1          |

| fr = fp                 |                        | 7          | Z                      | 7          |

### Z : High-impedance

Depending upon the VCO and LPF polarity, FC bit should be set.

Note: Give attention to the polarity for using active type LPF.

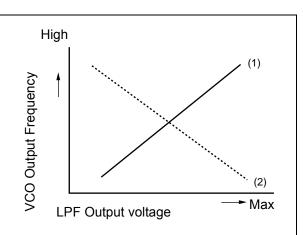

#### **Power Saving Mode (Intermittent Mode Control Circuit)**

| Status            | PS pins |

|-------------------|---------|

| Normal mode       | Н       |

| Power saving mode | L       |

The intermittent mode control circuit reduces the PLL power consumption.

By setting the PS pin low, the device enters into the power saving mode, reducing the current consumption. See the Electrical Characteristics chart for the specific value.

The phase detector output, Do, becomes high impedance.

For the dual PLL, the lock detector, LD, is as shown in the LD Output Logic table.

Setting the PS pin high, releases the power saving mode, and the device works normally.

The intermittent mode control circuit also ensures a smooth startup when the device returns to normal operation. When the PLL is returned to normal operation, the phase comparator output signal is unpredictable. This is because of the unknown relationship between the comparison frequency (fp) and the reference frequency (fr) which can cause a major change in the comparator output, resulting in a VCO frequency jump and an increase in lockup time.

To prevent a major VCO frequency jump, the intermittent mode control circuit limits the magnitude of the error signal from the phase detector when it returns to normal operation.

Notes: ■ When power (Vcc) is first applied, the device must be in standby mode, PS = Low, for at least 1 µs.

■ PS pins must be set at "L" at Power-ON.

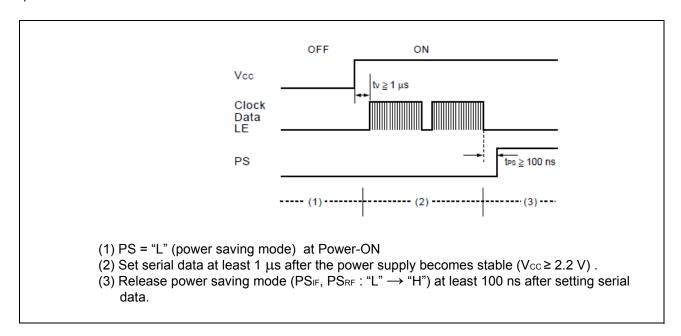

### **Serial Data Input Timing**

Divide ratio is performed through a serial interface using the Data pin, Clock pin, and LE pin.

Setting data is read into the shift register at the rise of the clock signal, and transferred to a latch at the rise of the LE signal. The

| Parameter      | Min | Тур | Max | Unit |

|----------------|-----|-----|-----|------|

| <b>t</b> 1     | 20  | -   | _   | ns   |

| <b>t</b> 2     | 20  | -   | -   | ns   |

| <b>t</b> 3     | 30  | -   | _   | ns   |

| t <sub>4</sub> | 30  | _   | _   | ns   |

| Parameter      | Min | Тур | Max | Unit |

|----------------|-----|-----|-----|------|

| <b>t</b> 5     | 100 | _   | _   | ns   |

| t <sub>6</sub> | 20  | _   | -   | ns   |

| t <sub>7</sub> | 100 | _   | _   | ns   |

Note: LE should be "L" when the data is transferred into the shift register.

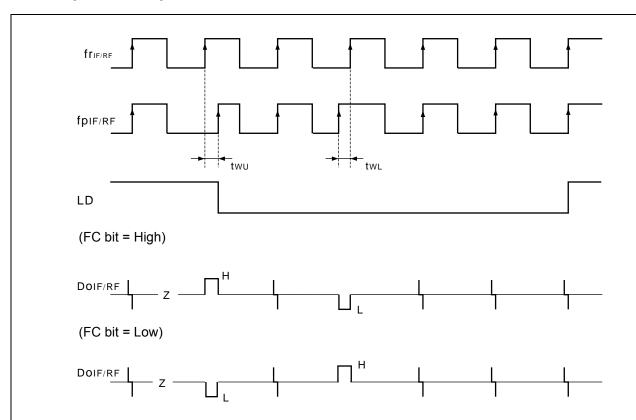

### **Phase Comparator Output Waveform**

### **LD Output Logic**

| IF-PLL section                   | RF-PLL section                   | LD output |

|----------------------------------|----------------------------------|-----------|

| Locking state/Power saving state | Locking state/Power saving state | Н         |

| Locking state/Power saving state | Unlocking state                  | L         |

| Unlocking state                  | Locking state/Power saving state | L         |

| Unlocking state                  | Unlocking state                  | L         |

Note: • Phase error detection range =  $-2\pi$  to  $+2\pi$

- Pulses on DoiF/RF signals are output to prevent dead zone.

- LD output becomes low when phase error is two or more.

- LD output becomes high when phase error is twL or less and continues to be so for three cycles or more.

- two and two depend on OSCIN input frequency as follows.

twu≥ 2/fosc: for example, twu≥ 156.3 ns when fosc = 12.8 MHz

$t_{WU} \le 4/fosc$ : for example,  $t_{WL} \le 312.5$  ns when fosc = 12.8 MHz

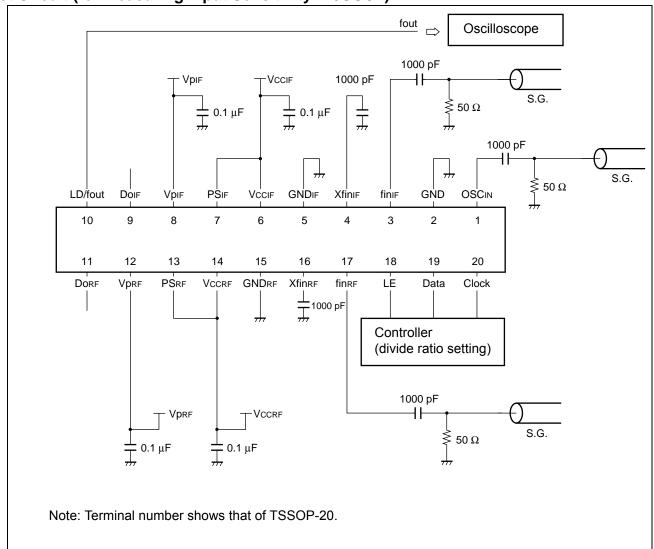

### Test Circuit (for Measuring Input Sensitivity fin/OSCIN)

### **Typical Characteristics**

### **Fin Input Sensitivity**

OSC<sub>IN</sub> Input Sensitivity

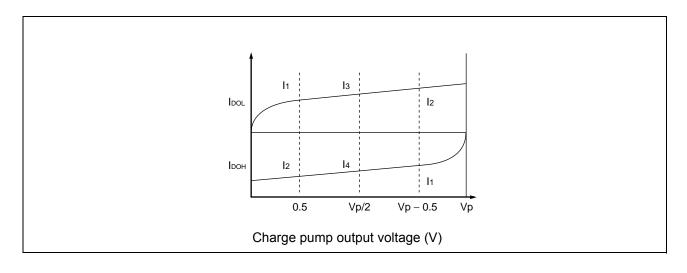

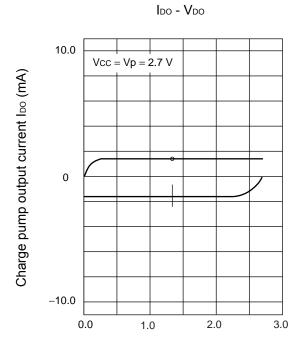

### **RF-PLL Do Output Current**

• 1.5 mA mode

Charge pump output voltage V<sub>DO</sub> (V)

• 6.0 mA mode

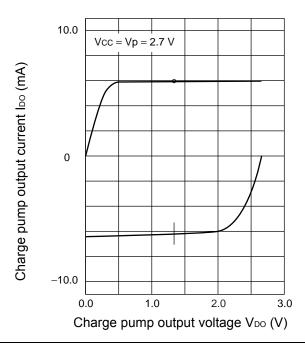

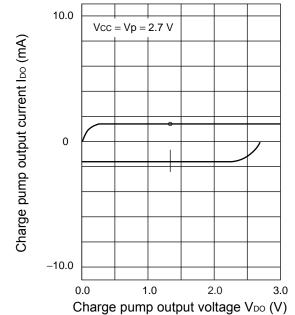

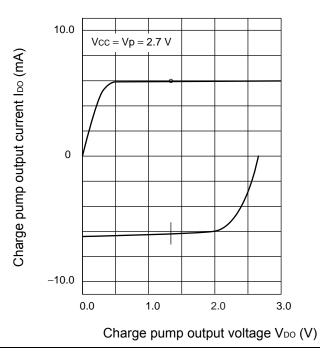

### **IF-PLL Do Output Current**

• 1.5 mA mode

$I_{DO} - V_{DO}$

• 6.0 mA mode

$I_{DO} - V_{DO}$

### fin Input Impedance

### **OSCIN Input Impedance**

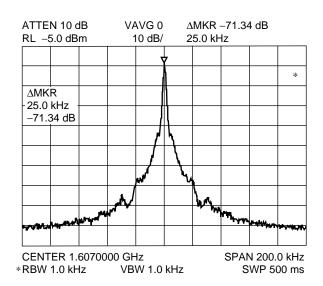

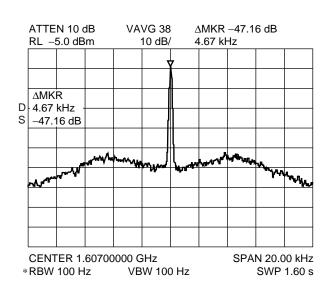

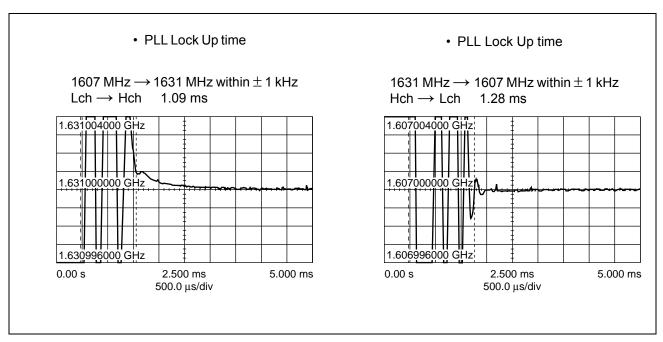

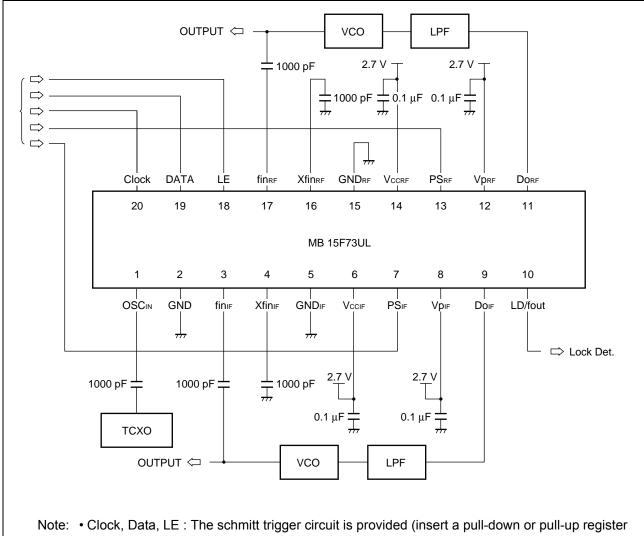

### Reference Information (for Lock-up Time, Phase Noise, and Reference Leakage)

VCO : FUJITSU MEDIA DEVICES (VC-2R3A50-1619)

### • PLL Reference Leakage

### PLL Phase Noise

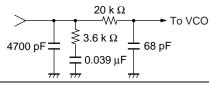

### **Application Example**

to prevent oscillation when open-circuit in the input).

• The terminal number shows that of TSSOP-20.

### **Usage Precautions**

- 1. Vccrf, Vprf, Vccif and Vpif must be equal voltage.

- a. Even if either RF-PLL or IF-PLL is not used, power must be supplied to VCCRF, VPRF, VCCIF and VPIF to keep them equal. It is recommended that the non-use PLL is controlled by power saving function.

- 2. To protect against damage by electrostatic discharge, note the following handling precautions:

- a. Store and transport devices in conductive containers.

- b. Use properly grounded workstations, tools, and equipment.

- c. Turn off power before inserting or removing this device into or from a socket.

- d. Protect leads with conductive sheet, when transporting a board mounted device.

### **Ordering Information**

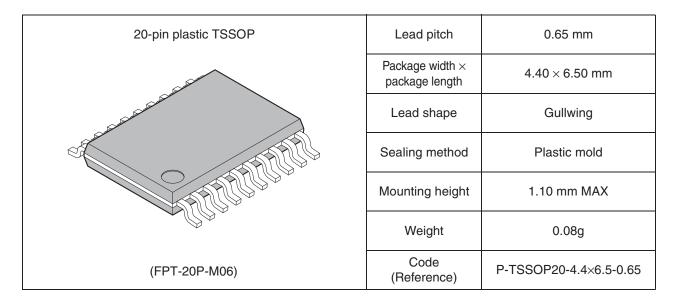

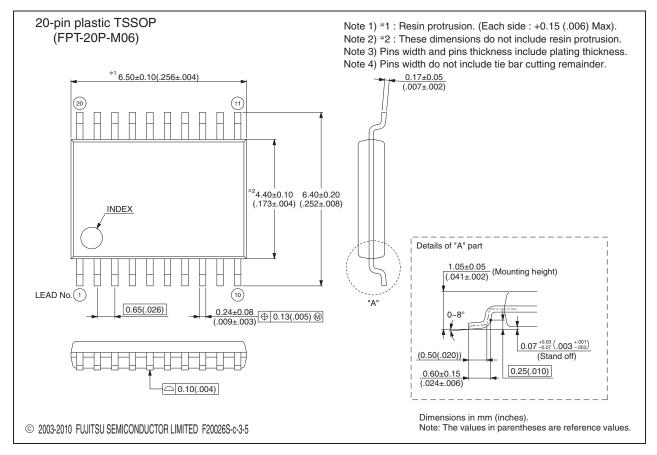

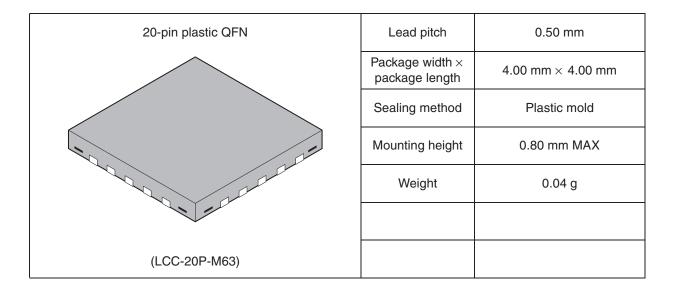

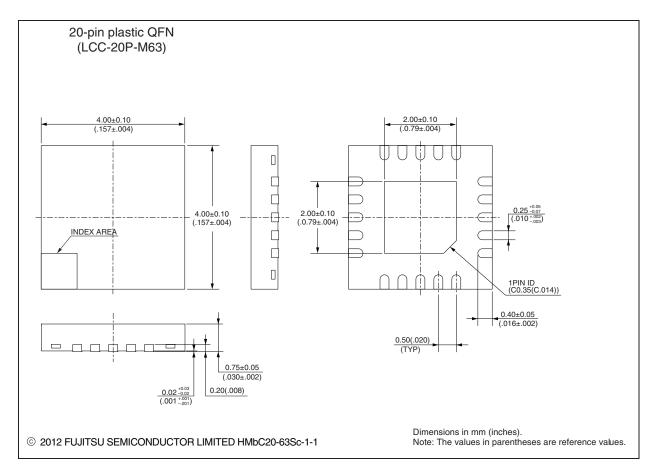

| Part number  | Package                                | Remarks |

|--------------|----------------------------------------|---------|

| MB15F73ULPFT | 20-pin, plastic TSSOP<br>(FPT-20P-M06) |         |

| MB15F73ULWQN | 20-pin, Plastic QFN<br>(LCC-20P-M63)   |         |

Document Number: 002-08480 Rev. \*A Page 25 of 29

### **Package Dimensions**

### **Document History**

Spansion Publication Code: DS04-21368-2E

| Document Title: MB15F73UL ASSP Dual Serial Input PLL Frequency Synthesizer Datasheet Document Number: 002-08480 |         |      |            |                                |

|-----------------------------------------------------------------------------------------------------------------|---------|------|------------|--------------------------------|

| Revision ECN Orig. of Change Date Description of Change                                                         |         |      |            |                                |

| **                                                                                                              | _       | TAOA | 05/31/2012 | New datasheet                  |

| *A                                                                                                              | 5575514 | TAOA | 01/05/2017 | Converted to Cypress template. |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

cypress.com/usb

cypress.com/wireless

#### **Products**

**USB Controllers**

Wireless Connectivity

ARM® Cortex® Microcontrollers cypress.com/arm Automotive cypress.com/automotive Clocks & Buffers cypress.com/clocks Interface cypress.com/interface Internet of Things cypress.com/iot cypress.com/memory Memory Microcontrollers cypress.com/mcu **PSoC** cypress.com/psoc Power Management ICs cypress.com/pmic Touch Sensing cypress.com/touch

#### **PSoC®Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2001-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems (including resuscitation equipment and singical implants), pollution control or hazardous substances management, or other uses where the deliure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-08480 Rev. \*A Revised January 5, 2017 Page 29 of 29