## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# Three-PLL General Purpose Flash Programmable Clock Generator

#### **Features**

- Three Integrated Phase-locked Loops

- Ultra Wide Divide Counters (8-bit Q, 11-bit P, and 7-bit Post Divide)

- Improved Linear Crystal Load Capacitors

- Flash Programmability

- Field Programmable

- Low-jitter, High-accuracy Outputs

- Power Management Options (Shutdown, OE, Suspend)

- Configurable Crystal Drive Strength

- Frequency Select through three External LVTTL Inputs

- 3.3 V Operation

- Automotive A temperature range

- AEC-Q100 Qualified

- 16-pin TSSOP Package

- CyClocksRT™ Support

#### Benefits

Generates up to three unique frequencies on six outputs up to 166 MHz from an external source. Functional upgrade for current CY2292 family.

- Enables 0 ppm frequency generation and frequency conversion under the most demanding applications.

- Improves frequency accuracy over temperature, age, process, and initial offset.

- Nonvolatile programming enables easy customization, fast turnaround, performance tweaking, design timing margin testing, inventory control, lower part count, and more secure product supply. In addition, any part in the family can also be programmed multiple times, which reduces programming errors and provides an easy upgrade path for existing designs.

- In-house programming of samples and prototype quantities is available using the CY3672 development kit.

- Performance suitable for high-end multimedia, communications, industrial, A/D Converters, and consumer applications.

- Supports numerous low power application schemes and reduces EMI by enabling unused outputs to be turned off.

- Adjusts crystal drive strength for compatibility with virtually all crystals.

- 3-bit external frequency select options for PLL1, CLKA, and CLKB.

- Industry-standard supply voltage.

- Industry-standard packaging saves on board space.

- Easy to use software support for design entry.

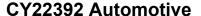

## **Logic Block Diagram**

**Cypress Semiconductor Corporation**Document Number: 001-88434 Rev. \*B

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised October 8, 2014

## Contents

| Pin Configurations               | 3 |

|----------------------------------|---|

| Pin Definitions                  |   |

| Operation                        | 4 |

| Configurable PLLs                |   |

| General Purpose Inputs           |   |

| Crystal Input                    | 4 |

| Output Configuration             | 4 |

| Power Saving Features            | 4 |

| Improving Jitter                 |   |

| Power Supply Sequencing          |   |

| CyberClocks™ Software            |   |

| Device Programming               |   |

| Junction Temperature Limitations |   |

| Maximum Ratings                  |   |

| Operating Conditions             |   |

| Electrical Characteristics       |   |

| Switching Characteristics        |   |

| Switching Waveforms                     | 8  |

|-----------------------------------------|----|

| Test Circuit                            |    |

| Ordering Information                    |    |

| Possible Configurations                 |    |

| Ordering Code Definitions               |    |

| Package Diagrams                        |    |

| Acronyms                                | 11 |

| Document Conventions                    | 11 |

| Units of Measure                        | 11 |

| Document History Page                   | 12 |

| Sales, Solutions, and Legal Information |    |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         | 13 |

| Cypress Developer Community             |    |

| Technical Support                       |    |

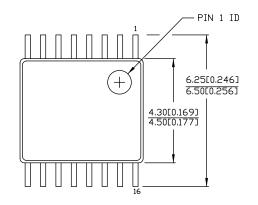

## **Pin Configurations**

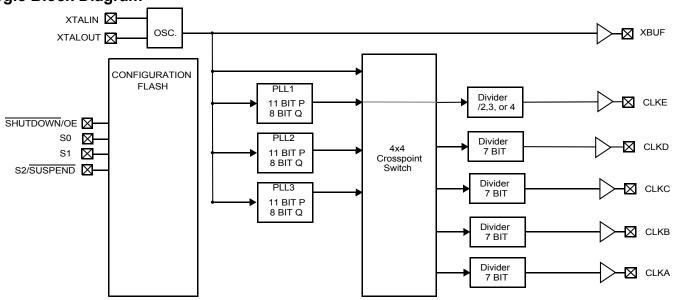

Figure 1. 16-pin TSSOP pinout

## **Pin Definitions**

| Name            | Pin Number | Description                                                                                                                                                       |  |

|-----------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLKC            | 1          | Configurable clock output C                                                                                                                                       |  |

| V <sub>DD</sub> | 2          | Power supply                                                                                                                                                      |  |

| AGND            | 3          | Analog Ground                                                                                                                                                     |  |

| XTALIN          | 4          | Reference crystal input or external reference clock input                                                                                                         |  |

| XTALOUT         | 5          | Reference crystal feedback                                                                                                                                        |  |

| XBUF            | 6          | Buffered reference clock output                                                                                                                                   |  |

| CLKD            | 7          | Configurable clock output D                                                                                                                                       |  |

| CLKE            | 8          | Configurable clock output E                                                                                                                                       |  |

| CLKB            | 9          | onfigurable clock output B                                                                                                                                        |  |

| CLKA            | 10         | onfigurable clock output A                                                                                                                                        |  |

| GND             | 11         | Ground                                                                                                                                                            |  |

| S0              | 12         | General Purpose Input for Frequency Control; bit 0                                                                                                                |  |

| S1              | 13         | General Purpose Input for Frequency Control; bit 1                                                                                                                |  |

| $AV_DD$         | 14         | Analog Power Supply                                                                                                                                               |  |

| S2/SUSPEND      | 15         | General Purpose Input for Frequency Control; bit 2. Optionally Suspend mode control input.                                                                        |  |

| SHUTDOWN/OE     | 16         | Places outputs in three-state condition and shuts down chip when Low. Optionally, only places outputs in tristate condition and does not shut down chip when Low. |  |

#### Operation

The CY22392 is an upgrade to the existing CY2292. The new device has a wider frequency range, greater flexibility, improved performance, and incorporates many features that reduce PLL sensitivity to external system issues.

The device has three PLLs which, when combined with the reference, enable up to four independent frequencies to be output on up to six pins. These three PLLs are completely programmable.

#### Configurable PLLs

PLL1 generates a frequency that is equal to the reference divided by an 8-bit divider (Q) and multiplied by an 11-bit divider in the PLL feedback loop (P). The output of PLL1 is sent to the crosspoint switch. The output of PLL1 is also sent to a /2, /3, or /4 synchronous post-divider that is output through CLKE. The frequency of PLL1 can be changed by external CMOS inputs, S0, S1, S2. See the following section on General Purpose Inputs for more details.

PLL2 generates a frequency that is equal to the reference divided by an 8-bit divider (Q) and multiplied by an 11-bit divider in the PLL feedback loop (P). The output of PLL2 is sent to the crosspoint switch.

PLL3 generates a frequency that is equal to the reference divided by an 8-bit divider (Q) and multiplied by an 11-bit divider in the PLL feedback loop (P). The output of PLL3 is sent to the cross-point switch.

#### General Purpose Inputs

S0, S1, and S2 are general purpose inputs that can be programmed to enable eight different frequency settings. Options that may be switched with these general purpose inputs are as follows: the frequency of PLL1, the output divider of CLKB, and the output divider of CLKA.

CLKA and CLKB both have 7-bit dividers that point to one of two programmable settings (register 0 and register 1). Both clocks share a single register control, so both must be set to register 0, or both must be set to register 1.

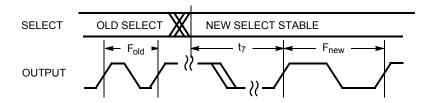

For example, the part may be programmed to use S0, S1, and S2 (0, 0, 0 to 1, 1, 1) to control eight different values of P and Q on PLL1. For each PLL1 P and Q setting, one of the two CLKA and CLKB divider registers can be chosen. Any divider change as a result of switching S0, S1, or S2 is guaranteed to be glitch free.

#### **Crystal Input**

The input crystal oscillator is an important feature of this device because of its flexibility and performance features.

The oscillator inverter has programmable drive strength. This enables maximum compatibility with crystals from various manufacturers, processes, performances, and qualities.

The input load capacitors are placed on-die to reduce external component cost. These capacitors are true parallel-plate capacitors for ultra-linear performance. These were chosen to reduce the frequency shift that occurs when non-linear load capacitance interacts with load, bias, supply, and temperature changes. Non-linear (FET gate) crystal load capacitors must not be used for MPEG, POTS dial tone, communications, or other

applications that are sensitive to absolute frequency requirements.

The value of the load capacitors is determined by six bits in a programmable register. The load capacitance can be set with a resolution of 0.375 pF for a total crystal load range of 6 pF to 30 pF.

For driven clock inputs the input load capacitors may be completely bypassed. This enables the clock chip to accept driven frequency inputs up to 166 MHz. If the application requires a driven input, then XTALOUT must be left floating.

#### **Output Configuration**

Under normal operation there are four internal frequency sources that may be routed through a programmable crosspoint switch to any of the four programmable 7-bit output dividers. The four sources are: reference, PLL1, PLL2, and PLL3. In addition, many outputs have a unique capability for even greater flexibility. The following is a description of each output.

CLKA's output originates from the crosspoint switch and goes through a programmable 7-bit post divider. The 7-bit post divider derives its value from one of two programmable registers. Each of the eight possible combinations of S0, S1, S2 controls which of the two programmable registers is loaded into CLKA's 7-bit post divider. See the section General Purpose Inputs for more information.

CLKB's output originates from the crosspoint switch and goes through a programmable 7-bit post divider. The 7-bit post divider derives its value from one of two programmable registers. Each of the eight possible combinations of S0, S1, and S2 controls which of the two programmable registers is loaded into CLKA's 7-bit post divider. See the section General Purpose Inputs for more information.

CLKC's output originates from the crosspoint switch and goes through a programmable 7-bit post divider. The 7-bit post divider derives its value from one programmable register.

CLKD's output originates from the crosspoint switch and goes through a programmable 7-bit post divider. The 7-bit post divider derives its value from one programmable register.

CLKE's output originates from PLL1 and goes through a post divider that may be programmed to /2, /3, or /4.

XBUF is simply the buffered reference.

The clock outputs have been designed to drive a single point load with a total lumped load capacitance of 15 pF. While driving multiple loads is possible with proper termination, it is generally not recommended.

## **Power Saving Features**

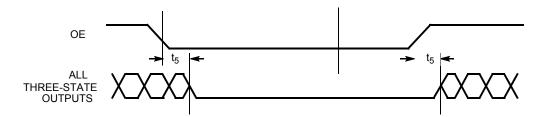

The SHUTDOWN/OE input tristates the outputs when pulled low. If system shutdown is enabled, a Low on this pin also shuts off the PLLs, counters, the reference oscillator, and all other active components. The resulting current on the  $V_{DD}$  pins is less than 5  $\mu A$  (typical). After leaving shutdown mode, the PLLs must relock.

The S2/SUSPEND input can be configured to shut down a customizable set of outputs and/or PLLs, when LOW. All PLLs and any of the outputs can be shut off in nearly any combination. The only limitation is that if a PLL is shut off, all outputs derived from it must also be shut off. Suspending a PLL shuts off all

associated logic, while suspending an output simply forces a tristate condition.

#### **Improving Jitter**

Jitter Optimization Control is useful in mitigating problems related to similar clocks switching at the same moment, causing excess jitter. If one PLL is driving more than one output, the negative phase of the PLL can be selected for one of the outputs (CLKA–CLKD). This prevents the output edges from aligning, enabling superior jitter performance.

#### **Power Supply Sequencing**

For parts with multiple  $V_{DD}$  pins, there are no power supply sequencing requirements. The part is not fully operational until all  $V_{DD}$  pins have been brought up to the voltages specified in the Operating Conditions. All grounds must be connected to the same ground plane.

## CyberClocks™ Software

The CyberClocks application enables users to configure this device. Within CyberClocks, select the CyClocksRT tool. The easy-to-use interface offers complete control of the many features of this family including input frequency, PLL, output frequencies, and different functional options. Data sheet frequency range limitations are checked and performance tuning is automatically applied. CyClocksRT also has a power estimation feature that enables you to see the power

consumption of your specific configuration. Download a copy of CyberClocks free on Cypress's web site at <a href="https://www.cypress.com">www.cypress.com</a>. Install and run it on any PC running Windows.

## **Device Programming**

Part numbers starting with CY22392F are 'field programmable' devices. Field programmable devices are shipped unprogrammed, and must be programmed prior to installation on a PCB. After a programming file (.jed) is created using CyberClocks software, devices can be programmed in small quantities using the CY3672 programmer and CY3698 <sup>[1]</sup> adapter. Programming of the clock device should be done at temperatures < 75 °C. Volume programming is available through Cypress Semiconductor's value added distribution partners or by using third party programmers from BP Microsystems, HiLo Systems, and others. For sufficiently large volumes, Cypress can supply pre-programmed devices with a part number extension that is configuration-specific.

## **Junction Temperature Limitations**

It is possible to program the CY22392 such that the maximum junction temperature rating is exceeded. The package  $\theta_{JA}$  is 115 °C/W. Use the CyClocksRT power estimation feature to verify that the programmed configuration meets the junction temperature and package power dissipation maximum ratings.

#### Note

<sup>1.</sup> Programming of only 16-pin TSSOP package is supported by CY3698.

## **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

| Maximum Programming Cycles                              | 100                 |

|---------------------------------------------------------|---------------------|

| Package Power Dissipation (A-Grade)                     | 350 mW              |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | 2000 V              |

| Latch up (according to JEDEC 17)                        | <u>&gt;</u> ±200 mA |

Stresses exceeding absolute maximum conditions may cause permanent damage to the device. These conditions are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operation sections of this data sheet is not implied. Extended exposure to Absolute Maximum Conditions may affect reliability.

## **Operating Conditions**

The following table lists the recommended operating conditions. [2]

| Parameter        | Description                                                                                    | Min   | Тур | Max   | Unit |

|------------------|------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| $V_{DD}/AV_{DD}$ | Supply Voltage                                                                                 | 3.135 | 3.3 | 3.465 | V    |

| T <sub>A</sub>   | Automotive A-Grade Operating Temperature, Ambient                                              | -40   | _   | +85   | °C   |

| f <sub>REF</sub> | External Reference Crystal                                                                     | 8     | _   | 30    | MHz  |

|                  | External Reference Clock [3], Automotive A-Grade                                               | 1     | _   | 166   | MHz  |

| t <sub>PU</sub>  | Power up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05  | -   | 500   | ms   |

#### **Electrical Characteristics**

| Parameter             | Description                                 | Conditions                                                        | Min | Тур | Max | Unit      |

|-----------------------|---------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|-----------|

| Гон                   | Output High Current [4]                     | $V_{OH} = V_{DD} - 0.5 \text{ V}, V_{DD} = 3.3 \text{ V}^{[5]}$   | 12  | 24  | _   | mA        |

| I <sub>OL</sub>       | Output Low Current [4]                      | V <sub>OL</sub> = 0.5 V, V <sub>DD</sub> = 3.3 V <sup>[5]</sup>   | 12  | 24  | _   | mA        |

| C <sub>XTAL_MIN</sub> | Crystal Load Capacitance [4]                | Capload at minimum setting                                        | -   | 6   | _   | pF        |

| C <sub>XTAL_MAX</sub> | Crystal Load Capacitance [4]                | Capload at maximum setting                                        | _   | 30  | _   | pF        |

| C <sub>LOAD_IN</sub>  | Input Pin Capacitance [4]                   | Except crystal pins                                               | _   | 7   | _   | pF        |

| V <sub>IH</sub>       | High Level Input Voltage                    | CMOS levels,% of AV <sub>DD</sub>                                 | 70% | _   | _   | $AV_{DD}$ |

| V <sub>IL</sub>       | Low Level Input Voltage                     | CMOS levels,% of AV <sub>DD</sub>                                 | _   | _   | 30% | $AV_{DD}$ |

| I <sub>IH</sub>       | Input High Current                          | $V_{IN} = AV_{DD} - 0.3 V$                                        | _   | <1  | 10  | μА        |

| I <sub>IL</sub>       | Input Low Current                           | V <sub>IN</sub> = +0.3 V                                          | _   | <1  | 10  | μА        |

| l <sub>oz</sub>       | Output Leakage Current                      | Three-state outputs (OE = Low)                                    | _   | _   | 10  | μΑ        |

| I <sub>DD</sub>       | Total Power Supply Current under 15 pF load | 3.3 V Power Supply; 2 outputs at 166 MHz; 4 outputs at 83 MHz [6] | -   | 100 | _   | mA        |

|                       |                                             | 3.3 V Power Supply; 2 outputs at 20 MHz; 4 outputs at 40 MHz [6]  | -   | 50  | -   | mA        |

| I <sub>DDS</sub>      | Total Power Supply Current in Shutdown Mode | Shutdown active                                                   | -   | 5   | 20  | μА        |

#### Notes

- Unless otherwise noted, Electrical and Switching Characteristics are guaranteed across these operating conditions.

- 3. External input reference clock must have a duty cycle between 40% and 60%, measured at V<sub>DD</sub>/2.

- 4. Guaranteed by design, not 100% tested.

- 5. Profile configuration through CyberClocks (JEDEC file) should be so generated such that Drive strength should be at 'Mid Low' or above.

- 6. Profile configuration through CyberClocks (JEDEC file) should be so generated such that for A Grade, I<sub>DDmax</sub> ≤ 90mA (considering T<sub>Amax</sub> = 85 °C).

## **Switching Characteristics**

| Parameter        | Name                                     | Description                                                                                                  | Min  | Тур | Max | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| 1/t <sub>1</sub> | Output Frequency under 15 pF load [7, 8] | Clock output limit, CMOS,<br>Automotive                                                                      | _    | _   | 166 | MHz  |

|                  | load                                     | ratomotivo                                                                                                   |      |     |     |      |

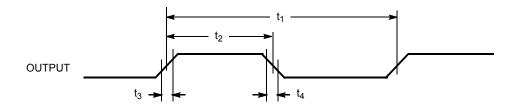

| t <sub>2</sub>   | Output Duty Cycle [7, 9]                 | Duty cycle for outputs, defined as $t_2 \div t_1$ , Fout < 100 MHz, divider $\ge 2$ , measured at $V_{DD}/2$ | 45%  | 50% | 55% |      |

|                  |                                          | Duty cycle for outputs, defined as $t_2 \div t_1$ , Fout > 100 MHz or divider = 1, measured at $V_{DD}/2$    | 40%  | 50% | 60% |      |

| t <sub>3</sub>   | Rising Edge Slew Rate [7]                | Output clock rise time, 20% to 80% of $V_{DD}$                                                               | 0.75 | 1.4 | _   | V/ns |

| t <sub>4</sub>   | Falling Edge Slew Rate [7]               | Output clock fall time, 80% to 20% of V <sub>DD</sub>                                                        | 0.75 | 1.4 | _   | V/ns |

| t <sub>5</sub>   | Output three-state Timing [7]            | Time for output to enter or leave three-state mode after SHUTDOWN/OE switches                                | -    | 150 | 300 | ns   |

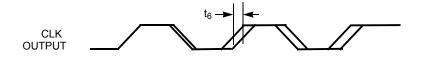

| t <sub>6</sub>   | Clock Jitter [7, 10]                     | Peak-to-peak period jitter, CLK outputs measured at V <sub>DD</sub> /2                                       | -    | 400 | -   | ps   |

| t <sub>7</sub>   | Lock Time [7]                            | PLL Lock Time from Power up                                                                                  | _    | 1.0 | 3   | ms   |

- 7. Guaranteed by design, not 100% tested.

8. Guaranteed to meet 20%–80% output thresholds and duty cycle specifications.

9. Reference Output duty cycle depends on XTALIN duty cycle.

10. Jitter varies significantly with configuration. Reference Output jitter depends on XTALIN jitter and edge rate.

## **Switching Waveforms**

Figure 2. All Outputs, Duty Cycle, and Rise/Fall Time

Figure 3. Output Three-State Timing

Figure 4. CLK Output Jitter

Figure 5. Frequency Change

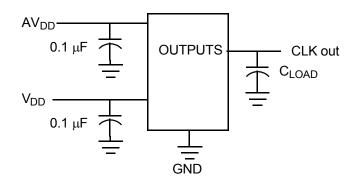

## **Test Circuit**

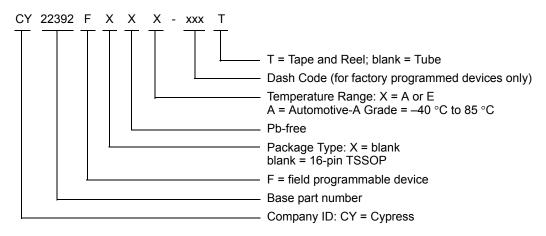

## **Ordering Information**

| Ordering Code          | Package Name | Package Type                                                          | Operating Range                                       |

|------------------------|--------------|-----------------------------------------------------------------------|-------------------------------------------------------|

| Pb-free                |              |                                                                       |                                                       |

| CY22392FXA             | ZZ16         | 16-pin TSSOP                                                          | Automotive-A Grade (T <sub>A</sub> = -40 °C to 85 °C) |

| CY22392FXAT            | ZZ16         | 16-pin TSSOP – Tape and Reel                                          | Automotive-A Grade (T <sub>A</sub> = -40 °C to 85 °C) |

| Programmer             |              |                                                                       |                                                       |

| CY3672-USB             |              | FTG Programmer                                                        |                                                       |

| CY3698 <sup>[11]</sup> |              | CY22392F, CY22393F<br>CY22394F and CY22395F<br>Adapter for CY3672-USB |                                                       |

Some product offerings are factory programmed, customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE or Sales Representative for more information.

#### **Possible Configurations**

| Ordering Code        | Package Name | Package Type                 | Operating Range                                       |

|----------------------|--------------|------------------------------|-------------------------------------------------------|

| Pb-free              |              |                              |                                                       |

| CY22392ZXA-xxx [12]  | ZZ16         | 16-pin TSSOP                 | Automotive-A Grade (T <sub>A</sub> = -40 °C to 85 °C) |

| CY22392ZXA-xxxT [12] | ZZ16         | 16-pin TSSOP – Tape and Reel | Automotive-A Grade (T <sub>A</sub> = -40 °C to 85 °C) |

## **Ordering Code Definitions**

#### Notes

Programming of only 16-pin TSSOP package is supported by CY3698.

The CY22392ZX are factory programmed configurations. Factory programming is available for high-volume design opportunities of 100 Ku/year or more in production. For more details, contact your local Cypress FAE or Cypress Sales Representative.

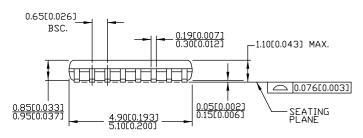

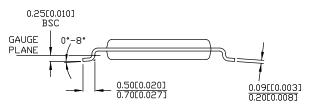

## **Package Diagrams**

Figure 6. 16-pin TSSOP 4.40 mm Body Z16.173/ZZ16.173 Package Outline, 51-85091

DIMENSIONS IN MMEINCHES) MIN. MAX.

REFERENCE JEDEC MD-153

PACKAGE WEIGHT 0.05gms

|          | PART #         |

|----------|----------------|

| Z16.173  | STANDARD PKG.  |

| ZZ16.173 | LEAD FREE PKG. |

51-85091 \*D

## Acronyms

| Acronym | Description                                |

|---------|--------------------------------------------|

| CMOS    | Complementary Metal Oxide Semiconductor    |

| EMI     | Electromagnetic Interference               |

| FET     | Field-Effect Transistor                    |

| FTG     | Frequency Timing Generator                 |

| JEDEC   | Joint Electron Devices Engineering Council |

| LVTTL   | Low Voltage Transistor-Transistor Logic    |

| OSC     | Oscillator                                 |

| PCB     | Printed Circuit Board                      |

| PLL     | Phase Locked Loop                          |

| TSSOP   | Thin Shrink Small Outline Package          |

## **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure   |

|--------|-------------------|

| °C     | degree Celsius    |

| MHz    | megahertz         |

| μΑ     | microampere       |

| μF     | microfarad        |

| mA     | milliampere       |

| mm     | millimeter        |

| ms     | millisecond       |

| mW     | milliwatt         |

| ns     | nanosecond        |

| %      | percent           |

| pF     | picofarad         |

| ppm    | parts per million |

| ps     | picosecond        |

| V      | volt              |

| W      | watt              |

## **Document History Page**

| REV. | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|---------|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 4062529 | CINM               | 08/23/2013         | New data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *A   | 4322006 | CINM               | 04/23/2014         | Updated Features:<br>Added Automotive-E grade temperature related information.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|      |         |                    |                    | Updated Device Programming: Added "Programming of the clock device should be done at temperatures < 75 °C."                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |         |                    |                    | Updated Maximum Ratings: Added "Data Retention at Tj = 150 °C" as "> 2 years". Added "Package Power Dissipation (E-Grade)" as "217 mW". Added "Stresses exceeding absolute maximum conditions may caus permanent damage to the device. These conditions are stress ratings only Functional operation of the device at these or any other conditions beyon those indicated in the operation sections of this data sheet is not implied Extended exposure to Absolute Maximum Conditions may affect reliability." |

|      |         |                    |                    | Updated Electrical Characteristics: Added Note 5 and referred the same note in Conditions of $I_{OH}$ and $I_{C}$ parameters. Updated Conditions of $I_{OZ}$ parameter. Added Note "Profile configuration through CyberClocks (JEDEC file) should b so generated such that for E-Grade, $I_{DDmax} \leq 56$ mA (considerin $T_{Amax}$ = 125 °C)." referred the same note in Conditions of $I_{DD}$ parameter. Added Note 6 and referred the same note in Conditions of $I_{DD}$ parameter.                      |

|      |         |                    |                    | Updated Ordering Information: Updated part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *B   | 4528309 | TAVA               | 10/08/2014         | Changed status from Preliminary to Final.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |         |                    |                    | Removed Automotive-E grade temperature related information in all instance across the document.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |         |                    |                    | Updated Electrical Characteristics: Removed Note "Profile configuration through CyberClocks (JEDEC file) should be so generated such that for E-Grade, $I_{DDmax} \leq 56$ mA (considerin $T_{Amax} = 125$ °C)." and its reference in $I_{DD}$ parameter.                                                                                                                                                                                                                                                       |

|      |         |                    |                    | Updated Ordering Information:<br>Updated part numbers.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|      |         |                    |                    | Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive Clocks & Buffers Interface

Lighting & Power Control

Memory PSoC Touch Sensing USB Controllers Wireless/RF cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc cypress.com/go/plc cypress.com/go/memory cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

## PSoC® Solutions

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

## **Technical Support**

cypress.com/go/support

© Cypress Semiconductor Corporation, 2013-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document Number: 001-88434 Rev. \*B