# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

### TRIPLE PLL FIELD PROG. SPREAD SPECTRUM CLOCK SYNTHESIZER ICS290

## **Description**

The ICS290 field programmable spread spectrum clock synthesizer generates up to eight high-quality, high-frequency clock outputs including multiple reference clocks from a low-frequency crystal input. It is designed to replace crystals, crystal oscillators and stand alone spread spectrum devices in most electronic systems.

Using IDT's VersaClock<sup>TM</sup> software to configure PLLs and outputs, the ICS290 contains a One-Time Programmable (OTP) ROM for field programmability. Programming features include input/output frequencies, spread spectrum amount, eight selectable configuration registers and up to two sets of four low-skew outputs.

Using Phase-Locked Loop (PLL) techniques, the device runs from a standard fundamental mode, inexpensive crystal, or clock. It can replace multiple crystals and oscillators, saving board space and cost.

The ICS290 is also available in factory programmed custom versions for high-volume applications.

#### **Features**

- Packaged as 20-pin TSSOP Pb-free, RoHS compliant

- Eight addressable registers

- · Replaces multiple crystals and oscillators

- Output frequencies up to 200 MHz at 3.3 V

- Configurable Spread Spectrum Modulation

- Input crystal frequency of 5 to 27 MHz

- Clock input frequency of 3 to 166 MHz

- · Up to eight reference outputs

- Up to two sets of four low-skew outputs

- Operating voltages of 3.3 V

- · Controllable output drive levels

- Advanced, low-power CMOS process

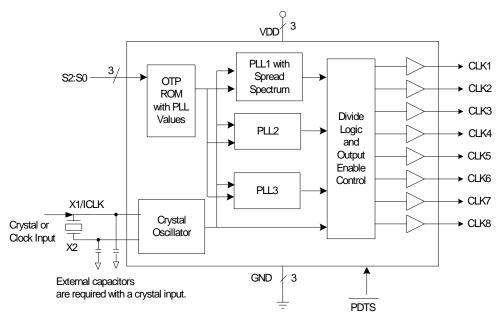

## **Block Diagram**

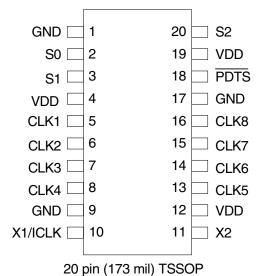

# **Pin Assignment**

# **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                                                                                                 |  |  |

|---------------|-------------|-------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| 1             | GND         | Power       | Connect to ground.                                                                                              |  |  |

| 2             | S0          | Input       | Select pin 0. Internal pull-up resistor.                                                                        |  |  |

| 3             | S1          | Input       | Select pin 1. Internal pull-up resistor.                                                                        |  |  |

| 4             | VDD         | Power       | Connect to +3.3 V.                                                                                              |  |  |

| 5             | CLK1        | Output      | Output clock 1. Weak internal pull-down when tri-state.                                                         |  |  |

| 6             | CLK2        | Output      | Output clock 2. Weak internal pull-down when tri-state.                                                         |  |  |

| 7             | CLK3        | Output      | Output clock 3. Weak internal pull-down when tri-state.                                                         |  |  |

| 8             | CLK4        | Output      | Output clock 4. Weak internal pull-down when tri-state.                                                         |  |  |

| 9             | GND         | Power       | Connect to ground.                                                                                              |  |  |

| 10            | X1/ICLK     | XI          | Crystal input. Connect this pin to a crystal or external input clock.                                           |  |  |

| 11            | X2          | XO          | Crystal Output. Connect this pin to a crystal. Float for clock input.                                           |  |  |

| 12            | VDD         | Power       | Connect to +3.3 V.                                                                                              |  |  |

| 13            | CLK5        | Output      | Output clock 5. Weak internal pull-down when tri-state.                                                         |  |  |

| 14            | CLK6        | Output      | Output clock 6. Weak internal pull-down when tri-state.                                                         |  |  |

| 15            | CLK7        | Output      | Output clock 7. Weak internal pull-down when tri-state.                                                         |  |  |

| 16            | CLK8        | Output      | Output clock 8. Weak internal pull-down when tri-state.                                                         |  |  |

| 17            | GND         | Power       | Connect to ground.                                                                                              |  |  |

| 18            | PDTS        | Input       | Power-down tri-state. Powers down entire chip and tri-states clock outputs when low. Internal pull-up resistor. |  |  |

| 19            | VDD         | Power       | Connect to +3.3 V.                                                                                              |  |  |

| 20            | S2          | Input       | Select pin 2. Internal pull-up resistor.                                                                        |  |  |

ICS290

## **External Components**

The ICS290 requires a minimum number of external components for proper operation.

#### **Series Termination Resistor**

Clock output traces over one inch should use series termination. To series terminate a  $50\Omega$  trace (a commonly used trace impedance), place a  $33\Omega$  resistor in series with the clock line, as close to the clock output pin as possible. The nominal impedance of the clock output is  $20\Omega$

#### **Decoupling Capacitors**

As with any high-performance mixed-signal IC, the ICS290 must be isolated from system power supply noise to perform optimally.

Decoupling capacitors of 0.01µF must be connected between each VDD and the PCB ground plane. For optimum device performance, the decoupling capacitor should be mounted on the component side of the PCB. Avoid the use of vias on the decoupling circuit.

#### **Crystal Load Capacitors**

The device crystal connections should include pads for small capacitors from X1 to ground and from X2 to ground. These capacitors are used to adjust the stray capacitance of the board to match the nominally required crystal load capacitance. Because load capacitance can only be increased in this trimming process, it is important to keep stray capacitance to a minimum by using very short PCB traces (and no vias) between the crystal and device. Crystal capacitors must be connected from each of the pins X1 and X2 to ground.

The value (in pF) of these crystal caps should equal (C<sub>1</sub> -6 pF)\*2. In this equation,  $C_1$  = crystal load capacitance in pF. Example: For a crystal with a 16 pF load capacitance, each crystal capacitor would be 20 pF  $[(16-6) \times 2] = 20$ .

#### **ICS290 Configuration Capabilities**

The architecture of the ICS290 allows the user to easily configure the device to a wide range of output frequencies, for a given input reference frequency.

The frequency multiplier PLL provides a high degree of precision. The M/N values (the multiplier/divide values available to generate the target VCO frequency) can be set within the range of M = 1 to 1024 and N = 1 to 32,895.

The ICS290 also provides separate output divide values, from 2 through 63, to allow the two output clock banks to support widely differing frequency values from the same PLL.

Each output frequency can be represented as:

OutputFreq = REFFreq

$$\cdot$$

$\frac{N}{N}$

#### **Output Drive Control**

The ICS290 has two output drive settings. Low drive should be selected when outputs are less than 100 MHz. High drive should be selected when outputs are greater than 100 MHz. (Consult the AC Electrical Characteristics for output rise and fall times for each drive option.)

#### **IDT VersaClock Software**

IDT applies years of PLL optimization experience into a user friendly software that accepts the user's target reference clock and output frequencies and generates the lowest jitter, lowest power configuration, with only a press of a button. The user does not need to have prior PLL experience or determine the optimal VCO frequency to support multiple output frequencies.

VersaClock software quickly evaluates accessible VCO frequencies with available output divide values and provides an easy to understand, bar code rating for the target output frequencies. The user may evaluate output accuracy, performance trade-off scenarios in seconds.

#### **Spread Spectrum Modulation**

The ICS290 utilizes frequency modulation (FM) to distribute energy over a range of frequencies. By modulating the output clock frequencies, the device effectively lowers energy across a broader range of frequencies; thus, lowering a system's electromagnetic interference (EMI). The modulation rate is the time from transitioning from a minimum frequency to a maximum frequency and then back to the minimum.

Spread Spectrum Modulation can be applied as either "center spread" or "down spread". During center spread modulation, the deviation from the target frequency is equal in the positive and negative directions. The effective average frequency is equal to the target frequency. In

applications where the clock is driving a component with a maximum frequency rating, down spread should be applied. In this case, the maximum frequency, including modulation, is the target frequency. The effective average frequency is less than the target frequency.

The ICS290 operates in both center spread and down spread modes. For center spread, the frequency can be modulated between  $\pm 0.125\%$  to  $\pm 2.0\%$ . For down spread, the frequency can be modulated between -0.25% to -4.0%.

Both output frequency banks will utilize identical spread spectrum percentage deviations and modulation rates, if a common VCO frequency can be identified.

#### **Spread Spectrum Modulation Rate**

The spread spectrum modulation frequency applied to the output clock frequency may occur at a variety of rates. For applications requiring the driving of "down-circuit" PLLs, Zero Delay Buffers, or those adhering to PCI standards, the spread spectrum modulation rate should be set to 30-33 kHz. For other applications, a 120 kHz modulation option is available.

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the ICS290. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Parameter             | Condition         | Min. | Тур.    | Max.    | Units |

|-----------------------|-------------------|------|---------|---------|-------|

| Supply Voltage, VDD   | Referenced to GND |      |         | 7       | V     |

| Inputs                | Referenced to GND | -0.5 | VDD+0.5 |         | V     |

| Clock Outputs         | Referenced to GND | -0.5 |         | VDD+0.5 | V     |

| Storage Temperature   |                   | -65  |         | 150     | °C    |

| Soldering Temperature | Max 10 seconds    |      |         | 260     | °C    |

| Junction Temperature  |                   |      |         | 125     | °C    |

## **Recommended Operation Conditions**

| Parameter                                         | Min.   | Тур. | Max.   | Units |

|---------------------------------------------------|--------|------|--------|-------|

| Ambient Operating Temperature (ICS290GP)          | 0      |      | +70    | °C    |

| Ambient Operating Temperature (ICS290GIP)         | -40    |      | +85    | °C    |

| Power Supply Voltage (measured in respect to GND) | +3.135 | +3.3 | +3.465 | V     |

| Power Supply Ramp Time                            |        |      | 4      | ms    |

## **DC Electrical Characteristics**

Unless stated otherwise, **VDD = 3.3 V ±5%**, Ambient Temperature -40 to +85° C

| Parameter                          | Symbol           | Conditions                                                                    | Min.    | Тур. | Max.    | Units |

|------------------------------------|------------------|-------------------------------------------------------------------------------|---------|------|---------|-------|

| Operating Voltage                  | VDD              |                                                                               | 3.135   |      | 3.465   | V     |

|                                    |                  | Config. Dependent - See<br>VersaClock <sup>TM</sup> Estimates                 |         |      |         | mA    |

| Operating Supply Current           | IDD              | Eight 33.3333 MHz outs, PDTS = 1, no load, Note 1                             |         | 27   |         | mA    |

|                                    |                  | PDTS = 0, no load                                                             |         | 500  |         | μΑ    |

| Input High Voltage                 | $V_{IH}$         | S2:S0                                                                         | VDD/2+1 |      |         | V     |

| Input Low Voltage                  | V <sub>IL</sub>  | S2:S0                                                                         |         |      | 0.4     | V     |

| Input High Voltage, PDTS           | V <sub>IH</sub>  |                                                                               | VDD-0.5 |      |         | V     |

| Input Low Voltage, PDTS            | V <sub>IL</sub>  |                                                                               |         |      | 0.4     | V     |

| Input High Voltage                 | V <sub>IH</sub>  | ICLK                                                                          | VDD/2+1 |      |         | V     |

| Input Low Voltage                  | $V_{IL}$         | ICLK                                                                          |         |      | VDD/2-1 | V     |

| Output High Voltage<br>(CMOS High) | V <sub>OH</sub>  | I <sub>OH</sub> = -4 mA                                                       | VDD-0.4 |      |         | V     |

| Output High Voltage                | V <sub>OH</sub>  | I <sub>OH</sub> = -8 mA (Low Drive);<br>I <sub>OH</sub> = -12 mA (High Drive) | 2.4     |      |         | V     |

| Output Low Voltage                 | V <sub>OL</sub>  | I <sub>OL</sub> = 8 mA (Low Drive);<br>I <sub>OL</sub> = 12 mA (High Drive)   |         |      | 0.4     | V     |

| Short Circuit Current              | Ios              | Low Drive                                                                     |         | ±40  |         |       |

|                                    |                  | High Drive                                                                    |         | ±70  |         | mA    |

| Nom. Output Impedance              | Z <sub>O</sub>   |                                                                               |         | 20   |         | Ω     |

| Internal pull-up Resistor          | R <sub>PUS</sub> | S2:S0, PDTS                                                                   |         | 190  |         | kΩ    |

| Internal pull-down<br>Resistor     | R <sub>PD</sub>  | CLK outputs                                                                   |         | 120  |         | kΩ    |

| Input Capacitance                  | C <sub>IN</sub>  | Inputs                                                                        |         | 4    |         | pF    |

Note 1: Example with 25 MHz crystal input with eight outputs of  $33.\overline{3}$  MHz, no load, and VDD = 3.3 V.

## **AC Electrical Characteristics**

Unless stated otherwise, **VDD = 3.3 V \pm 5\%**, Ambient Temperature -40 to +85° C

| Parameter                        | Symbol          | Conditions                                                                  | Min.  | Тур.         | Max. | Units |

|----------------------------------|-----------------|-----------------------------------------------------------------------------|-------|--------------|------|-------|

| Input Frequency                  | F <sub>IN</sub> | Fundamental crystal                                                         | 5     |              | 27   | MHz   |

|                                  |                 | Clock input                                                                 | 3     |              | 166  | MHz   |

| Output Frequency                 |                 |                                                                             | 0.314 |              | 200  | MHz   |

| Output Rise/Fall Time            | t <sub>OF</sub> | 80% to 20%, high drive,<br>Note 1                                           |       | 1.0          |      | ns    |

| Output Rise/Fall Time            | t <sub>OF</sub> | 80% to 20%, low drive,<br>Note 1                                            |       | 2.0          |      | ns    |

| Duty Cycle                       |                 | Note 2                                                                      | 40    | 49-51        | 60   | %     |

| Output Frequency Synthesis Error |                 | Configuration Dependent                                                     |       | TBD          |      | ppm   |

| Power-up Time                    |                 | PLL lock-time from power-up                                                 |       | 4            | 10   | ms    |

|                                  |                 | PDTS goes high until<br>stable CLK output,<br>Spread Spectrum Off           |       | 0.6          | 2    | ms    |

|                                  |                 | PDTS goes high until<br>stable CLK output,<br>Spread Spectrum On            |       | 4            | 7    | ms    |

|                                  |                 | PDTS goes high until<br>spread spectrum is<br>stable, Spread Spectrum<br>On |       | 10           | 50   | ms    |

| One Sigma Clock Period Jitter    |                 | Configuration Dependent                                                     |       | 50           |      | ps    |

| Maximum Absolute Jitter          | t <sub>ja</sub> | Deviation from Mean.<br>Configuration Dependent                             |       | <u>+</u> 200 |      | ps    |

| Pin-to-Pin Skew                  | _               | Low Skew Outputs                                                            | -250  |              | 250  | ps    |

Note 1: Measured with 15 pF load.

Note 2: Duty Cycle is configuration dependent. Most configurations are min 45% / max 55%.

## **Thermal Characteristics**

| Parameter                           | Symbol        | Conditions     | Min. | Тур. | Max. | Units |

|-------------------------------------|---------------|----------------|------|------|------|-------|

| Thermal Resistance Junction to      | $\theta_{JA}$ | Still air      |      | 93   |      | ° C/W |

| Ambient                             | $\theta_{JA}$ | 1 m/s air flow |      | 78   |      | ° C/W |

|                                     | $\theta_{JA}$ | 3 m/s air flow |      | 65   |      | ° C/W |

| Thermal Resistance Junction to Case | $\theta_{JC}$ |                |      | 20   |      | ° C/W |

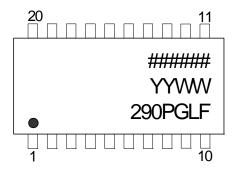

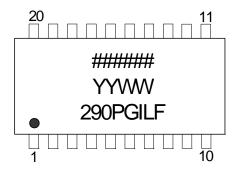

# **Marking Diagrams**

#### Notes:

- 1. ##### is the lot number.

- 2. YYWW is the last two digits of the year and week that the part was assembled.

- 3. "I" denotes industrial temperature range (if applicable).

- 4. "L" denotes Pb (lead) free package.

- 5. Bottom marking: country of origin.

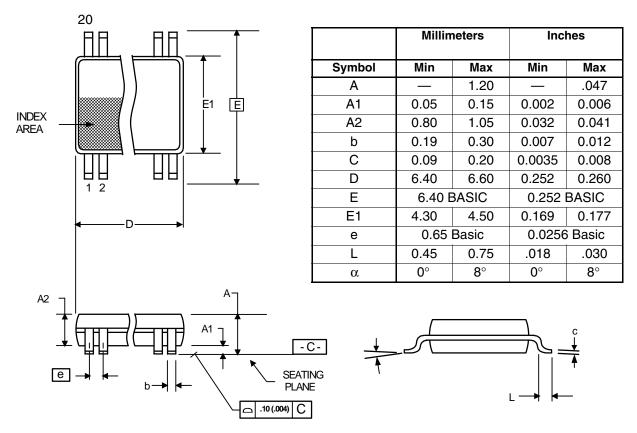

## Package Outline and Package Dimensions (20-pin TSSOP, 173 Mil. Body)

Package dimensions are kept current with JEDEC Publication No. 95

## **Ordering Information**

| Part / Order Number | Marking    | <b>Shipping Packaging</b> | Package      | Temperature   |

|---------------------|------------|---------------------------|--------------|---------------|

| 290PGLF             | see page 7 | see page 7 Tubes 20       |              | 0 to +70° C   |

| 290PGILF            |            | Tubes                     | 20-pin TSSOP | -40 to +85° C |

| 290G-XXLF           | 290GXXL    | Tubes                     | 20-pin TSSOP | 0 to +70° C   |

| 290GI-XXLF          | 290GIXXL   | Tubes                     | 20-pin TSSOP | -40 to +85° C |

| 290G-XXLFT          | 290GXXL    | Tape and Reel             | 20-pin TSSOP | 0 to +70° C   |

| 290GI-XXLFT         | 290GIXXL   | Tape and Reel             | 20-pin TSSOP | -40 to +85° C |

<sup>&</sup>quot;LF" suffix to the part number denotes the Pb-Free configuration, RoHS compliant.

The 290G-XXLF and 290GI-XXLF are factory programmed versions of the 290PGLF and 290PGILF. A unique "-XX" suffix is assigned by the factory for each custom configuration, and a separate data sheet is kept on file. For more information on custom part numbers programmed at the factory, please contact your local IDT sales and marketing representative.

While the information presented herein has been checked for both accuracy and reliability, IDT assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

VersaClock<sup>TM</sup> is a trademark of IDT, Inc. All rights reserved.

## Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775 For Tech Support

www.idt.com/go/clockhelp

#### **Corporate Headquarters**

Integrated Device Technology, Inc. www.idt.com