# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# 155.52 MHz Frequency Synthesizer

AD809

#### **FEATURES**

Frequency Synthesis to 155.52 MHz 19.44 MHz or 9.72 MHz Input Reference Signal Select Mux Single Supply Operation: +5 V or -5.2 V

Output Jitter: 2.0 Degrees RMS

Low Power: 90 mW

10 KH ECL/PECL Compatible Output

10 KH ECL/PECL/TTL/CMOS Compatible Input

Package: 16-Pin Narrow 150 Mil SOIC

#### PRODUCT DESCRIPTION

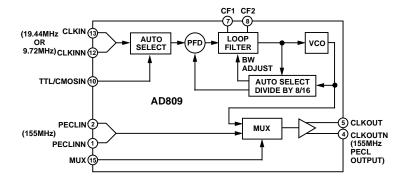

The AD809 provides a 155.52 MHz ECL/PECL output clock from either a 19.44 MHz or a 9.72 MHz TTL/CMOS/ECL/PECL reference frequency. The AD809 functionality supports a distributed timing architecture, allowing a backplane or PCB 19.44 MHz or 9.72 MHz timing reference signal to be distributed to multiple

155.52 Mbps ports. The AD809 can be applied to create the transmit bit clock for one or more ports.

An input signal multiplexer supports loop-timed applications where a 155.52 MHz transmit bit clock is recovered from the 155.52 Mbps received data.

The low jitter VCO, low power and wide operating temperature range make the device suitable for generating a 155.52 MHz bit clock for SONET/SDH/Fiber in the Loop systems.

The device has a low cost, on-chip VCO that locks to either 8× or 16× the frequency at the 19.44 MHz or 9.72 MHz input. No external components are needed for frequency synthesis; however, the user can adjust loop dynamics through selection of a damping factor capacitor whose value determines loop damping.

The AD809 design guarantees that the clock output frequency will drift low (by roughly 20%) in the absence of a signal at the input.

The AD809 consumes 90 mW and operates from a single power supply at either +5 V or -5.2 V.

#### FUNCTIONAL BLOCK DIAGRAM

# **AD809\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

# **DOCUMENTATION**

## **Application Notes**

• AN-349: Keys to Longer Life for CMOS

#### **Data Sheet**

• AD809: 155.52 MHz Frequency Synthesizer Data Sheet

# **TOOLS AND SIMULATIONS**

- ADIsimPLL™

- ADIsimRF

# REFERENCE MATERIALS $\Box$

## **Product Selection Guide**

· RF Source Booklet

#### **Technical Articles**

- Phase Locked Loops for High-Frequency Receivers and Transmitters – Part 1

- Phase Locked Loops for High-Frequency Receivers and Transmitters – Part 3

- Phase-Locked Loops for High-Frequency Receivers and Transmitters - Part 2

# **DESIGN RESOURCES**

- · AD809 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all AD809 EngineerZone Discussions.

# SAMPLE AND BUY

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

# $\textbf{AD809-SPECIFICATIONS} \ \, (\textbf{T}_{A} = \textbf{T}_{MIN} \ \, \text{to} \ \, \textbf{T}_{MAX}, \ \, \textbf{V}_{S} = \textbf{V}_{MIN} \ \, \text{to} \ \, \textbf{V}_{MAX}, \ \, \textbf{C}_{D} = 22 \ \, \text{nF}, \ \, \text{unless otherwise noted})$

| Parameter                                                                                                                                                                                                                                                     | Condition                                                                  | Min               | Тур                 | Max                 | Units                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------|---------------------|---------------------|----------------------------------|

| TRACKING AND CAPTURE RANGE <sup>1</sup>                                                                                                                                                                                                                       | ×8 Synthesis<br>×16 Synthesis                                              | 19.42<br>9.71     |                     | 19.46<br>9.73       | MHz<br>MHz                       |

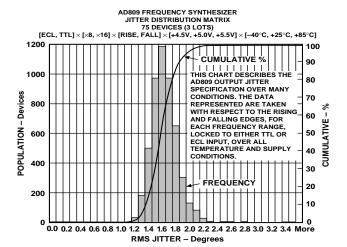

| OUTPUT JITTER                                                                                                                                                                                                                                                 | ×8 Synthesis<br>×16 Synthesis                                              |                   | 1.6<br>1.6          | 2.9<br>2.9          | Degrees RMS<br>Degrees RMS       |

| JITTER TRANSFER<br>Bandwidth<br>Peaking                                                                                                                                                                                                                       | $C_D = 5.6 \text{ nF } (\zeta = 5)$<br>$C_D = 22 \text{ nF } (\zeta = 10)$ |                   | 200<br>0.08<br>0.02 |                     | kHz<br>dB<br>dB                  |

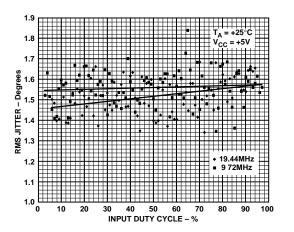

| DUTY CYCLE TOLERANCE                                                                                                                                                                                                                                          | ×8 or ×16 Synthesis<br>Output Jitter ≤ 2.9 Degrees RMS                     | 15                |                     | 85                  | %                                |

| $\begin{array}{c} \text{INPUT VOLTAGE LEVELS} \\ \text{PECL} \\ \text{Input Logic High, V}_{\text{IH}} \\ \text{Input Logic Low, V}_{\text{IL}} \\ \text{TTL} \\ \text{Input Logic High, V}_{\text{IH}} \\ \text{Input Logic Low, V}_{\text{IL}} \end{array}$ | @ CLKIN/N and PECLIN/N Inputs  @ TTL/CMOSIN and MUX Inputs                 | 3.8<br>3.1<br>2.0 |                     | V <sub>CC</sub> 3.6 | Volts<br>Volts<br>Volts<br>Volts |

| OUTPUT VOLTAGE LEVELS PECL Output Logic High, $V_{OH}$ Output Logic Low, $V_{OL}$                                                                                                                                                                             | Referenced to V <sub>CC</sub>                                              | -1.2<br>-2.0      | -1.0<br>-1.8        | -0.7<br>-1.7        | Volts<br>Volts                   |

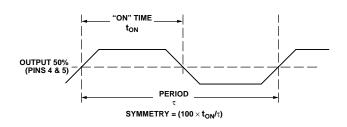

| SYMMETRY (Duty Cycle)                                                                                                                                                                                                                                         | ×8 Synthesis or<br>×16 Synthesis                                           | 46                | 52                  | 62                  | %<br>%                           |

| OUTPUT RISE/FALL TIMES 1.5 Rise Time $(t_R)$ Fall Time $(t_F)$                                                                                                                                                                                                | 20%–80%<br>80%–20%                                                         |                   | 1.1<br>1.1          | 1.5<br>1.5          | ns<br>ns                         |

| POWER SUPPLY VOLTAGE                                                                                                                                                                                                                                          | V <sub>MIN</sub> to V <sub>MAX</sub>                                       | 4.5               |                     | 5.5                 | Volts                            |

| POWER SUPPLY CURRENT                                                                                                                                                                                                                                          |                                                                            |                   | 17                  | 26                  | mA                               |

| OPERATING TEMPERATURE RANGE                                                                                                                                                                                                                                   | T <sub>MIN</sub> to T <sub>MAX</sub>                                       | -40               |                     | +85                 | °C                               |

#### NOTES

Specifications subject to change without notice.

## **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                                   |

|--------------------------------------------------|

| Input Voltage (Pin 12 or Pin 13)                 |

| Maximum Junction Temperature +165°C              |

| Storage Temperature Range65°C to +150°C          |

| Lead Temperature Range (Soldering 10 sec) +300°C |

| ESD Rating (Human Body Model)1500 V              |

<sup>\*</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Thermal Characteristics:

16-Pin Narrow Body SOIC Package:  $\theta_{JA} = 110^{\circ}\text{C/W}$ .

Figure 1. Symmetry

## **ORDERING GUIDE**

| Model         | Temperature Range | Package Description     | Package Option |  |

|---------------|-------------------|-------------------------|----------------|--|

| AD809BR       | -40°C to +85°C    | 16-Pin Narrow Body SOIC | R-16A          |  |

| AD809BR-REEL7 | -40°C to +85°C    | 750 Pieces, 7" Reel     | R-16A          |  |

-2- REV. A

$<sup>^{1}</sup>$ Device design is guaranteed for operation over Capture Ranges and Tracking Ranges, however the device has wider capture and tracking ranges (for both  $\times 8$  and  $\times 16$  synthesis).

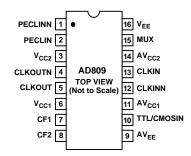

### PIN DESCRIPTIONS

| Pin<br>No. | Mnemonic          | Description                                |

|------------|-------------------|--------------------------------------------|

| 1          | PECLINN           | Differential 155 MHz Input                 |

| 2          | PECLIN            | Differential 155 MHz Input                 |

| 3          | $V_{CC2}$         | Digital V <sub>CC</sub> for PECL Outputs   |

| 4          | CLKOUTN           | Differential 155 MHz Output                |

| 5          | CLKOUT            | Differential 155 MHz Output                |

| 6          | $V_{CC1}$         | Digital V <sub>CC</sub> for Internal Logic |

| 7          | CF1               | Loop Damping Capacitor                     |

| 8          | CF2               | Loop Damping Capacitor                     |

| 9          | $AV_{EE}$         | Analog $ m V_{EE}$                         |

| 10         | TTL/CMOSIN        | TTL/CMOS Reference Clock Input             |

| 11         | AV <sub>CC1</sub> | Analog $V_{CC}$ for PLL                    |

| 12         | CLKINN            | PECL Differential Reference Clock Input    |

| 13         | CLKIN             | PECL Differential Reference Clock Input    |

| 14         | AV <sub>CC2</sub> | Analog V <sub>CC</sub> for Input Stage     |

| 15         | MUX               | Input Signal Mux Control Input             |

| 16         | $V_{\rm EE}$      | Digital V <sub>EE</sub>                    |

### PIN CONFIGURATION

#### Table I.

| MUX Input | Input Selected |  |  |

|-----------|----------------|--|--|

| TTL "0"   | CLKIN/CLKINN   |  |  |

| TTL "1"   | PECLIN/PECLINN |  |  |

Table II. Applying a PECL/ECL or CMOS/TTL Reference Input to the AD809

| Input Reference          | AD809 Configuration                                                                                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PECL/ECL Differential    | Apply the valid PECL–level reference frequency to Pins 13 and 12. AD809 frequency synthesizer ignores the input at Pin 10.                                                   |

| TTL/CMOS<br>Single-Ended | Apply the reference frequency to Pin 10.                                                                                                                                     |

|                          | Connect Pins 13 and 12 to $AV_{EE}$ (Pins 9 and 16). The AD809 senses the common-mode signal at these pins as less than valid PECL and selects the TTL/CMOS input as active. |

#### AD809 Phase Skew

The AD809 output is in phase with the input. The falling edge at Pin 4, CLKOUTN, occurs 700 ps before the rising edge at Pin 10, TTL/CMOSIN at 27°C. The phase skew remains relatively constant over temperature. Refer to Table III for phase skew data.

Table III. Phase Skew vs. Temperature

| Temperature (°C) | Skew (CLKOUTN, Pin 4, Relative to TTL/CMOSIN, Pin 10 Measured in ps at Package Pins) |

|------------------|--------------------------------------------------------------------------------------|

| -35              | -1000                                                                                |

| -20              | -950                                                                                 |

| 0                | -850                                                                                 |

| 10               | -750                                                                                 |

| 30               | -700                                                                                 |

| 50               | -600                                                                                 |

| 70               | -450                                                                                 |

| 80               | -450                                                                                 |

| 90               | -350                                                                                 |

| 100              | -250                                                                                 |

### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD809 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. A -3-

# **AD809**

#### **DEFINITION OF TERMS**

## Maximum, Minimum and Typical Specifications

Specifications for every parameter are derived from statistical analyses of data taken on multiple devices from multiple wafer lots. Typical specifications are the mean of the distribution of the data for that parameter. If a parameter has a maximum (or a minimum), that value is calculated by adding to (or subtracting from) the mean six times the standard deviation of the distribution. This procedure is intended to tolerate production variations: if the mean shifts by 1.5 standard deviations, the remaining 4.5 standard deviations still provide a failure rate of only 3.4 parts per million. For all tested parameters, the test limits are guardbanded to account for tester variation to thus guarantee that no device is shipped outside of data sheet specifications.

### Capture and Tracking Range

This is the range of input data rates over which the AD809 will remain in lock.

#### **Jitter**

This is the dynamic displacement of digital signal edges from their long term average positions, measured in degrees rms. Jitter on the input clock causes jitter on the synthesized clock.

#### **Output Jitter**

This is the jitter on the synthesized clock (OUTPUT, OUTPUT), in degrees rms.

### Jitter Transfer

The AD809 exhibits a low-pass filter response to jitter applied to its input data.

#### Bandwidth

This describes the frequency at which the AD809 attenuates sinusoidal input jitter by 3 dB.

#### Peaking

This describes the maximum jitter gain of the AD809 in dB.

## Damping Factor, ζ

Damping factor,  $\zeta$  describes the compensation of the second order PLL. A larger value of  $\zeta$  corresponds to more damping and less peaking in the jitter transfer function.

#### **Duty Cycle Tolerance**

The AD809 exhibits a duty cycle tolerance that is measured by applying an input signal (nominal input frequency) with a known duty cycle imbalance and measuring the  $\times 8$  or  $\times 16$  output frequency.

### Symmetry-Recovered Clock Duty Cycle

Symmetry is calculated as (100× on time)/period, where on time equals the time that the clock signal is greater than the midpoint between its "0" level and its "1" level.

# **Typical Characteristic Curves**

Figure 2. Jitter Histogram

Figure 3. Jitter vs. Input Duty Cycle

\_4\_

#### **USING THE AD809**

#### **Ground Planes**

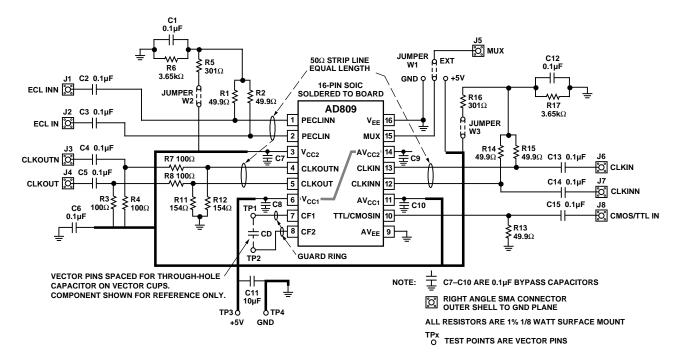

Use of one ground plane for connections to both analog and digital grounds is recommended.

### **Power Supply Connections**

Use of a 10  $\mu$ F capacitor between  $V_{CC}$  and ground is recommended. Care should be taken to isolate the +5 V power trace to  $V_{CC2}$  (Pin 3). The  $V_{CC2}$  pin is used inside the device to provide the CLKOUT/CLKOUTN signals.

Use of a trace connecting Pin 14 and Pin 6 (AV<sub>CC2</sub> and V<sub>CC1</sub> respectively) is recommended. Use of 0.1  $\mu$ F capacitors between IC power supply and ground is recommended. Power supply decoupling should take place as close to the IC as possible. Refer to the schematic, Figure 5, for advised connections.

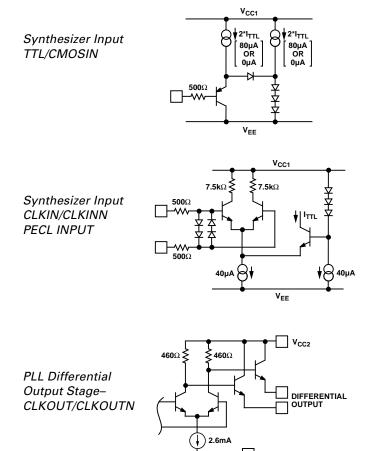

#### **Transmission Lines**

Use of 50  $\Omega$  transmission lines are recommended for PECL inputs.

#### **Terminations**

Termination resistors should be used for PECL input signals. Metal, thick film, 1% tolerance resistors are recommended. Termination resistors for the PECL input signals should be placed as close as possible to the PECL input pins.

Connections from the power supply to load resistors for input and output signals should be individual, not daisy chained. This will avoid crosstalk on these signals.

#### Loop Damping Capacitor, CD

A ceramic capacitor may be used for the loop damping capacitor. A 22 nF capacitor provides a damping factor of 10.

Figure 4. Simplified Schematics

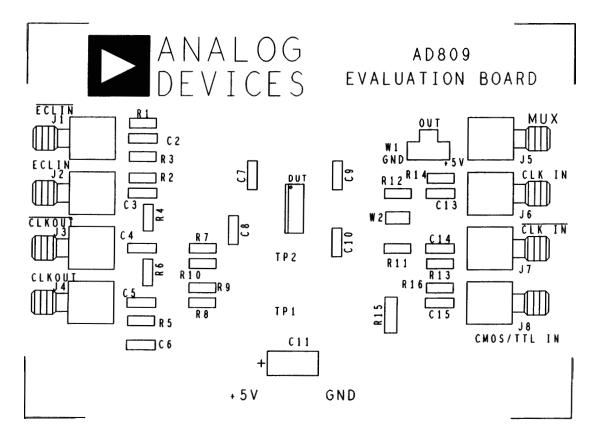

Figure 5. Evaluation Board Schematic

REV. A -5-

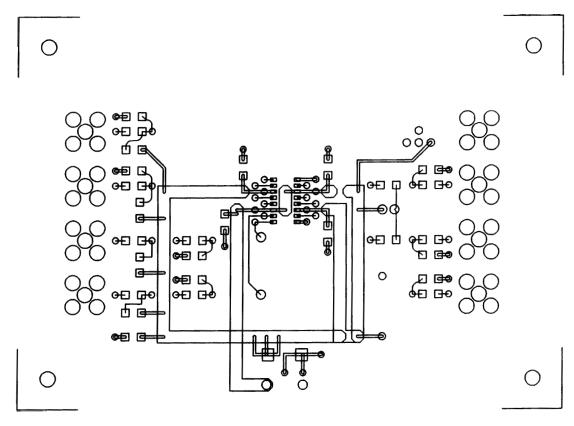

Figure 6. Evaluation Board: Component Side

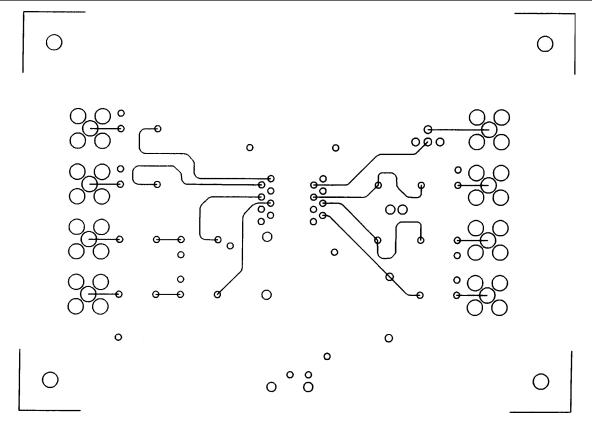

Figure 7. Evaluation Board: Solder Side

Figure 8. Evaluation Board: INT2

REV. A -7-

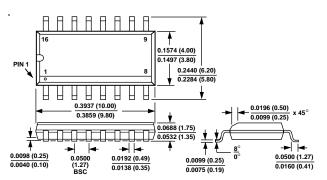

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

# 16-Lead Small Outline IC Package (R-16A)