# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

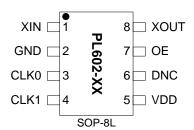

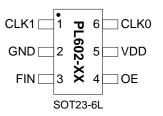

# HCSL Compatible Clock Generator for PCI Express PIN CONFIGURATION

• Input Frequency:

**FEATURES**

- o Fundamental Crystal or Reference Input: 25MHz

- Output Frequency:

- o PL602-21: 100MHz differential outputs.

- o PL602-22: 125MHz differential outputs.

- o PL602-23: 200MHz differential outputs.

- PL602-26: 25MHz differential outputs.

- o PL602-27: 250MHz differential outputs.

- o PL602-15: 156.25 MHz differential outputs.

- Very low Jitter: 28ps Pk-Pk typ.

- Very low Phase Noise:

- o -130 dBc at 10kHz offset at 100MHz

- No external loop filter is required

- Power supply range: 2.25V to 3.63V

- Operating temperature range from -40°C to 85°C

- Available in 6-pin SOT or 8-pin SOP Green/RoHS compliant package.

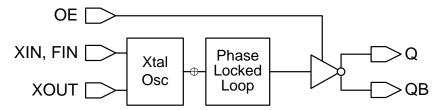

### **DESCRIPTION**

The PL602-XX is the smallest, high performance, lowest power differential output clock IC available for HCSL timing applications. PL602-XX offers -130dBc at 10kHz offset at 100MHz, with a very low jitter (2 ps TIE RMS), making it ideal for HCSL applications requiring small size and low power.

# **BLOCK DIAGRAM**

## PIN DESCRIPTION

| Nome     | Pin # |       | T    | Description                                               |  |

|----------|-------|-------|------|-----------------------------------------------------------|--|

| Name     | SOP   | SOT23 | Type |                                                           |  |

| XIN      | 1     | -     | I    | Crystal input (SOP package only)                          |  |

| FIN      | -     | 3     | I    | Reference clock input (SOT23 package only)                |  |

| GND      | 2     | 2     | Р    | GND connection                                            |  |

| CLK[0:1] | 3,4   | 1,6   | 0    | Differential clock outputs [note:CLK0=~CLK1]              |  |

| VDD      | 5     | 5     | Р    | VDD connection                                            |  |

| DNC      | 6     | -     | -    | Do not connect                                            |  |

| OE       | 7     | 4     | I    | Output enable (OE) input. Internal 60KΩ pull up resistor. |  |

| XOUT     | 8     | -     | 0    | Crystal output pin.                                       |  |

# ELECTRICAL SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                     | SYMBOL   | MIN. | MAX.                 | UNITS |

|--------------------------------|----------|------|----------------------|-------|

| Supply Voltage Range           | $V_{DD}$ | -0.5 | 4.6                  | ٧     |

| Input Voltage Range            | Vı       | -0.5 | V <sub>DD</sub> +0.5 | ٧     |

| Output Voltage Range           | Vo       | -0.5 | V <sub>DD</sub> +0.5 | ٧     |

| Soldering Temperature          |          |      | 260                  | °C    |

| Storage Temperature            | Ts       | -65  | 150                  | °C    |

| Ambient Operating Temperature* |          | -40  | +85                  | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

## **AC SPECIFICATIONS**

| PARAMETERS                                | CONDITIONS                                                                                 | MIN. | TYP. | MAX.     | UNITS |

|-------------------------------------------|--------------------------------------------------------------------------------------------|------|------|----------|-------|

| Crystal Input Frequency                   | Fundamental Crystal                                                                        |      | 25   |          | MHz   |

| Input (F <sub>IN</sub> ) Frequency        |                                                                                            |      | 25   |          | MHz   |

| Input (F <sub>IN</sub> ) Signal Amplitude | Internally AC coupled                                                                      | 0.9  |      | $V_{DD}$ | Vpp   |

| Output Frequency                          |                                                                                            | 25   |      | 200      | MHz   |

| Output Enable Time                        | OE Function; Ta=25° C, Add one clock period to this measurement for a usable clock output. |      |      | 10       | ns    |

| Output Disable Time                       | OE Function; Ta=25° C                                                                      |      |      | 10       | ns    |

| Settling Time                             | At power-up $(V_{DD} \ge 2.25V)$                                                           |      |      | 10       | ms    |

| VDD Sensitivity                           | Frequency vs. V <sub>DD</sub> , ±10%                                                       | -2   |      | 2        | ppm   |

| Output Rise Time                          | 10/90%V <sub>он</sub>                                                                      |      | 0.3  | 0.5      | ns    |

| Output Fall Time                          | 90/10%V <sub>он</sub>                                                                      |      | 0.3  | 0.5      | ns    |

| Skew Between Outputs                      | Measured at 50% V <sub>OH</sub>                                                            |      |      | 250      | ps    |

| Duty Cycle                                | At V <sub>DD</sub> /2                                                                      | 45   | 50   | 55       | %     |

| Period Jitter, peak-to-peak               | With canacitive decoupling between V                                                       |      | 28   |          | ps    |

| Cycle-to-Cycle, RMS                       | - With capacitive decoupling between $V_{\text{DD}}$ and GND                               |      | 9    |          | ps    |

| Cycle-to-Cycle, peak                      | - At 100MHz                                                                                |      | 25   |          | ps    |

| TIE, RMS                                  | - 20,000 samples measured                                                                  |      | 2    |          | ps    |

# **DC SPECIFICATIONS**

| PARAMETERS              | SYMBOL           | CONDITIONS                               | MIN. | TYP. | MAX. | UNITS |

|-------------------------|------------------|------------------------------------------|------|------|------|-------|

| Supply Current, Dynamic | I <sub>DD</sub>  | At 100MHz, No Load                       |      | 25   |      | mA    |

| Operating Voltage       | $V_{DD}$         |                                          | 2.25 |      | 3.63 | V     |

| Output Low Voltage      | V <sub>OL</sub>  | HCSL termination,                        |      |      | 0.05 | V     |

| Output High Voltage     | V <sub>OH</sub>  | $(RS = 150\Omega, RT = 49.9\Omega) 3.3V$ | 0.65 | 0.75 | 0.85 | V     |

| Output Current          | I <sub>OSD</sub> | $(RS = 100\Omega, RT = 49.9\Omega) 2.5V$ | 13   | 15   | 17   | mA    |

# **CRYSTAL SPECIFICATIONS**

| PARAMETERS                               | SYMBOL                | MIN. | TYP. | MAX. | UNITS |

|------------------------------------------|-----------------------|------|------|------|-------|

| Fundamental Crystal Resonator Frequency  | F <sub>XIN</sub>      |      | 25   |      | MHz   |

| Crystal Loading Rating                   | C <sub>L (xtal)</sub> |      | 18   |      | pF    |

| Maximum Sustainable Drive Level          |                       |      |      | 500  | μW    |

| Operating Drive Level                    |                       |      | 100  |      | μW    |

| Crystal Shunt Capacitance                | C0                    |      |      | 6    | pF    |

| Effective Series Resistance, Fundamental | ESR                   |      |      | 45   | Ω     |

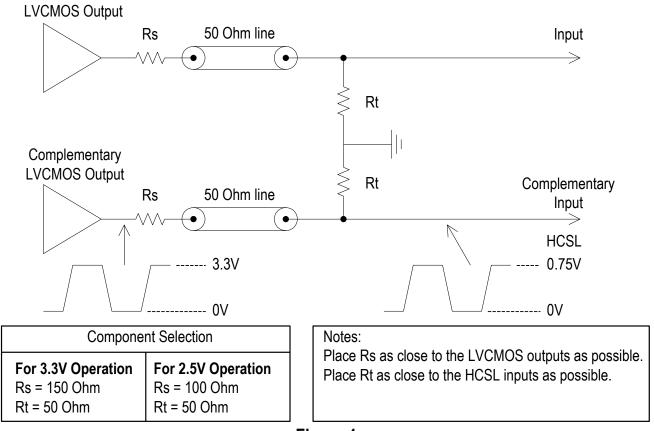

### PCI EXPRESS/HCSL COMPATIBLE LAYOUT GUIDELINES

Figure 1 below describes how to terminate the complementary LVCMOS outputs of PL602-XX for use with HCSL inputs.

Figure 1

## PCB LAYOUT CONSIDERATIONS FOR PERFORMANCE OPTIMIZATION

The following guidelines are to assist you with a performance optimized PCB design:

- Keep all the PCB traces to PL602-XX as short as possible, as well as keeping all other traces as far away from it as possible.

- Place the crystal as close as possible to both crystal pins of the device. This will reduce the cross-talk between the crystal and the other signals.

- Separate crystal pin traces from the other signals on the PCB, but allow ample distance between the two crystal pin traces.

- Place a 0.01µF~0.1µF decoupling capacitor between VDD and GND, on the component side of the PCB, close to the VDD pin. It is not recommended to place this component on the backside of the PCB.

- It is highly recommended to keep the VDD and GND traces as short as possible.

- When connecting long traces (> 1 inch) to a CMOS output, it is important to design the traces as a transmission line or 'stripline', to avoid reflections or ringing. In this case, the CMOS output needs to be matched to the trace impedance. Usually 'striplines' are designed for  $50\Omega$  impedance and CMOS outputs usually have lower than  $50\Omega$  impedance so matching can be achieved by adding a resistor in series with the CMOS output pin to the 'stripline' trace.

# PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

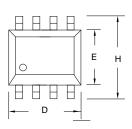

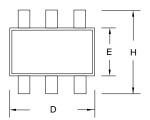

## SOP-8L

| Symbol | Dimension in MM |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min.            | Max. |  |  |

| Α      | 1.35            | 1.75 |  |  |

| A1     | 0.10            | 0.25 |  |  |

| A2     | 1.25            | 1.50 |  |  |

| В      | 0.33            | 0.53 |  |  |

| С      | 0.19            | 0.27 |  |  |

| D      | 4.80            | 5.00 |  |  |

| Е      | 3.80            | 4.00 |  |  |

| Н      | 5.80            | 6.20 |  |  |

| L      | 0.40            | 0.89 |  |  |

| е      | 1.27 BSC        |      |  |  |

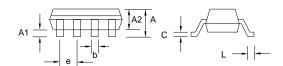

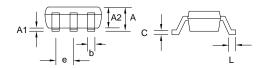

### SOT23-6L

| Cumbal | Dimension in MM |      |  |  |

|--------|-----------------|------|--|--|

| Symbol | Min.            | Max. |  |  |

| Α      | 1.05            | 1.35 |  |  |

| A1     | 0.05            | 0.15 |  |  |

| A2     | 1.00            | 1.20 |  |  |

| В      | 0.30            | 0.50 |  |  |

| С      | 0.08            | 0.20 |  |  |

| D      | 2.80            | 3.00 |  |  |

| Е      | 1.50            | 1.70 |  |  |

| Н      | 2.60            | 3.0  |  |  |

| L      | 0.35            | 0.55 |  |  |

| е      | e 0.95 BS       |      |  |  |

# ORDERING INFORMATION (GREEN PACKAGE COMPLIANT)

## For part ordering, please contact our Sales Department:

2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

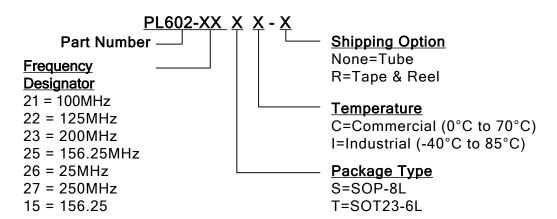

#### PART NUMBER

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

| Part / Order Number | Marking     | Package Option               |

|---------------------|-------------|------------------------------|

| PL602-2XSC          | P602-2X     | 8-Pin SOP (Tube)             |

| PL602-2XSC-R        | SC<br>LLLLL | 8-Pin SOP (Tape and Reel)    |

| PL602-1XTC-R        | F1X<br>LLL  | 6-Pin SOT-23 (Tape and Reel) |

| PL602-2XTC-R        | F2X<br>LLL  | 6-Pin SOT-23 (Tape and Reel) |

Note: LLL / LLLLL designate Production Lot.

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.