# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

## **FEATURES**

- < 0.5ps RMS phase jitter (12kHz to 20MHz) at 622.08MHz

- 25ps max peak to peak period jitter

- Ultra Low-Power Consumption

- < 90mA @622MHz PECL output</li>

- <10 μA at Power Down (PDB) Mode</li>

- Input Frequency:

- Fundamental Crystal: 19MHz to 40MHz

- Output Frequency:

- 19MHz to 800MHz output.

- Output type: LVPECL

- High Linearity VCXO: <10% linearity</li>

- Pullability: ±150 ppm

- Programmable OE input polarity selection.

- Power Supply: 3.3V, ±10%

- Operating Temperature Ranges:

- Commercial: 0°C to 70°C

- Industrial: -40°C to 85°C

- Available in Die or Wafer

## **DESCRIPTION**

The PL585 is a Dual LC core monolithic IC clock, capable of maintaining sub-picoseconds RMS phase jitter, while covering a wide frequency output range up to 800MHz, without the use of external components. The high performance and high frequency output is achieved using a low cost fundamental crystal of between 19MHz and 40 MHz. The PL585 is designed to address the demanding requirements of high performance applications such as Fiber Channel, serial ATA, Ethernet, SAN, SONET/SDH, etc.

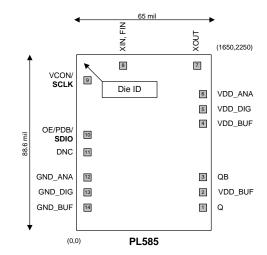

## PIN CONFIGURATION

## **DIE SPECIFICATIONS**

| Name           | Value                 |

|----------------|-----------------------|

| Size           | 65 x 88.6 mil         |

| Reverse side   | GND                   |

| Pad dimensions | 80 micron x 80 micron |

| Thickness      | 8 mils                |

## **OUTPUT ENABLE CONTROL**

| OE Select<br>(Programmable) | OE          | State          |

|-----------------------------|-------------|----------------|

| 0                           | 0 (Default) | Output enabled |

| U                           | 1           | Tri-state      |

| 1 (Default)                 | 0           | Tri-state      |

| 1 (Default)                 | 1 (Default) | Output enabled |

## **BLOCK DIAGRAM**

## **PAD ASSIGNMENT**

| Name        | Pad # | X (μm) | Υ (μm) | Description                                                                                                                                                                                                                                                  |

|-------------|-------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q           | 1     | 1551   | 220    | Output buffer                                                                                                                                                                                                                                                |

| VDD_BUF     | 2     | 1551   | 448    | VDD connection for buffer circuitry                                                                                                                                                                                                                          |

| QB          | 3     | 1551   | 676    | Output buffer                                                                                                                                                                                                                                                |

| VDD_BUF     | 4     | 1551   | 1390   | VDD connection for buffer circuitry                                                                                                                                                                                                                          |

| VDD_DIG     | 5     | 1551   | 1552   | VDD connection for digital circuitry                                                                                                                                                                                                                         |

| VDD_ANA     | 6     | 1551   | 1790   | VDD connection for analog circuitry                                                                                                                                                                                                                          |

| XOUT        | 7     | 1503   | 2156   | Output connection to crystal                                                                                                                                                                                                                                 |

| XIN         | 8     | 630    | 2156   | Crystal input connection                                                                                                                                                                                                                                     |

| VCON/SCLK   | 9     | 99     | 2060   | Analog voltage pin for the VCXO. The serial interface uses this pin for the serial clock input (SCLK), during programming.                                                                                                                                   |

| OE/PDB/SDIO | 10    | 99     | 1256   | This pin may be programmed as output enable (OE), or power-down (PDB) pin. The serial interface uses this pin for the serial data input (SDIO) during programming. This pin incorporates an Internal pull-up resistor of $60K\Omega$ for OE, PDB operations. |

| DNC         | 11    | 99     | 970    | Do not connect                                                                                                                                                                                                                                               |

| GND_ANA     | 12    | 99     | 700    | GND connection for analog circuitry                                                                                                                                                                                                                          |

| GND_DIG     | 13    | 99     | 532    | GND connection for digital circuitry                                                                                                                                                                                                                         |

| GND_BUF     | 14    | 99     | 364    | GND connection for buffer circuitry                                                                                                                                                                                                                          |

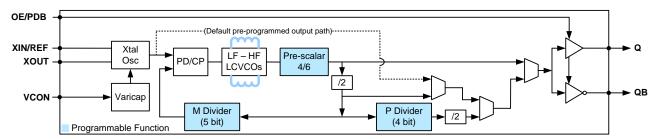

## **FUNCTIONAL DESCRIPTION**

PL585 family of products is an advanced, programmable LCVCO clock IC that is designed to meet the most stringent performance specifications for phase noise, jitter, and power consumption.

There are two main types of VCOs, a) Ring Oscillator, b) LC Tank oscillator. An LCVCO is made up of an LC tank oscillator. Although a Ring Oscillator has very good performance, and has a good tuning range, its phase noise and jitter performance, in particular at higher frequencies, degrades.

On the other hand, an LCVCO has an outstanding phase noise and jitter performance, even at higher frequencies. PL585 family of products takes advantage of this state of the art technology, and incorporates the LC tank on-chip, for optimal performance.

PL585 family of products exhibit very low phase noise/phase jitter and peak to peak jitter, wide tuning range, and very low-power. All members of the PL585 family accept a low-cost fundamental crystal input of 19MHz to 40MHz, and its flexible

core is capable of producing any output frequency between 19MHz to 800MHz.

## **PLL Programming**

The PLL in the PL585 family is fully programmable. The PLL is equipped with a Pre-Scalar to divide down the VCO frequency, and a 5-bit VCO frequency feedback loop divider (M-Counter). The output of the PLL is transferred to a 4-bit post VCO divider (P-Counter), to achieve the desired output frequency.

## **OE (Output Enable)**

The OE pin in PL585 family, through programming, can be configured to support OE pin activation with a logic '1' or logic '0', to provide you with the desired enable polarity.

| OE Select<br>(Programmable) | OE          | State          |

|-----------------------------|-------------|----------------|

| 0                           | 0 (Default) | Output enabled |

| U                           | 1           | Tri-state      |

| 1 (Default)                 | 0           | Tri-state      |

| 1 (Default)                 | 1 (Default) | Output enabled |

The OE pin incorporates a  $60 \text{K}\Omega$  resistor to either pull-up or pull-down to the default state, when the OE pad is left open.

## **ELECTRICAL SPECIFICATIONS**

## 1. ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                                              | SYMBOL   | MIN  | MAX                  | UNITS |

|---------------------------------------------------------|----------|------|----------------------|-------|

| Supply Voltage                                          | $V_{DD}$ |      | 4.6                  | V     |

| Input Voltage, dc                                       | Vı       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage                                          | Vo       | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Storage Temperature                                     | Ts       | -65  | 150                  | °C    |

| Ambient Operating Temperature (industrial temperature)* | $T_Al$   | -40  | 85                   | °C    |

| Ambient Operating Temperature (commercial temperature)  | $T_{AC}$ | 0    | 70                   | °C    |

| Junction Temperature                                    | TJ       |      | 125                  | °C    |

| ESD Protection, Machine Model                           |          | 200  |                      | V     |

| ESD Protection, Human Body Model                        |          | 2    |                      | kV    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied.

## 2. GENERAL ELECTRICAL SPECIFICATIONS

| PARAMETERS                          | SYMBOL          | CONDITIONS                                                                                                    | MIN  | TYP | MAX  | UNITS |

|-------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Supply Current, Dynamic             | $I_{DDQ}$       | LVPECL, 622.08MHz, 3.3V                                                                                       |      |     | 90   | mA    |

| Supply Current, Dynamic PDB Enabled |                 | PDB = 0, 3.3V                                                                                                 |      |     | 10   | uA    |

| Output Enable Time                  | toE             | OE logic 0 to logic 1, Ta=25° C.<br>Add one clock period to this<br>measurement for a usable clock<br>output. |      |     | 50   | ns    |

| Power Up Time                       | $T_PU$          | PDB logic 0 to logic 1, Ta=25° C.                                                                             |      |     | 10   | ms    |

| Operating Voltage                   | $V_{DD}$        |                                                                                                               | 2.97 | 3.3 | 3.63 | V     |

| Power Up Ramp Rate                  | t <sub>PU</sub> | Time for $V_{DD}$ to reach 90% $V_{DD}$ . Power ramp must be monotonic.                                       | 0.1  |     | 100  | ms    |

| Auto-Calibration Time               | t <sub>AC</sub> | At power up                                                                                                   |      |     | 10   | ms    |

| Output Clock Duty Cycle             |                 | @ V <sub>DD</sub> – 1.3V                                                                                      | 45   | 50  | 55   | %     |

<sup>\*</sup>Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

## 3. VOLTAGE CONTROLLED CRYSTAL OSCILLATOR

| PARAMETERS                 | SYMBOL | CONDITIONS                                                                                    | MIN  | TYP | MAX | UNITS |

|----------------------------|--------|-----------------------------------------------------------------------------------------------|------|-----|-----|-------|

| VCXO Pullability           |        | VCON=1.65V, $\pm 1.65$ V<br>XTAL C <sub>1</sub> >10fF and C <sub>0</sub> /C <sub>1</sub> <250 | ±150 |     |     | ppm   |

| VCXO Tuning Characteristic |        |                                                                                               |      | 100 |     | ppm/V |

| Pull Range Linearity       |        |                                                                                               |      |     | 10  | %     |

| VCON Pin Input Impedance   |        |                                                                                               | 10   |     |     | МΩ    |

| VCON Modulation BW         |        | $0V \le VCON \le 3.3V$ , $-3dB$                                                               | 18   |     |     | kHz   |

## 4. CRYSTAL SPECIFICATIONS

| PARAMETERS                  | SYMBOL                         | CONDITIONS                           | MIN | TYP | MAX | UNITS |

|-----------------------------|--------------------------------|--------------------------------------|-----|-----|-----|-------|

| Crystal Resonator Frequency | F <sub>XIN</sub>               | Parallel Fundamental Mode            | 19  |     | 40  | MHz   |

| Crystal Cload               | C <sub>L_Crystal</sub>         | V <sub>DD</sub> = 3.3V, VCON = 1.65V |     | 8.5 |     |       |

| Shunt Capacitance           | C <sub>0_Crystal</sub>         |                                      |     |     | 3.5 | pF    |

| Crystal Pullability         | C <sub>0</sub> /C <sub>1</sub> | AT cut                               | 250 |     |     |       |

| Recommended ESR             | R <sub>E</sub>                 | AT cut                               |     |     | 50  | Ω     |

## 5. JITTER SPECIFICATIONS

| PARAMETERS              | FREQUENCY | CONDITIONS                   | MIN | TYP | MAX | UNITS |

|-------------------------|-----------|------------------------------|-----|-----|-----|-------|

| RMS Phase Jitter        | 622.08MHz | 10kHz to 20MHz, XIN=38.88MHz |     | 0.5 |     | ps    |

| Period Jitter, Pk-to-Pk | 622.08MHz | 10K cycles, XIN=38.88MHz     |     | 25  |     | ps    |

## 6. PHASE NOISE SPECIFICATIONS

| PARAMETERS            | Freq.<br>(MHz) | @<br>10Hz | @<br>100Hz | @<br>1KHz | @<br>10KHz | @<br>100KHz | @<br>1MHz | @<br>10MHz | UNITS  |

|-----------------------|----------------|-----------|------------|-----------|------------|-------------|-----------|------------|--------|

| Phase Noise, relative | 155.52         | -56       | -86        | -112      | -123       | -127        | 136       | 147        | dBc/Hz |

| to carrier (typical)  | 622.08         | -47       | -77        | -101      | -111       | -114        | -127      | -145       | UDC/HZ |

Note: Phase Noise measured at VCON = 1.65V

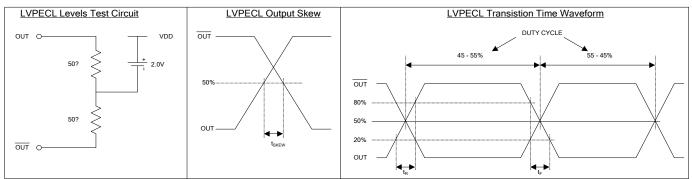

## 7. LVPECL OUTPUTS (Q, QB)

| PARAMETERS              | SYMBOL          | CONDITIONS                                          | MIN   | TYP   | MAX   | UNITS |

|-------------------------|-----------------|-----------------------------------------------------|-------|-------|-------|-------|

| Output High Voltage     | V <sub>OH</sub> | Q, QB                                               | 2.275 | 2.350 | 2.420 | V     |

| Output Low Voltage      | V <sub>OL</sub> | Standard LVPECL Termination, V <sub>DD</sub> = 3.3V | 1.490 | 1.600 | 1.680 | V     |

| Output Frequency        | Fout            | 3.3V                                                | 19    |       | 800   | MHz   |

| Output Rise, Fall Times | $t_r$ , $t_f$   | 20% - 80% of Q <sub>pp</sub> /QB <sub>pp</sub>      |       | 200   | 300   | ns    |

| Output Voltage Swing    | $V_{pp}$        | Q, QB                                               | 550   | 800   | 900   | mV    |

## ORDERING INFORMATION

## For part ordering, please contact our Sales Department:

2180 Fortune Drive, San Jose, CA 95131, USA Tel: (408) 944-0800 Fax: (408) 474-1000

## **PART NUMBER**

The order number for this device is a combination of the following: Part number, Package type, Thickness and Operating temperature range

Part Number

Packaging Option

D = Die

W = Wafer

PL585-88 XX

Temperature Range

C=Commercial (0°C to 70°C)

| Order Number P/N | Output<br>Frequency Range | Packaging Option  |

|------------------|---------------------------|-------------------|

| PECL             |                           |                   |

| PL585-88DC       | ≤800MHz                   | Waffle Pack (Die) |

|                  |                           |                   |

| PL585-88WC       | ≤800MHz                   | Wafer             |

Micrel Inc., reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Micrel is believed to be accurate and reliable. However, Micrel makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: Micrel's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of Micrel Inc.