# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

# DS1244/DS1244P 256K NV SRAM with Phantom Clock

#### **FEATURES**

- Real-Time Clock (RTC) Keeps Track of Hundredths of Seconds, Minutes, Hours, Days, Date of the Month, Months, and Years

- 32K x 8 NV SRAM Directly Replaces Volatile Static RAM or EEPROM

- Embedded Lithium Energy Cell Maintains Calendar Operation and Retains RAM Data

- Watch Function is Transparent to RAM Operation

- Automatic Leap Year Compensation Valid Up to 2100

- Full 10% Operating Range

- Over 10 Years of Data Retention in the Absence of Power

- Lithium Energy Source is Electrically Disconnected to Retain Freshness Until Power is Applied for the First Time

- DIP Module Only

- Standard 28-Pin JEDEC Pinout

- PowerCap Module Board Only

- Surface Mountable Package for Direct Connection to PowerCap Containing Battery and Crystal

- Replaceable Battery (PowerCap)

- Pin-for-Pin Compatible with DS1248P and DS1251P

- Underwriters Laboratories (UL) Recognized

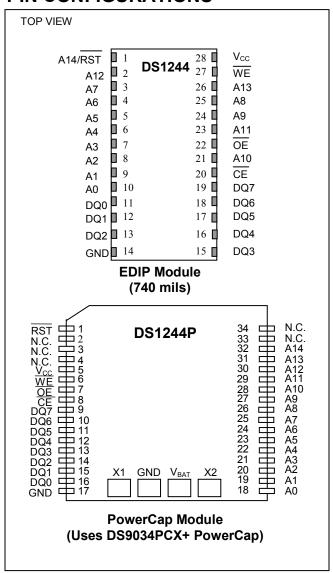

#### **PIN CONFIGURATIONS**

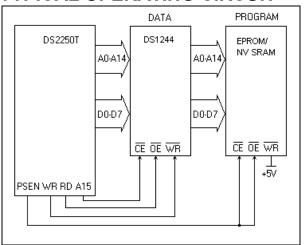

# TYPICAL OPERATING CIRCUIT

### **ORDERING INFORMATION**

| PART             | TEMP RANGE     | PIN-PACKAGE      | VOLTAGE<br>(V) |

|------------------|----------------|------------------|----------------|

| DS1244W-120+     | 0°C to +70°C   | 28 EDIP (0.740a) | 3.3            |

| DS1244W-120IND+  | -40°C to +85°C | 28 EDIP (0.740a) | 3.3            |

| DS1244WP-120+    | 0°C to +70°C   | 34 PowerCap*     | 3.3            |

| DS1244WP-120IND+ | -40°C to +85°C | 34 PowerCap*     | 3.3            |

| DS1244Y-70+      | 0°C to +70°C   | 28 EDIP (0.740a) | 5.0            |

| DS1244YP-70+     | 0°C to +70°C   | 34 PowerCap*     | 5.0            |

$<sup>+</sup>Denotes\ a\ lead (Pb)-free/RoHS-compliant\ device.$   $*DS9034PCX+\ or\ DS9034I-PCX+\ (PowerCap)\ required.\ (Must\ be\ ordered\ separately.)$

### **PIN DESCRIPTION**

| PIN  |                    |                       | DUNCTION                                                                                                                                       |  |  |  |  |

|------|--------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| EDIP | PowerCap           | NAME                  | FUNCTION                                                                                                                                       |  |  |  |  |

| 1    | 1                  | A14/RST               | Address Input/Active-Low Reset Input. This pin has an internal pullup resistor connected to $V_{\text{CC}}$ . A14 address on the EDIP package. |  |  |  |  |

| 1    | 32                 | A14                   |                                                                                                                                                |  |  |  |  |

| 2    | 30                 | A12                   |                                                                                                                                                |  |  |  |  |

| 3    | 25                 | A7                    |                                                                                                                                                |  |  |  |  |

| 4    | 24                 | A6                    |                                                                                                                                                |  |  |  |  |

| 5    | 23                 | A5                    |                                                                                                                                                |  |  |  |  |

| 6    | 22                 | A4                    |                                                                                                                                                |  |  |  |  |

| 7    | 21                 | A3                    |                                                                                                                                                |  |  |  |  |

| 8    | 20                 | A2                    | Address Inputs                                                                                                                                 |  |  |  |  |

| 9    | 19                 | A1                    |                                                                                                                                                |  |  |  |  |

| 10   | 18                 | A0                    |                                                                                                                                                |  |  |  |  |

| 21   | 28                 | A10                   |                                                                                                                                                |  |  |  |  |

| 23   | 29                 | A11                   |                                                                                                                                                |  |  |  |  |

| 24   | 27                 | A9                    |                                                                                                                                                |  |  |  |  |

| 25   | 26                 | A8                    |                                                                                                                                                |  |  |  |  |

| 26   | 31                 | A13                   |                                                                                                                                                |  |  |  |  |

| 11   | 16                 | DQ0                   |                                                                                                                                                |  |  |  |  |

| 12   | 15                 | DQ1                   |                                                                                                                                                |  |  |  |  |

| 13   | 14                 | DQ2                   |                                                                                                                                                |  |  |  |  |

| 15   | 13                 | DQ3                   | Data In/Data Out                                                                                                                               |  |  |  |  |

| 16   | 12                 | DQ4                   |                                                                                                                                                |  |  |  |  |

| 17   | 11                 | DQ5                   |                                                                                                                                                |  |  |  |  |

| 18   | 10                 | DQ6                   |                                                                                                                                                |  |  |  |  |

| 19   | 9                  | DQ7                   |                                                                                                                                                |  |  |  |  |

| 20   | 8                  | <del>CE</del>         | Active-Low Chip-Enable Input                                                                                                                   |  |  |  |  |

| 22   | 7                  | ŌĒ                    | Active-Low Output-Enable Input                                                                                                                 |  |  |  |  |

| 27   | 6                  | $\overline{	ext{WE}}$ | Active-Low Write-Enable Input                                                                                                                  |  |  |  |  |

|      | 2, 3, 4, 33,<br>34 | N.C.                  | No Connection                                                                                                                                  |  |  |  |  |

| 28   | 5                  | $V_{CC}$              | Power-Supply Input                                                                                                                             |  |  |  |  |

| 14   | 17                 | GND                   | Ground                                                                                                                                         |  |  |  |  |

#### DESCRIPTION

The DS1244 256K NV SRAM with a Phantom clock is a fully static nonvolatile RAM (NV SRAM) (organized as 32K words by 8 bits) with a built-in real-time clock. The DS1244 has a self-contained lithium energy source and control circuitry, which constantly monitors  $V_{CC}$  for an out-of-tolerance condition. When such a condition occurs, the lithium energy source is automatically switched on and write protection is unconditionally enabled to prevent garbled data in both the memory and real-time clock.

The phantom clock provides timekeeping information for hundredths of seconds, seconds, minutes, hours, days, date, months, and years. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including correction for leap years. The phantom clock operates in either 24-hour or 12-hour format with an AM/PM indicator.

#### **PACKAGES**

The DS1244 is available in two packages: 28-pin encapsulated DIP and 34-pin PowerCap module. The 28-pin DIP-style module integrates the crystal, lithium energy source, and silicon all in one package. The 34-pin PowerCap module board is designed with contacts for connection to a separate PowerCap (DS9034PCX) that contains the crystal and battery. This design allows the PowerCap to be mounted on top of the DS1244P after the completion of the surface mount process. Mounting the PowerCap after the surface mount process prevents damage to the crystal and battery due to the high temperatures required for solder reflow. The PowerCap is keyed to prevent reverse insertion. The PowerCap module board and PowerCap are ordered separately and shipped in separate containers. The part number for the PowerCap is DS9034PCX.

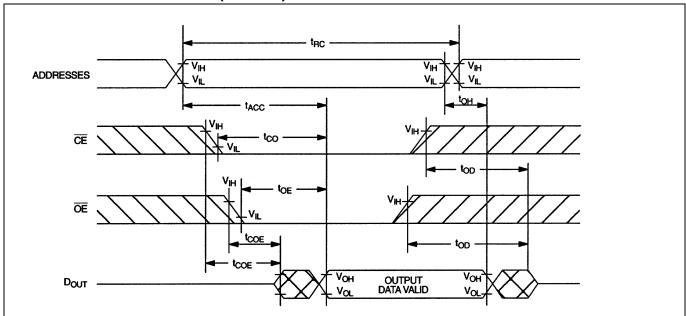

#### RAM READ MODE

The DS1244 executes a read cycle whenever  $\overline{WE}$  (write enable) is inactive (high) and  $\overline{CE}$  (chip enable) is active (low). The unique address specified by the 15 address inputs (A0–A14) defines which of the 32,768 bytes of data is to be accessed. Valid data is available to the eight data-output drivers within  $t_{ACC}$  (access time) after the last address input signal is stable, providing that  $\overline{CE}$  and  $\overline{OE}$  (output enable) access times and states are also satisfied. If  $\overline{OE}$  and  $\overline{CE}$  access times are not satisfied, then data access must be measured from the later occurring signal ( $\overline{CE}$  or  $\overline{OE}$ ) and the limiting parameter is either  $t_{CO}$  for  $\overline{CE}$  or  $t_{OE}$  for  $\overline{OE}$ , rather than address access.

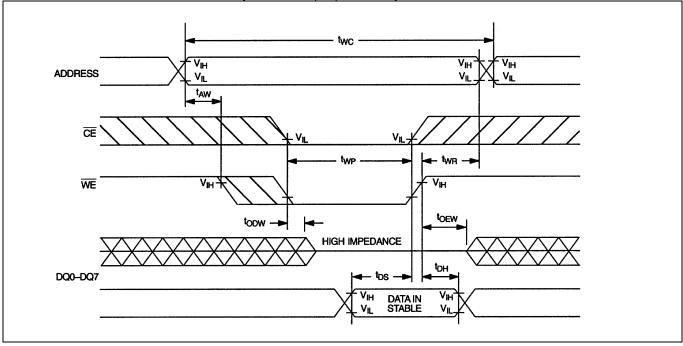

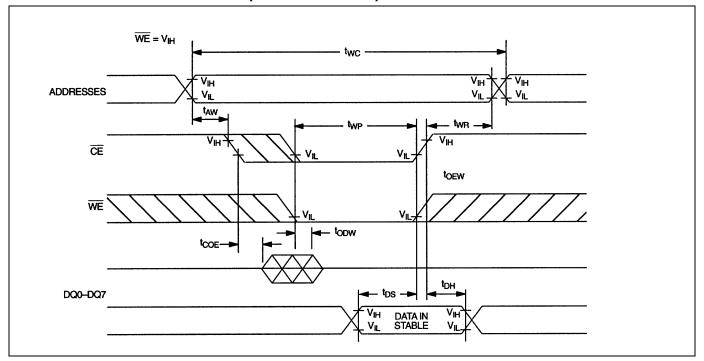

#### **RAM WRITE MODE**

The DS1244 is in the write mode whenever the  $\overline{WE}$  and  $\overline{CE}$  signals are in the active (low) state after address inputs are stable. The latter occurring falling edge of  $\overline{CE}$  or  $\overline{WE}$  will determine the start of the write cycle. The write cycle is terminated by the earlier rising edge of  $\overline{CE}$  or  $\overline{WE}$ . All address inputs must be kept valid throughout the write cycle.  $\overline{WE}$  must return to the high state for a minimum recovery time ( $t_{WR}$ ) before another cycle can be initiated. The  $\overline{OE}$  control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output bus has been enabled ( $\overline{CE}$  and  $\overline{OE}$  active) then  $\overline{WE}$  will disable the outputs in  $t_{ODW}$  from its falling edge.

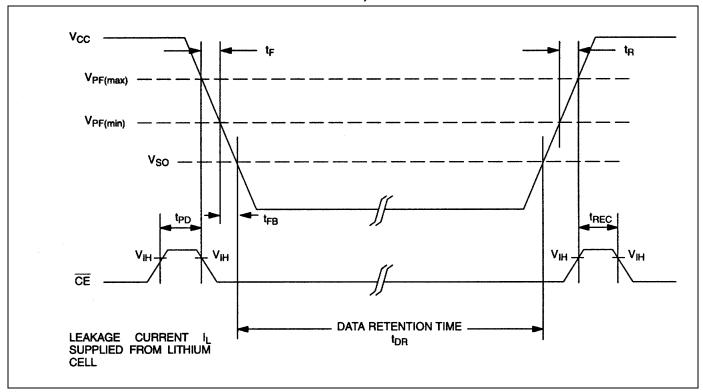

#### DATA RETENTION MODE

The 5V device is fully accessible and data can be written or read only when  $V_{CC}$  is greater than  $V_{PF}$ . However, when  $V_{CC}$  is below the power fail point,  $V_{PF}$  (point at which write protection occurs), the internal clock registers and SRAM are blocked from any access. When  $V_{CC}$  falls below the battery switch point,  $V_{SO}$  (battery supply level), device power is switched from the  $V_{CC}$  pin to the backup battery. RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels.

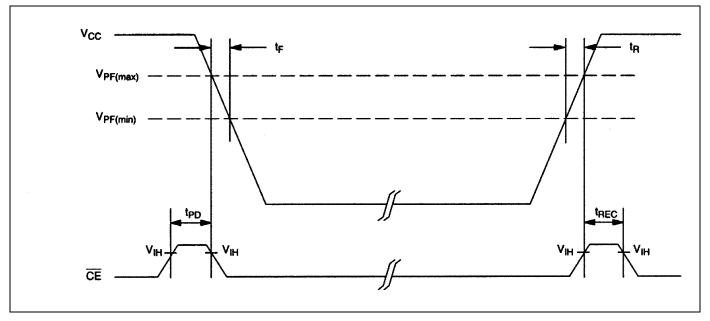

The 3.3V device is fully accessible and data can be written or read only when  $V_{CC}$  is greater than  $V_{PF}$ . When  $V_{CC}$  fall as below the  $V_{PF}$ , access to the device is inhibited. If  $V_{PF}$  is less than  $V_{BAT}$ , the device power is switched from  $V_{CC}$  to the backup supply  $(V_{BAT})$  when  $V_{CC}$  drops below  $V_{PF}$ . If  $V_{PF}$  is greater than  $V_{BAT}$ , the device power is switched from  $V_{CC}$  to the backup supply  $(V_{BAT})$  when  $V_{CC}$  drops below  $V_{BAT}$ . RTC operation and SRAM data are maintained from the battery until  $V_{CC}$  is returned to nominal levels.

All control, data, and address signals must be powered down when V<sub>CC</sub> is powered down.

#### PHANTOM CLOCK OPERATION

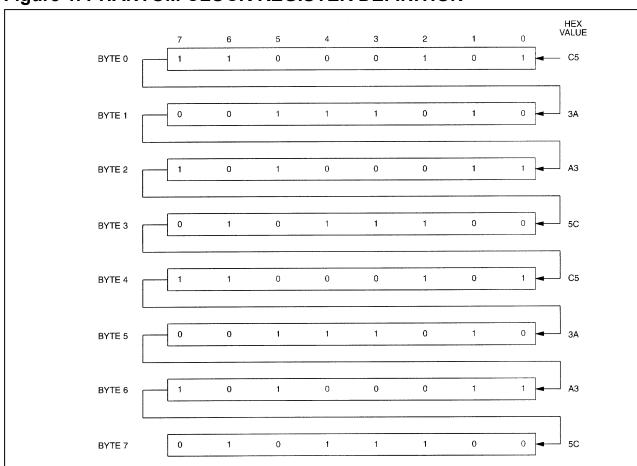

Communication with the phantom clock is established by pattern recognition on a serial bit stream of 64 bits, which must be matched by executing 64 consecutive write cycles containing the proper data on DQ0. All accesses that occur prior to recognition of the 64-bit pattern are directed to memory.

After recognition is established, the next 64 read or write cycles either extract or update data in the phantom clock, and memory access is inhibited.

Data transfer to and from the timekeeping function is accomplished with a serial bit stream under control of the chip enable, output enable, and write enable. Initially, a read cycle to any memory location using the CE and OE control of the phantom clock starts the pattern recognition sequence by moving a pointer to the first bit of the 64-bit comparison register. Next, 64 consecutive write cycles are executed using the CE and WE control of the SmartWatch. These 64 write cycles are used only to gain access to the phantom clock. Therefore, any address to the memory in the socket is acceptable. However, the write cycles generated to gain access to the phantom clock are also writing data to a location in the mated RAM. The preferred way to manage this requirement is to set aside just one address location in RAM as a phantom clock scratch pad. When the first write cycle is executed, it is compared to bit 0 of the 64-bit comparison register. If a match is found, the pointer increments to the next location of the comparison register and awaits the next write cycle. If a match is not found, the pointer does not advance and all subsequent write cycles are ignored. If a read cycle occurs at any time during pattern recognition, the present sequence is aborted and the comparison register pointer is reset. Pattern recognition continues for a total of 64 write cycles as described above until all the bits in the comparison register have been matched (Figure 1). With a correct match for 64 bits, the phantom clock is enabled and data transfer to or from the timekeeping registers can proceed. The next 64 cycles will cause the phantom clock to either receive or transmit data on DQ0, depending on the level of the OE pin or the WE pin. Cycles to other locations outside the memory block can be interleaved with CE cycles without interrupting the pattern recognition sequence or data transfer sequence to the phantom clock.

#### PHANTOM CLOCK REGISTER INFORMATION

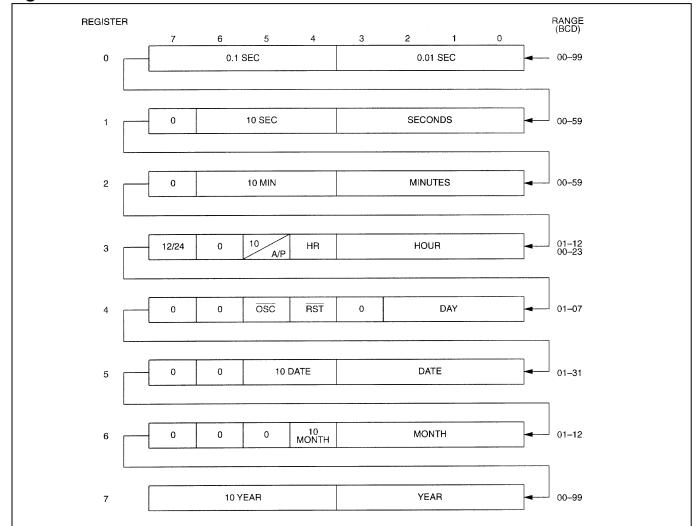

The phantom clock information is contained in eight registers of 8 bits, each of which is sequentially accessed 1 bit at a time after the 64-bit pattern recognition sequence has been completed. When updating the phantom clock registers, each register must be handled in groups of 8 bits. Writing and reading individual bits within a register could produce erroneous results. These read/write registers are defined in Figure 2.

Data contained in the phantom clock register is in binary coded decimal (BCD) format. Reading and writing the registers is always accomplished by stepping through all eight registers, starting with bit 0 of register 0 and ending with bit 7 of register 7.

Figure 1. PHANTOM CLOCK REGISTER DEFINITION

**NOTE**: THE PATTERN RECOGNITION IN HEX IS C5, 3A, A3, 5C, C5, 3A, A3, 5C. THE ODDS OF THIS PATTERN BEING ACCIDENTALLY DUPLICATED AND CAUSING INADVERTENT ENTRY TO THE PHANTOM CLOCK IS LESS THAN 1 IN 10<sup>19</sup>. THIS PATTERN IS SENT TO THE PHANTOM CLOCK LSB TO MSB.

Figure 2. PHANTOM CLOCK REGISTER DEFINITION

#### **AM/PM/12/24 MODE**

Bit 7 of the hours register is defined as the 12-hour or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the 20-hour bit (20–23 hours).

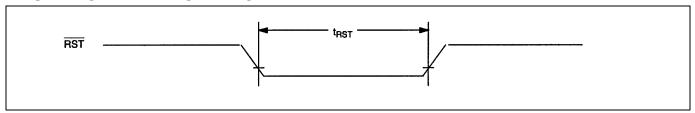

#### OSCILLATOR AND RESET BITS

Bits 4 and 5 of the day register are used to control the RESET and oscillator functions. Bit 4 controls the RESET (pin 1). When the RESET bit is set to logic 1, the RESET input pin is ignored. When the RESET bit is set to logic 0, a low input on the RESET pin will cause the phantom clock to abort data transfer without changing data in the watch registers. Bit 5 controls the oscillator. When set to logic 1, the oscillator is off. When set to logic 0, the oscillator turns on and the watch becomes operational. These bits are shipped from the factory set to a logic 1.

#### **ZERO BITS**

Registers 1, 2, 3, 4, 5, and 6 contain one or more bits that always read logic 0. When writing these locations, either a logic 1 or 0 is acceptable.

#### **BATTERY LONGEVITY**

The DS1244 has a lithium power source that is designed to provide energy for clock activity and clock and RAM data retention when the  $V_{CC}$  supply is not present. The capability of this internal power supply is sufficient to power the DS1244 continuously for the life of the equipment in which it is installed. For specification purposes, the life expectancy is 10 years at +25°C with the internal clock oscillator running in the absence of  $V_{CC}$  power. Each DS1244 is shipped from Maxim with its lithium energy source disconnected, guaranteeing full energy capacity. When  $V_{CC}$  is first applied at a level greater than  $V_{PF}$ , the lithium energy source is enabled for battery-backup operation. Actual life expectancy of the DS1244 will be much longer than 10 years since no lithium battery energy is consumed when  $V_{CC}$  is present.

See "Conditions of Acceptability" at www.maxim-ic.com/TechSupport/QA/ntrl.htm.

#### **CLOCK ACCURACY (DIP MODULE)**

The DS1244 is guaranteed to keep time accuracy to within  $\pm 1$  minute per month at  $\pm 25$ °C. The clock is calibrated at the factory by Maxim using special calibration nonvolatile tuning elements and does not require additional calibration. For this reason, methods of field clock calibration are not available and not necessary.

#### **CLOCK ACCURACY (POWERCAP MODULE)**

The DS1244P and DS9034PCX are each individually tested for accuracy. Once mounted together, the module will typically keep time accuracy to within  $\pm 1.53$  minutes per month (35ppm) at  $\pm 25$ °C.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin Relative to Ground | (5V product)0.3V   | V to +6.0V |

|---------------------------------------------|--------------------|------------|

|                                             | (3.3V product)0.3V | 7 to +4.6V |

| Storage Temperature Range                   |                    |            |

| EDIP                                        | 40°C               | C to +85°C |

| PowerCap                                    | 55°C               | to +125°C  |

| Lead Temperature (soldering, 10 seconds)    |                    |            |

| Note: EDIP is wave or hand-soldered only    | 7.                 |            |

| Soldering Temperature (reflow, PowerCap)    |                    | +260°C     |

This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time can affect reliability.

#### **OPERATING RANGE**

| RANGE      | TEMP RANGE (NONCONDENSING) | $\mathbf{V}_{\mathbf{CC}}$       |

|------------|----------------------------|----------------------------------|

| Commercial | 0°C to +70°C               | $3.3V \pm 10\%$ or $5V \pm 10\%$ |

| Industrial | -40°C to +85°C             | $3.3V \pm 10\%$ or $5V \pm 10\%$ |

### **RECOMMENDED OPERATING CONDITIONS**

Over the operating range

| PAR             | RAMETER                  | SYMBOL          | MIN  | TYP | MAX            | UNITS | NOTES |

|-----------------|--------------------------|-----------------|------|-----|----------------|-------|-------|

| Input Logic 1   | $V_{CC} = 5V \pm 10\%$   | V               | 2.2  |     | $V_{CC} + 0.3$ | V     | 1.1   |

| Input Logic 1   | $V_{CC} = 3.3V \pm 10\%$ | V <sub>IH</sub> | 2.0  |     | $V_{CC} + 0.3$ | ] V   | 11    |

| Innut I agia () | $V_{CC} = 5V \pm 15\%$   | V               | -0.3 |     | 0.8            | V     | 11    |

| Input Logic 0   | $V_{CC} = 3.3V \pm 10\%$ | $ m V_{IL}$     | -0.3 |     | 0.6            | V     | 11    |

### DC ELECTRICAL CHARACTERISTICS

Over the operating range (5V)

| PARAMETER                                             | SYMBOL         | MIN  | TYP       | MAX  | UNITS  | NOTES |

|-------------------------------------------------------|----------------|------|-----------|------|--------|-------|

| Input Leakage Current                                 | $I_{IL}$       | -1.0 |           | +1.0 | μΑ     | 12    |

| I/O Leakage Current                                   | $I_{IO}$       | -1.0 |           | +1.0 | μA     |       |

| $CE \ge V_{IH} \le V_{CC}$                            | -10            |      |           |      | P** 2  |       |

| Output Current at 2.4V                                | $I_{OH}$       | -1.0 |           |      | mA     |       |

| Output Current at 0.4V                                | $I_{OL}$       | 2.0  |           |      | mA     |       |

| Standby Current $\overline{\text{CE}} = 2.2\text{V}$  | $I_{CCS1}$     |      | 5         | 10   | mA     |       |

| Standby Current                                       | $I_{CCS2}$     |      | 3.0       | 5.0  | mA     |       |

| $\overline{\text{CE}} = V_{\text{CC}} - 0.5 \text{V}$ | ICCS2          |      | 5.0       | 5.0  | 1117 1 |       |

| Operating Current $t_{CYC} = 70$ ns                   | $I_{CC01}$     |      |           | 85   | mA     |       |

| Write Protection Voltage                              | $V_{	ext{PF}}$ | 4.25 | 4.37      | 4.50 | V      | 11    |

| Battery Switchover Voltage                            | $V_{SO}$       |      | $V_{BAT}$ |      | V      | 11    |

### DC ELECTRICAL CHARACTERISTICS

### Over the operating range (3.3V)

| PARAMETER                                                  | SYMBOL            | MIN  | TYP                   | MAX  | UNITS | NOTES |

|------------------------------------------------------------|-------------------|------|-----------------------|------|-------|-------|

| Input Leakage Current                                      | $I_{\mathrm{IL}}$ | -1.0 |                       | +1.0 | μΑ    | 12    |

| I/O Leakage Current                                        | т                 | 1.0  |                       | +1.0 |       |       |

| $\overline{\text{CE}} \ge V_{\text{IH}} \le V_{\text{CC}}$ | $I_{IO}$          | -1.0 |                       | +1.0 | μΑ    |       |

| Output Current at 2.4V                                     | $I_{OH}$          | -1.0 |                       |      | mA    |       |

| Output Current at 0.4V                                     | $I_{OL}$          | 2.0  |                       |      | mA    |       |

| Standby Current $\overline{\text{CE}} = 2.2\text{V}$       | $I_{CCS1}$        |      | 5                     | 7    | mA    |       |

| Standby Current                                            | ī                 |      | 2.0                   | 3.0  | mA    |       |

| $\overline{\text{CE}} = V_{\text{CC}} - 0.5 \text{V}$      | $I_{CCS2}$        |      | 2.0                   | 3.0  | IIIA  |       |

| Operating Current $t_{CYC} = 70$ ns                        | $I_{CC01}$        |      |                       | 50   | mA    |       |

| Write Protection Voltage                                   | $ m V_{PF}$       | 2.80 | 2.86                  | 2.97 | V     | 11    |

| Battery Switchover Voltage                                 | $V_{SO}$          |      | $V_{BAT}$ or $V_{PF}$ | V    | 11    |       |

# **CAPACITANCE** $(T_A = +25^{\circ}C)$

| PARAMETER                | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance        | $C_{IN}$         |     | 5   | 10  | pF    |       |

| Input/Output Capacitance | C <sub>I/O</sub> |     | 5   | 10  | pF    |       |

# MEMORY AC ELECTRICAL CHARACTERISTICS Over the operating range (5V)

| DADAMETED                       | SYMBOL             | DS124 | 4Y-70 | UNITS | NOTES |

|---------------------------------|--------------------|-------|-------|-------|-------|

| PARAMETER                       | SYMBOL             | MIN   | MAX   | UNIIS | NOTES |

| Read Cycle Time                 | $t_{ m RC}$        | 70    |       | ns    |       |

| Access Time                     | $t_{ACC}$          |       | 70    | ns    |       |

| OE to Output Valid              | $t_{ m OE}$        |       | 35    | ns    |       |

| CE to Output Valid              | $t_{CO}$           |       | 70    | ns    |       |

| OE or CE to Output Active       | $t_{\rm COE}$      | 5     |       | ns    | 5     |

| Output High-Z from Deselection  | $t_{\mathrm{OD}}$  |       | 25    | ns    | 5     |

| Output Hold from Address Change | $t_{\mathrm{OH}}$  | 5     |       | ns    |       |

| Write Cycle Time                | $t_{\mathrm{WC}}$  | 70    |       | ns    |       |

| Write Pulse Width               | $t_{\mathrm{WP}}$  | 50    |       | ns    | 3     |

| Address Setup Time              | $t_{AW}$           | 0     |       | ns    |       |

| Write Recovery Time             | $t_{\mathrm{WR}}$  | 0     |       | ns    |       |

| Output High-Z from WE           | $t_{\mathrm{ODW}}$ |       | 25    | ns    | 5     |

| Output Active from WE           | $t_{ m OEW}$       | 5     |       | ns    | 5     |

| Data Setup Time                 | $t_{ m DS}$        | 30    |       | ns    | 4     |

| Data Hold Time from WE          | $t_{ m DH}$        | 5     |       | ns    | 4     |

### PHANTOM CLOCK AC ELECTRICAL CHARACTERISTICS

Over the operating range (5V)

| PARAMETER           | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|---------------------|-------------------|-----|-----|-----|-------|-------|

| Read Cycle Time     | $t_{RC}$          | 65  |     |     | ns    |       |

| CE Access Time      | $t_{\rm CO}$      |     |     | 55  | ns    |       |

| OE Access Time      | $t_{ m OE}$       |     |     | 55  | ns    |       |

| CE to Output Low-Z  | $t_{\rm COE}$     | 5   |     |     | ns    |       |

| OE to Output Low-Z  | $t_{ m OEE}$      | 5   |     |     | ns    |       |

| CE to Output High-Z | $t_{\mathrm{OD}}$ |     |     | 25  | ns    | 5     |

| OE to Output High-Z | $t_{ m ODO}$      |     |     | 25  | ns    | 5     |

| Read Recovery       | $t_{ m RR}$       | 10  |     |     | ns    |       |

| Write Cycle Time    | $t_{ m WC}$       | 65  |     |     | ns    |       |

| Write Pulse Width   | $t_{\mathrm{WP}}$ | 55  |     |     | ns    | 3     |

| Write Recovery      | $t_{ m WR}$       | 10  |     |     | ns    | 10    |

| Data Setup Time     | $t_{ m DS}$       | 30  |     |     | ns    | 4     |

| Data Hold Time      | $t_{ m DH}$       | 0   |     |     | ns    | 4     |

| CE Pulse Width      | $t_{CW}$          | 60  |     |     | ns    |       |

| RESET Pulse Width   | $t_{RST}$         | 65  |     |     | ns    |       |

### POWER-DOWN/POWER-UP TIMING

Over the operating range (5V)

| PARAMETER                                                   | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| $\overline{\text{CE}}$ at $V_{\text{IH}}$ before Power-Down | $t_{PD}$          | 0   |     |     | μs    |       |

| $V_{CC}$ Slew from $V_{PF(max)}$ to                         | $t_{\mathrm{F}}$  | 300 |     |     | μs    |       |

| $V_{PF(min)}(\overline{CE} \text{ at } V_{PF})$             |                   |     |     |     |       |       |

| $V_{CC}$ Slew from $V_{PF(min)}$ to $V_{SO}$                | $t_{\mathrm{FB}}$ | 10  |     |     | μs    |       |

| V <sub>CC</sub> Slew from V <sub>PF(max)</sub> to           | $t_R$             | 0   |     |     | μs    |       |

| $V_{PF(min)}(\overline{CE} \text{ at } V_{PF})$             |                   |     |     |     |       |       |

| $\overline{\text{CE}}$ at $V_{\text{IH}}$ after Power-Up    | $t_{REC}$         | 1.5 |     | 2.5 | ms    |       |

$(T_A = +25^{\circ}C)$

| PARAMETER                    | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------|-------------------|-----|-----|-----|-------|-------|

| Expected Data Retention Time | $t_{\mathrm{DR}}$ | 10  |     |     | years | 9     |

Warning: Under no circumstances are negative undershoots of any amplitude allowed when device is in battery-backup mode.

### **MEMORY AC ELECTRICAL CHARACTERISTICS**

Over the operating range (3.3V)

| DADAMETED                       | CVMDOI             | DS124 | 4W-120 | LINUTC | NOTES |

|---------------------------------|--------------------|-------|--------|--------|-------|

| PARAMETER                       | SYMBOL             | MIN   | MAX    | UNITS  |       |

| Read Cycle Time                 | $t_{RC}$           | 120   |        | ns     |       |

| Access Time                     | $t_{ACC}$          |       | 120    | ns     |       |

| OE to Output Valid              | $t_{ m OE}$        |       | 60     | ns     |       |

| CE to Output Valid              | $t_{CO}$           |       | 120    | ns     |       |

| OE or CE to Output Active       | t <sub>COE</sub>   | 5     |        | ns     | 5     |

| Output High-Z from Deselection  | $t_{\mathrm{OD}}$  |       | 40     | ns     | 5     |

| Output Hold from Address Change | $t_{\mathrm{OH}}$  | 5     |        | ns     |       |

| Write Cycle Time                | $t_{WC}$           | 120   |        | ns     |       |

| Write Pulse Width               | $t_{\mathrm{WP}}$  | 90    |        | ns     | 3     |

| Address Setup Time              | $t_{\mathrm{AW}}$  | 0     |        | ns     |       |

| Write Recovery Time             | $t_{\mathrm{WR}}$  | 20    |        | ns     | 10    |

| Output High-Z from WE           | $t_{\mathrm{ODW}}$ |       | 40     | ns     | 5     |

| Output Active from WE           | $t_{OEW}$          | 5     |        | ns     | 5     |

| Data Setup Time                 | $t_{ m DS}$        | 50    |        | ns     | 4     |

| Data Hold Time from WE          | $t_{ m DH}$        | 20    |        | ns     | 4     |

### PHANTOM CLOCK AC ELECTRICAL CHARACTERISTICS

Over the operating range (3.3V)

| PARAMETER           | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|---------------------|--------------------|-----|-----|-----|-------|-------|

| Read Cycle Time     | $t_{RC}$           | 120 |     |     | ns    |       |

| CE Access Time      | $t_{CO}$           |     |     | 100 | ns    |       |

| OE Access Time      | $t_{OE}$           |     |     | 100 | ns    |       |

| CE to Output Low-Z  | $t_{COE}$          | 5   |     |     | ns    |       |

| OE to Output Low-Z  | $t_{OEE}$          | 5   |     |     | ns    |       |

| CE to Output High-Z | $t_{\mathrm{OD}}$  |     |     | 40  | ns    | 5     |

| OE to Output High-Z | $t_{\mathrm{ODO}}$ |     |     | 40  | ns    | 5     |

| Read Recovery       | $t_{RR}$           | 20  |     |     | ns    |       |

| Write Cycle Time    | $t_{ m WC}$        | 120 |     |     | ns    |       |

| Write Pulse Width   | $t_{\mathrm{WP}}$  | 100 |     |     | ns    | 3     |

| Write Recovery      | $t_{ m WR}$        | 20  |     |     | ns    | 10    |

| Data Setup Time     | $t_{ m DS}$        | 45  |     |     | ns    | 4     |

| Data Hold Time      | $t_{ m DH}$        | 0   |     |     | ns    | 4     |

| CE Pulse Width      | $t_{CW}$           | 105 |     |     | ns    |       |

| RESET Pulse Width   | $t_{RST}$          | 120 |     |     | ns    |       |

### POWER-DOWN/POWER-UP TIMING

### Over the operating range (3.3V)

| PARAMETER                                                   | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| $\overline{\text{CE}}$ at $V_{\text{IH}}$ before Power-Down | $t_{\mathrm{PD}}$ | 0   |     |     | μs    |       |

| $V_{CC}$ Slew from $V_{PF(MAX)}$ to                         | $t_{\mathrm{F}}$  | 300 |     |     | μs    |       |

| $V_{PF(MIN)}(\overline{CE} \text{ at } V_{IH})$             |                   |     |     |     |       |       |

| $V_{CC}$ Slew from $V_{PF(MAX)}$ to                         | $t_{R}$           | 0   |     |     | μs    |       |

| $V_{PF(MIN)}(\overline{CE} \text{ at } V_{IH})$             |                   |     |     |     |       |       |

| $\overline{\text{CE}}$ at $V_{\text{IH}}$ after Power-Up    | $t_{REC}$         | 1.5 |     | 2.5 | ms    |       |

$(T_A = +25^{\circ}C)$

| PARAMETER                    | SYMBOL   | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------|----------|-----|-----|-----|-------|-------|

| Expected Data Retention Time | $t_{DR}$ | 10  |     |     | years | 9     |

Warning: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in battery-backup mode.

# **MEMORY READ CYCLE (Note 1)**

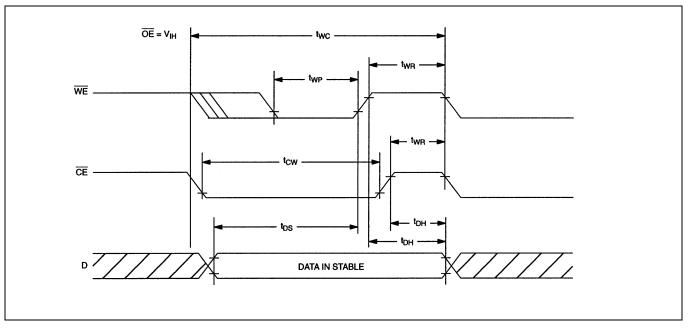

# MEMORY WRITE CYCLE 1 (Notes 2, 6, and 7)

# MEMORY WRITE CYCLE 2 (Notes 2 and 8)

### **RESET FOR PHANTOM CLOCK**

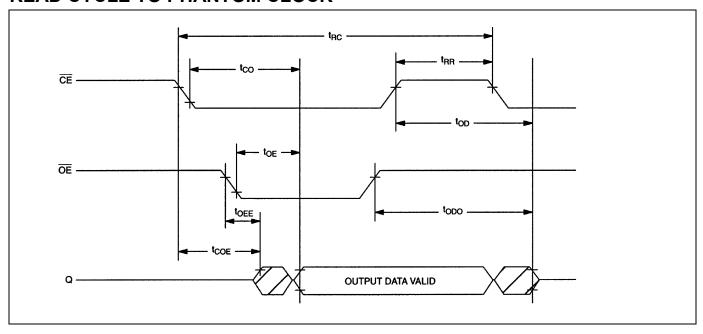

# **READ CYCLE TO PHANTOM CLOCK**

# WRITE CYCLE TO PHANTOM CLOCK

# POWER-DOWN/POWER-UP CONDITION, 5V

# POWER-DOWN/POWER-UP CONDITION, 3.3V

#### **AC TEST CONDITIONS**

Output Load: 50pF + 1TTL Gate Input Pulse Levels: 0 to 3V

Timing Measurement Reference Levels

Input: 1.5V Output: 1.5V

Input Pulse Rise and Fall Times: 5ns

#### **NOTES:**

- 1) WE is high for a read cycle.

- 2)  $\overline{OE} = V_{IH}$  or  $V_{IL}$ . If  $\overline{OE} = V_{IH}$  during write cycle, the output buffers remain in a high-impedance state.

- 3)  $t_{WP}$  is specified as the logical AND of  $\overline{CE}$  and  $\overline{WE}$ .  $t_{WP}$  is measured from the latter of  $\overline{CE}$  or  $\overline{WE}$  going low to the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 4)  $t_{DH}$ ,  $t_{DS}$  are measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 5) These parameters are sampled with a 50pF load and are not 100% tested.

- 6) If the  $\overline{CE}$  low transition occurs simultaneously with or later than the  $\overline{WE}$  low transition in Write Cycle 1, the output buffers remain in a high-impedance state during this period.

- 7) If the  $\overline{\text{CE}}$  high transition occurs prior to or simultaneously with the WE high transition, the output buffers remain in a high-impedance state during this period.

- 8) If WE is low or the WE low transition occurs prior to or simultaneously with the CE low transition, the output buffers remain in a high-impedance state during this period.

- 9) The expected  $t_{DR}$  is defined as cumulative time in the absence of  $V_{CC}$  with the clock oscillator running.

- 10)  $t_{WR}$  is a function of the latter occurring edge of  $\overline{WE}$  or  $\overline{CE}$ .

- 11) Voltages are referenced to ground.

- 12) RST (Pin 1) has an internal pullup resistor.

- 13) RTC modules can be successfully processed through conventional wave-soldering techniques as long as temperature exposure to the lithium energy source contained within does not exceed +85°C. Post-solder cleaning with water-washing techniques is acceptable, provided that ultrasonic vibration is not used.

In addition, for the PowerCap:

- 1) Maxim recommends that PowerCap module bases experience one pass through solder reflow oriented with the label side up ("live-bug").

- 2) Hand soldering and touch-up: Do not touch or apply the soldering iron to leads for more than three seconds.

- To solder, apply flux to the pad, heat the lead frame pad, and apply solder. To remove the part, apply flux, heat the lead frame pad until the solder reflows, and use a solder wick to remove solder.

### **PACKAGE INFORMATION**

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 32 EDIP      | MDT28+4      | <u>21-0245</u> | _                |

| 34 PWRCP     | PC2+4        | <u>21-0246</u> | _                |

### **REVISION HISTORY**

| REVISION<br>DATE | DESCRIPTION                                                                       | PAGES<br>CHANGED |

|------------------|-----------------------------------------------------------------------------------|------------------|

| 11/11            | Updated the Features, Ordering Information, and Absolute Maximum Ratings sections | 1, 2, 9          |