# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

# NIXIN

## Complete 10µs CMOS 12-Bit ADC

### **General Description**

The MAX172 is a complete 12-Bit analog-to-digital converter (ADC) that combines high speed, low power consumption, and an on-chip voltage reference. The conversion time is 10 $\mu$ s. The buried zener reference provides low drift and low noise performance.

External component requirements are limited to only decoupling capacitors for the power supply and reference voltages. On-chip clock circuitry is also included which can either be driven from an external source, or in stand-alone applications, can be used with a crystal.

The MAX172 uses a standard microprocessor interface architecture. Three-state data outputs are controlled by Read (RD) and Chip Select (CS) inputs. Data access and bus release times of 90 and 75ns respectively ensure compatibility with most popular microprocessors without resorting to wait states.

### **Applications**

Digital Signal Processing (DSP) High Accuracy Process Control High Speed Data Acquisition Electro-Mechanical Systems

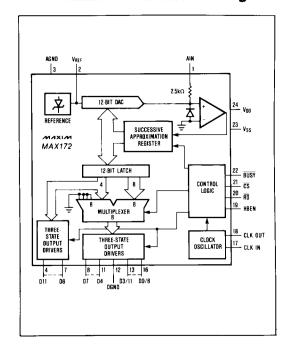

#### Functional Diagram

## Features

- ♦ 12-Bit Resolution and Linearity

- ♦ 10µs Conversion Time

- **♦ No Missing Codes**

- ♦ On-Chip Voltage Reference

- ♦ 90ns Access Time

- ♦ 215mW Max Power Consumption

- ♦ 24-Lead Narrow DIP Package

- ♦ Pin-for-Pin AD7572 Replacement

#### **Ordering Information**

| PART       | TEMP<br>RANGE   | PIN-<br>PACKAGE | ERROR<br>(LSB) | PKG<br>CODE |

|------------|-----------------|-----------------|----------------|-------------|

| MAX172ACNG | 0°C to +70°C    | 24 Plastic DIP  | ±0.5           | N24-3       |

| MAX172BCNG | 0°C to +70°C    | 24 Plastic DIP  | ±1             | N24-3       |

| MAX172ACWG | 0°C to +70°C    | 24 Wide SO      | ±0.5           | W24-1       |

| MAX172BCWG | 0°C to +70°C    | 24 Wide SO      | ±1             | W24-1       |

| MAX172CC/D | 0°C to +70°C    | Dice*           | ±1             | _           |

| MAX172AENG | -40°C to +85°C  | 24 Plastic DIP  | ±0.5           | N24-3       |

| MAX172BENG | -40°C to +85°C  | 24 Plastic DIP  | ±1             | N24-3       |

| MAX172AMRG | -55°C to +125°C | 24 CERDIP       | ±0.5           | R24-4       |

| MAX172BMRG | -55°C to +125°C | 24 CERDIP       | ±1             | R24-4       |

\* Consult factory for dice specifications

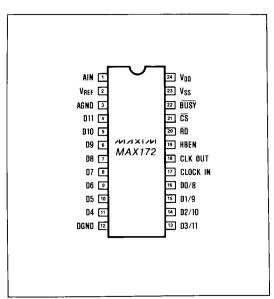

## Pin Configuration

MIXIM

Maxim Integrated Products

## Complete 10µs CMOS 12-Bit ADC

## **ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

**ELECTRICAL CHARACTERISTICS** ( $V_{DD}$  = +5V  $\pm$  5%,  $V_{SS}$  = -12V or -15V  $\pm$  5%; Slow Memory Mode;  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted,  $f_{CLK}$  = 1.25MHz.)

| PARAMETER                                     | SYMBOL           | CON                                | IDITIONS                                                                       | MIN  | TYP   | MAX                  | UNITS  |

|-----------------------------------------------|------------------|------------------------------------|--------------------------------------------------------------------------------|------|-------|----------------------|--------|

| ACCURACY                                      |                  |                                    |                                                                                |      |       |                      |        |

| Resolution                                    |                  |                                    |                                                                                | 12   |       |                      | Bits   |

|                                               |                  | MAX172A                            | T <sub>A</sub> = 25°C                                                          |      |       | + 1/2                | T      |

| Integral NonLinearity                         | INL              | MAX172AC/AE<br>MAX172AM<br>MAX172B |                                                                                |      |       | ± 1/2<br>+ 3/4<br>±1 | LSB    |

| Differential NonLinearity                     | DNL              | Guaranteed Monot                   | onic Over Temp.                                                                |      |       | +1                   | LSB    |

|                                               |                  | MAX172B                            | MAX172B $ T_A = 25^{\circ} C $ $ T_A = T_{MIN} \text{ to } T_{MAX} $           |      |       | ±4<br>±6             | 1.00   |

| Offset Error (Note 1)                         |                  | MAX172A                            | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |      |       | ±3<br>±4             | LSB    |

|                                               | _                | MAX172B                            | T <sub>A</sub> = 25°C                                                          |      |       | + 15                 | LSB    |

| Full Scale Error (Note 2)                     |                  | MAX172A                            | T <sub>A</sub> = 25°C                                                          |      |       | + 10                 | LSB    |

| Full Scale Tempco (Notes 3, 4)                |                  |                                    |                                                                                |      |       | +45                  | ppm/°( |

| ANALOG INPUT                                  |                  |                                    |                                                                                |      |       |                      |        |

| Input Voltage Range                           |                  |                                    |                                                                                | 0    | _     | 5                    | V      |

| Input Current                                 |                  | AIN = 0V to +5V                    |                                                                                |      |       | 3.5                  | rnA    |

| INTERNAL REFERENCE                            |                  |                                    |                                                                                |      |       |                      |        |

| V <sub>REF</sub> Output Voltage               |                  | T <sub>A</sub> = 25°C              |                                                                                | -5.2 | -5.25 | -5.3                 | V      |

| V <sub>REF</sub> Output Tempco (Note 5)       |                  |                                    |                                                                                |      | 40    |                      | ppm/°  |

| Output Current Sink Capability                |                  | (Note 6)                           |                                                                                |      |       | 500                  | μΑ     |

| LOGIC INPUTS                                  |                  |                                    |                                                                                |      |       |                      |        |

| Input Low Voltage                             | V <sub>IL</sub>  | CS, RD, HBEN, C                    | LKIN                                                                           |      |       | 0.8                  | V      |

| Input High Voltage                            | V <sub>IH</sub>  | CS, RD, HBEN, C                    | LKIN                                                                           | 2.4  |       |                      | V      |

| Input Capacitance (Note 7)                    | CIN              | CS, RD, HBEN, C                    | LKIN                                                                           |      |       | 10                   | pF     |

| Input Current                                 | I <sub>IN</sub>  | CS, RD, HBEN<br>CLKIN              | VIN = 0 to V <sub>DD</sub>                                                     |      |       | + 10<br>+ 20         | μΑ     |

| LOGIC OUTPUTS                                 |                  |                                    |                                                                                |      |       |                      |        |

| Output Low Voltage                            | V <sub>OL</sub>  | D11-D0/8, BUSY,                    | CLKOUT I <sub>SINK</sub> = 1.6mA                                               |      |       | 0.4                  | V      |

| Output High Voltage                           | V <sub>OH</sub>  | D11-D0/8, BUSY,                    | CLKOUT I <sub>SOURCE</sub> = 200µA                                             | 4    |       |                      | V      |

| Floating State Leakage<br>Current             | I <sub>LKG</sub> | D11-D0/8, V <sub>OUT</sub> =       | 0V to V <sub>DD</sub>                                                          |      |       | + 10                 | μΑ     |

| Floating State Output<br>Capacitance (Note 7) | Соит             |                                    |                                                                                |      |       | 15                   | pF     |

3

## Complete 10 µs CMOS 12-Bit ADC

**ELECTRICAL CHARACTERISTICS (Continued)**  $(V_{DD} = +5V + 5W, V_{SS} = -12V \text{ or } -15V \pm 5W$ ; Slow Memory Mode;  $T_A = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted,  $f_{CLK} = 1.25MHz$ .)

| PARAMETER                | SYMBOL            | CONDITIONS                                                           | MIN                                                      | TYP       | MAX        | UNITS |

|--------------------------|-------------------|----------------------------------------------------------------------|----------------------------------------------------------|-----------|------------|-------|

| CONVERSION TIME          |                   |                                                                      |                                                          |           |            |       |

| MAX172                   | t <sub>CONV</sub> | Synchronous (12.5 clock cycles) Asynchronous (12 to 13 clock cycles) | 9.6                                                      |           | 10<br>10.4 | μS    |

| POWER SUPPLY REJECT      | ION               |                                                                      |                                                          |           |            |       |

| V <sub>DD</sub> Only     |                   | FS Change, $V_{SS} = -15V$ , $V_{DD} = 4.75V$ to 5.25V               |                                                          | ±1/2      |            | LSB   |

| V <sub>SS</sub> Only     |                   | FS Change, V <sub>DD</sub> = 5V, V <sub>SS</sub> = -5% to +5%        |                                                          | LSB       |            |       |

| POWER REQUIREMENTS       |                   |                                                                      |                                                          |           |            |       |

| V <sub>DD</sub>          |                   | ±5% for Specified Performance                                        |                                                          | 5         |            | VV    |

| V <sub>SS</sub> (Note 8) |                   | ±5% for Specified Performance                                        |                                                          | -12 or -1 | 5          |       |

| I <sub>DD</sub>          |                   | CS = RD = V <sub>DD</sub> , AIN = 5V                                 |                                                          | 5         | 7          | mA    |

| Iss                      |                   | CS = RD = V <sub>DD</sub> , AIN = 5V                                 | $\overline{CS} = \overline{RD} = V_{DD}$ , AIN = 5V 8 12 |           |            |       |

| Power Dissipation        |                   | $V_{DD} = +5V, V_{SS} = -15V$ 145 215                                |                                                          |           |            | mW    |

Note 1: Typical change over temp is +1 LSB. Note 2:  $V_{DD} = +5V$ ,  $V_{SS} = -15V$ , FS = +5.000V, Ideal last code transition = FS - 3/2LSB. Note 3: Full Scale TC =  $\Delta$ FS/ $\Delta$ T, where  $\Delta$ FS is full scale change from  $T_A = 25^{\circ}$ C to  $T_{MIN}$  or  $T_{MAX}$ .

Note 4: Includes internal reference drift.

Note 5: V<sub>REF</sub> TC = ΔV<sub>REF</sub>/ΔT, where ΔV<sub>REF</sub> is reference voltage change from T<sub>A</sub> = 25°C to T<sub>MIN</sub> or T<sub>MAX</sub>.

Note 6: Output current should not change during conversion.

Note 7: Guaranteed by design, not subject to test.

Note 8: Functional operation at V<sub>SS</sub> = -12V + 5% is guaranteed by testing offset error and full scale error.

#### TIMING CHARACTERISTICS (Note 9)

(V<sub>DD</sub> = +5V, V<sub>SS</sub> = -12V or -15V;  $T_A = T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.)

|                                         | SYMBOL          | CONDITIONS                                      | T <sub>A</sub> = 25°C |          | MAX172C/E |       | MAX172M    |                | UNITS      |        |

|-----------------------------------------|-----------------|-------------------------------------------------|-----------------------|----------|-----------|-------|------------|----------------|------------|--------|

| PARAMETER                               |                 |                                                 | MIN                   | TYP      | MAX       | MIN   | MAX        | MIN            | MAX        | DIALLS |

| CS to RD Setup Time                     | t <sub>1</sub>  |                                                 | 0                     |          |           | 0     |            | 0              |            | ns     |

| RD to BUSY Delay                        | t <sub>2</sub>  | C <sub>L</sub> = 50pF                           |                       | 90       | 190       |       | 230        |                | 270        | ns     |

| Data Access Time (Note 10)              | t <sub>3</sub>  | C <sub>L</sub> = 20pF<br>C <sub>L</sub> = 100pF |                       | 60<br>70 | 90<br>125 |       | 110<br>150 | _              | 120<br>170 | ns     |

| RD Pulse Width                          | t <sub>4</sub>  |                                                 | t <sub>3</sub>        |          |           | $t_3$ |            | t <sub>3</sub> |            |        |

| CS to RD Hold Time                      | t <sub>5</sub>  |                                                 | 0                     |          |           | 0     |            | 0              |            | ns     |

| Data Setup Time After BUSY<br>Note (10) | t <sub>6</sub>  |                                                 |                       |          | 70        | _     | 90         |                | 100        | ns     |

| Bus Relinquish Time (Note 11)           | t <sub>7</sub>  |                                                 | 20                    |          | 75        | 20    | 85         | 20             | 90         | ns     |

| HBEN to RD Setup Time                   | t <sub>8</sub>  |                                                 | 0                     |          |           | 0     |            | 0              |            | ns     |

| HBEN to RD Hold Time                    | t <sub>9</sub>  |                                                 | 0                     |          |           | 0     |            | 0              |            | ns     |

| Delay Between Read Operations           | t <sub>10</sub> |                                                 | 200                   |          |           | 200   |            | 200            |            | ns     |

Timing specifications are sample tested at 25°C to ensure compliance. All input control signals are specified with

$t_r = t_1 = 5$ ns (10% to 90% of +5V) and timed from a voltage level of +1.6V.  $t_3$  and  $t_6$  are measured with the load circuits of Figure 1 and defined as the time required for an output to cross Note 10:

Note 11: t<sub>7</sub> is defined as the time required for the data lines to change 0.5V when loaded with the circuits of Figure 2.

## For additional information on using the MAX172 please refer to MAX162 data sheet.

| VI/IXI/VI |  |

|-----------|--|

## Complete 10µs CMOS 12-Bit ADC

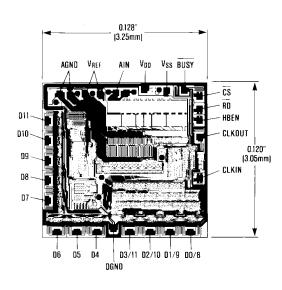

## Chip Topography

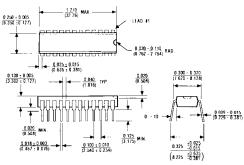

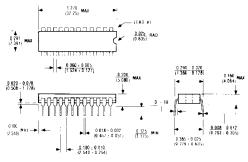

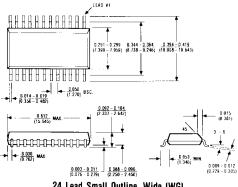

## Package Information

24 Lead Plastic Narrow DIP (NG)  $\theta_{JA} = 120^{\circ}C/W$   $\theta_{JC} = 60^{\circ}C/W$

24 Lead Narrow CERDIP (RG)

$$\theta_{JA} = 80^{\circ}\text{C/W}$$

$\theta_{JC} = 40^{\circ}\text{C/W}$

24 Lead Small Outline, Wide (WG)

$\theta_{JA} = 85^{\circ}\text{C/W}$  $\theta_{JC}^{NA} = 45^{\circ} \text{ C/W}$

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.