## 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

## 308ksps ADC with DSP Interface and 78dB SINAD

#### **General Description**

The MAX121 is a complete, BiCMOS, serial-output, sampling 14-bit analog-to-digital converter (ADC) that combines an on-chip track/hold and a low-drift, low-noise, buried-zener voltage reference with fast conversion speed and low power consumption. The throughput rate is as high as 308k samples per second (ksps). The full-scale analog input range is ±5V.

The MAX121 utilizes the successive-approximation architecture with a high-speed DAC to achieve both fast conversion speeds and low-power operation. Operating with +5V and -12V or -15V power supplies, power consumption is only 210mW.

The MAX121 can be directly interfaced to the serial port of most popular digital-signal processors, and comes in space-saving 16-pin DIP and SO and smaller 20-pin SSOP packages. The MAX121 operates with TTL- and CMOS-compatible clocks in the frequency range from 1.1MHz to 5.5MHz. All logic inputs and outputs are TTL- and CMOS-compatible. This data sheet includes application notes for easy interface to TMS320,  $\mu PD77230$ , and ADSP2101 digital-signal processors, as well as  $\mu Ps$  using the Motorola SPI and QSPI interface standards.

#### **Applications**

- Digital Signal Processing

- Audio and Telecom Processing

- Speech Recognition and Synthesis

- DSP Servo Control

- Spectrum Analysis

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX121.related.

#### **Benefits and Features**

- 14-Bit Resolution

- 2.9µs Conversion Time/308ksps Throughput

- 400ns Acquisition Time

- Low Noise and Distortion

- 78d8 SINAD

- -85dB THD

- ±5V Bipolar Input Range, Overvoltage Tolerant to ±15V

- 210mW Power Dissipation

- Continuous-Conversion Mode Available

- 30ppm/°C, -5V Internal Reference

- Interfaces to DSP Processors

- 16-Pin DIP and SO Packages,

20-Pin SSOP Package

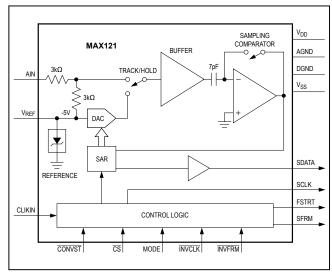

### **Functional Diagram**

## 308ksps ADC with DSP Interface and 78dB SINAD

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to DGND          | 0.3V to +6V                         |

|----------------------------------|-------------------------------------|

| V <sub>SS</sub> to DGND          |                                     |

| AIN to AGND                      | ±15V                                |

| AGND to DGND                     | ±0.3V                               |

| Digital Inputs to DGNO           | 0.3V to (V <sub>DD</sub> + 0.3V)    |

| (CS, CONVST, MODE, CLKIN, INVCLK | , INVFRM)                           |

| Digital Outputs to DGND          | . +0.3V to (V <sub>DD</sub> + 0.3V) |

| (SFRM, FSTRT, SCLK, SDATA)       |                                     |

| Continuous Power Dissipation (T <sub>A</sub> = +70 | O°C)             |

|----------------------------------------------------|------------------|

| 16-Pin PDIP (derate 10.53mW/°C abov                | /e +70°C)842mW   |

| 16-Pin Wide SO (derate 9.52mW/°C at                | oove +70°C)762mW |

| 20-Pin SSOP (derate 8.00mW/°C abov                 | re +70°C)640mW   |

| Operating Temperature Ranges                       |                  |

| MAX121C                                            | 0°C to +70°C     |

| MAX121E                                            |                  |

| Storage Temperature Range                          | 65°C to + 160°C  |

| Lead Temperature (soldering, 10s)                  |                  |

| Soldering Temperature (reflow)                     | +260°C           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(V<sub>DD</sub> = 4.75V to 5.25V, V<sub>SS</sub> = -10.8V to -15.75V,  $f_{CLK}$  = 5.5MHz,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                                | SYMBOL     | COND                                                          | MIN                                             | TYP | MAX  | UNITS  |        |

|----------------------------------------------------------|------------|---------------------------------------------------------------|-------------------------------------------------|-----|------|--------|--------|

| DYNAMIC PERFORMANCE (fS =                                | 308kHz, VA | N = 10Vp_p, 50kHz)                                            |                                                 |     |      |        |        |

| Signal-to-Noise Ratio                                    | SINAD      | Including distortion                                          | MAX121C                                         | 75  | 78   |        | dB     |

|                                                          | SINAD      |                                                               | MAX121E                                         | 73  | 77   |        | dB     |

| Total Harmonic Distortion                                | THD        | First five harmonics                                          |                                                 |     | -85  | -77    | dB     |

| Spurious-Free Dynamic Range                              | SFDR       |                                                               |                                                 | 77  | 86   |        | dB     |

| ACCURACY                                                 |            |                                                               |                                                 |     |      |        |        |

| Resolution                                               | RES        |                                                               |                                                 | 14  |      |        | Bits   |

| Differential Nonlinearity (Note 1)                       | DNL        | 12 bits no missing cod range                                  | 12 bits no missing codes over temperature range |     |      |        | LSB    |

| Integral Nonlinearity                                    | INL        |                                                               |                                                 |     | ±2   |        | LSB    |

| Code 0000 to 0001 transition, near V <sub>AIN</sub> = 0V |            |                                                               |                                                 | ±10 | mV   |        |        |

|                                                          |            | Temperature drift                                             |                                                 | ±1  |      | ppm/°C |        |

| Full-Scale Error (Notes 1, 2)                            |            | Including reference; ac<br>zero error; T <sub>A</sub> = +25°C |                                                 |     |      | ±0.2   | %      |

| Full-Scale Temperature Drift                             |            | Excluding reference                                           |                                                 |     | ±1   |        | ppm/°C |

|                                                          |            | V <sub>DD</sub> only, 5V ±5%                                  |                                                 |     | ±1/2 | ±2     |        |

| Power-Supply Rejection                                   |            | V <sub>SS</sub> only, -12V ±10%                               |                                                 | ±1  | ±2   | LSB    |        |

|                                                          |            | V <sub>SS</sub> only, -15V ±5%                                |                                                 | ±1  | ±2   |        |        |

| ANALOG INPUT                                             |            |                                                               |                                                 |     |      |        |        |

| Input Range                                              |            |                                                               |                                                 | -5  |      | +5     | V      |

| Input Current                                            |            | V <sub>AIN</sub> = 5V (R <sub>IN</sub> approx                 | kimately 6kΩ to REF)                            |     |      | 2.5    | mA     |

| Input Capacitance (Note 3)                               |            |                                                               |                                                 | ·   |      | 10     | pF     |

| Full-Power Bandwidth                                     |            |                                                               |                                                 |     | 1.5  |        | MHz    |

## **Electrical Characteristics (continued)**

(V<sub>DD</sub> = 4.75V to 5.25V, V<sub>SS</sub> = -10.8V to -15.75V,  $f_{CLK}$  = 5.5MHz,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                   | SYMBOL           | CONDITIONS                                                                                                            | MIN                   | TYP | MAX    | UNITS  |

|-----------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------|-----|--------|--------|

| REFERENCE                   |                  |                                                                                                                       |                       |     |        |        |

| Output Voltage              |                  | No external load, V <sub>AIN</sub> = 5V, T <sub>A</sub> = +25°C                                                       | -5.02                 |     | -4.98  | V      |

| External Load Regulation    |                  | 0mA < I <sub>SINK</sub> < 5mA, V <sub>AIN</sub> = 0V                                                                  |                       |     | 5      | mV     |

| Temperature Drift (Note 4)  |                  |                                                                                                                       |                       |     | ±30    | ppm/°C |

| CONVERSION TIME             |                  |                                                                                                                       |                       |     |        |        |

| Synchronous                 | tCONV            | 16 t <sub>CLK</sub>                                                                                                   |                       |     | 2.91   | μs     |

| Clock Frequency             | fCLK             |                                                                                                                       | 0.1                   |     | 5.5    | MHz    |

| DIGITAL INPUTS (CLKIN, CON  | /ST, CS)         |                                                                                                                       |                       |     |        |        |

| Input High Voltage          | V <sub>IH</sub>  |                                                                                                                       | 2.4                   |     |        | V      |

| Input Low Voltage           | V <sub>IL</sub>  |                                                                                                                       |                       |     | 0.8    | V      |

| Input Capacitance (Note 3)  |                  |                                                                                                                       |                       |     | 10     | pF     |

| Input Current               |                  | $V_{DD} = 0V \text{ or } V_{DD}$                                                                                      |                       |     | ±5     | μA     |

| DIGITAL OUTPUTS (SCLK, SDA  | ATA, FSTRT, S    | FRM)                                                                                                                  |                       |     |        |        |

| Output Low Voltage          | V <sub>OL</sub>  | I <sub>SINK</sub> = 1.6mA                                                                                             |                       |     | 0.4    | V      |

| Output High Voltage         | V <sub>OH</sub>  | I <sub>SOURCE</sub> = 1mA                                                                                             | V <sub>DD</sub> - 0.5 |     |        | V      |

| Leakage Current             | <sup>I</sup> LKG | V <sub>OUT</sub> = 0V or V <sub>DD</sub>                                                                              |                       |     | ±5     | μA     |

| Output Capacitance (Note 3) |                  |                                                                                                                       |                       |     | 10     | pF     |

| POWER REQUIREMENTS          | ·                |                                                                                                                       |                       |     |        |        |

| Positive Supply Voltage     | V <sub>DD</sub>  | By supply rejection test                                                                                              | 4.75                  |     | 5.25   | V      |

| Negative Supply Voltage     | V <sub>SS</sub>  | By supply rejection test                                                                                              | -10.8                 |     | -15.75 | V      |

| Positive Supply Current     | I <sub>DD</sub>  | $V_{DD} = 15.25V$ , $V_{SS} = -15.75V$ , $V_{AIN} = 0V$ , $V_{\overline{CS}} = V_{\overline{CONVST}} = V_{MODE} = 5V$ |                       | 9   | 15     | mA     |

| Negative Supply Current     | I <sub>SS</sub>  | $V_{DD} = 15.25V$ , $V_{SS} = -15.75V$ , $V_{AIN} = 0V$ , $V_{\overline{CS}} = V_{\overline{CONVST}} = V_{MODE} = 5V$ |                       | 14  | 20     | mA     |

| Power Dissipation           |                  | $V_{DD}$ = 15.25V, $V_{SS}$ = 12V, $V_{AIN}$ = 0V, $V_{\overline{CS}}$ = $V_{\overline{CONVST}}$ = $V_{MODE}$ = 5V    |                       | 213 | 315    | mW     |

Maxim Integrated | 3 www.maximintegrated.com

#### **Timing Characteristics**

(V<sub>DD</sub> = 5V, V<sub>SS</sub> = -12V or -15V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 5)

| PARAMETER                   | SYMBOL          | CONDITIONS            | T <sub>A</sub> = +25°C |     | MAX121C/E |     | MAX121M |     | М   | UNITS |      |       |

|-----------------------------|-----------------|-----------------------|------------------------|-----|-----------|-----|---------|-----|-----|-------|------|-------|

| PARAIVIETER                 | STWIBUL         | CONDITIONS            | MIN                    | TYP | MAX       | MIN | TYP     | MAX | MIN | TYP   | MAX  | UNITS |

| CONVST Pulse Width (Note 6) | tcw             |                       | 20                     |     |           | 30  |         |     | 35  |       |      | ns    |

| Data-Access Time            | t <sub>DA</sub> | C <sub>L</sub> = 50pF |                        | 25  | 50        |     |         | 65  |     |       | 80   | ns    |

| Data-Hold Time              | t <sub>DH</sub> |                       |                        | 25  | 50        |     |         | 65  |     |       | 80   | ns    |

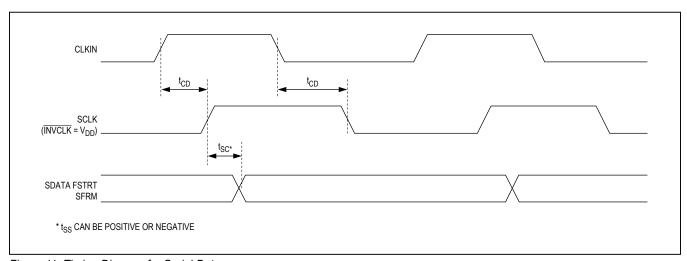

| CLKIN to SCLK               | tCD             | C <sub>L</sub> = 50pF |                        | 40  | 65        |     |         | 85  |     |       | 105  | ns    |

| SCLK to SDATA<br>Skew       | tsc             | C <sub>L</sub> = 50pF |                        |     | ±65       |     |         | ±80 |     |       | ±100 | ns    |

| SCLK to SFRM or FSTRT Skew  | tsc             | C <sub>L</sub> = 50pF |                        |     | ±25       |     |         | ±35 |     |       | ±40  | ns    |

| Acquisition Time (Note 6)   | tAQ             |                       | 400                    |     |           | 400 |         |     | 400 |       |      | ns    |

| Aperture Delay              | t <sub>AP</sub> |                       |                        | 10  |           |     |         |     |     |       |      | ns    |

| Aperture Jitter             |                 |                       |                        | 30  |           |     |         |     |     |       |      | ns    |

| Clock Setup/Hold<br>Time    | tCK             |                       | 10                     |     | 50        | 10  |         | 50  | 10  |       | 50   | ns    |

- Note 1: These tests are performed at  $V_{DD}$  = +5V.  $V_{SS}$  = -15V. Operation over supply is guaranteed by supply-rejection tests. Note 2: Ideal full-scale transition is at +5V 3/2 LSB = +4.9991V adjusted for offset error.

- Note 3: Guaranteed, not tested.

- Note 4: Temperature drift is defined as the change in output voltage from +25 $^{\circ}$ C to T<sub>MIN</sub> or T<sub>MAX</sub>. It is calculated as  $T_C = (\Delta V_{REF}/V_{REF})/\Delta T$ .

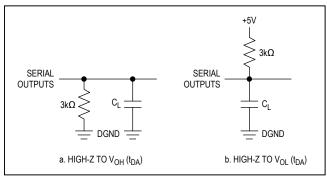

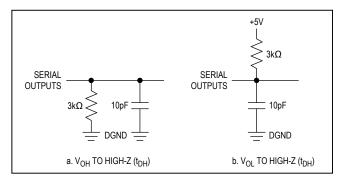

- Note 5: Control inputs specified with  $t_r = t_f = 5$ ns (10% to 90% of +5V) and timed from a voltage level of 1.6V. Output delays are measured to +0.8V if going low, or +2.4V if going high. For a data-hold time, a change of 0.5V is measured. See Figures 4 and 5 for load circuits.

- Note 6: Guaranteed, not tested.

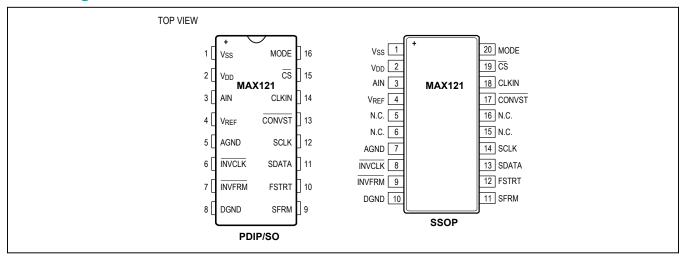

## **Pin Configurations**

### **Pin Description**

|         | PIN          |                  |                                                                                                                                                                                                                    |  |  |

|---------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PDIP/SO | SSOP         | NAME             | FUNCTION                                                                                                                                                                                                           |  |  |

| 1       | 1            | V <sub>SS</sub>  | Negative Power Supply, -12V or -15V. Bypass to AGND with 10μF and 0.1μF capacitors.                                                                                                                                |  |  |

| 2       | 2            | V <sub>DD</sub>  | Positive Power Supply, +5V. Bypass to AGND with 10µF and 0.1µF capacitors.                                                                                                                                         |  |  |

| 3       | 3            | AIN              | Sampling Analog Input, ±5V Bipolar Input Range                                                                                                                                                                     |  |  |

| 4       | 4            | V <sub>REF</sub> | -5V Reference Output. Bypass to AGND with 22μF    0.1μF capacitors.                                                                                                                                                |  |  |

| 5       | 7            | AGND             | Analog Ground                                                                                                                                                                                                      |  |  |

| 6       | 8            | INVCLK           | Invert Serial Clock. Connect to DGND to invert the SCLK output (relative to CLKIN).                                                                                                                                |  |  |

| 7       | 9            | INVFRM           | Invert Serial Frame. This input sets the polarity of the SFRM output as follows:  If INVFRM = DGND, SFRM is high during a conversion.  If INVFRM = VDD, SFRM is low during a conversion.                           |  |  |

| 8       | 10           | DGND             | Digital Ground                                                                                                                                                                                                     |  |  |

| 9       | 11           | SFRM             | Serial Frame Output. Normally high ( $\overline{\text{INVFRM}} = \text{V}_{DD}$ ), falls at the beginning of the conversion and rises at the end (after 16 t <sub>CLK</sub> ) signaling the end of a 16-bit frame. |  |  |

| 10      | 12           | FSTRT            | Frame Start Output. High pulse that lasts one clock cycle, falling edge indicates that a valid MSB is available.                                                                                                   |  |  |

| 11      | 13           | SDATA            | Serial Data Output. MSB first, two's-complement binary output code.                                                                                                                                                |  |  |

| 12      | 14           | SCLK             | Serial Clock Output. Same polarity as CLKIN if INVCLK = V <sub>DD</sub> , inverted CLKIN if INVCLK = DGND. Note that SCLK runs whenever CLKIN is active.                                                           |  |  |

| 13      | 17           | CONVST           | Active-Low Convert Start Input. Conversions are initiated on falling edges.                                                                                                                                        |  |  |

| 14      | 18           | CLKIN            | Clock Input. Supply at TTL-/CMOS-compatible clock from 0.1MHz to 5.5MHz, 40% to 60% duty cycle.                                                                                                                    |  |  |

| 15      | 19           | CS               | Active-Low Chip Select Input. $\overline{CS}$ = DGND enables the three-state outputs. Also, if $\overline{CONVST}$ is low, initiates a conversion on the falling edge of $\overline{CS}$ .                         |  |  |

| 16      | 20           | MODE             | Hardwire to set operational mode. V <sub>DD</sub> (single conversions), DGND (continuous conversions).                                                                                                             |  |  |

| _       | 5, 6, 15, 16 | N.C.             | No Connection. Not internally connected.                                                                                                                                                                           |  |  |

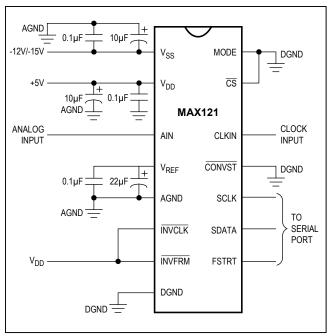

Figure 1. MAX121 in the Simplest Operational Mode (Continuous-Conversion Mode)

#### **Detailed Description**

#### **ADC Operation**

The MAX121 uses successive approximation and input track/hold (T/H) circuitry to convert an analog signal to a 14-bit serial digital output code. The control logic interfaces easily to most microprocessors (µPs) and digital signal processors (DSPs), requiring only a few passive components for most applications. The T/H does not require an external capacitor. Figure 1 shows the MAX121 in its simplest operational configuration.

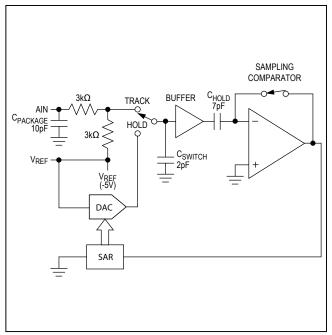

#### Analog Input Track/Hold

The Equivalent Input Circuit (Figure 2) illustrates the sampling architecture of the ADC's analog comparator. An internal buffer charges the hold capacitor to minimize the required acquisition time between conversions. The analog input appears as a  $6k\Omega$  resistor in parallel with a 10pF capacitor.

Between conversions, the buffer input is connected to AIN through the input resistance. When a conversion starts, the buffer input is disconnected from AIN, thus sampling the input. At the end of the conversion, the buffer input is reconnected to AIN, and the hold capacitor tracks the input voltage.

The T/H is in its tracking mode whenever a conversion is not in progress. Hold mode starts approximately 10ns after

Figure 2. Equivalent Input Circuit

a conversion is initiated (aperture delay). The variation in this delay from one conversion to the next (aperture jitter) is typically 30ps. Figures 7-9 detail the track/hold mode and interface timing for the three different interface modes.

#### **Internal Reference**

The MAX121 -5.00V buried-zener reference biases the internal DAC. The reference output is available at the V<sub>REF</sub> pin and must be bypassed to the AGND pin with a 0.1µF ceramic capacitor in parallel with a 22µF or greater electrolytic capacitor. The electrolytic capacitor's equivalent series resistance (ESR) must be  $100m\Omega$  or less to properly compensate the reference output buffer. Sanyo's organic semiconductor capacitors work well; telephone and FAX numbers are provided below.

Sanyo Video Components (USA)

Phone: (619) 661-6835 FAX: (619) 661-1055

Sanyo Electric Company, LTD. (Japan)

Phone: 0720-70-1005 FAX: 0720-70-1174

Sanyo Fisher Vertriebs GmbH (Germany)

Phone: 06102-27041, ext. 44

FAX: 06102-27045

Proper bypassing minimizes reference noise and maintains a low impedance at high frequencies. The internalreference output buffer can sink up to 5mA from an external load.

An external reference voltage can be used to overdrive the MAX121's internal reference, if the external reference lies within the range from -5.05V to -5.10V. The external reference must be capable of sinking a minimum of 5mA. The external V<sub>RFF</sub> bypass capacitors are still required.

#### **External Clock**

The MAX121 requires a TTL-/CMOS-compatible clock for proper operation. The MAX121 accepts clocks in the frequency range from 0.1MHz to 5.5MHz when operating in mode 1 or mode 2 (see the *Operating Modes* section). To satisfy the 400ns acquisition-time requirement with 2 clock cycles, the maximum clock frequency is limited to 5MHz when operating in mode 3 (continuous-conversion mode). The minimum clock frequency in all modes is limited to 0.1MHz due to the droop rate of the internal T/H.

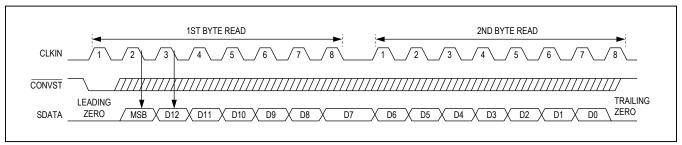

#### **Output Data Format**

The conversion result is output as a 16-bit serial data stream, starting with the 14 data bits (MSB first) followed by 2 trailing zeros. The format of the output data is two'scomplement binary. Data is clocked out of the SDATA pin on the rising edge of CLKIN.

The output data can be framed using either the FSTRT or the SFRM output. FSTRT (normally low) goes high for 1

Figure 3. Data-Access + Data-Hold Timing

Figure 4. Load Circuits for Data-Access Time

clock cycle preceding the MSB. A falling edge on FSTRT indicates that the MSB is available on the SDATA output.

The SFRM output (normally high when  $\overline{INVFRM} = V_{DD}$ ) goes low coincident with the MSB appearing at the SDATA pin. SFRM returns high 16 clock cycles later. The polarity of SFRM can be inverted by tying the INVFRM input to DGND. A minimum of 18 clock cycles per conversion is required to obtain a valid SFRM output.

See Figure 3 for the data-access and data-hold timing diagram if several devices share the serial bus. The equivalent load circuits for data-access and data-hold timing are shown in Figures 4 and 5.

#### **Digital Interface**

The MAX121 serial interface is compatible with SPI and QSPI serial interfaces. In addition, two framing signals (FSTRT and SFRM) are provided to allow the MAX121 to easily interface to most digital-signal processors (DSP) with no external glue logic. The INVCLK input inverts the phase of SCLK relative to CLKIN, and the INVFRM input inverts the phase of the SFRM output. These control signals allow the MAX121 to directly interface to devices with many different serial-interface standards. Specific information for interfacing the MAX121 with SPI, QSPI, and several DSP devices is included in the Applications Information section.

Figure 5. Load Circuits for Data-Hold Time

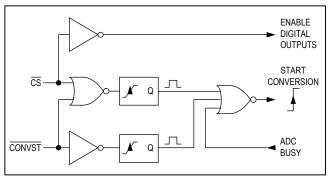

Figure 6. Conversion Control Logic

#### **Timing and Control**

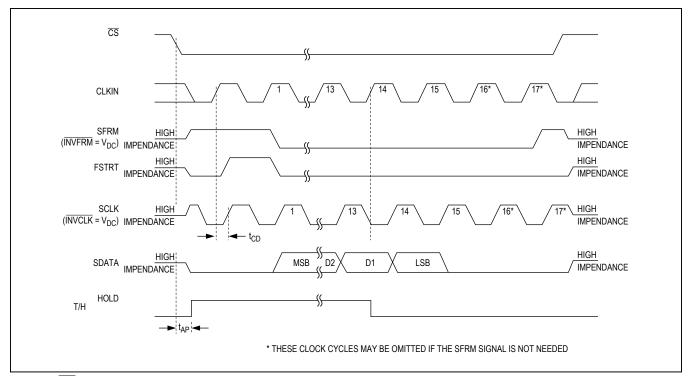

The MAX121 has three possible modes of operation, as outlined in the timing diagrams of Figures 7–9 and discussed in the *Operating Modes* section.

In Mode 1, the  $\overline{\text{CONVST}}$  input is used to control the start of the conversion. Mode 1 is intended for DSP and other applications where the analog input must be sampled at a precise instant in time.

In Mode 2, the  $\overline{\text{CS}}$  input controls the start of the conversion. This mode is useful when several devices are multiplexed on the same serial data bus, since the MAX121 outputs are placed in a high-impedance state when  $\overline{\text{CS}}$  is pulled high.

Mode 3 is the continuous-conversion mode. This mode is intended for data logging and similiar applications where the MAX121 is directly linked to memory through a first-in/first-out (FIFO) buffer or a direct memory access (OMA) port.

In all three operating modes, the start of conversion is controlled by either the  $\overline{\text{CS}}$  or the  $\overline{\text{CONVST}}$  input. Both of these inputs must be low for a conversion to take place. Figure 6 shows the logic equivalent for the conversion circuitry. Once the conversion is in progress, it cannot be restarted.

#### **Operating Modes**

## Mode 1: $\overline{\text{CONVST}}$ Controls Conversion Starts (MODE = $V_{DD}$ , $\overline{\text{CS}}$ = DGND)

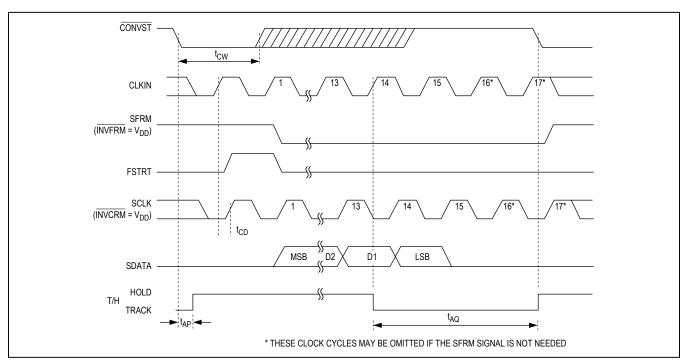

Figure 7 shows the timing diagram for mode 1. In this mode, conversion start operations are controlled by the  $\overline{\text{CONVST}}$  input.

A falling edge on the  $\overline{\text{CONVST}}$  input places the T/H into the hold mode and starts a conversion in the successive approximation register (SAR). The FSTRT (normally low) output goes high on the next rising clock edge and remains high for one clock cycle. On the next rising clock edge, FSTRT goes low and the SFRM output goes low ( $\overline{\text{INVFRM}} = V_{DD}$ ), indicating that the MSB is ready to be latched. SFRM remains high for 16 clock cycles ( 4 data bits plus 2 trailing zeros).

The T/H amplifier returns to the track mode when the 14th bit (D0) is clocked out of the SDATA pin. A new conversion can be initiated by the CONVST input after the 400ns minimum acquisition time has been satisfied.

$\overline{\text{CS}}$  must be low to start a conversion. In applications where the MAX121 interfaces with a dedicated serial port,  $\overline{\text{CS}}$  can be hardwired to DGND. To interface the MAX121 to a multiplexed serial bus,  $\overline{\text{CS}}$  can be externally driven low to enable conversions, or driven high to place the serial outputs into a high-impedance state.

Figure 7. CONVST Controls Conversion Starts (Mode 1)

## Mode 2: CS Controls Conversion Starts (MODE = V<sub>DD</sub>, CONVST = DGND)

Figure 8 shows the timing diagram for mode 2. In mode 2,  $\overline{CS}$  controls the conversion start and enables the serial output pins. Mode 2 is useful in applications where the MAX121 shares the output data bus with other devices. When  $\overline{CS}$  is driven high, the MAX121 is disabled and its serial outputs (SCLK, SDATA, SFRM, and FSTRT) are placed into a high-impedance state.

A falling edge on the  $\overline{\text{CS}}$  input places the T/H into the hold mode and starts a conversion in the SAR. The FSTRT and SFRM outputs can be used to frame the output data as described in the mode 1 section.  $\overline{\text{CS}}$  must remain low for the duration of the conversion.

The T/H amplifier returns to the track mode when the 14th bit (D0) is clocked out of the SDATA pin. A new conversion can be initiated by the  $\overline{\text{CS}}$  input after the 400ns acquisition time has been satisfied.

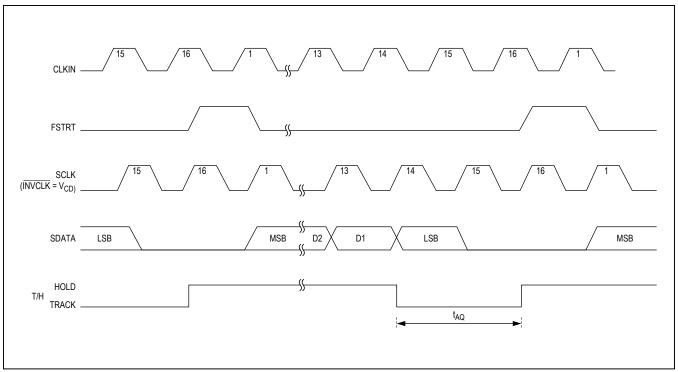

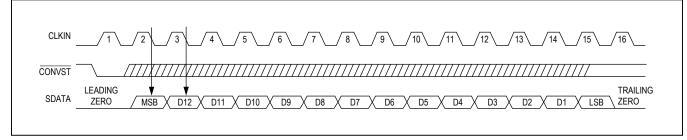

## Mode 3: Continuous-Conversion Mode (CONVST = CS = MODE = DGND)

For applications that do not require precise control of sampling in time, such as data logging, the MAX121 can operate in continuous-conversion mode, directly linked to memory through DMA ports or a FIFO buffer.

In this mode, conversions are performed continuously at the rate of one conversion for every 16 clock cycles, which includes 2 clock cycles for the T/H acquisition time. To satisfy the 400ns minimum acquisition-time requirement within 2 clock cycles, the MAX121 's maximum clock frequency is limited to 5MHz when operating in mode 3.

The FSTRT output is used to frame data, as described in the mode 1 section and the mode 3 timing diagram (Figure 9). The SFRM output is meaningless in mode 3, since it will not change state.

The MODE input should be hardwired to DGND, since this input must be low when the MAX121 powers up for proper operation of mode 3. To disable conversions, drive  $\overline{\text{CONVST}}$  high. To put the serial outputs into a high-impedance state, drive  $\overline{\text{CS}}$  high.

Figure 8. CS Controls Conversion Starts (Mode 2)

Figure 9. Continuous-Conversion Mode (Mode 3)

#### **Applications Information**

#### **Initialization After Power-Up**

Upon power-up, the first conversion of the MAX121 will be valid if the following conditions are met:

- Allow 16 clock cycles for the internal T/H to enter the track mode, plus a minimum of 400ns in the track mode for the data-acquisition time.

- Make sure the reference voltage has settled. Allow 0.5ms for each 1µF of reference bypass capacitance 11ms for a 22µF capacitor.

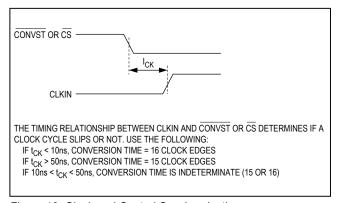

#### **Clock and Control Synchronization**

If the clock and conversion start inputs (CONVST or CS—see the *Operating Modes* section) are not synchronized, the conversion time can vary from 15 to 16 clock cycles. The SAR always changes state on the rising edge of the CLKIN input. To ensure a fixed conversion time, see Figure 10 and the following guidelines.

For a conversion time of 15 clock cycles, the conversion start input(s) should go low at least 50ns before the next rising edge of CLKIN. For a conversion time of 16 clock

Figure 10. Clock and Control Synchronization

cycles, the conversion start input(s) should go low within 10ns of the next rising edge of CLKIN. If the conversion start input(s) go low from 10ns of the next rising edge of CLKIN. If the conversion start input(s) go low from 10ns to 50ns before the next rising edge of CLKIN, the number of clock cycles required is undefined and can be either 15 or 16. For best analog performance, the conversion start inputs must be synchronized with CLKIN.

#### **Maximum Clock Rate tor Serial Interface**

The maximum serial clock rate depends upon the minimum setup time required by the receiving processor's serial data input and the ADC's maximum clock-to-data delay. The MAX121 allows two fundamentally different methods of clocking data into the processor. In the first clocking method, CLKIN is both the input clock to the MAX121 and the serial clock for the processor. With the second method, CLKIN is the input clock for the MAX121 while SCLK is the serial clock for shifting data into the processor (see Figure 11).

The first method would generally be used with simple serial-interface standards (such as SPI) where the processor does not support asynchronous data transfers. The maximum clock-to-data delay would be  $t_{CD}$  +  $t_{SC}$ . For this case, calculate the maximum serial clock rate with the following formula:

$$f_{CLKIN} = (1/2) \times 1/(t_{SU} + t_{CD} + t_{SC})$$

where  $t_{SU}$  is the minimum data setup time required at the processor serial data input,  $t_{CD}$  is the maximum CLKIN to-SCLK delay of the MAX121, and  $t_{SC}$  is the maximum SCLK-to-SDATA delay for the MAX121.

The second type of interface is intended for applications where the processor supports asynchronous data transfers. The SCLK output of the MAX121 drives the serial clock of the processor, eliminating the  $t_{CD}$  term from the above equation and allowing the use of faster clocks. For this case, calculate the maximum serial clock rate with the following formula:

$$f_{CLKIN} = (1/2) \times 1/(t_{SU} + t_{SC})$$

where the variables are as defined above.

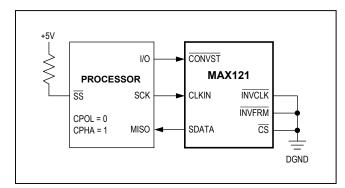

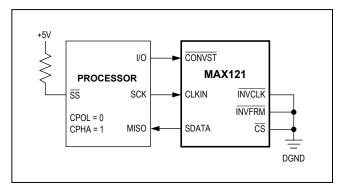

#### Motorola SPI Serial Interface (CPOL = 0, CPHA = 1)

Figure 13 shows the MAX121 and processor interface connections required to support the SPI standard. Figure 12 shows the SPI interface timing diagram. For SPI interfaces, the processor \$\overline{SS}\$ input should be pulled high, to configure the processor as the master. An I/O port from the processor drives the MAX121 \$\overline{CONVST}\$ (mode 1) or \$\overline{CS}\$ (mode 2) low to control the conversion starts. The SCK output of the processor will drive the CLKIN of the MAX121. The MISO I/O of the processor is driven by the SDATA output of the MAX121.

The SPI standard requires that all data transfers occur in blocks of 8 bits, but the MAX121 outputs data in 16-bit blocks. Therefore, two 1-byte read operations are required to receive the full 14 data bits from the MAX121.

A conversion is initiated by driving the processor I/O port low. Next, a write operation must be performed by the processor to activate the serial clock and read the first 8 bits of data from the MAX121.

The MAX121 output data transitions on the rising edge of the clock. The processor reads data on the falling edge of the clock (CPHA = 1). This provides one half clock cycle to satisfy the minimum setup and hold time requirement of the processor data input. The maximum clock rate for SPI interfaces is 2MHz.

The first byte of data read by the processor will consist of a leading zero followed by the 7 MSBs of data. A second write operation should then be initiated to read the second byte of data, which contains the 7 LSBs of conversion data followed by a trailing zero. To minimize errors due to the droop of the MAX121 internal T/H, limit the maximum time delay between the conversion start and the end of the second read operation to no more than  $160\mu s$ .

Figure 11. Timing Diagram for Serial Data

## Motorola QSPI Serial Interlace (CPOL = 0, CPHA = 1)

Figure 14 shows the connections required to implement a QSPI interface with the MAX121. The timing diagram for this interface is shown in Figure 15. The QSPI standard is similiar to SPI, with the primary differences as follows:

- 1) QSPI allows arbitrary length data transfers from 8 to 16 bits, so only one read operation is required to receive the 14 bits of output data from the MAX121.

- QSPI allows clock rates up to 4MHz, compared to 2MHz with SPI.

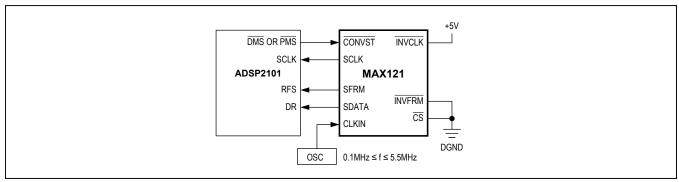

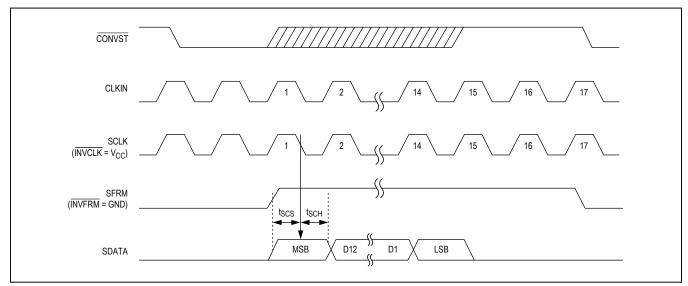

#### **ADSP2101 Serial Interlace**

Figure 16 shows the connections required to interface the MAX121 to Analog Devices' ADSP2101 DSP. Figure 17 is a plot of the timing diagram. The ADSP2101 has a high-speed serial interface with a minimum serial data setup

time of 10ns ( $t_{SCS}$ ) and a minimum data-hold time of 10ns ( $t_{SCH}$ ). This interface permits operation of the MAX121 at its maximum clock rate of 5.5MHz.

An output port of the ADSP2101 drives the MAX121  $\overline{\text{CONVST}}$  input low to initiate a conversion. The SFRM output of the MAX121 drives the RFS (Receive Frame Synchronization) input to the DSP low to indicate that the MSB has been shifted out of the MAX121 SDATA pin. On the next falling edge on SCLK, the MSB is shifted into the ADSP2101 serial input. Note that the MAX121  $\overline{\text{INVFRM}}$  input is grounded to provide the proper phase for the SFRM output.

The SCLK terminal of the ADSP2101 is configured as an input and is driven by the MAX121 SCLK output to clock data into the DSP. The SFRM output remains low for 16 clock cycles, allowing the 14 data bits to be shifted into the ADSP2101, followed by 2 trailing zeros.

Figure 12. SPI Interface Timing Diagram

Figure 13. SPI Interface Circuit

Figure 14. QSPI Interface Circuit

Figure 15. QSPI Interface Timing Diagram

Figure 16. ADSP2101 to MAX121 Interface

Figure 17. ADSP2101 Interface Timing Diagram

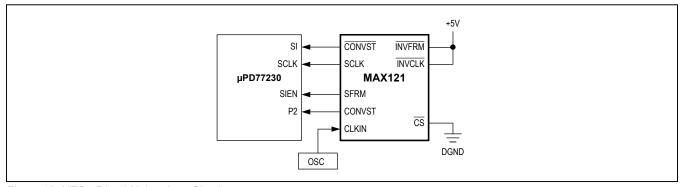

Figure 18. NEC μP077230 Interlace Circuit

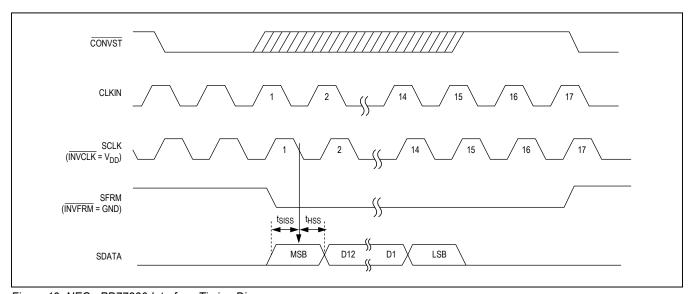

#### NEC µPD77230 Serial Interface

Figure 18 shows the connections required to interface the MAX121 to NEC's  $\mu$ PD77230 DSP without external glue logic. The timing diagram is shown in Figure 19. See the *Maximum Clock Rate for Serial Interface* section to determine the maximum usable clock rate for this interface, substituting t<sub>SISS</sub> for t<sub>SU</sub> in the equations. The t<sub>HSSI</sub> term in the timing diagram is the minimum data-hold time for the  $\mu$ PD77230's serial data input.

An I/O port of the  $\mu$ PD77230 drives the MAX121  $\overline{\text{CONVST}}$  pin low to initiate a conversion. The MAX121 SFRM output drives the SIEN (Serial Input Enable) terminal of the DSP low to frame the data. On the next falling edge of SCLK, the MSB is shifted into the SI (Serial Input) pin of the  $\mu$ PD77230. SDATA drives the SI terminal of the DSP. The MSB is followed by the other 13 data bits and two trailing zeros, after which the SFRM output returns high to disable the DSP serial input until the next conversion is initiated.

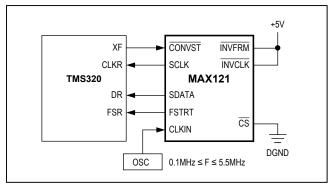

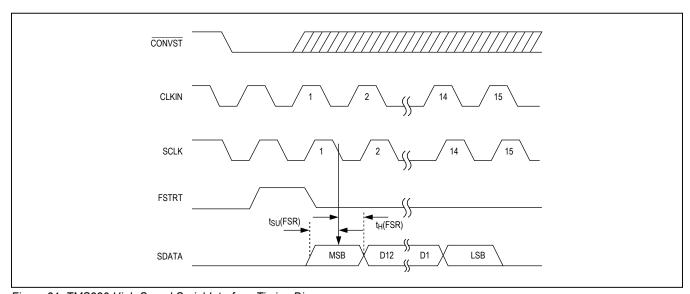

#### TMS320 High-Speed Serial Interface

The flexibility of the MAX121 permits the implementation of a variety of interfaces with the Texas Instruments' TMS320 DSP. The *TMS320 Simple Serial Interface* section of this data sheet discusses the simplest type of MAX121-to-TMS320 interface, which works with serial clock rates up to 3.2MHz.

This section describes an interface that allows the maximum throughput to be obtained from the MAX121-to-TMS320 system, by operating the MAX121 at its maximum clock. Figure 20 shows the interconnections required to implement this interface. Figure 21 is the timing diagram for this interface.

The MAX121 CLKIN is driven by an external clock oscillator. The XFO I/O port of the TMS320 drives the MAX121 CONVST input low to initiate a conversion. CLKR (Receive Clock) of the TMS320 is configured as an input and driven by the MAX121 SCLK output. Data on the MAX121 SDATA output changes state on the rising edge of the clock, while data is latched into the DR input of the TMS320 on the falling edge. This provides one half clock cycle to meet the setup and hold time requirements of the TMS320 DR input. The maximum skew between the MAX121 SCLK and SDATA is ±65ns at +25°C, so one half clock cycle is more than sufficient to guarantee that the setup and hold time requirement is satisfied.

The FSTRT output of the MAX121 drives the FSR input of the TMS320 to frame the data. A falling edge on the FSTRT output indicates that the MSB is ready to be latched. On the next falling clock edge, the MSB is latched into the TMS320. For this interface, the TMS320 is configured to receive a 16-bit word (RLEN = 01 in the TMS320 serial-port global control register) so the 14 bits of data are clocked into the DSP, followed by two trailing zeros.

Figure 19. NEC μPD77230 Interface Timing Diagram

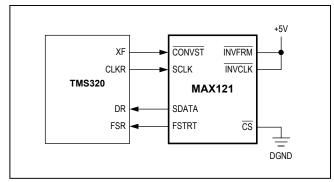

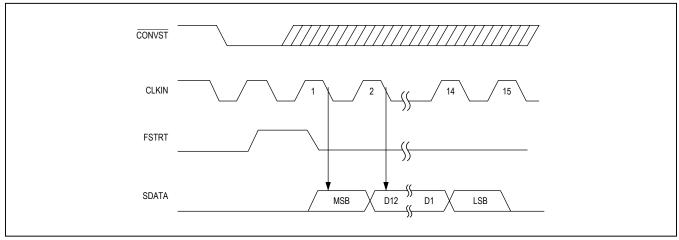

#### **TMS320 Simple Serial Interface**

Figure 22 shows an application circuit using the simplest interface between the MAX121 and the TMS320. The timing diagram for this circuit is shown in Figure 23.

In this circuit, the CLKR port of the TMS320 is configured as a clock output and drives the CLKIN of the MAX121. The MAX121 output changes state on the rising edge of the CLKIN while the data is latched into the DR port of the TMS320 on the falling edge. The XF1 I/O port of the TMS320 drives the MAX121 CONVST input low to initiate a conversion. The FSTRT output of the MAX121 drives the FSR input of the TMS320 to frame the data. A falling edge on the FSTRT output indicates that the MSB is ready to be latched. On the next falling clock edge, the MSB is latched into the TMS320. For this interface, the TMS320 is configured to receive a 16-bit word (RLEN = 01 in the TMS320 serial-port global control register) so the 14 bits of data are

Figure 20. TMS320 High-Speed Serial-Interface Circuit

clocked into the DSP, followed by two trailing zeros. At  $T_A$  = +25°C, the clock frequency is limited to approximately 3.2MHz with this interface, due to the CLKIN-to-SDATA maximum delay of 130ns and the 25ns setup and hold time requirement for the TMS320.

Figure 24 is a listing of a short program written in the TMS320 assembly language that initiates conversions in the TMS320 and ships the output data back to the host PC. The C language program listed in Figure 25 displays the results of every 30,000th conversion on the PC screen, along with the min and max values for all conversions performed during one operating sequence.

#### **Digital Bus/Clock Noise**

If the clock is active when the T/H is sampling the input signal, errors can be caused by coupling from the CLKIN pin to the analog input. If this is a problem, the clock should be disabled for one clock cycle while the T/H is placed into hold mode. In mode 1, the clock should be disabled (CLKIN = DGND) for one cycle while CONVST is pulsed low. In mode 2, the clock should be disabled (CLKIN = DGND) for one clock cycle while CS is driven low. The clock should be reactivated on the first cycle after the conversion is started (CONVST or CS pulsed low).

#### Layout, Grounding and Bypassing

For best system performance, use PCBs with separate analog and digital ground planes. Wirewrap boards are not recommended. The two ground planes should be tied together at the low-impedance power-supply source, as shown in Figure 26.

Figure 21. TMS320 High-Speed Serial-Interface Timing Diagram

The board layout should ensure that digital and analog signal lines are kept separate, as much as possible. Take care not to run analog and digital (especially clock) lines parallel to one another.

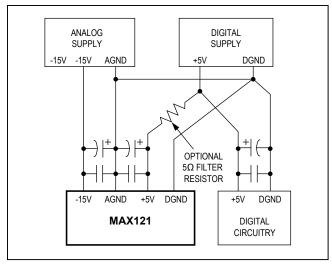

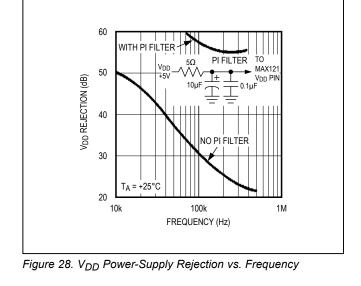

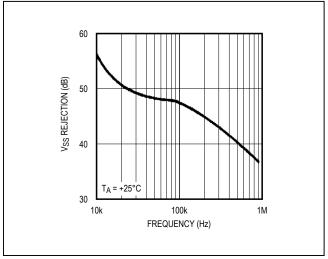

The high-speed comparator in the ADC is sensitive to high-frequency noise in the  $V_{DD}$  and  $V_{SS}$  power supplies. Bypass these supplies to the analog-ground plane with  $0.1\mu F$  and  $10\mu F$  bypass capacitors. Keep capacitor leads at a minimum length for best supply-noise rejection. If the +5V power supply is very noisy, a  $5\Omega$  resistor can be connected, as shown in Figure 26, to filter this noise. Figure 27 shows the negative power-supply ( $V_{SS}$ ) rejection vs. frequency. Figure 28 shows the positive power-supply ( $V_{DD}$ ) rejection vs. frequency, with and without the optional  $5\Omega$  resistor.

#### **Dynamic Performance**

High-speed sampling capability and 308kHz throughput make the MAX121 ideal for wideband signal processing. To support these and other related applications, FFT (Fast Fourier Transform) test techniques are used to guarantee the ADC's dynamic frequency response, distortion, and noise at the rated throughput. Specifically, this involves applying a low-distortion sinewave to the ADC input and recording the digital conversion results for a specified time. The data is then analyzed using an FFT algorithm, which determines its spectral content. Conversion errors are then seen as spectral elements outside of the fundamental input frequency.

ADCs have traditionally been evaluated by specifications such as Zero and Full-Scale Error, Integral Nonlinearity (INL), and Differential Nonlinearity (DNL). Such parameters are widely accepted for specifying performance with DC and slowly varying signals, but are less useful in signal processing applications where the ADC's impact on the system transfer function is the main concern. The significance of various DC errors does not translate well to the dynamic case, so different tests are required.

Figure 22. TMS320 Simple Serial-Interface Circuit

## Signal-to-Noise Ratio and Effective Number of Bits

The signal-to-noise plus distortion ratio (SINAD) is the ratio of the fundamental input frequency's RMS amplitude to the RMS amplitude of all other ADC output signals. The output band is limited to frequencies above DC and below one-half the ADC sample (conversion) rate.

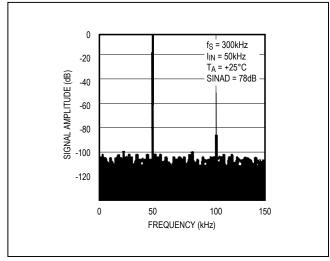

The theoretical minimum ADC noise is caused by quantization error and is a direct result of the ADC's resolution: SINAD = (6.02N + 1.76)dB, where N is the number of bits of resolution. A perfect 14-bit ADC can, therefore, do no better than 86dB. An FFT plot of the output shows the output level in various spectral bands. Figure 29 shows the result of sampling a pure 50kHz sinusoid at a 300kHz rate with the MAX121.

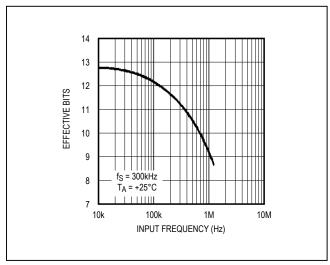

By transposing the equation that converts resolution to SINAD, the user can, from the measured SINAD, determine the effective resolution (effective number of bits) that the ADC provides: N = (SINAD - 1.76)/6.02. Figure 30 shows the effective number of bits as a function of the input frequency for the MAX121.

Figure 23. TMS320 Simple Serial-Interface Timing Diagram

Figure 24.TMS320 Assembly Language Program to Control Conversions Using the TMS320 Simple Serial Interface

```

Publics;

.global maxim

.global wait_sample

.global wait_loop

.global next_sample

.global IOF_MASK_AMASK

.global IOF_SET_XFI

.global IOF_RESET_XFI

.global CTRL

.global SERGLOB1

.global SERPRTX1

.global SERPRTR1

.global SERTIM1

.global SERTIM1VAL

.global HOST_DATA

, Data, Data,

; Preserve XFO settings

IOF AMASK

000000EH

.word

IOF_SET_XF1

0000060H

Set XF1 as output high

IOF_RESET_XF1

0000020H

; Set XF1 as output low

.word

CTRL

0808000H

word

; Pointer to peripheral-bus memory map

SERGLOB1

8120280H

.word

; Setup serial 1 global control (80)

Use internal recieve clock

FSR active during entire transfer

16-bit rcv data length

FSR active low

Take rcvr out of reset

SERPRTX1

H0000000H

Setup serial 1 xmt port control (82)

.word

SERPRTR1

.word

0000111H

Setup serial 1 rcv port control (83)

CLKR1 = serial port pin

DR1 = serial port pin

FSR1 = serial port pin

SERTIM1

.word

00003C0H

Setup serial 1 timer control (84)

Start rcv timer, 50% duty cycle,

internal clk src = 1/2 CLKOUT is

used to increment rcvr timer.

SERTIMIVAL

.word

00020000H

Timer period values RX and TX

Rcvr timer is high order 16-bits

(CLKOUT/2)/2 = 1.875Mhz CLKR1 - >MAX121 CLKIN

HOST_DATA

word

00804000H

; Memory address of host data port

```

Figure 24.TMS320 Assembly Language Program to Control Conversions Using the TMS320 Simple Serial Interface (continued)

## 308ksps ADC with DSP Interface and 78dB SINAD

```

; Functions;

maxim

Initialization Code

0,ST

Initialize status register

LDIU

128,DP

Initialize data page register

0985CH,SP

Initialize stack pointer

LDI

IOF,R1

Read in I/O Flags register to R1

@IOF_AMASK,R1

AND

Remove current XF1 bits, preserve XF0 settings

@IOF_SET_XF1,R1

Set XF1 (CONVST*) Inactive (high)

R1, IOF

LDI

Make it so!

@CTRL, AR0

I DI

Load AR0 w/ptr to control reg base

LDI

@HOST_DATA,AR1

Load AR1 w/host interface address

LDI

@SERTIM1VAL,R0

STI

R0, *+AR0(86)

Setup serial ch1 timer period value

@SERGLOB1,R0

R0, *+AR0(80)

STI

Setup serial ch1 global register

@SERPRTX1,R0

R0, *+AR0(82)

STI

Setup serial ch1 xmt control register

LDI

@SERPRTR1,R0

R0, *+AR0(83)

Setup serial ch1 rcv control register

STI

@SERTIM1,R0

STI

R0, *+AR0(84)

Setup serial ch1 timer register

next_sample

Start Conversion -->

(CONVST*)

LDI

IOF,R1

Read in I/O Flags register to R1

Remove current XF1 bits, preserve XF0 settings

AND

@IOF_AMASK,R1

@IOF_SET_XF1,R1

Set XF1 (CONVST*) Inactive (high)

OR

LDI

R1, IOF

Make it so!

@IOF_AMASK,R1

AND

Remove current XF1 bits, preserve XF0

OR

@IOF_RESET_XF1,R1

Set XF1 (CONVST*) Active (low)

LDI

R1, IOF

Make it so!

```

Figure 24.TMS320 Assembly Language Program to Control Conversions Using the TMS320 Simple Serial Interface (continued)

## 308ksps ADC with DSP Interface and 78dB SINAD

```

wait_sample

wait for completion of conversion

MAX121 SFRM Active signals TMS320 FSR1 that data transfer

is ready to start.

Read in Serial Ch 1 global register

*+AR0 (80), R2

LDI

AND

01H, R2

Check for RRDY Active (1)

RRDY goes active when 16-bits have been rcvd

wait_sample

Keep waiting if not ready

*+AR0 (92), R3

Ready, read value from Data Receive register

R3, *+AR1 (0)

STI

Send out value to host

Arbitrary wait time until start of next convert.

100, R0

LDI

wait_loop:

SUB1

1, R0

\mathsf{BNZ}

Keep waiting until R0 decremented to zero

wait_loop

BR

@next_sample

Go start next convert

```

Figure 24.TMS320 Assembly Language Program to Control Conversions Using the TMS320 Simple Serial Interface (continued)

```

Project:

Maxim 121 to TMS320C30 Application Note

File:

readdata.c

This file contains a PC based program used to read data from the TMS320C30 Evaluation Module (EVM) and display the

Purpose:

This file may be compiled with either the Microsoft C Compiler of Borland C++ Compiler.

Tabstops:

$Log:$

Edit History:

* *

Description

09/24/92

KHB

Initial Creation

/* for printf( ) */

#include <stdio.h>

#include <conio.h>

/* for kbhit(), getch(), and inpw */

#define VERSION_STAMP 1

void

main(void)

int value;

int quit = 0;

int min = 32767;

int max = -32768;

printf( "TMS320 EVM Data Display Program - Version %d\n", VERSION_STAMP);

printf( "m = reset Max/Min values, ESC to quit\n\n" )`

```

Figure 25. C Language Program to Log Data from MAX121 Conversions

```

while( !quit )

if(kbhit())

switch ( gletch ( ))

case 'm':

/* Clear Max/Min Storage Variables */

max = -32768

min = 32767;

break:

/* Quit Program */

case 'q':

case 0x1B:

quit = 1;

break;

for (x=o; x<30000; x++)

/* Gather samples as fast as possible and update Max/Min */

^{\prime \star} Only output every 30,000th sample. The 30,000 has no ^{\,\star \prime}

/* specific origin other than the display updated at a */

/* comfortable rate. */

value = inpw ( 0x0240+0x0808 );

/* EVM Data Port */

value >>= 2;

/* Shift from 16-bit back to 14-bit */

/* Update Max/Min */

If( value > max )

max = value;

else if( value < min)

main = value;

/* Output the latest sample in decimal and hex along with Max/Min */

printf(" %06d %04Xh min:%06d \r", value, value, min, max);

/* Exit */

Printf( '\n\n" );

return;

```

Figure 25. C Language Program to Log Data from MAX121 Conversions (continued)

## 308ksps ADC with DSP Interface and 78dB SINAD

Figure 26. Power-Supply Grounding

Figure 27. V<sub>SS</sub> Power-Supply Rejection vs. Frequency

Figure 29. MAX121 FFT Plot

Figure 30. Effective Bits vs. Input Frequency

#### **Total Harmonic Distortion**

If a pure sine wave is sampled by an ADC at greater than the Nyquist frequency, the nonlinearities in the ADC's transfer function create harmonics of the input frequency present in the sampled output data.

Total Harmonic Distortion (THD) is the ratio of the RMS sum of all the harmonics (in the frequency band above DC and below one-half the sample rate, but not including the DC component) to the RMS amplitude of the fundamental frequency. This is expressed as follows:

THD = 20 log

$$\sqrt{\frac{V_2^2 + V_3^2 + V_4^2 + V_N^2}{V_1}}$$

where  $V_1$  is the fundamental RMS amplitude, and  $V_2$  through  $V_N$  are the amplitudes of the 2nd through Nth harmonics. The THD specification in the *Electrical Characteristics* includes the 2nd through 5th harmonics.

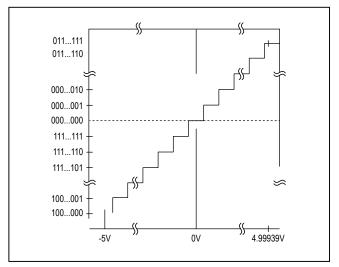

Figure 31. Bipolar Transfer Function

#### **Spurious-Free Dynamic Range**

Spurious-free dynamic range is the ratio of the fundamental RMS amplitude to the amplitude of the next largest spectral component (in the frequency band above DC and below one-half the sample rate). Usually the next largest spectral component occurs at some harmonic of the input frequency. However, if the ADC is exceptionally linear, it may occur only at a random peak in the ADC's noise floor.

#### **Transfer Function**

The plot in Figure 31 graphs the bipolar input/output transfer function for the MAX121. Code transitions occur halfway between successive integer LSB values. Output coding is two's-complement binary, with 1 LSB =  $610\mu V$  (10V/16384).

### **Ordering Information**

| PART            | TEMP RANGE     | PIN-PACKAGE  |

|-----------------|----------------|--------------|

| MAX121CPE+      | 0°C to +70°C   | 16 PDIP      |

| MAX121CWE+      | 0°C to +70°C   | 16 Wide SO   |

| MAX121CAP+      | 0°C to +70°C   | 20 SSOP*     |

| MAX121EPE+      | -40°C to +85°C | 16 PDIP      |

| MAX121EWE+      | -40°C to +85°C | 16 Wide SO   |

| MAX121EAP+      | -40°C to +85°C | 20 SSOP*     |

| MAX121EVKIT-DIP | 0°C to +70°C   | Through-Hole |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 16 PDIP         | P16+3           | <u>21-0043</u> | _                   |

| 16 Wide SO      | W16+2           | 21-0042        | <u>90-0107</u>      |

| 20 SSOP         | A20+1           | <u>21-0056</u> | 90-0094             |

<sup>\*20-</sup>pin SSOP is 50% smaller than 16-pin SO.

### **MAX121**

## 308ksps ADC with DSP Interface and 78dB SINAD

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                           | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------|------------------|

| 0                  | 1/93             | Initial release                                       | _                |

| 3                  | 1/12             | Remove military grade and update Ordering Information | 1–4, 24          |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.