# 阅读申明

- 1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任何异议请及时告之,我们将妥善解决。

- 2.本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

- 3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

- 4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

- 1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

- 2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

- 3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

- 4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets" .

FN3577.8

# 8-Bit, 20MSPS, Flash A/D Converter

The HI1175 is an 8-bit, analog-to-digital converter built in a  $1.4\mu m$  CMOS process. The low power, low differential gain and phase, high sampling rate, and single 5V supply make the HI1175 ideal for video and imaging applications.

The adoption of a 2-step flash architecture achieves low power consumption (60mW) at a maximum conversion speed of 20MSPS (Min), 35MSPS typical with only a 2.5 clock cycle data latency. The HI1175 also features digital output enable/disable and a built in voltage reference. The HI1175 can be configured to use the internal reference or an external reference if higher precision is required.

## **Ordering Information**

| PART NUMBER | TEMP.<br>RANGE (°C) | PACKAGE          | PKG.<br>NO. |  |

|-------------|---------------------|------------------|-------------|--|

| HI1175JCB   | -40 to 85           | 24 Ld SOIC       | M24.2-S     |  |

| HI1175-EV   | 25                  | Evaluation Board |             |  |

#### **Features**

| • | Resolution | <br> | 8-Bit ±0.3 L | SB (DNL) |

|---|------------|------|--------------|----------|

|   |            |      |              |          |

- Maximum Sampling Frequency . . . . . . . . . . . . . 20MSPS

- Low Power Consumption . . . . . 60mW (at 20MSPS Typ) (Reference Current Excluded)

- · Built-In Sample and Hold Circuit

- Built-In Reference Voltage Self Bias Circuit

- Three-State TTL Compatible Output

- Single +5V Power Supply

- Low Input Capacitance......11pF (Typ)

- Evaluation Board Available (HI1175-EV)

- · Low Cost

- · Direct Replacement for the Sony CXD1175

## **Applications**

- · Video Digitizing

- · PC Video Capture

- Image Scanners

- TV Set Top Boxes

- Multimedia

- Personal Communication Systems (PCS)

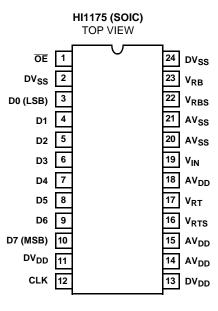

#### **Pinout**

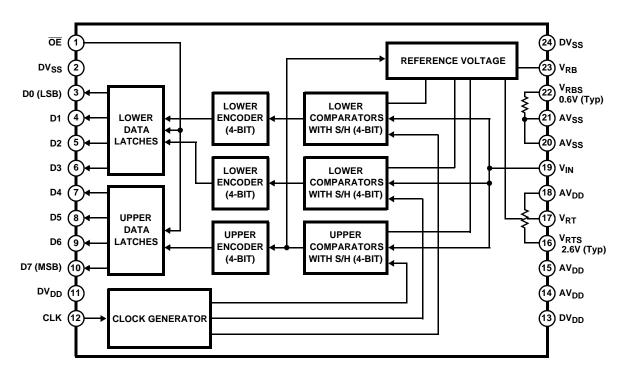

## Functional Block Diagram

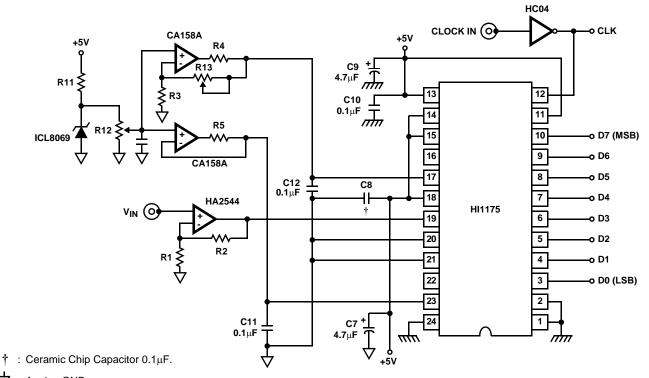

# **Typical Application Schematic**

: Analog GND.

NOTE: It is necessary that  $AV_{DD}$  and  $DV_{DD}$  pins be driven from the same supply. The gain of analog input signal can be changed by adjusting the ratio of R2 to R1.

# Pin Descriptions and Equivalent Circuits

| PIN<br>NUMBER | SYMBOL           | EQUIVALENT CIRCUIT                     | DESCRIPTION                                                                                              |  |  |  |

|---------------|------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| 1 ŌE          |                  | ①—W——————————————————————————————————— | When $\overline{OE}$ = Low, Data is valid.<br>When $\overline{OE}$ = High, D0 to D7 pins high impedance. |  |  |  |

| 2, 24         | DV <sub>SS</sub> |                                        | Digital GND.                                                                                             |  |  |  |

| 3-10          | D0 to D7         |                                        | D0 (LSB) to D7 (MSB) Output.                                                                             |  |  |  |

| 11, 13        | DV <sub>DD</sub> | I                                      | Digital +5V.                                                                                             |  |  |  |

| 12            | CLK              | 12—W—DV <sub>DD</sub>                  | Clock Input.                                                                                             |  |  |  |

| 16            | V <sub>RTS</sub> | P AV <sub>DD</sub>                     | Shorted with V <sub>RT</sub> generates, +2.6V.                                                           |  |  |  |

| 17            | V <sub>RT</sub>  | φ AV <sub>DD</sub>                     | Reference Voltage (Top).                                                                                 |  |  |  |

| 23            | V <sub>RB</sub>  | 17 23 AV <sub>SS</sub>                 | Reference Voltage (Bottom).                                                                              |  |  |  |

| 14, 15, 18    | AV <sub>DD</sub> |                                        | Analog +5V.                                                                                              |  |  |  |

| 19            | V <sub>IN</sub>  | 19 AV <sub>SS</sub>                    | Analog Input.                                                                                            |  |  |  |

| 20, 21        | AV <sub>SS</sub> |                                        | Analog GND.                                                                                              |  |  |  |

| 22            | V <sub>RBS</sub> | Q AV <sub>SS</sub>                     | Shorted with V <sub>RB</sub> generates +0.6V.                                                            |  |  |  |

## **Absolute Maximum Ratings**

| 7 V                                                        |

|------------------------------------------------------------|

| $V_{\mbox{\scriptsize DD}}$ to $V_{\mbox{\scriptsize SS}}$ |

| $V_{DD}$ to $V_{SS}$                                       |

| $V_{DD}$ to $V_{SS}$                                       |

| $V_{\mbox{\scriptsize DD}}$ to $V_{\mbox{\scriptsize SS}}$ |

|                                                            |

## **Operating Conditions** (Note 1)

| Temperature Range, T <sub>A</sub> 40°C to 85°C                                                                       |

|----------------------------------------------------------------------------------------------------------------------|

| Supply Voltage                                                                                                       |

| AV <sub>DD</sub> , AV <sub>SS</sub> , DV <sub>DD</sub> , DV <sub>SS</sub> +4.75V to +5.25V                           |

| DGND-AGND                                                                                                            |

| Reference Input Voltage                                                                                              |

| V <sub>RB</sub>                                                                                                      |

| V <sub>RT</sub>                                                                                                      |

| Analog Input Range, V <sub>IN</sub> V <sub>RB</sub> to V <sub>RT</sub> (1.8V <sub>P-P</sub> to 2.8V <sub>P-P</sub> ) |

| Clock Pulse Width                                                                                                    |

| t <sub>PW1</sub>                                                                                                     |

| tpwo 25ns (Min)                                                                                                      |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| SOIC Package                             | . 98                   |

| Maximum Junction Temperature             |                        |

| Maximum Storage Temperature Range, TSTG  | -65°C to 150°C         |

| Maximum Lead Temperature (Soldering 10s) | 300°C                  |

| (SOIC - Lead Tips Only)                  |                        |

|                                          |                        |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{\mbox{\scriptsize JA}}$  is measured with the component mounted on an evaluation PC board in free air.

## **Electrical Specifications** $f_C = 20 \text{ MSPS}, V_{DD} = +5V, V_{RB} = 0.5V, V_{RT} = 2.5V, T_A = 25^{\circ}C \text{ (Note 1)}$

| PARAMETER                                  | TEST CONDITIONS                                             | MIN | TYP  | MAX  | UNIT   |

|--------------------------------------------|-------------------------------------------------------------|-----|------|------|--------|

| SYSTEM PERFORMANCE                         |                                                             | 1   | •    |      | "      |

| Offset Voltage                             |                                                             | -   | -    | -    | -      |

| E <sub>OT</sub>                            |                                                             | -60 | -35  | -10  | mV     |

| E <sub>OB</sub>                            |                                                             | 0   | +15  | +45  | mV     |

| Integral Non-Linearity, INL                | f <sub>C</sub> = 20 MSPS, V <sub>IN</sub> = 0.6V to 2.6V    | -   | ±0.5 | ±1.3 | LSB    |

| Differential Non-Linearity, DNL            | f <sub>C</sub> = 20 MSPS, V <sub>IN</sub> = 0.6V to 2.6V    | -   | ±0.3 | ±0.5 | LSB    |

| DYNAMIC CHARACTERISTICS                    |                                                             | 1   |      |      |        |

| Effective Number of Bits, ENOB             | f <sub>IN</sub> = 1MHz                                      | -   | 7.6  | -    | Bits   |

| Spurious Free Dynamic Range                | f <sub>IN</sub> = 1MHz                                      | -   | 51   | -    | dB     |

| Signal to Noise Ratio, SINAD<br>RMS Signal | f <sub>C</sub> = 20MHz, f <sub>IN</sub> = 1MHz              | -   | 46   | -    | dB     |

| RMS Noise + Distortion                     | $f_C = 20MHz$ , $f_{IN} = 3.58MHz$                          | -   | 46   | -    | dB     |

| Maximum Conversion Speed, f <sub>C</sub>   | V <sub>IN</sub> = 0.6V to 2.6V, f <sub>IN</sub> = 1kHz Ramp | 20  | 35   | -    | MSPS   |

| Minimum Conversion Speed                   |                                                             | -   | -    | 0.5  | MSPS   |

| Differential Gain Error, DG                | NTSC 40 IRE Mod Ramp, f <sub>C</sub> = 14.3 MSPS            | -   | 1.0  | -    | %      |

| Differential Phase Error, DP               |                                                             | -   | 0.5  | -    | Degree |

| Aperture Jitter, t <sub>AJ</sub>           |                                                             | -   | 30   | -    | ps     |

| Sampling Delay, t <sub>DS</sub>            |                                                             | -   | 4    | -    | ns     |

| Data Latency, t <sub>LAT</sub>             |                                                             | -   | -    | 2.5  | Cycles |

| ANALOG INPUTS                              |                                                             |     |      | •    | •      |

| Analog Input Bandwidth (-1dB), BW          |                                                             | -   | 18   | -    | MHz    |

| Analog Input Capacitance, C <sub>IN</sub>  | $V_{IN} = 1.5V + 0.07V_{RMS}$                               | -   | 11   | -    | pF     |

$\textbf{Electrical Specifications} \quad \text{$f_C = 20$ MSPS, $V_{DD} = +5V$, $V_{RB} = 0.5V$, $V_{RT} = 2.5V$, $T_A = 25^{\circ}C$ (Note 1) } \label{eq:fc} \textbf{(Continued)}$

| PARAMETER                                                | TEST CON                                                          | DITIONS                                 | MIN  | TYP  | MAX  | UNIT |

|----------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------|------|------|------|------|

| REFERENCE INPUT                                          |                                                                   |                                         |      |      | И.   |      |

| Reference Pin Current, I <sub>REF</sub>                  |                                                                   |                                         | 4.5  | 6.6  | 8.7  | mA   |

| Reference Resistance ( $V_{RT}$ to $V_{RB}$ ), $R_{REF}$ |                                                                   |                                         | 230  | 300  | 450  | Ω    |

| INTERNAL VOLTAGE REFERENCE                               |                                                                   |                                         |      |      |      |      |

| Self Bias Mode 1                                         |                                                                   |                                         | -    | -    | -    | -    |

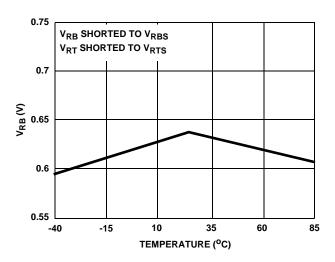

| $V_{RB}$                                                 | Short V <sub>RB</sub> and V <sub>RBS</sub> , Short V <sub>F</sub> | RT and V <sub>RTS</sub>                 | 0.60 | 0.64 | 0.68 | V    |

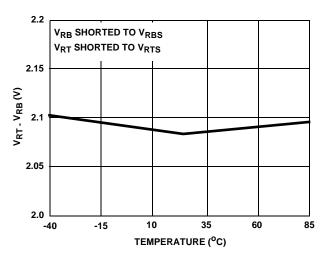

| V <sub>RT</sub> - V <sub>RB</sub>                        |                                                                   |                                         | 1.96 | 2.09 | 2.21 | V    |

| Self Bias Mode 2, V <sub>RT</sub>                        | $V_{RB}$ = AGND, Short $V_{RT}$ and $V_{RT}$                      | / <sub>RTS</sub>                        | 2.25 | 2.39 | 2.53 | V    |

| DIGITAL INPUTS                                           | 1                                                                 |                                         | 1    | 1    | 1    | ı    |

| Digital Input Voltage                                    |                                                                   |                                         | -    | -    | -    | -    |

| V <sub>IH</sub>                                          |                                                                   |                                         | 4.0  | -    | -    | V    |

| V <sub>IL</sub>                                          |                                                                   |                                         | -    | -    | 1.0  | V    |

| Digital Input Current                                    |                                                                   |                                         | -    | -    | -    | -    |

| I <sub>IH</sub>                                          | V <sub>DD</sub> = Max                                             | $V_{IH} = V_{DD}$                       | -    | -    | 5    | μΑ   |

| I <sub>IL</sub>                                          |                                                                   | V <sub>IL</sub> = 0V                    | -    | -    | 5    | μА   |

| DIGITAL OUTPUTS                                          | -                                                                 | ,                                       | 1    | 1    | 1    |      |

| Digital Output Current                                   |                                                                   |                                         | -    | -    | -    | -    |

| I <sub>OH</sub>                                          | $\overline{OE} = V_{SS}, V_{DD} = Min$                            | V <sub>OH</sub> = V <sub>DD</sub> -0.5V | -1.1 | -    | -    | mA   |

| I <sub>OL</sub>                                          |                                                                   | V <sub>OL</sub> = 0.4V                  | 3.7  | -    | -    | mA   |

| Digital Output Current                                   |                                                                   |                                         | -    | -    | -    | -    |

| I <sub>OZH</sub>                                         | $\overline{OE} = V_{DD}, V_{DD} = Max$                            | $V_{OH} = V_{DD}$                       | -    | 0.01 | 16   | μΑ   |

| I <sub>OZL</sub>                                         |                                                                   | V <sub>OL</sub> = 0V                    | -    | 0.01 | 16   | μА   |

| TIMING CHARACTERISTICS                                   | 1                                                                 | -                                       | 1    | 1    | 1    | 1    |

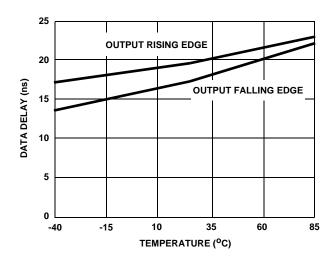

| Output Data Delay, t <sub>DL</sub>                       |                                                                   |                                         | -    | 18   | 30   | ns   |

| POWER SUPPLY CHARACTERISTIC                              | ;                                                                 |                                         | 1    |      | 1    | 1    |

| Supply Current, I <sub>DD</sub>                          | f <sub>C</sub> = 20 MSPS, NTSC Ramp W                             | /ave Input                              | -    | 12   | 17   | mA   |

| JOTE:                                                    | I                                                                 |                                         | 1    | 1    | 1    | l    |

#### NOTE:

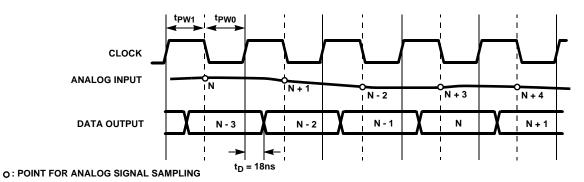

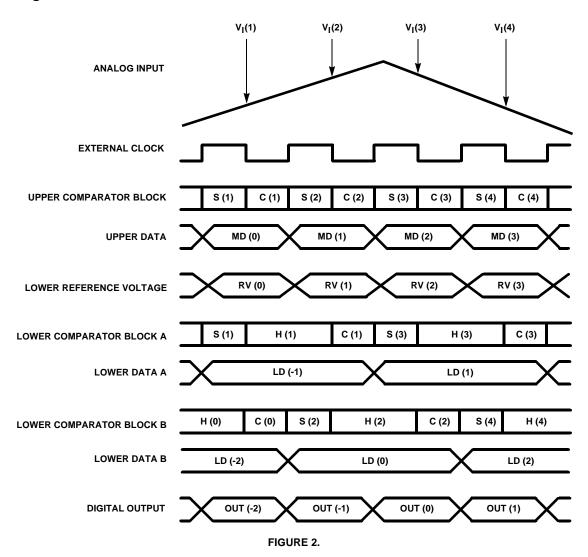

# **Timing Diagrams**

FIGURE 1.

<sup>2.</sup> Electrical specifications guaranteed only under the stated operating conditions.

## Timing Diagrams (Continued)

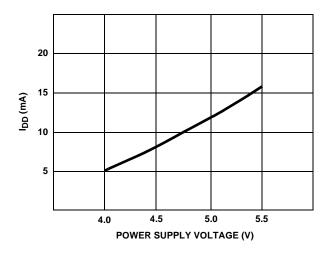

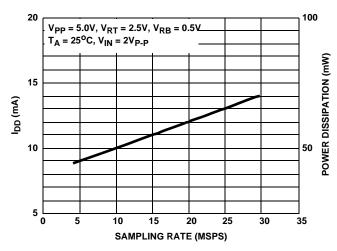

# **Typical Performance Curves**

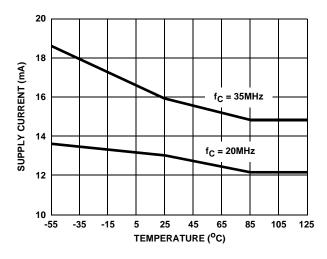

FIGURE 3. SUPPLY CURRENT vs SUPPLY VOLTAGE

FIGURE 4. SUPPLY CURRENT AND POWER vs SAMPLING RATE

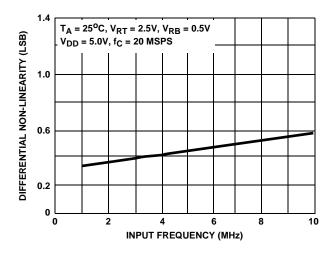

# Typical Performance Curves (Continued)

FIGURE 5. DIFFERENTIAL NON-LINEARITY VS INPUT FREQUENCY

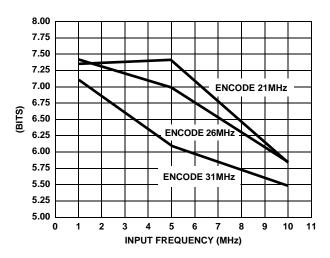

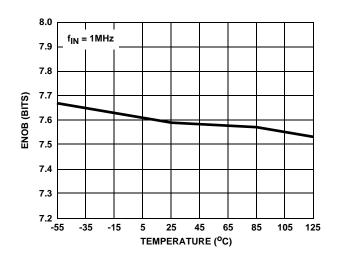

FIGURE 7. HI1175JCP ENOB vs INPUT FREQUENCY

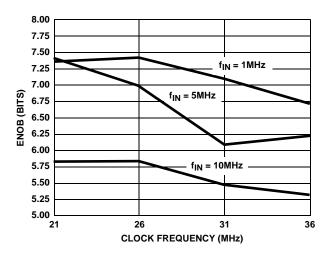

FIGURE 9. ENOB vs CLOCK FREQUENCY

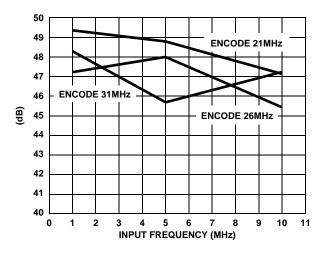

FIGURE 6. HI1175JCP SNR vs INPUT FREQUENCY

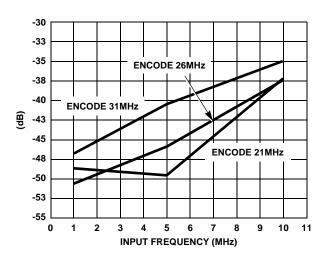

FIGURE 8. HI1175JCP THD vs INPUT FREQUENCY

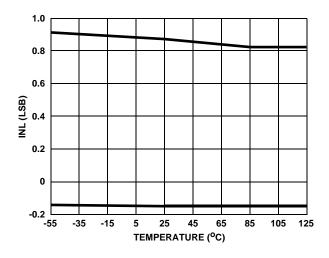

FIGURE 10. INL vs TEMPERATURE

# Typical Performance Curves (Continued)

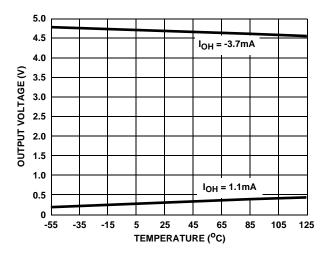

FIGURE 11. DIGITAL OUTPUT VOLTAGE vs TEMPERATURE

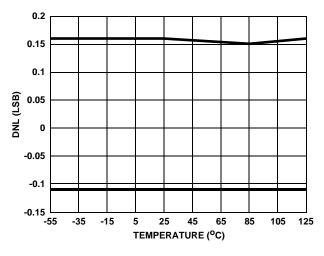

FIGURE 13. DNL vs TEMPERATURE

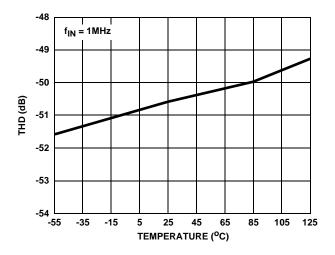

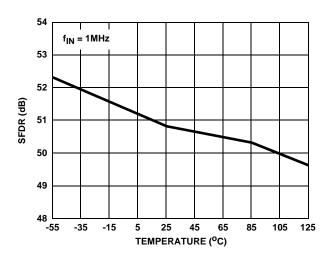

FIGURE 15. THD vs TEMPERATURE

FIGURE 12. SUPPLY CURRENT vs TEMPERATURE

FIGURE 14. SFDR vs TEMPERATURE

FIGURE 16. ENOB vs TEMPERATURE

# Typical Performance Curves (Continued)

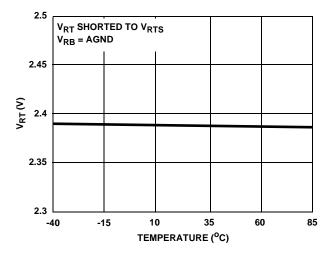

FIGURE 17. V<sub>RT</sub> vs TEMPERATURE

FIGURE 18.  $V_{RT}$  -  $V_{RB}$  vs TEMPERATURE

FIGURE 19. V<sub>RB</sub> vs TEMPERATURE

FIGURE 20. OUTPUT DATA DELAY vs TEMPERATURE

#### A/D OUTPUT CODE TABLE

| INPUT SIGNAL    |      |     |    |    | DIGITAL OU | TPUT CODE |    |    |     |

|-----------------|------|-----|----|----|------------|-----------|----|----|-----|

| VOLTAGE         | STEP | MSB | D6 | D5 | D4         | D3        | D2 | D1 | LSB |

| V <sub>RT</sub> | 255  | 1   | 1  | 1  | 1          | 1         | 1  | 1  | 1   |

| •               | •    |     |    |    |            | •         |    |    |     |

| •               | •    |     |    |    |            | •         |    |    |     |

| •               | •    |     |    |    |            | •         |    |    |     |

| •               | 128  | 1   | 0  | 0  | 0          | 0         | 0  | 0  | 0   |

| •               | 127  | 0   | 1  | 1  | 1          | 1         | 1  | 1  | 1   |

| •               |      |     |    |    |            |           |    |    |     |

| •               | •    |     |    |    |            | •         |    |    |     |

|                 | •    |     |    |    |            | •         |    |    |     |

|                 | •    |     |    |    |            | •         |    |    |     |

| $V_{RB}$        | 0    | 0   | 0  | 0  | 0          | 0         | 0  | 0  | 0   |

## **Detailed Description**

The HI1175 is a 2-step A/D converter featuring a 4-bit upper comparator group and two lower comparator groups of 4 bits each. The reference voltage can be obtained from the onboard bias generator or be supplied externally. This IC uses an offset canceling type comparator that operates synchronously with an external clock. The operating modes of the part are input sampling (S), hold (H), and compare (C).

The operation of the part is illustrated in Figure 2. A reference voltage that is between V<sub>RT</sub>-V<sub>RB</sub> is constantly applied to the upper 4-bit comparator group. V<sub>I</sub>(1) is sampled with the falling edge of the first clock by the upper comparator block. The lower block A also samples  $V_I(1)$  on the same edge. The upper comparator block finalizes comparison data MD(1) with the rising edge of the first clock. Simultaneously the reference supply generates a reference voltage RV(1) that corresponds to the upper results and applies it to the lower comparator block A. The lower comparator block finalizes comparison data LD(1) with the rising edge of the second clock. MD(1) and LD(1) are combined and output as OUT(1) with the rising edge of the third clock. There is a 2.5 cycle clock delay from the analog input sampling point to the corresponding digital output data. Notice how the lower comparator blocks A and B alternate generating the lower data in order to increase the overall A/D sampling rate.

#### Power, Grounding, and Decoupling

To reduce noise effects, separate the analog and digital arounds.

In order to avoid latchup at power up, it is necessary that  $AV_{DD}$  and  $DV_{DD}$  be driven from the same supply.

Bypass both the digital and analog  $V_{DD}$  pins to their respective grounds with a ceramic  $0.1\mu F$  capacitor close to the pin.

#### Analog Input

The input capacitance is small when compared with other flash type A/D converters. However, it is necessary to drive the input with an amplifier with sufficient bandwidth and drive capability. In order to prevent parasitic oscillation, it may be necessary to insert a low value (i.e.,  $0.24\Omega$ ) resistor between the output of the amplifier and the A/D input.

#### Reference Input

The range of the A/D is set by the voltage between V $_{RT}$  and V $_{RB}$ . The internal bias generator will set V $_{RTS}$  to 2.6V and V $_{RBS}$  to 0.6V. These can be used as the part reference by shorting V $_{RTS}$  and V $_{RTS}$  and V $_{RBS}$ . The analog input range of the A/D will now be from 0.6V to 2.6V and is referred to as Self Bias Mode 1. Self Bias Mode 2 is where V $_{RB}$  is connected to AGND and V $_{RTS}$  is shorted to V $_{RTS}$ . The analog input range will now be from 0V to 2.4V.

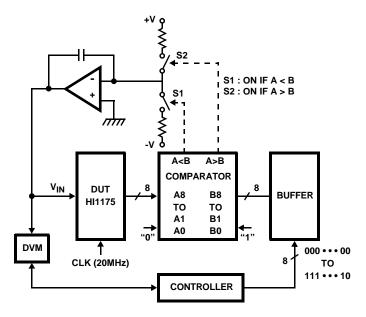

#### **Test Circuits**

FIGURE 21. INTEGRAL AND DIFFERENTIAL NON-LINEARITY ERROR AND OFFSET VOLTAGE TEST CIRCUIT

## Test Circuits (Continued)

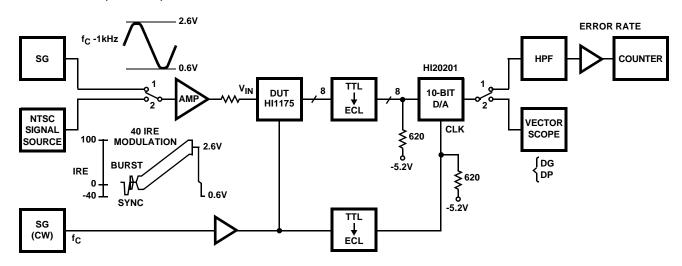

FIGURE 22. MAXIMUM OPERATIONAL SPEED AND DIFFERENTIAL GAIN AND PHASE ERROR TEST CIRCUIT

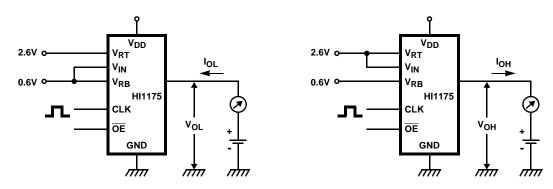

FIGURE 23. DIGITAL OUTPUT CURRENT TEST CIRCUIT

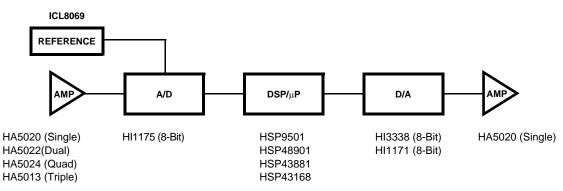

HSP9501: Programmable Data Buffer HSP48901: 3 x 3 Image Filter, 30MHz, 8-Bit

HSP43881: Digital Filter, 30MHz, 1-D and 2-D FIR Filters HSP43168: Dual FIR Filter, 10-Bit, 33MHz/45MHz

CMOS Logic Available in HC, HCT, AC, ACT and FCT.

HA5013: Triple, 125MHz,  $I_{OUT} = 20mA$

HA5020: Single, 100MHz,  $I_{OUT}$  = 30mA, Output Enable/Disable HA5022: Dual, 125MHz,  $I_{OUT}$  = 20mA, Output Enable/Disable HA5024: Quad, 125MHz,  $I_{OUT}$  = 20mA, Output Enable/Disable

FIGURE 24. 8-BIT SYSTEM COMPONENTS

#### Static Performance Definitions

Offset, full scale, and gain all use a measured value of the internal voltage reference to determine the ideal plus and minus full scale values. The results are all displayed in LSBs.

#### Offset Error (EOB)

The first code transition should occur at a level  $^{1}/_{2}$  LSB above the bottom reference voltage. Offset is defined as the deviation of the actual code transition from this point. Note that this is adjustable to zero.

## Full Scale Error (EOT)

The last code transition should occur for a analog input that is  $1^{1}/_{2}$  LSBs below full scale. Full scale error is defined as the deviation of the actual code transition from this point.

#### Differential Linearity Error (DNL)

DNL is the worst case deviation of a code width from the ideal value of 1 LSB. The converter is guaranteed to have no missing codes.

#### Integral Linearity Error (INL)

INL is the worst case deviation of a code center from a best fit straight line calculated from the measured data.

## **Dynamic Performance Definitions**

Fast Fourier Transform (FFT) techniques are used to evaluate the dynamic performance of the HI1175. A low distortion sine wave is applied to the input, it is sampled, and the output is stored in RAM. The data is then transformed into the frequency domain with a 1024 point FFT and analyzed to evaluate the dynamic performance of the A/D. The sine wave input to the part is -0.5dB down from fullscale for all these tests. The distortion numbers are quoted in dBc (decibels with respect to carrier) and **DO NOT** include any correction factors for normalizing to fullscale.

#### Signal-to-Noise Ratio (SNR)

SNR is the measured RMS signal to RMS noise at a specified input and sampling frequency. The noise is the RMS sum of all of the spectral components except the fundamental and the first five harmonics.

### Signal-to-Noise + Distortion Ratio (SINAD)

SINAD is the measured RMS signal to RMS sum of all other spectral components below the Nyquist frequency excluding DC.

#### Effective Number Of Bits (ENOB)

The effective number of bits (ENOB) is derived from the SINAD data. ENOB is calculated from:

$ENOB = (SINAD - 1.76 + V_{CORR}) / 6.02,$

where:  $V_{CORR} = 0.5dB$ .

#### **Total Harmonic Distortion**

This is the ratio of the RMS sum of the first 5 harmonic components to the RMS value of the measured input signal.

#### 2nd and 3rd Harmonic Distortion

This is the ratio of the RMS value of the 2nd and 3rd harmonic component respectively to the RMS value of the measured input signal.

#### Spurious Free Dynamic Range (SFDR)

SFDR is the ratio of the fundamental RMS amplitude to the RMS amplitude of the next largest spur or spectral component. If the harmonics are buried in the noise floor it is the largest peak.

#### Full Power Input Bandwidth

Full power bandwidth is the frequency at which the amplitude of the digitally reconstructed output has decreased 3dB below the amplitude of the input sine wave. The input sine wave has a peak-to-peak amplitude equal to the reference voltage. The bandwidth given is measured at the specified sampling frequency.

## **Timing Definitions**

### Sampling Delay (tSD)

Sampling delay is the time delay between the external sample command (the falling edge of the clock) and the time at which the signal is actually sampled. This delay is due to internal clock path propagation delays.

#### Aperture Jitter (t<sub>AJ</sub>)

This is the RMS variation in the sampling delay due to variation of internal clock path delays.

#### Data Latency (t<sub>LAT</sub>)

After the analog sample is taken, the data on the bus is available after 2.5 cycles of the clock. This is due to the architecture of the converter where the data has to ripple through the stages. This delay is specified as the data latency. After the data latency time, the data representing each succeeding sample is output at the following clock pulse. The digital data lags the analog input by 2.5 cycles.

#### Output Data Delay (t<sub>D</sub>)

Output Data Delay is the delay time from when the data is valid (rising clock edge) to when it shows up at the output bus. This is due to internal delays at the digital output.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com