1.本站收集的数据手册和产品资料都来自互联网,版权归原作者所有。如读者和版权方有任 何异议请及时告之,我们将妥善解决。

本站提供的中文数据手册是英文数据手册的中文翻译,其目的是协助用户阅读,该译文无法自动跟随原稿更新,同时也可能存在翻译上的不当。建议读者以英文原稿为参考以便获得更精准的信息。

3.本站提供的产品资料,来自厂商的技术支持或者使用者的心得体会等,其内容可能存在描 叙上的差异,建议读者做出适当判断。

4.如需与我们联系,请发邮件到marketing@iczoom.com,主题请标有"数据手册"字样。

# **Read Statement**

1. The datasheets and other product information on the site are all from network reference or other public materials, and the copyright belongs to the original author and original published source. If readers and copyright owners have any objections, please contact us and we will deal with it in a timely manner.

2. The Chinese datasheets provided on the website is a Chinese translation of the English datasheets. Its purpose is for reader's learning exchange only and do not involve commercial purposes. The translation cannot be automatically updated with the original manuscript, and there may also be improper translations. Readers are advised to use the English manuscript as a reference for more accurate information.

3. All product information provided on the website refer to solutions from manufacturers' technical support or users the contents may have differences in description, and readers are advised to take the original article as the standard.

4. If you have any questions, please contact us at marketing@iczoom.com and mark the subject with "Datasheets".

Data Sheet

#### June 27, 2006

## 24-Bit, High Precision, Sigma Delta A/D Converter

intersil

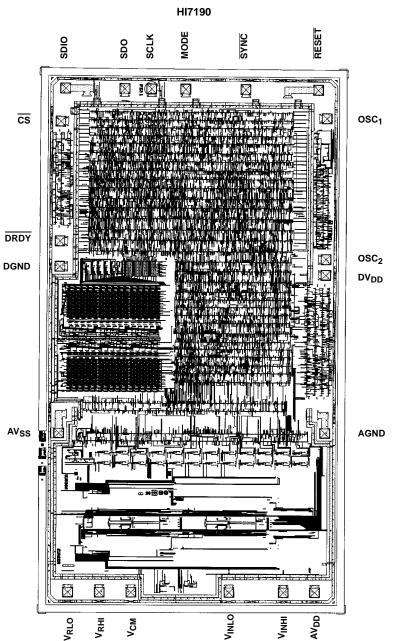

The Intersil HI7190 is a monolithic instrumentation, sigma delta A/D converter which operates from ±5V supplies. Both the signal and reference inputs are fully differential for maximum flexibility and performance. An internal Programmable Gain Instrumentation Amplifier (PGIA) provides input gains from 1 to 128 eliminating the need for external pre-amplifiers. The on-demand converter autocalibrate function is capable of removing offset and gain errors existing in external and internal circuitry. The on-board user programmable digital filter provides over 120dB of 60/50Hz noise rejection and allows fine tuning of resolution and conversion speed over a wide dynamic range. The HI7190 and HI7191 are functionally the same device, but the HI7190 has tighter linearity specifications.

The HI7190 contains a serial I/O port and is compatible with most synchronous transfer formats including both the Motorola 6805/11 series SPI and Intel 8051 series SSR protocols. A sophisticated set of commands gives the user control over calibration, PGIA gain, device selection, standby mode, and several other features. The On-chip Calibration Registers allow the user to read and write calibration data.

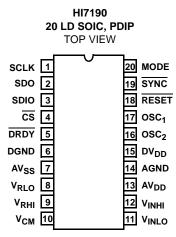

#### Pinout

#### Features

- 22-Bit Resolution with No Missing Code

- 0.0007% Integral Non-Linearity (Typ)

- 20mV to ±2.5V Full Scale Input Ranges

- Internal PGIA with Gains of 1 to 128

- Serial Data I/O Interface, SPI Compatible

- Differential Analog and Reference Inputs

- Internal or System Calibration

- 120dB Rejection of 60/50Hz Line Noise

- Settling Time of 4 Conversions (Max) for a Step Input

- Pb-Free Plus Anneal Available (RoHS Compliant)

#### Applications

- Process Control and Measurement

- Industrial Weight Scales

- Part Counting Scales

- Laboratory Instrumentation

- Seismic Monitoring

- Magnetic Field Monitoring

- Additional Reference Literature

- Technical Brief, TB348 "HI7190/1 Negative Full Scale Error vs Conversion Frequency"

- Application Note, AN9504 "A Brief Intro to Sigma Delta Conversion"

- Technical Brief, TB329 "Intersil Sigma Delta Calibration Technique"

- Application Note, AN9505 "Using the HI7190 Evaluation Kit"

- Technical Brief, TB331 "Using the HI7190 Serial Interface"

- Application Note, AN9527 "Interfacing HI7190 to a Microcontroller"

- Application Note, AN9532 "Using HI7190 in a Multiplexed System"

- Application Note, AN9601 "Using HI7190 with a Single +5V Supply"

#### **Ordering Information**

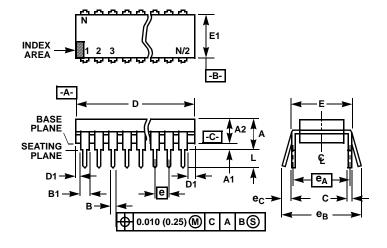

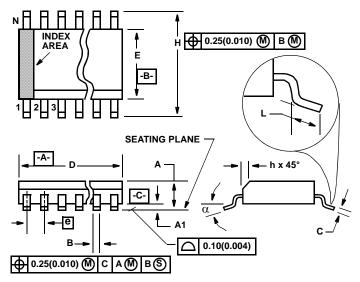

| PART<br>NUMBER        | PART<br>MARKING | TEMP.<br>RANGE<br>(°C) | PACKAGE                                  | PKG.<br>DWG. # |

|-----------------------|-----------------|------------------------|------------------------------------------|----------------|

| HI7190IP              | HI7190IP        | -40 to 85              | 20 Ld PDIP                               | E20.3          |

| HI7190IPZ             | HI7190IPZ       | -40 to 85              | 20 Ld PDIP*<br>(Pb-free)                 | E20.3          |

| HI7190IB              | HI7190IB        | -40 to 85              | 20 Ld SOIC                               | M20.3          |

| HI7190IBZ<br>(Note)   | HI7190IBZ       | -40 to 85              | 20 Ld SOIC<br>(Pb-free)                  | M20.3          |

| HI7190IBZ-T<br>(Note) | HI7190IBZ       | -40 to 85              | 20 Ld SOIC<br>Tape and Reel<br>(Pb-free) | M20.3          |

| HI7190EVAL            | Evaluation Kit  |                        |                                          |                |

\*Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

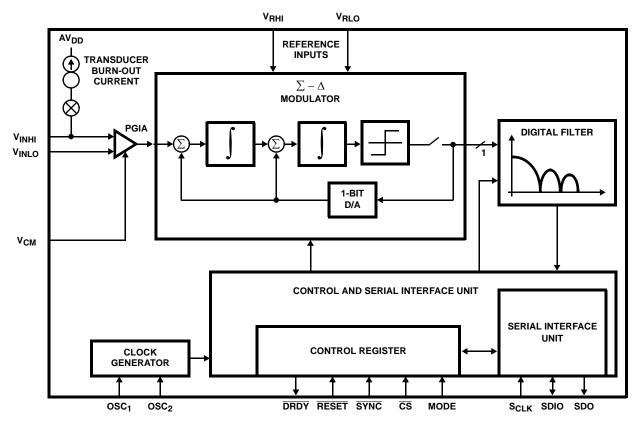

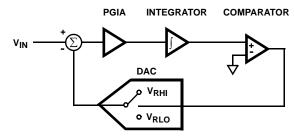

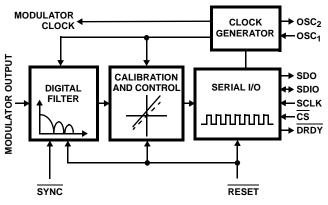

#### Functional Block Diagram

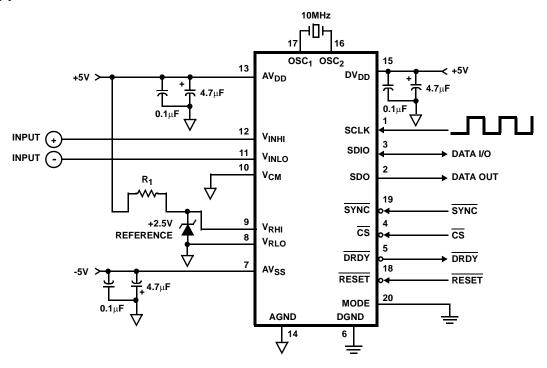

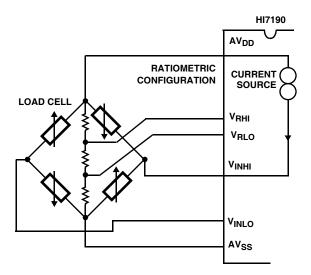

Typical Application Schematic

#### Absolute Maximum Ratings

| Supply Voltage                                              |

|-------------------------------------------------------------|

| AV <sub>DD</sub> to AGND+5.5V                               |

| AV <sub>SS</sub> to AGND5.5V                                |

| DV <sub>DD</sub> to DGND+5.5V                               |

| DGND to AGND                                                |

| Analog Input Pins AV <sub>SS</sub> to AV <sub>DD</sub>      |

| Digital Input, Output and I/O Pins DGND to DV <sub>DD</sub> |

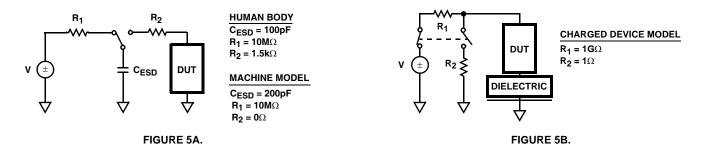

| ESD Tolerance (No Damage)                                   |

| Human Body Model                                            |

| Machine Model100V                                           |

| Charged Device Model                                        |

#### **Operating Conditions**

Temperature Range ......-40° C to 85°C

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

## **Electrical Specifications** $AV_{DD} = +5V, AV_{SS} = -5V, DV_{DD} = +5V, V_{RHI} = +2.5V, V_{RLO} = AGND = 0V, V_{CM} = AGND, PGIA Gain = 1, OSC_{IN} = 10MHz, Bipolar Input Range Selected, f<sub>N</sub> = 10Hz$

| PARAMETER                                                                                              | TEST CONDITIONS MIN                                               |                             | TYP        | MAX                         | UNITS       |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------|------------|-----------------------------|-------------|

| SYSTEM PERFORMANCE                                                                                     |                                                                   | I                           | 1          |                             | 1           |

| Integral Non-Linearity, INL                                                                            | End Point Line Method (Notes 3, 5, 6)                             | -                           | ±0.0007    | ±0.0015                     | %FS         |

| Differential Non-Linearity                                                                             | (Note 2)                                                          | No Missi                    | ng codes t | o 22-Bits                   | LSB         |

| Offset Error, V <sub>OS</sub>                                                                          | See Table 1                                                       | -                           | -          | -                           | -           |

| Offset Error Drift                                                                                     | V <sub>INHI</sub> = V <sub>INLO</sub> (Notes 3, 8)                | -                           | 1          | -                           | μV/°C       |

| Full Scale Error, FSE                                                                                  | V <sub>INHI</sub> - V <sub>INLO</sub> = +2.5V (Notes 3, 5, 8, 10) | -                           | -          | -                           | -           |

| Noise, e <sub>N</sub>                                                                                  | See Table 1                                                       | -                           | -          | -                           | -           |

| Common Mode Rejection Ratio, CMRR                                                                      | $V_{CM} = 0V, V_{INHI} = V_{INLO}$ from -2V to +2V                | -                           | 70         | _                           | dB          |

| Normal Mode 50Hz Rejection                                                                             | Filter Notch = 10Hz, 25Hz, 50Hz (Note 2)                          | 120                         | -          | -                           | dB          |

| Normal Mode 60Hz Rejection                                                                             | Filter Notch = 10Hz, 30Hz, 60Hz (Note 2)                          | 120                         | -          | -                           | dB          |

| Step Response Settling Time                                                                            |                                                                   | -                           | 2          | 4                           | Conversions |

| ANALOG INPUTS                                                                                          |                                                                   | l                           | 1          |                             | 1           |

| Input Voltage Range                                                                                    | Unipolar Mode (Note 9)                                            | 0                           | -          | V <sub>REF</sub>            | V           |

| Input Voltage Range                                                                                    | Bipolar Mode (Note 9)                                             | - V <sub>REF</sub>          | -          | V <sub>REF</sub>            | V           |

| Common Mode Input Range                                                                                | (Note 2)                                                          | AV <sub>SS</sub>            | -          | AV <sub>DD</sub>            | V           |

| Input Leakage Current, IIN                                                                             | V <sub>IN</sub> = AV <sub>DD</sub> (Note 2)                       | -                           | -          | 1.0                         | nA          |

| Input Capacitance, CIN                                                                                 |                                                                   | -                           | 5.0        | -                           | pF          |

| Reference Voltage Range, V <sub>REF</sub><br>(V <sub>REF</sub> = V <sub>RHI</sub> - V <sub>RLO</sub> ) |                                                                   | 2.5                         | -          | 5                           | V           |

| Transducer Burn-Out Current, IBO                                                                       |                                                                   | -                           | 200        | -                           | nA          |

| CALIBRATION LIMITS                                                                                     |                                                                   | 1                           |            |                             |             |

| Positive Full Scale Calibration Limit                                                                  |                                                                   | -                           | -          | 1.2(V <sub>REF</sub> /Gain) | -           |

| Negative Full Scale Calibration Limit                                                                  |                                                                   | -                           | -          | 1.2(V <sub>REF</sub> /Gain) | -           |

| Offset Calibration Limit                                                                               |                                                                   |                             | -          | 1.2(V <sub>REF</sub> /Gain) | -           |

| Input Span                                                                                             |                                                                   | 0.2(V <sub>REF</sub> /Gain) | -          | 2.4(V <sub>REF</sub> /Gain) | -           |

| DIGITAL INPUTS                                                                                         |                                                                   |                             |            |                             |             |

| Input Logic High Voltage, V <sub>IH</sub>                                                              | (Note 11)                                                         | 2.0                         | -          | -                           | V           |

| Input Logic Low Voltage, VIL                                                                           |                                                                   | -                           | -          | 0.8                         | V           |

| Input Logic Current, II                                                                                | V <sub>IN</sub> = 0V, +5V                                         | -                           | 1.0        | 10                          | μΑ          |

| Thermal Resistance (Typical, Note 1)                                 | $\theta_{JA}$ (°C/W) |

|----------------------------------------------------------------------|----------------------|

| PDIP Package                                                         | 125                  |

| SOIC Package                                                         | 75                   |

| Maximum Junction Temperature                                         |                      |

| Plastic Packages                                                     | 150°C                |

| Maximum Storage Temperature Range65                                  | 5°C to 150°C         |

| Maximum Lead Temperature (Soldering, 10s)<br>(SOIC - Lead Tips Only) | 300°C                |

### **Electrical Specifications** $AV_{DD} = +5V, AV_{SS} = -5V, DV_{DD} = +5V, V_{RHI} = +2.5V, V_{RLO} = AGND = 0V, V_{CM} = AGND, PGIA Gain = 1, OSC<sub>IN</sub> = 10MHz, Bipolar Input Range Selected, f<sub>N</sub> = 10Hz (Continued)$

| PARAMETER                                                       | TEST CONDITIONS                     | MIN | TYP | MAX  | UNITS |  |

|-----------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|--|

| Input Capacitance, C <sub>IN</sub>                              | $V_{IN} = 0V$                       | -   |     | -    | pF    |  |

| DIGITAL OUTPUTS                                                 |                                     |     |     |      |       |  |

| Output Logic High Voltage, V <sub>OH</sub>                      | I <sub>OUT</sub> = -100μA (Note 7)  | 2.4 | -   | -    | V     |  |

| Output Logic Low Voltage, V <sub>OL</sub>                       | I <sub>OUT</sub> = 3mA (Note 7)     | -   | -   | 0.4  | V     |  |

| Output Three-State Leakage Current,<br>I <sub>OZ</sub>          | V <sub>OUT</sub> = 0V, +5V (Note 7) | -10 | 1   | 10   | μΑ    |  |

| Digital Output Capacitance, C <sub>OUT</sub>                    |                                     | -   | 10  | -    | pF    |  |

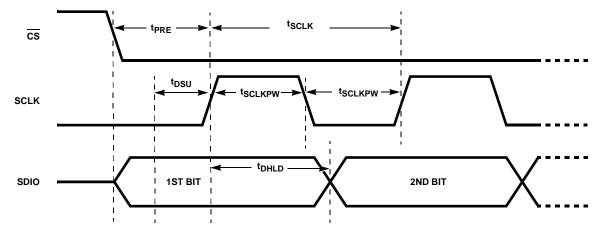

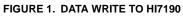

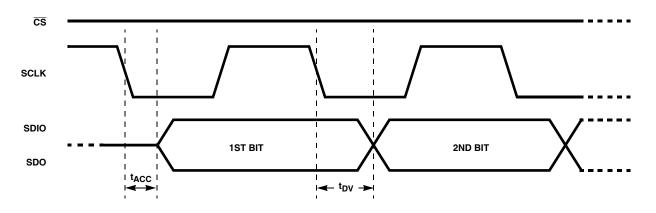

| TIMING CHARACTERISTICS                                          |                                     | L   |     |      |       |  |

| SCLK Minimum Cycle Time, t <sub>SCLK</sub>                      |                                     | 200 | -   | -    | ns    |  |

| SCLK Minimum Pulse Width, t <sub>SCLKPW</sub>                   |                                     | 50  | -   | -    | ns    |  |

| CS to SCLK Precharge Time, tPRE                                 |                                     | 50  | -   | -    | ns    |  |

| DRDY Minimum High Pulse Width                                   | (Notes 2, 7)                        | 500 | -   | -    | ns    |  |

| Data Setup to SCLK Rising Edge (Write),<br><sup>t</sup> DSU     |                                     | 50  | -   | -    | ns    |  |

| Data Hold from SCLK Rising Edge<br>(Write), t <sub>DHLD</sub>   |                                     | 0   | -   | -    | ns    |  |

| Data Read Access from Instruction Byte Write, $t_{ACC}$         | (Note 7)                            | -   | -   | 40   | ns    |  |

| Read Bit Valid from SCLK Falling Edge,<br><sup>t</sup> DV       | (Note 7)                            | -   | -   | 40   | ns    |  |

| Last Data Transfer to Data Ready<br>Inactive, t <sub>DRDY</sub> | (Note 7)                            | -   | 35  | -    | ns    |  |

| RESET Low Pulse Width                                           | (Note 2)                            | 100 | -   | -    | ns    |  |

| SYNC Low Pulse Width                                            | (Note 2)                            | 100 | -   | -    | ns    |  |

| Oscillator Clock Frequency                                      | (Note 2)                            | 0.1 | -   | 10   | MHz   |  |

| Output Rise/Fall Time                                           | (Note 2)                            | -   | -   | 30   | ns    |  |

| Input Rise/Fall Time                                            | (Note 2)                            | -   | -   | 1    | μS    |  |

| POWER SUPPLY CHARACTERISTICS                                    |                                     |     | I   |      |       |  |

| IAV <sub>DD</sub>                                               |                                     | -   | -   | 1.5  | mA    |  |

| AV <sub>SS</sub>                                                |                                     | -   | -   | 2.0  | mA    |  |

| IDV <sub>DD</sub>                                               | SCLK = 4MHz                         | -   | -   | 3.0  | mA    |  |

| Power Dissipation, Active PDA                                   | SB = '0'                            | -   | 15  | 32.5 | mW    |  |

| Power Dissipation, Standby PD <sub>S</sub>                      | SB = '1'                            | -   | 5   | -    | mW    |  |

| PSRR                                                            | (Note 3)                            | -   | -70 | -    | dB    |  |

NOTES:

2. Parameter guaranteed by design or characterization, not production tested.

3. Applies to both bipolar and unipolar input ranges.

4. These errors can be removed by re-calibrating at the desired operating temperature.

- 5. Applies after system calibration.

- 6. Fully differential input signal source is used.

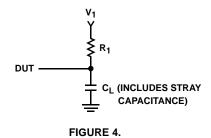

- 7. See Load Test Circuit, Figure 4, R1 = 10k $\Omega$ , C<sub>L</sub> = 50pF.

- 8. 1 LSB = 298nV at 24 bits for a Full Scale Range of 5V.

- 9.  $V_{REF} = V_{RHI} V_{RLO}$ .

10. These errors are on the order of the output noise shown in Table 1.

11. All inputs except OSC<sub>1</sub>. The OSC<sub>1</sub> input  $V_{IH}$  is 3.5V minimum.

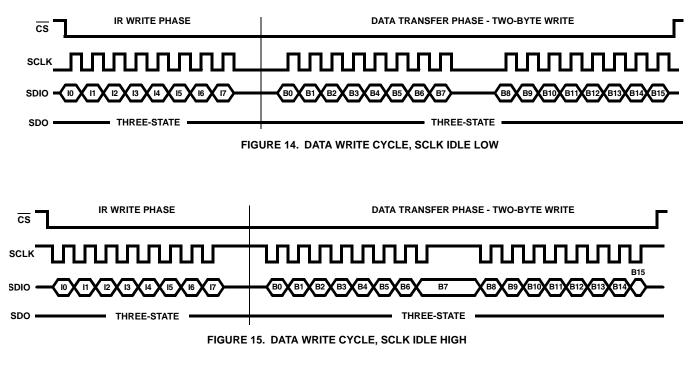

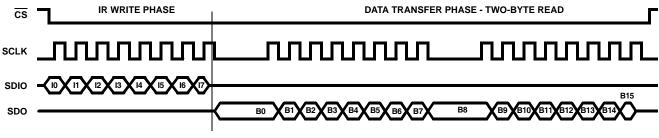

#### **Timing Diagrams**

FIGURE 3. DATA READ FROM HI7190

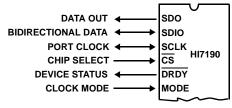

#### **Pin Descriptions**

| 20 LEAD<br>DIP, SOIC | PIN NAME          | DESCRIPTION                                                                                                                                                                                                                              |

|----------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | SCLK              | Serial Interface Clock. Synchronizes serial data transfers. Data is input on the rising edge and output on the falling edge.                                                                                                             |

| 2                    | SDO               | Serial Data OUT. Serial data is read from this line when using a 3-wire serial protocol such as the Motorola Serial Peripheral Interface.                                                                                                |

| 3                    | SDIO              | Serial Data IN or OUT. This line is bidirectional programmable and interfaces directly to the Intel Standard Serial Interface using a 2-wire serial protocol.                                                                            |

| 4                    | CS                | Chip Select Input. Used to select the HI7190 for a serial data transfer cycle. This line can be tied to DGND.                                                                                                                            |

| 5                    | DRDY              | An Active Low Interrupt indicating that a new data word is available for reading.                                                                                                                                                        |

| 6                    | DGND              | Digital Supply Ground.                                                                                                                                                                                                                   |

| 7                    | AV <sub>SS</sub>  | Negative Analog Power Supply (-5V).                                                                                                                                                                                                      |

| 8                    | V <sub>RLO</sub>  | External Reference Input. Should be negative referenced to V <sub>RHI</sub> .                                                                                                                                                            |

| 9                    | V <sub>RHI</sub>  | External Reference Input. Should be positive referenced to V <sub>RLO</sub> .                                                                                                                                                            |

| 10                   | V <sub>CM</sub>   | Common Mode Input. Should be set to halfway between AV <sub>DD</sub> and AV <sub>SS</sub> .                                                                                                                                              |

| 11                   | VINLO             | Analog Input LO. Negative input of the PGIA.                                                                                                                                                                                             |

| 12                   | V <sub>INHI</sub> | Analog Input HI. Positive input of the PGIA. The V <sub>INHI</sub> input is connected to a current source that can be used to check the condition of an external transducer. This current source is controlled via the Control Register. |

| 13                   | AV <sub>DD</sub>  | Positive Analog Power Supply (+5V).                                                                                                                                                                                                      |

| 14                   | AGND              | Analog Supply Ground.                                                                                                                                                                                                                    |

| 15                   | DV <sub>DD</sub>  | Positive Digital Supply (+5V).                                                                                                                                                                                                           |

| 16                   | OSC <sub>2</sub>  | Used to connect a crystal source between OSC <sub>1</sub> and OSC <sub>2</sub> . Leave open otherwise.                                                                                                                                   |

| 17                   | OSC <sub>1</sub>  | Oscillator Clock Input for the device. A crystal connected between $OSC_1$ and $OSC_2$ will provide a clock to the device, or an external oscillator can drive $OSC_1$ . The oscillator frequency should be 10MHz (Typ).                 |

| 18                   | RESET             | Active Low Reset Pin. Used to initialize the HI7190 registers, filter and state machines.                                                                                                                                                |

| 19                   | SYNC              | Active Low Sync Input. Used to control the synchronization of a number of HI7190s. A logic '0' initializes the converter.                                                                                                                |

| 20                   | MODE              | Mode Pin. Used to select between Synchronous Self Clocking (Mode = 1) or Synchronous External Clocking (Mode = 0) for the Serial Port.                                                                                                   |

#### Load Test Circuit

#### **ESD Test Circuits**

7

#### TABLE 1. NOISE PERFORMANCE WITH INPUTS CONNECTED TO ANALOG GROUND

| HERTZ    | SNR   | ENOB | P-P NOISE<br>(μV) | RMS NOISE<br>(µV) |

|----------|-------|------|-------------------|-------------------|

| GAIN = 1 |       |      |                   | L                 |

| 10       | 132.3 | 21.7 | 9.8               | 1.5               |

| 25       | 129.5 | 21.2 | 13.6              | 2.1               |

| 30       | 127.7 | 20.9 | 16.6              | 2.5               |

| 50       | 126.3 | 20.7 | 19.5              | 3.0               |

| 60       | 125.6 | 20.6 | 21.2              | 3.2               |

| 100      | 122.4 | 20.0 | 30.7              | 4.6               |

| 250      | 107.7 | 17.6 | 166.7             | 25.3              |

| 500      | 98.1  | 16.0 | 505.3             | 76.6              |

| 1000     | 85.7  | 13.9 | 2101.8            | 318.5             |

| 2000     | 68.8  | 11.1 | 14661.6           | 2221.4            |

| GAIN = 2 |       | 1    |                   |                   |

| 10       | 129.2 | 21.2 | 14.0              | 2.1               |

| 25       | 125.7 | 20.6 | 20.9              | 3.2               |

| 30       | 124.5 | 20.4 | 24.1              | 3.7               |

| 50       | 123.4 | 20.2 | 27.3              | 4.1               |

| 60       | 122.5 | 20.1 | 30.3              | 4.6               |

| 100      | 118.1 | 19.3 | 50.0              | 7.6               |

| 250      | 106.1 | 17.3 | 199.5             | 30.2              |

| 500      | 96.9  | 15.8 | 580.1             | 87.9              |

| 1000     | 84.4  | 13.7 | 2435.6            | 369.0             |

| 2000     | 67.8  | 11.0 | 16469.7           | 2495.4            |

| GAIN = 4 |       |      |                   |                   |

| 10       | 125.9 | 20.6 | 20.5              | 3.1               |

| 25       | 123.1 | 20.1 | 28.4              | 4.3               |

| 30       | 121.8 | 19.9 | 32.8              | 5.0               |

| 50       | 119.9 | 19.6 | 40.9              | 6.2               |

| 60       | 119.9 | 19.6 | 40.9              | 6.2               |

| 100      | 116.1 | 19.0 | 63.2              | 9.6               |

| 250      | 105.7 | 17.3 | 209.7             | 31.8              |

| 500      | 96.6  | 15.8 | 597.8             | 90.6              |

| 1000     | 84.3  | 13.7 | 2469.5            | 374.2             |

| 2000     | 68.2  | 11.0 | 15656.1           | 2372.1            |

| GAIN = 8 |       |      | 1                 |                   |

| 10       | 124.7 | 20.4 | 23.4              | 3.5               |

| 25       | 120.6 | 19.7 | 37.8              | 5.7               |

| 30       | 119.2 | 19.5 | 44.3              | 6.7               |

| 50       | 117.5 | 19.2 | 53.8              | 8.2               |

| 60       | 116.8 | 19.1 | 58.6              | 8.9               |

| 100      | 112.1 | 18.3 | 100.0             | 15.2              |

| 250      | 101.4 | 16.5 | 345.2             | 52.3              |

| 500      | 95.3  | 15.5 | 691.1             | 104.7             |

| 1000     | 83.1  | 13.5 | 2838.6            | 430.1             |

| 2000     | 68.3  | 11.1 | 15494.7           | 2347.7            |

| HERTZ      | SNR   | ENOB | <b>P-P NOISE</b><br>(μV) | RMS NOISE<br>(µV) |

|------------|-------|------|--------------------------|-------------------|

| GAIN = 16  |       | 1    |                          |                   |

| 10         | 120.1 | 19.7 | 39.8                     | 6.0               |

| 25         | 114.8 | 18.8 | 73.4                     | 11.1              |

| 30         | 113.5 | 18.6 | 85.1                     | 12.9              |

| 50         | 111.0 | 18.1 | 114.4                    | 17.3              |

| 60         | 109.6 | 17.9 | 134.0                    | 20.3              |

| 100        | 105.5 | 17.2 | 214.8                    | 32.5              |

| 250        | 95.2  | 15.5 | 699.1                    | 105.9             |

| 500        | 89.1  | 14.5 | 1417.7                   | 214.8             |

| 1000       | 83.5  | 13.6 | 2686.0                   | 407.0             |

| 2000       | 62.6  | 10.1 | 30110.0                  | 4562.1            |

| GAIN = 32  |       |      |                          |                   |

| 10         | 113.2 | 18.5 | 88.8                     | 13.5              |

| 25         | 109.0 | 17.8 | 142.7                    | 21.6              |

| 30         | 108.2 | 17.7 | 157.4                    | 23.8              |

| 50         | 104.7 | 17.1 | 235.8                    | 35.7              |

| 60         | 105.0 | 17.1 | 227.8                    | 34.5              |

| 100        | 102.3 | 16.7 | 310.5                    | 47.0              |

| 250        | 93.4  | 15.2 | 861.1                    | 130.5             |

| 500        | 87.1  | 14.2 | 1782.7                   | 270.1             |

| 1000       | 78.2  | 12.7 | 4990.4                   | 756.1             |

| 2000       | 57.0  | 9.2  | 57311.1                  | 8683.5            |

| GAIN = 64  |       |      |                          |                   |

| 10         | 106.7 | 17.4 | 186.2                    | 28.2              |

| 25         | 102.9 | 16.8 | 288.4                    | 43.7              |

| 30         | 101.9 | 16.6 | 325.8                    | 49.4              |

| 50         | 98.5  | 16.1 | 479.8                    | 72.7              |

| 60         | 98.9  | 16.1 | 459.8                    | 69.7              |

| 100        | 96.3  | 15.7 | 620.2                    | 94.0              |

| 250        | 85.5  | 13.9 | 2133.5                   | 323.3             |

| 500        | 78.1  | 12.7 | 5025.0                   | 761.4             |

| 1000       | 66.7  | 10.8 | 18693.5                  | 2832.3            |

| 2000       | 50.5  | 8.1  | 120163.0                 | 18206.5           |

| GAIN = 128 |       | 1    | 1                        | I                 |

| 10         | 101.1 | 16.5 | 356.5                    | 54.0              |

| 25         | 96.0  | 15.7 | 638.3                    | 96.7              |

| 30         | 95.2  | 15.5 | 704.8                    | 106.8             |

| 50         | 93.2  | 15.2 | 882.2                    | 133.7             |

| 60         | 92.2  | 15.0 | 996.7                    | 151.0             |

| 100        | 91.4  | 14.9 | 1086.6                   | 164.6             |

| 250        | 79.4  | 12.9 | 4346.4                   | 658.5             |

| 500        | 71.8  | 11.6 | 10439.2                  | 1581.7            |

| 1000       | 60.1  | 9.7  | 39923.0                  | 6048.9            |

| 2000       | 44.8  | 7.1  | 233238.2                 | 35339.1           |

#### Definitions

**Integral Non-Linearity, INL**, is the maximum deviation of any digital code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are zero scale (a point 0.5 LSB below the first code transition 000...000 and 000...001) and full scale (a point 0.5 LSB above the last code transition 111...110 to 111...111).

**Differential Non-Linearity, DNL,** is the deviation from the actual difference between midpoints and the ideal difference between midpoints (1 LSB) for adjacent codes. If this difference is equal to or more negative than 1 LSB, a code will be missed.

**Offset Error,** V<sub>OS</sub>, is the deviation of the first code transition from the ideal input voltage (V<sub>IN</sub> - 0.5 LSB). This error can be calibrated to the order of the noise level shown in Table 1.

**Full Scale Error, FSE,** is the deviation of the last code transition from the ideal input full scale voltage  $(V_{IN} + V_{REF}/Gain - 1.5 LSB)$ . This error can be calibrated to the order of the noise level shown in Table 1.

**Input Span**, defines the minimum and maximum input voltages the device can handle while still calibrating properly for gain.

**Noise,**  $e_N$ , Table 1 shows the peak-to-peak and RMS noise for typical notch and -3dB frequencies. The device programming was for bipolar input with a V<sub>REF</sub> of +2.5V. This implies the input range is 5V. The analysis was performed on 100 conversions with the peak-to-peak output noise being the difference between the maximum and minimum readings over a rolling 10 conversion window. The equation to convert the peak-to-peak noise data to ENOB is:

$ENOB = Log_2 (V_{FS}/V_{NRMS})$

where:  $V_{FS} = 5V$ ,  $V_{NRMS} = V_{NP-P}/CF$  and

CF = 6.6 (Empirical Crest Factor)

The noise from the part comes from two sources, the quantization noise from the analog-to-digital conversion process and device noise. Device noise (or Wideband Noise) is independent of gain and essentially flat across the frequency spectrum. Quantization noise is ratiometric to input full scale (and hence gain) and its frequency response is shaped by the modulator.

Looking at Table 1, as the cutoff frequency increases the output noise increases. This is due to more of the quantization noise of the part coming through to the output and, hence, the output noise increases with increasing -3dB frequencies. For the lower notch settings, the output noise is dominated by the device noise and, hence, altering the gain has little effect on the output noise. At higher notch frequencies, the quantization noise dominates the output noise and, in this case, the output noise tends to decrease with increasing gain.

Since the output noise comes from two sources, the effective resolution of the device (i.e., the ratio of the input full scale to the output RMS noise) does not remain constant with increasing gain or with increasing bandwidth. It is possible to do post-filtering (such as brick wall filtering) on the data to improve the overall resolution for a given -3dB frequency and also to further reduce the output noise.

#### **Circuit Description**

The HI7190 is a monolithic, sigma delta A/D converter which operates from ±5V supplies and is intended for measurement of wide dynamic range, low frequency signals. It contains a Programmable Gain Instrumentation Amplifier (PGIA), sigma delta ADC, digital filter, bidirectional serial port (compatible with many industry standard protocols), clock oscillator, and an on-chip controller.

The signal and reference inputs are fully differential for maximum flexibility and performance. Normally V<sub>RHI</sub> and V<sub>RLO</sub> are tied to +2.5V and AGND respectively. This allows for input ranges of 2.5V and 5V when operating in the unipolar and bipolar modes respectively (assuming the PGIA is configured for a gain of 1). The internal PGIA provides input gains from 1 to 128 and eliminates the need for external pre-amplifiers. This means the device will convert signals ranging from 0V to +20mV and 0V to +2.5V when operating in the unipolar mode or signals in the range of  $\pm$ 20mV to  $\pm$ 2.5V when operating in the bipolar mode.

The input signal is continuously sampled at the input to the HI7190 at a clock rate set by the oscillator frequency and the selected gain. This signal then passes through the sigma delta modulator (which includes the PGIA) and emerges as a pulse train whose code density contains the analog signal information. The output of the modulator is fed into the sinc<sup>3</sup> digital low pass filter. The filter output passes into the calibration block where offset and gain errors are removed. The calibrated data is then coded (2's complement, offset binary or binary) before being stored in the Data Output Register. The Data Output Register update rate is determined by the first notch frequency of the digital filter. This first notch frequency is programmed into HI7190 via the Control Register and has a range of 10Hz to 1.953kHz which corresponds to -3dB frequencies of 2.62Hz and 512Hz respectively.

Output data coding on the HI7190 is programmable via the Control Register. When operating in bipolar mode, data output can be either 2's complement or offset binary. In unipolar mode output is binary.

The DRDY signal is used to alert the user that new output data is available. Converted data is read via the HI7190 serial I/O port which is compatible with most synchronous transfer formats including both the Motorola 6805/11 series

SPI and Intel 8051 series SSR protocols. Data Integrity is always maintained at the HI7190 output port. This means that if a data read of conversion N is begun but not finished before the next conversion (conversion N + 1) is complete, the DRDY line remains active (low) and the data being read is not overwritten.

The HI7190 provides many calibration modes that can be initiated at any time by writing to the Control Register. The device can perform system calibration where external components are included with the HI7190 in the calibration loop or self-calibration where only the HI7190 itself is in the calibration loop. The On-chip Calibration Registers are read/write registers which allow the user to read calibration coefficients as well as write previously determined calibration coefficients.

#### **Circuit Operation**

The analog and digital supplies and grounds are separate on the HI7190 to minimize digital noise coupling into the analog circuitry. Nominal supply voltages are  $AV_{DD} = +5V$ ,  $DV_{DD} = +5V$ , and  $AV_{SS} = -5V$ . If the same supply is used for  $AV_{DD}$  and  $DV_{DD}$  it is imperative that the supply is separately decoupled to the  $AV_{DD}$  and  $DV_{DD}$  pins on the HI7190. Separate analog and digital ground planes should be maintained on the system board and the grounds should be tied together back at the power supply.

When the HI7190 is powered up it needs to be reset by pulling the RESET line low. The reset sets the internal registers of the HI7190 as shown in Table 2 and puts the part in the bipolar mode with a gain of 1 and offset binary coding. The filter notch of the digital filter is set at 30Hz while the I/O is set up for bidirectional I/O (data is read and written on the SDIO line and SDO is three-stated), descending byte order, and MSB first data format. A self calibration is performed before the device begins converting. DRDY goes low when valid data is available at the output.

| REGISTER                                 | VALUE (HEX)            |

|------------------------------------------|------------------------|

| Data Output Register                     | XXXX (Undefined)       |

| Control Register                         | 28B300                 |

| Offset Calibration Register              | Self Calibration Value |

| Positive Full Scale Calibration Register | Self Calibration Value |

| Negative Full Scale Calibration Register | Self Calibration Value |

TABLE 2. REGISTER RESET VALUES

The configuration of the HI7190 is changed by writing new setup data to the Control Register. Whenever data is written to byte 2 and/or byte 1 of the Control Register the part assumes that a critical setup parameter is being changed which means that DRDY goes high and the device is resynchronized. If the configuration is changed such that the device is in any one of the calibration modes, a new calibration is performed before normal conversions continue.

If the device is written to the conversion mode, a new calibration is NOT performed (A new calibration is recommended any time data is written to the Control Register.). In either case, DRDY goes low when valid data is available at the output.

If a single data byte is written to byte 0 of the Control Register, the device assumes the gain has NOT been changed. It is up to the user to re-calibrate the device if the gain is changed in this manner. For this reason it is recommended that the entire Control Register be written when changing the gain of the device. This ensures that the part is re-calibrated (if in a calibration mode) before the DRDY output goes low indicating that valid data is available.

The calibration registers can be read via the serial interface at any time. However, care must be taken when writing data to the calibration registers. If the HI7190 is internally updating any calibration register the user can not write to that calibration register. See the Operational Modes section for details on which calibration registers are updated for the various modes.

Since access to the calibration registers is asynchronous to the conversion process the user is cautioned that new calibration data may not be used on the very next set of "valid" data after a calibration register write. It is guaranteed that the new data will take effect on the second set of output data. Non-calibrated data can be obtained from the device by writing 000000 (h) to the Offset Calibration Register, 800000 (h) to the Positive Full Scale Calibration Register, and 800000 (h) to the Negative Full Scale Calibration Register. This sets the offset correction factor to 0 and the positive and negative gain slope factors to 1.

If several HI7190s share a system master clock the SYNC pin can be used to synchronize their operation. A common SYNC input to multiple devices will synchronize operation such that all output registers are updated simultaneously. Of course the SYNC pin would normally be activated only after each HI7190 has been calibrated or has had calibration coefficients written to it.

The SYNC pin can also be used to control the HI7190 when an external multiplexer is used with a single HI7190. The SYNC pin in this application can be used to guarantee a maximum settling time of 3 conversion periods when switching channels on the multiplexer.

#### Analog Section Description

Figure 6 shows a simplified block diagram of the analog modulator front end of a sigma delta A/D Converter. The input signal  $V_{IN}$  comes into a summing junction (the PGIA in this case) where the previous modulator output is subtracted from it. The resulting signal is then integrated and the output of the integrator goes into the comparator. The output of the comparator is then fed back via a 1-bit DAC to the summing

junction. The feedback loop forces the average of the fed back signal to be equal to the input signal  $V_{\text{IN}}$ .

FIGURE 6. SIMPLE MODULATOR BLOCK DIAGRAM

#### Analog Inputs

The analog input on the HI7190 is a fully differential input with programmable gain capabilities. The input accepts both unipolar and bipolar input signals and gains range from 1 to 128. The common mode range of this input is from  $AV_{SS}$  to  $AV_{DD}$  provided that the absolute value of the analog input voltage lies within the power supplies. The input impedance of the HI7190 is dependent upon the modulator input sampling rate and the sampling rate varies with the selected PGIA gain. Table 3 shows the sampling rates and input impedances for the different gain settings of the HI7190. Note that this table is valid only for a 10MHz master clock. If the input clock frequency is changed, then the input impedance will change accordingly. The equation used to calculate the input impedance is:

$Z_{IN} = 1/(C_{IN} \times f_S),$

where  $C_{\text{in}}$  is the nominal input capacitance (8pF) and  $f_{\text{S}}$  is the modulator sampling rate.

| GAIN               | SAMPLING RATE<br>(kHz) | INPUT IMPEDANCE<br>(MΩ) |

|--------------------|------------------------|-------------------------|

| 1                  | 78.125                 | 1.6                     |

| 2                  | 156.25                 | 0.8                     |

| 4                  | 312.5                  | 0.4                     |

| 8, 16, 32, 64, 128 | 625                    | 0.2                     |

#### TABLE 3. EFFECTIVE INPUT IMPEDANCE vs GAIN

#### Bipolar/Unipolar Input Ranges

The input on the HI7190 can accept either unipolar or bipolar input voltages. Bipolar or unipolar options are chosen by programming the  $B/\overline{U}$  bit of the Control Register. Programming the part for either unipolar or bipolar operation does not change the input signal conditioning.

The inputs are differential, and as a result are referenced to the voltage on the V<sub>INLO</sub> input. For example, if V<sub>INLO</sub> is +1.25V and the HI7190 is configured for unipolar operation with a gain of 1 and a V<sub>REF</sub> of +2.5V, the input voltage range on the V<sub>INHI</sub> input is +1.25V to +3.75V. If V<sub>INLO</sub> is +1.25V and the HI7190 is configured for bipolar mode with gain of 1 and a V<sub>REF</sub> of +2.5V, the analog input range on the V<sub>INHI</sub> input is -1.25V to +3.75V.

#### Programmable Gain Instrumentation Amplifier

The Programmable Gain Instrumentation Amplifier allows the user to directly interface low level sensors and bridges directly to the HI7190. The PGIA has 4 selectable gain options of 1, 2, 4, 8 which are implemented by multiple sampling of the input signal. Input signals can be gained up further to 16, 32, 64 or 128. These higher gains are implemented in the digital section of the design to maintain a high signal to noise ratio through the front end amplifiers. The gain is digitally programmable in the Control Register via the serial interface. For optimum PGIA performance the V<sub>CM</sub> pin should be tied to the mid point of the analog supplies.

#### **Differential Reference Input**

The reference inputs of the of the HI7190, V<sub>RHI</sub> and V<sub>RLO</sub>, provide a differential reference input capability. The nominal differential voltage (V<sub>REF</sub> = V<sub>RHI</sub> - V<sub>RLO</sub>) is +2.5V and the common mode voltage cab be anywhere between AV<sub>SS</sub> and AV<sub>DD</sub>. Larger values of V<sub>REF</sub> can be used without degradation in performance with the maximum reference voltage being V<sub>REF</sub> = +5V. Smaller values of V<sub>REF</sub> can also be used but performance will be degraded since the LSB size is reduced.

The full scale range of the HI7190 is defined as:

$FSR_{BIPOLAR} = 2 \times V_{REF}/GAIN$

$FSR_{UNIPOLAR} = V_{REF}/GAIN$

and  $V_{\mbox{RHI}}$  must always be greater than  $V_{\mbox{RLO}}$  for proper operation of the device.

The reference inputs provide a high impedance dynamic load similar to the analog inputs and the effective input impedance for the reference inputs can be calculated in the same manner as it is for the analog input impedance. The only difference in the calculation is that C<sub>IN</sub> for the reference inputs is 10.67pF. Therefore, the input impedance range for the reference inputs is from 149k $\Omega$  in a gain of 8 or higher mode to 833k $\Omega$  in the gain of 1 mode.

#### V<sub>CM</sub> Input

The voltage at the V<sub>CM</sub> input is the voltage that the internal analog circuitry is referenced to and should always be tied to the midpoint of the AV<sub>DD</sub> and AV<sub>SS</sub> supplies. This point provides a common mode input voltage for the internal operational amplifiers and must be driven from a low noise, low impedance source if it is not tied to analog ground. Failure to do so will result in degraded HI7190 performance. It is recommended that V<sub>CM</sub> be tied to analog ground when operating off of AV<sub>DD</sub> = +5V and AV<sub>SS</sub> = -5V supplies.

$V_{CM}$  also determines the headroom at the upper and lower ends of the power supplies which is limited by the common mode input range where the internal operational amplifiers remain in the linear, high gain region of operation. The HI7190 is designed to have a range of AV\_{SS} +1.8V < V\_{CM} <

$AV_{DD}$  - 1.8V. Exceeding this range on the V<sub>CM</sub> pin will compromise the device performance.

#### Transducer Burn-Out Current Source

The V<sub>INHI</sub> input of the HI7190 contains a 500nA (Typ) current source which can be turned on/off via the Control Register. This current source can be used in checking whether a transducer has burnt-out or become open before attempting to take measurements on that channel. When the current source is turned on an additional offset will be created indicating the presence of a transducer. The current source is controlled by the BO bit (Bit 4) in the Control Register and is disabled on power up. See Figure 7 for an applications circuit.

FIGURE 7. BURN-OUT CURRENT SOURCE CIRCUIT

#### **Digital Section Description**

A block diagram of the digital section of the HI7190 is shown in Figure 8. This section includes a low pass decimation filter, conversion controller, calibration logic, serial interface, and clock generator.

FIGURE 8. DIGITAL SECTION BLOCK DIAGRAM

#### **Digital Filtering**

One advantage of digital filtering is that it occurs after the conversion process and can remove noise introduced during

the conversion. It can not, however, remove noise present on the analog signal prior to the ADC (which an analog filter can).

One problem with the modulator/digital filter combination is that excursions outside the full scale range of the device could cause the modulator and digital filter to saturate. This device has headroom built in to the modulator and digital filter which tolerates signal deviations up to 33% outside of the full scale range of the device. If noise spikes can drive the input signal outside of this extended range, it is recommended that an input analog filter is used or the overall input signal level is reduced.

#### Low Pass Decimation Filter

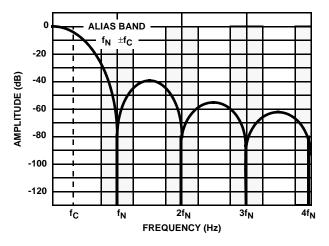

The digital low-pass filter is a Hogenauer (sinc<sup>3</sup>) decimating filter. This filter was chosen because it is a cost effective low pass decimating filter that minimizes the need for internal multipliers and extensive storage and is most effective when used with high sampling or oversampling rates. Figure 9 shows the frequency characteristics of the filter where f<sub>C</sub> is the -3dB frequency of the input signal and f<sub>N</sub> is the programmed notch frequency. The analog modulator sends a one bit data stream to the filter at a rate of that is determined by:

#### f<sub>MODULATOR</sub> = f<sub>OSC</sub>/128

$f_{MODULATOR} = 78.125$ kHz for  $f_{OSC} = 10$ MHz.

The filter then converts the serial modulator data into 40-bit words for processing by the Hogenauer filter. The data is decimated in the filter at a rate determined by the CODE word FP10-FP0 (programed by the user into the Control Register) and the external clock rate. The equation is:

#### $f_{NOTCH} = f_{OSC} / (512 \times CODE).$

The Control Register has 11 bits that select the filter cutoff frequency and the first notch of the filter. The output data update rate is equal to the notch frequency. The notch frequency sets the Nyquist sampling rate of the device while the -3dB point of the filter determines the frequency spectrum of interest ( $f_S$ ). The FP bits have a usable range of 10 through 2047 where 10 yields a 1.953kHz Nyquist rate.

The Hogenauer filter contains alias components that reflect around the notch frequency. If the spectrum of the frequency of interest reaches the alias component, the data has been aliased and therefore undersampled.

#### Filter Characteristics

Please note: We have recently discovered a performance anomaly with the HI7190. The problem occurs when the digital code for the notch filter is programmed within certain frequencies. We believe the error is caused by the calibration logic and the digital notch code NOT the absolute frequency. The error is seen when the user applies mid-scale (0V input, Bipolar mode). With this input, the expected digital output

# should be mid-scale ( $800000_h$ ). Instead, there is a small probability, of an erroneous negative full scale ( $000000_h$ ) output. Refer to Technical Brief TB348 for complete details.

The FP10 to FP0 bits programmed into the Control Register determine the cutoff (or notch) frequency of the digital filter. The allowable code range is 00A<sub>H</sub>. This corresponds to a maximum and minimum cutoff frequency of 1.953kHz and 10Hz, respectively when operating at a clock frequency of 10MHz. If a 1MHz clock is used then the maximum and minimum cutoff frequencies become 195.3kHz and 1Hz, respectively. A plot of the  $(sinx/x)^3$  digital filter characteristics is shown in Figure 9. This filter provides greater than 120dB of 50Hz or 60Hz rejection. Changing the clock frequency or the programming of the FP bits does not change the shape of the filter characteristics, it merely shifts the notch frequency. This low pass digital filter at the output of the converter has an accompanying settling time for step inputs just as a low pass analog filter does. New data takes between 3 and 4 conversion periods to settle and update on the serial port with a conversion period  $t_{CONV}$  being equal to 1/f<sub>N</sub>.

#### Input Filtering

The digital filter does not provide rejection at integer multiples of the modulator sampling frequency. This implies that there are frequency bands where noise passes to the output without attenuation. For most cases this is not a problem because the high oversampling rate and noise shaping characteristics of the modulator cause this noise to become a small portion of the broadband noise which is filtered. However, if an anti-alias filter is necessary a single pole RC filter is usually sufficient.

If an input filter is used the user must be careful that the source impedance of the filter is low enough not to cause gain errors in the system. The DC input impedance at the inputs is >  $1G\Omega$  but it is a dynamic load that changes with clock frequency and selected gain. The input sample rate, also dependent upon

clock frequency and gain, determines the allotted time for the input capacitor to charge. The addition of external components may cause the charge time of the capacitor to increase beyond the allotted time. The result of the input not settling to the proper value is a system gain error which can be eliminated by system calibration of the HI7190.

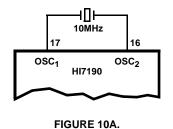

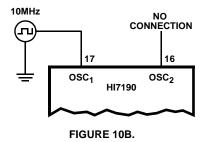

#### Clocking/Oscillators

The master clock into the HI7190 can be supplied by either a crystal connected between the OSC<sub>1</sub> and OSC<sub>2</sub> pins as shown in Figure 10A or a CMOS compatible clock signal connected to the OSC<sub>1</sub> pin as shown in Figure 10B. The input sampling frequency, modulator sampling frequency, filter -3dB frequency, output update rate, and calibration time are all directly related to the master clock frequency, f<sub>OSC</sub>. For example, if a 1MHz clock is used instead of a 10MHz clock, what is normally a 10Hz conversion rate becomes a 1Hz conversion rate. Lowering the clock frequency will also lower the amount of current drawn from the power supplies. Please note that the HI7190 specifications are written for a 10MHz clock only.

FIGURE 10. OSCILLATOR CONFIGURATIONS

#### **Operational Modes**

The HI7190 contains several operational modes including calibration modes for cancelling offset and gain errors of both internal and external circuitry. A calibration routine should be initiated whenever there is a change in the ambient operating temperature or supply voltage. Calibration should also be initiated if there is a change in the gain, filter notch, bipolar, or unipolar input range. Non-calibrated data can be obtained from the device by writing 000000 to the Offset Calibration Register, 800000 (h) to the Positive Full Scale Calibration Register. This sets the offset correction factor to 0 and both the positive and negative gain slope factors to 1.

The HI7190 offers several different modes of Self-Calibration and System Calibration. For calibration to occur, the on-chip microcontroller must convert the modulator output for three different input conditions - "zero-scale," "positive full scale," and "negative full scale". With these readings, the HI7190 can null any offset errors and calculate the gain slope factor for the transfer function of the converter. It is imperative that the zero-scale calibration be performed before either of the gain calibrations. However, the order of the gain calibrations is not important.

The calibration modes are user selectable in the Control Register by using the MD bits (MD2-MD0) as shown in Table 4. DRDY will go low indicating that the calibration is complete **and** there is valid data at the output.

| MD2 | MD1 | MD0 | OPERATIONAL MODE                                         |

|-----|-----|-----|----------------------------------------------------------|

| 0   | 0   | 0   | Conversion                                               |

| 0   | 0   | 1   | Self Calibration (Gain of 1 only)                        |

| 0   | 1   | 0   | System Offset Calibration                                |

| 0   | 1   | 1   | System Positive Full Scale Calibration                   |

| 1   | 0   | 0   | System Negative Full Scale Calibration                   |

| 1   | 0   | 1   | System Offset/Internal Gain Calibration (Gain of 1 only) |

| 1   | 1   | 0   | System Gain Calibration                                  |

| 1   | 1   | 1   | Reserved                                                 |

#### **Conversion Mode**

For Conversion Mode operation the HI7190 converts the differential voltage between V<sub>INHI</sub> and V<sub>INLO</sub>. From switching into this mode it takes 3 conversion periods (3 x  $1/f_N$ ) for DRDY to go low and new data to be valid. No calibration coefficients are generated when operating in Conversion Mode as data is calibrated using the existing calibration coefficients.

#### Self-Calibration Mode

Please note: Self-calibration is only valid when operating in a gain of one. In addition, the offset and gain errors are not reduced as with the full system calibration.

The Self-Calibration Mode is a three step process that updates the Offset Calibration Register, the Positive Full Scale Calibration Register, and the Negative Full Scale Calibration Register. In this mode an internal offset calibration is done by disconnecting the external inputs and shorting the inputs of the PGIA together. After 3 conversion periods the Offset Calibration Register is updated with the value that corrects any internal offset errors.

After the offset calibration is completed, the Positive and Negative Full Scale Calibration Registers are updated. The inputs  $V_{\text{INHI}}$  and  $V_{\text{INLO}}$  are disconnected and the external reference is applied across the modulator inputs. The

HI7190 then takes 3 conversion cycles to sample the data and update the Positive Full Scale Calibration Register. Next the polarity of the reference voltage across the modulator input terminals is reversed and after 3 conversion cycles the Negative Full Scale Calibration Register is updated. The values stored in the Positive and Negative Full Scale Calibration Registers correct for any internal gain errors in the A/D transfer function. After 3 more conversion cycles the DRDY line will activate signaling that the calibration is complete and valid data is present in the Data Output Register.

#### System Offset Calibration Mode

The System Offset Calibration Mode is a single step process that allows the user to lump offset errors of external circuitry and the internal errors of the HI7190 together and null them out. This mode will convert the external differential signal applied to the  $V_{IN}$  inputs and then store that value in the Offset Calibration Register. *The user must apply the zero point or offset voltage to the HI7190 analog inputs and allow the signal to settle before* selecting this mode. After 4 conversion periods the DRDY line will activate signaling that the calibration is complete and valid data is present in the Data Output Register.

#### System Positive Full Scale Calibration Mode

The System Positive Full Scale Calibration Mode is a single step process that allows the user to lump gain errors of external circuitry and the internal errors of the HI7190 together and null them out. This mode will convert the external differential signal applied to the  $V_{IN}$  inputs and stores the converted value in the Positive Full Scale Calibration Register. *The user must apply the +Full Scale voltage to the HI7190 analog inputs and allow the signal to settle before selecting this mode.* After 4 conversion periods the DRDY line will activate signaling the calibration is complete and valid data is present in the Data Output Register.

#### System Negative Full Scale Calibration Mode

The System Negative Full Scale Calibration Mode is a single-step process that allows the user to lump gain errors of external circuitry and the internal errors of the HI7190 together and null them out. This mode will convert the external differential signal applied to the V<sub>IN</sub> inputs and stores the converted value in the Negative Full Scale Calibration Register. *The user must apply the -Full Scale voltage to the HI7190 analog inputs and allow the signal to settle before* selecting this mode. After 4 conversion periods the DRDY line will activate signaling the calibration is complete and valid data is present in the Data Output Register.

#### System Offset/Internal Gain Calibration Mode

Please note: System Offset/Internal Gain is only valid when operating in a gain of one. In addition, the offset and gain errors are not reduced as with the full system calibration.

The System Offset/Internal Gain Calibration Mode is a single step process that updates the Offset Calibration Register, the Positive Full Scale Calibration Register, and the Negative Full Scale Calibration Register. First the external differential signal applied to the  $V_{IN}$  inputs is converted and that value is stored in the Offset Calibration Register. *The user must apply the zero point or offset voltage to the HI7190 analog inputs and allow the signal to settle before selecting this mode.*

After this is completed the Positive and Negative Full Scale Calibration Registers are updated. The inputs  $V_{INHI}$  and  $V_{INLO}$ are disconnected and the external reference is switched in. The HI7190 then takes 3 conversion cycles to sample the data and update the Positive Full Scale Calibration Register. Next the polarity of the reference voltage across the  $V_{INHI}$  and  $V_{INLO}$ terminals is reversed and after 3 conversion cycles the Negative Full Calibration Register is updated. The values stored in the Positive and Negative Full Scale Calibration Registers correct for any internal gain errors in the A/D transfer function. After 3 more conversion cycles, the DRDY line will activate signaling that the calibration is complete and valid data is present in the Data Output Register.

#### System Gain Calibration Mode

The Gain Calibration Mode is a single step process that updates the Positive and Negative Full Scale Calibration Registers. This mode will convert the external differential signal applied to the  $V_{IN}$  inputs and then store that value in the Negative Full Scale Calibration Register. Then the polarity of the input is reversed internally and another conversion is performed. This conversion result is written to the Positive Full Scale Calibration Register. The user must apply the +Full Scale voltage to the HI7190 analog inputs and allow the signal to settle before selecting this mode. After 1 more conversion period the DRDY line will activate signaling the calibration is complete and valid data is present in the data output register.

#### Reserved

This mode is not used in the HI7190 and should not be selected. There is no internal detection logic to keep this condition from being selected and care should be taken not to assert this bit combination.

#### Offset and Span Limits

There are limits to the amount of offset and gain which can be adjusted out for the HI7190. For both bipolar and unipolar modes the minimum and maximum input spans are  $0.2 \times V_{REF}$ /GAIN and  $1.2 \times V_{REF}$ /GAIN respectively.

In the unipolar mode the offset plus the span cannot exceed the 1.2 x  $V_{\mbox{\scriptsize REF}}/\mbox{\scriptsize GAIN}$  limit. So, if the span is at its minimum

value of 0.2 x V<sub>REF</sub>/GAIN, the offset must be less than 1 x V<sub>REF</sub>/GAIN. In bipolar mode the span is equidistant around the voltage used for the zero scale point. For this mode the offset plus half the span cannot exceed 1.2 x V<sub>REF</sub>/GAIN. If the span is at ±0.2 x V<sub>REF</sub>/GAIN, then the offset can not be greater than ±2 x V<sub>REF</sub>/GAIN.

#### Serial Interface

The HI7190 has a flexible, synchronous serial communication port to allow easy interfacing to many industry standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola 6805/11 SPI and Intel 8051 SSR protocols. The Serial Interface is a flexible 2-wire or 3-wire hardware interface where the HI7190 can be configured to read and write on a single bidirectional line (SDIO) or configured for writing on SDIO and reading on the SDO line.

The interface is byte organized with each register byte having a specific address and single or multiple byte transfers are supported. In addition, the interface allows flexibility as to the byte and bit access order. That is, the user can specify MSB/LSB first bit positioning and can access bytes in ascending/descending order from any byte position.

The serial interface allows the user to communicate with 5 registers that control the operation of the device.

**Data Output Register** - a 24-bit, read only register containing the conversion results.

**Control Register** - a 24-bit, read/write register containing the setup and operating modes of the device.

**Offset Calibration Register** - a 24-bit, read/write register used for calibrating the zero point of the converter or system.

**Positive Full Scale Calibration Register** - a 24-bit, read/write register used for calibrating the Positive Full Scale point of the converter or system.

**Negative Full Scale Calibration Register** - a 24-bit, read/write register used for calibrating the Negative Full Scale point of the converter or system.

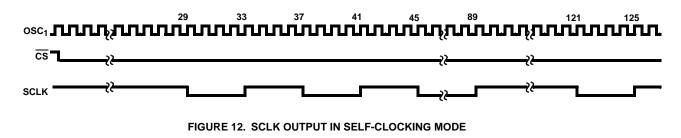

Two clock modes are supported. The HI7190 can accept the serial interface clock (SCLK) as an input from the system or generate the SCLK signal as an output. If the MODE pin is logic low the HI7190 is in external clocking mode and the SCLK pin is configured as an input. In this mode the user supplies the serial interface clock and all interface timing specifications are synchronous to this input. If the MODE pin is logic high the HI7190 is in self-clocking mode and the SCLK pin is configured as an output. In self-clocking mode, SCLK runs at  $F_{SCLK} = OSC_1/8$  and stalls high at byte boundaries. SCLK does NOT have the capability to stall low in this mode. All interface timing specifications are synchronous to the SCLK output.

Normal operation in self-clocking mode is as follows (See Figure 12):  $\overline{CS}$  is sampled low on falling OSC<sub>1</sub> edges. The

first SCLK transition output is delayed 29 OSC<sub>1</sub> cycles from the next rising OSC<sub>1</sub>. SCLK transitions eight times and then stalls high for 28 OSC<sub>1</sub> cycles. After this stall period is completed SCLK will again transition eight times and stall high. This sequence will repeat continuously while  $\overline{CS}$  is active.

The extra OSC<sub>1</sub> cycle required when coming out of the  $\overline{CS}$  inactive state is a one clock cycle latency required to properly sample the  $\overline{CS}$  input. Note that the normal stall at byte boundaries is 28 OSC<sub>1</sub> cycles thus giving a SCLK rising to rising edge stall period of 32 OSC<sub>1</sub> cycles.

The affects of  $\overline{CS}$  on the I/O are different for self-clocking mode (MODE = 1) than for external mode (MODE = 0). For external clocking mode  $\overline{CS}$  inactive disables the I/O state machine, effectively freezing the state of the I/O cycle. That is, an I/O cycle can be interrupted using chip select and the HI7190 will continue with that I/O cycle when re-enabled via  $\overline{CS}$ . SCLK can continue toggling while  $\overline{CS}$  is inactive. If  $\overline{CS}$ goes inactive during an I/O cycle, it is up to the user to ensure that the state of SCLK is identical when reactivating  $\overline{CS}$  as to what it was when  $\overline{CS}$  went inactive. For read operations in external clocking mode, the output will go three-state immediately upon deactivation of  $\overline{CS}$ .

For self-clocking mode (MODE = 1), the affects of CS are different. If CS transitions high (inactive) during the period when data is being transferred (any non stall time) the HI7190 will complete the data transfer to the byte boundary. That is, once SCLK begins the eight transition sequence, it will always complete the eight cycles. If CS remains inactive after the byte has been transferred it will be sampled and SCLK will remain stalled high indefinitely. If CS has returned to active low before the data byte transfer period is completed the HI7190 acts as if CS was active during the entire transfer period.

It is important to realize that the user can interrupt a data transfer on byte boundaries. That is, if the Instruction Register calls for a 3 byte transfer and  $\overline{CS}$  is inactive after only one byte has been transferred, the HI7190, when reactivated, will continue with the remaining two bytes before looking for the next Instruction Register write cycle.

Note that the outputs will NOT go three-state immediately upon CS inactive for read operations in self-clocking mode. In the case of CS going inactive during a read cycle the outputs remain driving until after the last data bit is transferred. In the case of CS inactive during the clock stall time it takes 1 OSC<sub>1</sub> cycle plus prop delay (Max) for the outputs to be disabled.

#### I/O Port Pin Descriptions

The serial I/O port is a bidirectional port which is used to read the data register and read or write the control register and calibration registers. The port contains two data lines, a synchronous clock, and a status flag. Figure 11 shows a diagram of the serial interface lines.

FIGURE 11. HI7190 SERIAL INTERFACE

**SDO** - Serial Data out. Data is read from this line using those protocols with separate lines for transmitting and receiving data. An example of such a standard is the Motorola Serial Peripheral Interface (SPI) using the 68HC05 and 68HC11 family of microcontrollers, or other similar processors. In the case of using bidirectional data transfer on SDIO, SDO does not output data and is set in a high impedance state.

**SDIO** - Serial Data in or out. Data is always written to the device on this line. However, this line can be used as a bidirectional data line. This is done by properly setting up the Control Register. Bidirectional data transfer on this line can be used with Intel standard serial interfaces (SSR, Mode 0) in MCS51 and MCS96 family of microcontrollers, or other similar processors.

**SCLK** - Serial clock. The serial clock pin is used to synchronize data to and from the HI7190 and to run the port state machines. In Synchronous External Clock Mode, SCLK is configured as an input, is supplied by the user, and can run up to a 5MHz rate. In Synchronous Self Clocking Mode, SCLK is configured as an output and runs at OSC<sub>1</sub>/8.

$\overline{CS}$  - Chip select. This signal is an active low input that allows more than one device on the same serial communication lines. The SDO and SDIO will go to a high impedance state when this signal is high. If driven high during any communication cycle, that cycle will be suspended until  $\overline{CS}$  reactivation. Chip select can be tied low in systems that maintain control of SCLK.

**DRDY** - Data Ready. This is an output status flag from the device to signal that the Data Output Register has been updated with the new conversion result. DRDY is useful as an edge or level sensitive interrupt signal to a microprocessor or microcontroller. DRDY low indicates that new data is available at the Data Output Register. DRDY will return high upon completion of a complete Data Output Register read cycle.

**MODE** - Mode. This input is used to select between Synchronous Self Clocking Mode ('1') or the Synchronous External Clocking Mode ('0'). When this pin is tied to  $V_{DD}$  the serial port is configured in the Synchronous Self Clocking mode where the synchronous shift clock (SCLK) for the serial port is generated by the HI7190 and has a frequency of OSC<sub>1</sub>/8. When the pin is tied to DGND the serial port is configured for the Synchronous External Clocking Mode where the synchronous shift clock for the serial port is generated by an external device up to a maximum frequency of 5MHz.

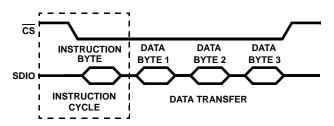

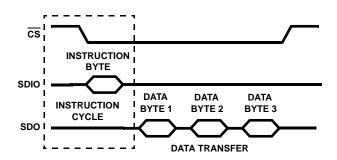

#### Programming the Serial Interface

It is useful to think of the HI7190 interface in terms of communication cycles. Each communication cycle happens in 2 phases. The first phase of every communication cycle is the writing of an instruction byte. The second phase is the data transfer as described by the instruction byte. It is important to note that phase 2 of the communication cycle can be a single byte or a multi-byte transfer of data. For example, the 3-byte Data Output Register can be read using one multi-byte communication cycle rather than three single-byte communication cycles. It is up to the user to maintain synchronism with respect to data transfers. If the system processor "gets lost" the only way to recover is to reset the HI7190. Figures 13A and 13B show both a 2-wire and a 3-wire data transfer.

Several formats are available for reading from and writing to the HI7190 registers in both the 2-wire and 3-wire protocols. A portion of these formats is controlled by the CR<2:1> (BD and  $\overline{\text{MSB}}$ ) bits which control the byte direction and bit order of a data transfer respectively. These two bits can be written in any combination but only the two most useful will be discussed here.